Harmonics Compensation by Using a Multi-Modular H-Bridge-Based Multilevel Converter

Abstract

:1. Introduction

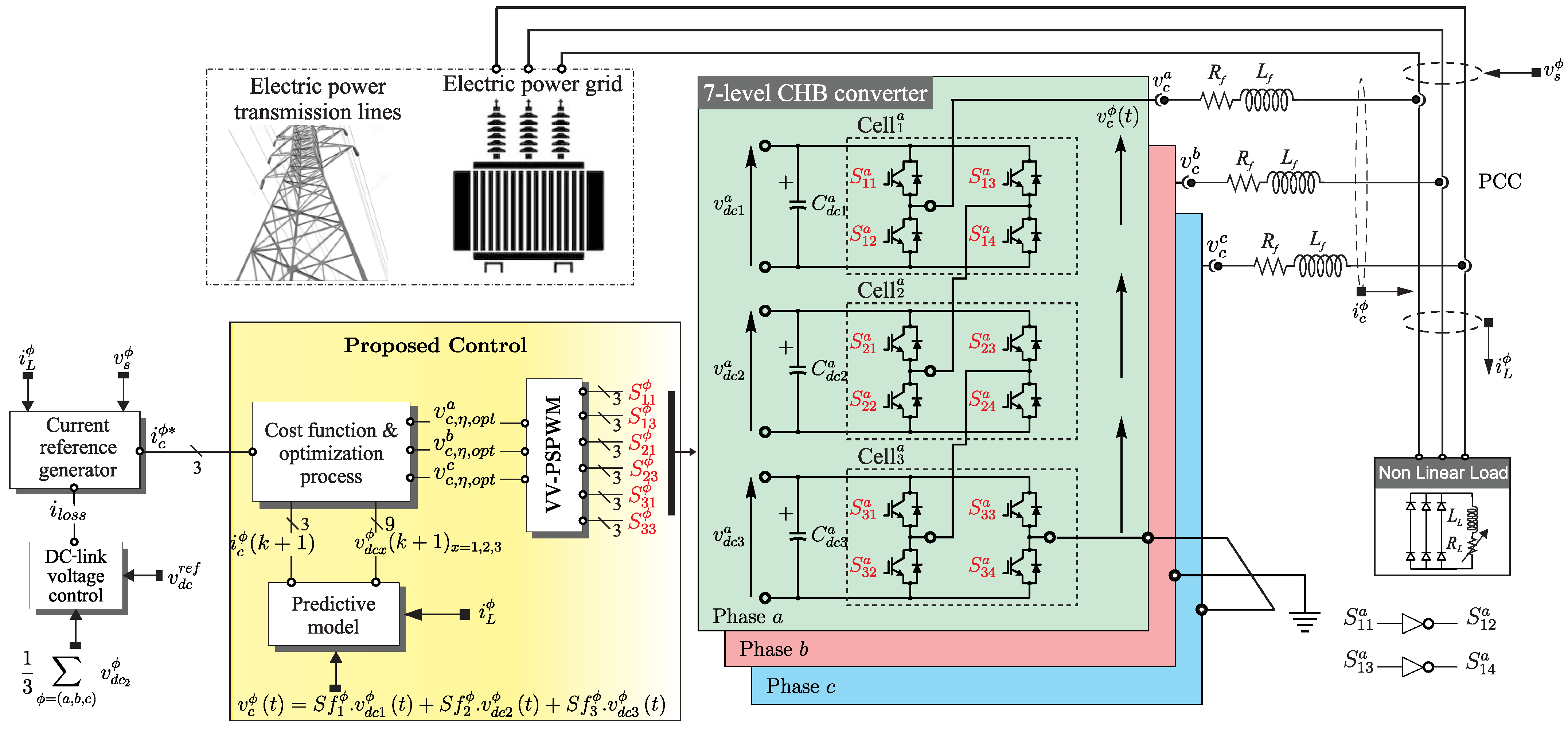

2. Multimodular APF Model

3. Predictive Model

3.1. Current Reference Generation

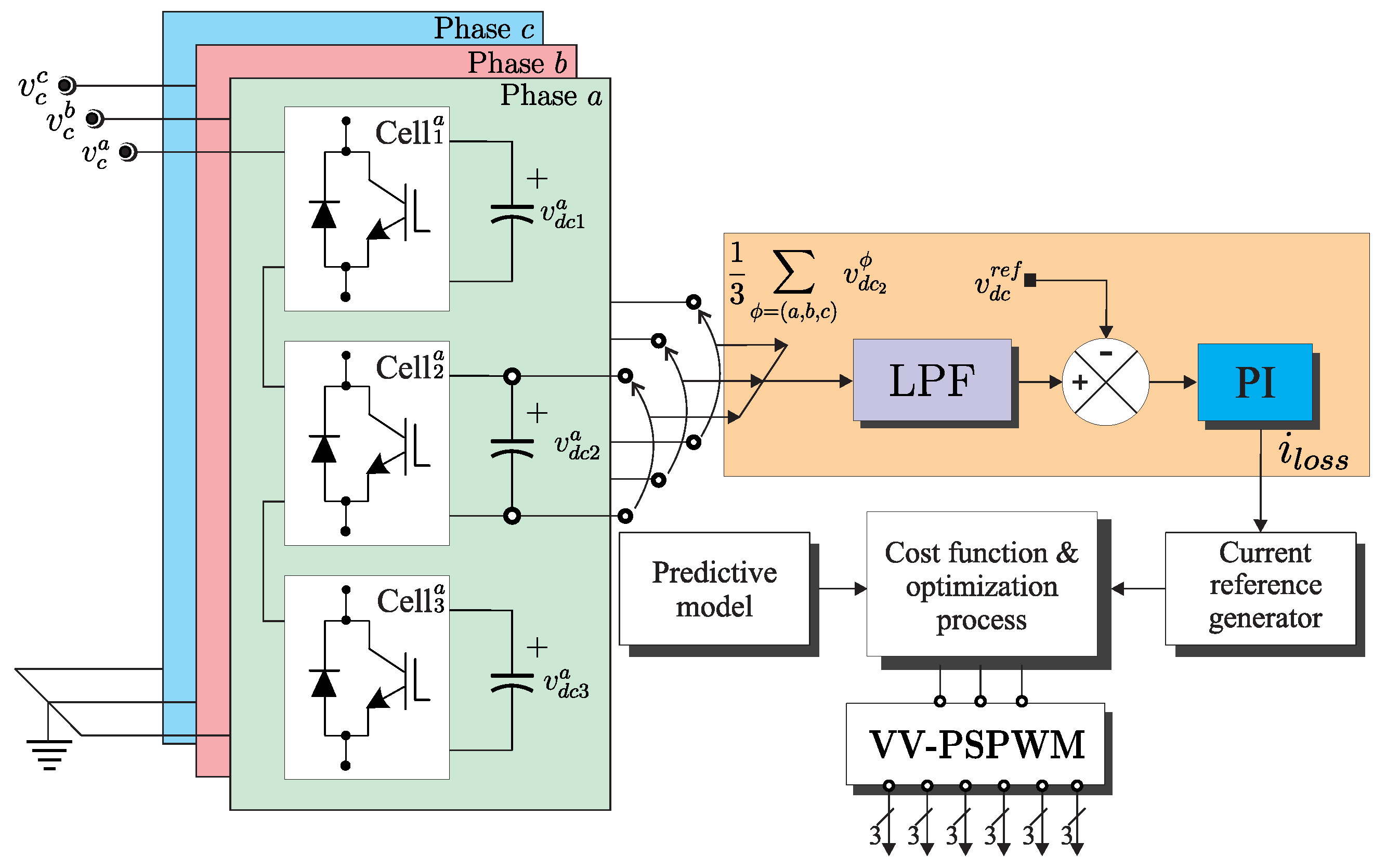

3.2. DC-Link Voltage Control

3.3. Cost Function and Optimization Process

| Algorithm 1 Optimization algorithm. |

1 Initialize 2 Compute the APF current references (12). 3 while do 4 5 Compute the output voltage of the multilevel converter (2). 6 Calculate the APF prediction currents and voltage (4). 7 Compute the cost function (18). 8 if then 9 10 end if 11 if then 12 13 end if 14 if then 15 16 end if 17 18 end while 19 Compute the modulation signals (19). 20 Obtain the turn-on times of the firing signals according to Figure 4. 21 Apply the firing signals. |

3.4. Voltage Vectors’ Phase-Shifted PWM Strategy

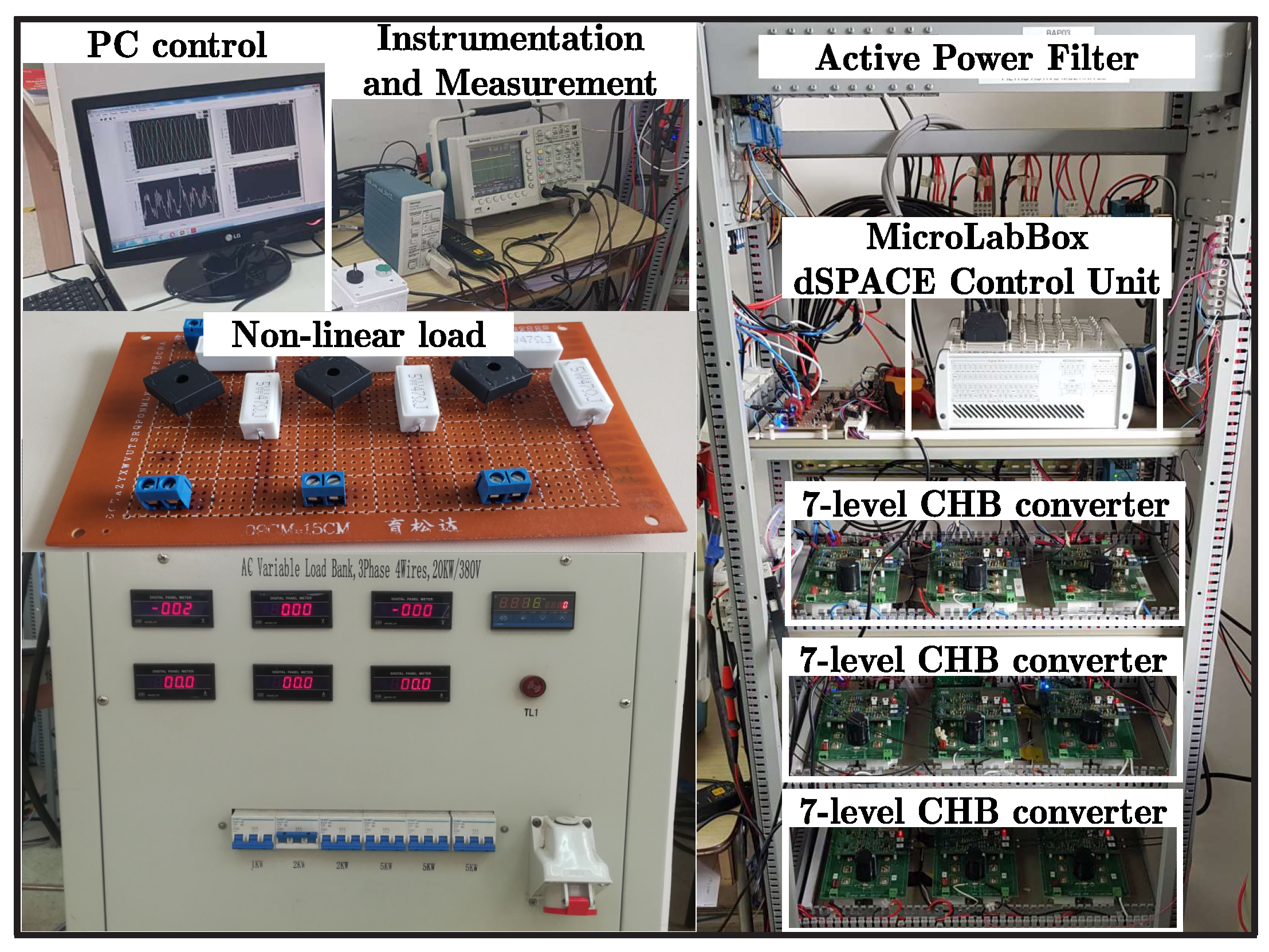

4. Experimental Test Bench

5. Experimental Validation

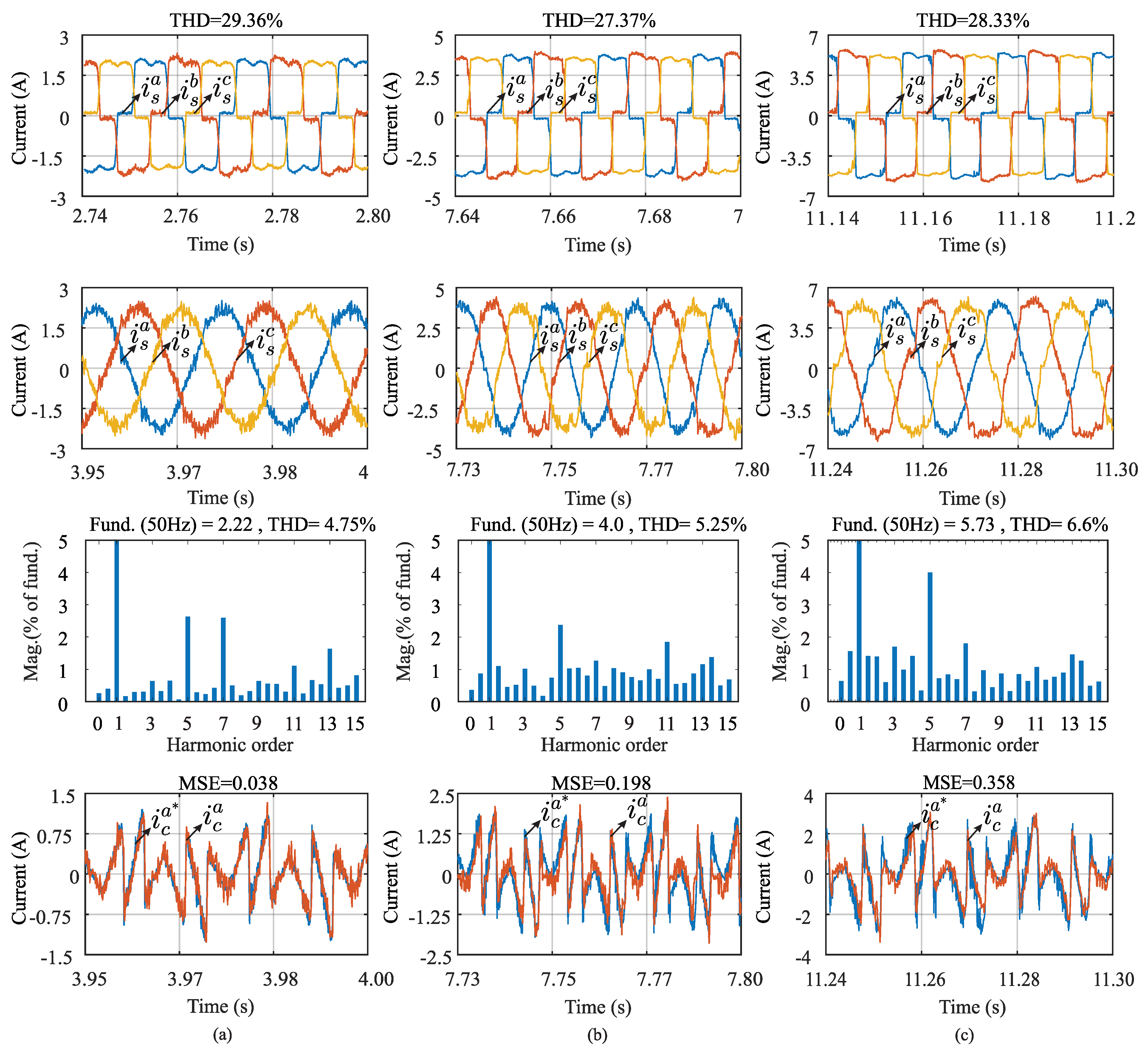

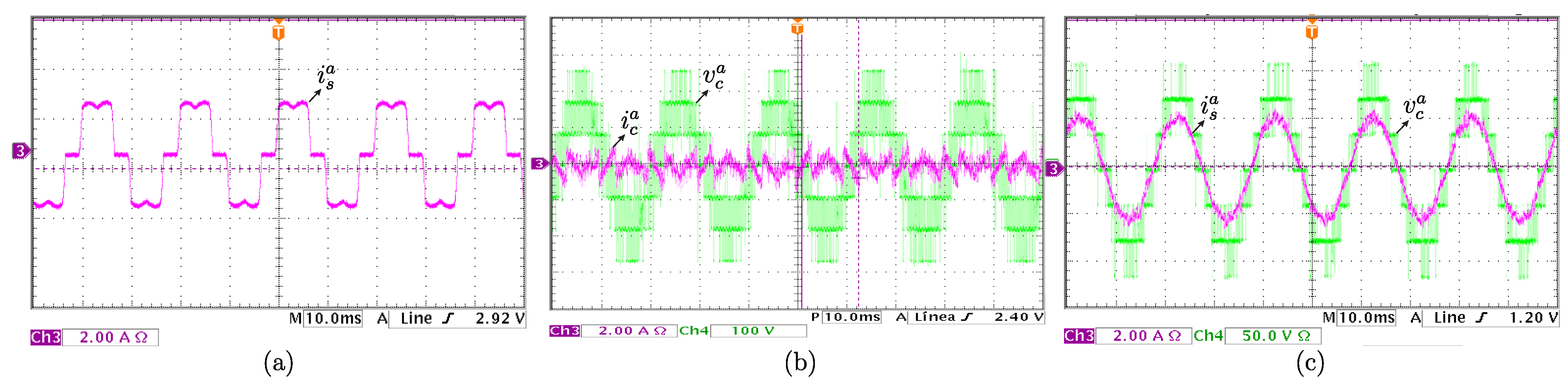

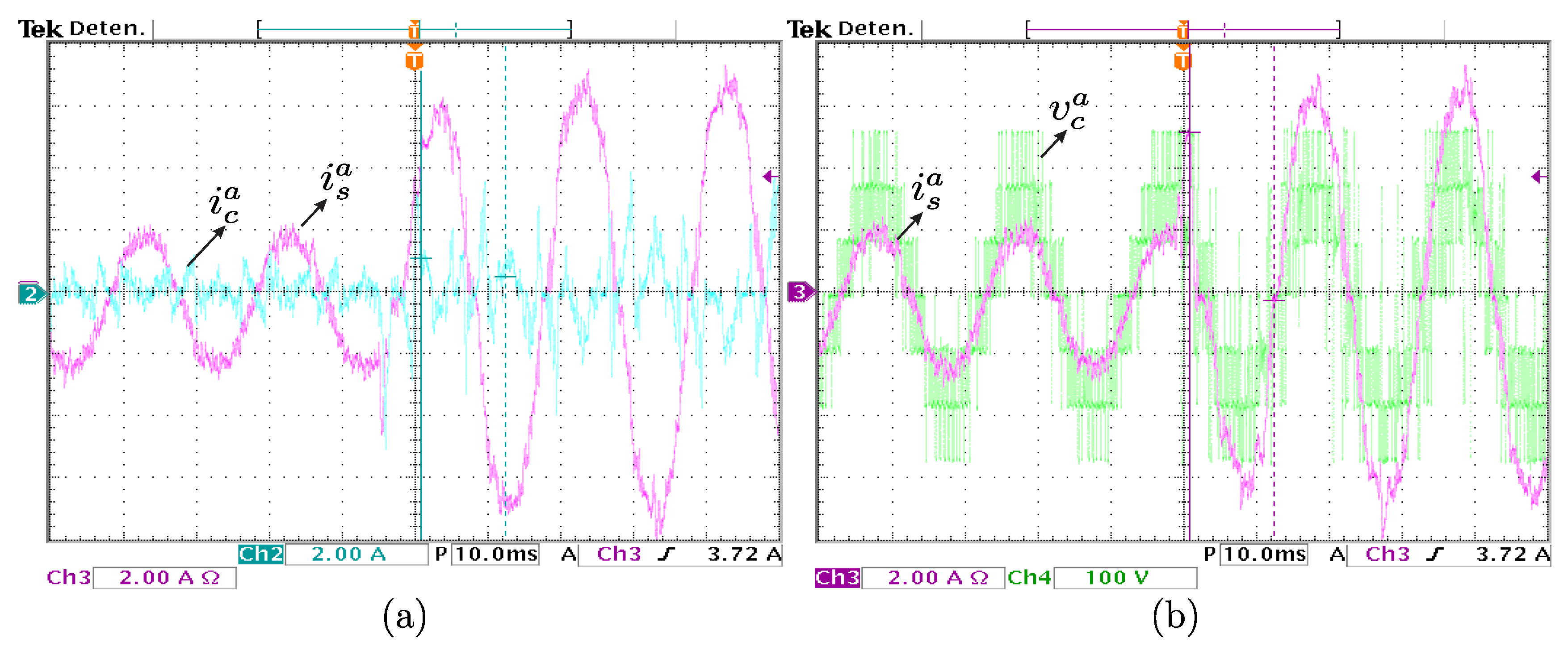

5.1. Verification of the Harmonics Compensation

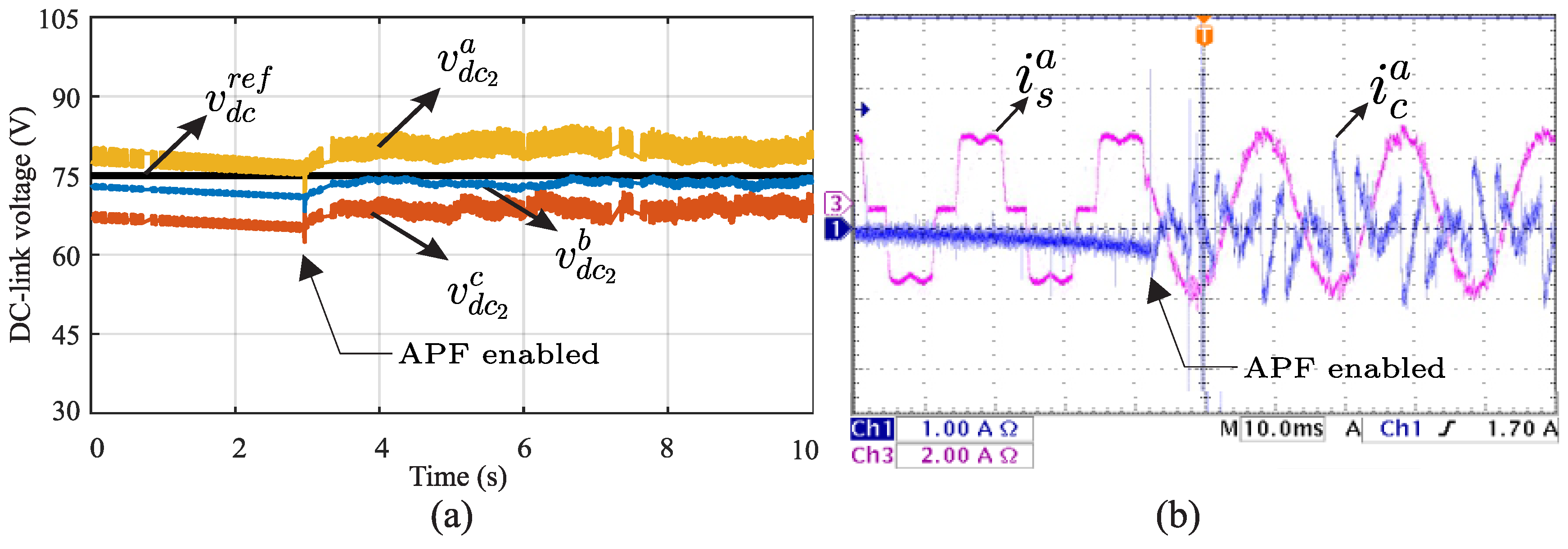

5.2. Verification of the DC-Link Voltage Control

5.3. Verification of the Compensation for Unbalanced Voltages

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| AC | Alternating current |

| ADC | Analog-to-digital converter |

| APF | Active power filter |

| CHB | Cascade H-bridge |

| CPDs | Custom power devices |

| DC | Direct current |

| DERs | Distributed energy resources |

| DVR | Dynamic voltage restorer |

| IGBT | Isolated gate bipolar transistors |

| LPF | Low-pass filter |

| MOSFET | Metal–oxide–semiconductor field-effect transistor |

| MPC | Model predictive control |

| MSE | Mean-squared error |

| PCB | Printed circuit board |

| PCC | Predictive current control |

| PI | Proportional–integral |

| PLL | Phase-locked loop |

| PSPWM | Phase-shifted PWM |

| PWM | Pulse width modulation |

| SiC | Silicon carbide |

| SRF | Synchronous reference frame |

| THD | Total harmonic distortion |

| UPQC | Unified power quality conditioners |

| VSCs | Voltage source converters |

| VV | Voltage vectors |

| Nomenclature | |

| Phase of power grid a, b, and c | |

| Firing signals | |

| x | Corresponding cell number |

| y | Switching device in each cell |

| C | Capacitor |

| Voltages measured in the DC-link | |

| Converter voltage output | |

| Current estimation in the capacitor | |

| APF measured current | |

| Load measured current | |

| Power grid measured current | |

| Voltage measurement in the power grid | |

| Filter resistance | |

| Filter inductance | |

| APF current prediction | |

| APF voltage prediction | |

| Sample time | |

| DC-link voltage reference | |

| Active power load in synchronous frame | |

| Reactive power load in synchronous frame | |

| continuous component of | |

| alternating component of | |

| Active power reference in synchronous frame | |

| Reactive power reference in synchronous frame | |

| Phase angle calculated by the PLL | |

| Estimation of the current required to charge the capacitors | |

| Transformation matrix to | |

| Inverse transformation matrix to | |

| Reference current of phases a, b, and c. | |

| Error between the reference and measured voltages | |

| Voltage error calculated in the previous instant | |

| Sums of the loss currents of each phase | |

| Loss current calculated in the previous instant | |

| PI controller actuation time | |

| PI proportional constant | |

| PI integral constant | |

| Optimum vector | |

| Optimal voltage | |

| Carrier wave | |

| Modulation signals | |

References

- Dash, S.K.; Ray, P.K. Power quality improvement utilizing PV fed unified power quality conditioner based on UV-PI and PR-R controller. CPSS Trans. Power Electron. Appl. 2018, 3, 243–253. [Google Scholar] [CrossRef]

- Zaidi, A.H.; Sunderland, K.; Conlon, M. Role of reactive power (STATCOM) in the planning of distribution network with higher EV charging level. IET Gener. Transm. Distrib. 2019, 13, 951–959. [Google Scholar] [CrossRef]

- Elmetwaly, A.H.; Eldesouky, A.A.; Sallam, A.A. An Adaptive D-FACTS for Power Quality Enhancement in an Isolated Microgrid. IEEE Access 2020, 8, 951–959. [Google Scholar] [CrossRef]

- Badoni, M.; Singh, A.; Singh, B.; Saxena, H. Real-time implementation of active shunt compensator with adaptive SRLMMN control technique for power quality improvement in the distribution system. IET Gener. Transm. Distrib. 2020, 14, 1598–1606. [Google Scholar] [CrossRef]

- Gregor, R.; Pacher, J.; Renault, A.; Comparatore, L.; Rodas, J. Experimental Validation of the DSTATCOM Based on SiC-MOSFET Multilevel Converter for Reactive Power Compensation. J. Syst. Cybern. Inform. 2020, 18, 57–61. [Google Scholar]

- Pradhan, M.; Mishra, M.K. Dual P-Q Theory Based Energy-Optimized Dynamic Voltage Restorer for Power Quality Improvement in a Distribution System. IEEE Trans. Ind. Electron. 2018, 66, 2946–2955. [Google Scholar] [CrossRef]

- Lakshmi, S.; Ganguly, S. An On-Line Operational Optimization Approach for Open Unified Power Quality Conditioner for Energy Loss Minimization of Distribution Networks. IEEE Trans. Power Syst. 2019, 34, 4784–4795. [Google Scholar] [CrossRef]

- Choudhury, S.R.; Das, A.; Anand, S.; Tungare, S.; Sonawane, Y. Adaptive shunt filtering control of UPQC for increased nonlinear loads. IET Power Electron. 2019, 12, 330–336. [Google Scholar] [CrossRef]

- Wang, J.; Xing, Y.; Wu, H.; Yang, T. Dual-DC-Port Dynamic Voltage Restorer With Reduced-Rating Integrated DC-DC Converter for Wide-Range Voltage Sag Compensation. IEEE Trans. Power Electron. 2018, 34, 7437–7449. [Google Scholar] [CrossRef]

- Li, P.; Xie, L.; Han, J.; Pang, S.; Li, P. A new voltage compensation philosophy for dynamic voltage restorer to mitigate voltage sags using three-phase voltage ellipse parameters. IEEE Trans. Power Electron. 2017, 33, 1154–1166. [Google Scholar] [CrossRef]

- Myneni, H.; Kumar, G.S. Simple algorithm for current and voltage control of LCL DSTATCOM for power quality improvement. IET Gener. Transm. Distrib. 2019, 13, 423–434. [Google Scholar] [CrossRef]

- Dheepanchakkravarthy, A.; Jawahar, M.R.; Venkatraman, K.; Selvan, M.P.; Moorthi, S. Performance evaluation of FPGA-based predictive current controller for FL-DSTATCOM in electric distribution system. IET Gener. Transm. Distrib. 2019, 13, 4400–4409. [Google Scholar] [CrossRef]

- Busarello, T.D.C.; Mortezaei, A.; Paredes, H.K.M.; Al-Durra, A.; Pomilio, J.A.; Simoes, M.G. Simplified small-signal model for output voltage control of asymmetric cascaded H-bridge multilevel inverter. IEEE Trans. Power Electron. 2018, 33, 3509–3519. [Google Scholar] [CrossRef] [Green Version]

- Ghat, M.B.; Shukla, A. A new H-bridge hybrid modular converter (HBHMC) for HVDC application: Operating modes, control, and voltage balancing. IEEE Trans. Power Electron. 2018, 33, 6537–6554. [Google Scholar] [CrossRef]

- Zhang, L.; Yuan, X.; Wu, X.; Shi, C.; Zhang, J.; Zhang, Y. Performance evaluation of high-power SiC MOSFET modules in comparison to Si IGBT modules. IEEE Trans. Power Electron. 2019, 34, 1181–1196. [Google Scholar] [CrossRef]

- Fuentes, C.D.; Kouro, S.; Bernet, S. Comparison of 1700-V SiC-MOSFET and Si-IGBT Modules Under Identical Test Setup Conditions. IEEE Trans. Ind. Appl. 2019, 55, 7765–7775. [Google Scholar] [CrossRef]

- Mortezaei, A.; Simões, M.G.; Busarello, T.D.C.; Marafão, F.P.; Al-Durra, A. Grid-connected symmetrical cascaded multilevel converter for power quality improvement. IEEE Trans. Ind. Appl. 2018, 54, 2792–2805. [Google Scholar] [CrossRef] [Green Version]

- Tanaka, T.; Ma, K.; Wang, H.; Blaabjerg, F. Asymmetrical Reactive Power Capability of Modular Multilevel Cascade Converter Based STATCOMs for Offshore Wind Farm. IEEE Trans. Power Electron. 2018, 34, 5147–5164. [Google Scholar] [CrossRef]

- Ye, S.; Zhang, Y.; Xie, L.; Lu, H. Shunt active power filter based on proportional integral and multi vector resonant controllers for compensating nonlinear loads. J. Electr. Comput. Eng. 2018, 2018, 1312064. [Google Scholar] [CrossRef] [Green Version]

- Kasmieh, T.A.; Omran, H.S. Active power filter dimensioning using a hysteresis current controller. Resonance 2009, 1, 2. [Google Scholar]

- Najjar, M.; Shahparasti, M.; Heydari, R.; Nymand, M. Model Predictive Controllers With Capacitor Voltage Balancing for a Single-Phase Five-Level SiC/Si Based ANPC Inverter. IEEE Open J. Power Electron. 2021, 2, 202–211. [Google Scholar] [CrossRef]

- Renault, A.; Ayala, M.; Pacher, J.; Comparatore, L.; Gregor, R.; Toledo, S. Current control based on space vector modulation applied to three-phase H-Bridge STATCOM. In Proceedings of the 2020 IEEE International Conference on Industrial Technology (ICIT), Buenos Aires, Argentina, 26–28 February 2020; pp. 1066–1070. [Google Scholar]

- Renault, A.; Ayala, M.; Pacher, J.; Comparatore, L.; Gregor, R.; Rivera, M. Analysis of H-Bridge STATCOM with Fault Phase Controlled by Modulated Predictive Current Control. In Proceedings of the 2019 IEEE CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), Valparaiso, Chile, 13–27 November 2019; pp. 1–5. [Google Scholar]

- Renault, A.; Rodas, J.; Comparatore, L.; Pacher, J.; Gregor, R. Modulated predictive current control technique for a three-phase four-wire active power filter based on H-bridge two-level converter. In Proceedings of the 2018 53rd International Universities Power Engineering Conference (UPEC), Glasgow, UK, 4–7 September 2018; pp. 1–6. [Google Scholar]

- Comparatore, L.; Renault, A.; Pacher, J.; Rodas, J.; Gregor, R. Finite control set model predictive control strategies for a three-phase seven-level cascade H-bridge DSTATCOM. In Proceedings of the 2018 7th International Conference on Renewable Energy Research and Applications (ICRERA), Paris, France, 14–17 October 2018; pp. 779–784. [Google Scholar]

- Gao, H.; Zhang, P.; Liu, X.; Feng, S.; Ma, J.; Li, R. Seven-Level Active Power Filter Based on a Novel H-Bridge Power Topology Structure. Energies 2019, 12, 2997. [Google Scholar] [CrossRef] [Green Version]

- Wang, Y.; Wang, Y.; Chen, S.Z.; Zhang, G.; Zhang, Y. A Simplified Minimum DC-Link Voltage Control Strategy for Shunt Active Power Filters. Energies 2018, 11, 2407. [Google Scholar] [CrossRef] [Green Version]

- Ayala, M.; Doval-Gandoy, J.; Rodas, J.; Gonzalez, O.; Gregor, R.; Rivera, M. A Novel Modulated Model Predictive Control Applied to Six-Phase Induction Motor Drives. IEEE Trans. Ind. Electron. 2020, 68, 3672–3682. [Google Scholar] [CrossRef]

- Ayala, M.; Doval-Gandoy, J.; Rodas, J.; Gonzalez, O.; Gregor, R. Current control designed with model based predictive control for six-phase motor drives. ISA Trans. 2020, 98, 496–504. [Google Scholar] [CrossRef]

- Toledo, S.; Maqueda, E.; Rivera, M.; Gregor, R.; Wheeler, P.; Romero, C. Improved Predictive Control in Multi-Modular Matrix Converter for Six-Phase Generation Systems. Energies 2020, 13, 2660. [Google Scholar] [CrossRef]

- Panda, A.; Patnaik, S. Analysis of cascaded multilevel inverters for active harmonic filtering in distribution networks. Int. J. Electr. Power Energy Syst. 2014, 66, 216–226. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.; Carrasco, J.; Franquelo, L.; Galvan, E.; Reyes, M.; Sanchez, J.; Dominguez, E. Analysis of the Power Balance in the Cells of a Multilevel Cascaded H-Bridge Converter. IEEE Trans. Ind. Electron. 2010, 57, 2287–2296. [Google Scholar] [CrossRef]

- Zhang, Y.; Wu, X.; Yuan, X.; Wang, Y.; Dai, P. Fast Model Predictive Control for Multilevel Cascaded H-Bridge STATCOM with Polynomial Computation Time. IEEE Trans. Ind. Electron. 2016, 63, 5231–5243. [Google Scholar] [CrossRef]

- Gregor, R.; Comparatore, L.; Renault, A.; Rodas, J.; Pacher, J.; Toledo, S.; Rivera, M. A novel predictive-fixed switching frequency technique for a cascade H-bridge multilevel STATCOM. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3672–3677. [Google Scholar] [CrossRef]

- Mishra, M.K.; Karthikeyan, K. A fast-acting DC-link voltage controller for three-phase DSTATCOM to compensate AC and DC loads. IEEE Trans. Power Deliv. 2009, 24, 2291–2299. [Google Scholar] [CrossRef]

| Cell | Cell | Cell | |||||

|---|---|---|---|---|---|---|---|

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | −3 |

| 0 | 1 | 0 | 1 | 0 | 0 | 2 | −2 |

| 0 | 1 | 0 | 0 | 0 | 0 | 3 | −1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 4 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 5 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 | 6 | 2 |

| 1 | 0 | 1 | 0 | 1 | 0 | 7 | 3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gregor, R.; Pacher, J.; Espinoza, A.; Renault, A.; Comparatore, L.; Ayala, M. Harmonics Compensation by Using a Multi-Modular H-Bridge-Based Multilevel Converter. Energies 2021, 14, 4698. https://doi.org/10.3390/en14154698

Gregor R, Pacher J, Espinoza A, Renault A, Comparatore L, Ayala M. Harmonics Compensation by Using a Multi-Modular H-Bridge-Based Multilevel Converter. Energies. 2021; 14(15):4698. https://doi.org/10.3390/en14154698

Chicago/Turabian StyleGregor, Raul, Julio Pacher, Alejandro Espinoza, Alfredo Renault, Leonardo Comparatore, and Magno Ayala. 2021. "Harmonics Compensation by Using a Multi-Modular H-Bridge-Based Multilevel Converter" Energies 14, no. 15: 4698. https://doi.org/10.3390/en14154698

APA StyleGregor, R., Pacher, J., Espinoza, A., Renault, A., Comparatore, L., & Ayala, M. (2021). Harmonics Compensation by Using a Multi-Modular H-Bridge-Based Multilevel Converter. Energies, 14(15), 4698. https://doi.org/10.3390/en14154698