1. Introduction

The increased adoption of power electronics in all areas in the electrical power domain has made various feasible innovations such as electric vehicles [

1,

2], HVDC transmission systems, large-scale transformation towards renewable energy resources [

3]. With the DC–AC conversion playing a significant role, the development of multilevel inverters (MLIs) is an essential process. Succeeding the conventional two-level and three-level inverter topologies, MLIs possess the advantages of better power quality, efficient conversion, reduced thermal management, smaller filter size as well as in-built redundancy and voltage boosting features [

4,

5]. The classical MLI topologies are the Neutral Point Clamped (NPC), the Flying Capacitor (FC), and the Cascaded H-bridge (CHB) topologies. Since their inception, a vast diversity of newer structures has been proposed to eliminate the disadvantages of classical topologies. They include reduced device count, lower per-unit total standing voltage, and greater efficiency converters. Recent developments in MLI design are also focused on EMI, volume, weight and cooling, and packaging requirements [

6].

Implementing a large number of power semiconductor switches leads to an increased susceptibility towards fault and makes monitoring and diagnosis more complex [

7]. This can be unacceptable in safety-critical applications such as onboard power systems. Isolated sites with heavy economic penalties for downtime and maintenance or repair such as an offshore wind farm also demand high reliability [

8,

9,

10]. Power converters are frequently operated in high-stress environments and less than optimal cooling management. One survey on electrical drive systems concluded that 47% of 484 failures were caused by semiconductor components [

11]. Another survey concluded that 37% of unexpected maintenance routines and 59% of maintenance expenditures are single-handedly caused by inverters in a 5-year operation period of a 3.5 MW PV system. These figures present the need for the reliable and fault-tolerant design of MLIs [

12].

Switch faults can manifest either as an open-circuit fault or a short-circuit fault. Open-circuit faults occur through various mechanisms such as bond-wire lift-off, gate driver failure, or internal connection rapture due to thermal or mechanical shocks [

13]. This work investigates the same. Researchers in this regard have made significant efforts. Reducing electrical or thermal stress can decrease failure probability. Including redundant states in the topology can make the post-fault operation possible. An early effort is made in [

14] on an FC topology, compromising with device count and having capacitor imbalance issues, thus increasing the cost and complexity of the structure. Adding extra legs to individual modules for modular multilevel converter (MMC) topologies is investigated in [

15], with similar consequences of increased switch count and complexity. Switches in parallel and an extra capacitor have been added in structure [

16] for fault handling capability. It adds to the circuit size, and the power loss of the converter increases. The use of a high number of DC sources for producing higher levels is also a disadvantage. A hybrid MLI with reduced device count is proposed in [

17], eliminating some of the drawbacks. However, the low-level post-fault operation leads to poor power quality, unsuitable for the majority of applications. Z-source inverter topology has been discussed with fault tolerant feature in [

18].

Likewise, a large number of switches in an MLI further leads to significant challenges in fault detection. Researchers have devised various techniques for fault detection. A work proposed in [

19] uses voltage vectors of the converter. Similarly, detection works using switching frequency component magnitude [

20], voltage pattern mass center [

21], a sliding mode observer for comparison between the actual state and simulated state [

22], and bridge voltage mean [

23] can be noted. Fault detection using output voltage mean can also be observed in [

24,

25]. The advent of artificial intelligence (AI) with powerful and low-cost microcontrollers has made the application of AI techniques ubiquitous in power electronics [

26]. Correspondingly, AI techniques have seen significant use in fault detection [

27,

28,

29]. Although fault detection in CHB-MLIs has been investigated in multiple works [

24,

29,

30,

31,

32], few works have focused on reduced device count topologies.

On account of the above, this paper proposes a reduced device count asymmetric multilevel inverter topology capable of producing 11 levels under healthy operation with fault tolerance across any switch undergoing an open-circuit fault, including across multiple switches simultaneously in some cases. The proposed fault-tolerant inverter is suitable for applications with high reliability demands. One application can be in renewable energy systems in remote or rural areas, where maintenance or repair can be significantly resource-intensive or delayed. The reduced peak level or power quality can still be useful as a temporary measure until repair. Another application where fault tolerance is crucial is vehicles onboard power electronics, where in the case of a fault, reduced power is still useful to function for a long enough duration to get the vehicle to a safe location. Post-fault modulation reconfiguration and use of redundant switches is used to handle switch open-circuit faults in this work. The healthy, under fault and post-fault conditions are examined and validated through simulation results. Moreover, a fault detection strategy based on artificial intelligence techniques is also presented, which can localize a fault under varying load and modulation index conditions. After fault mitigation, continued operation with an acceptable quality waveform on the output can be performed.

2. Proposed Structure

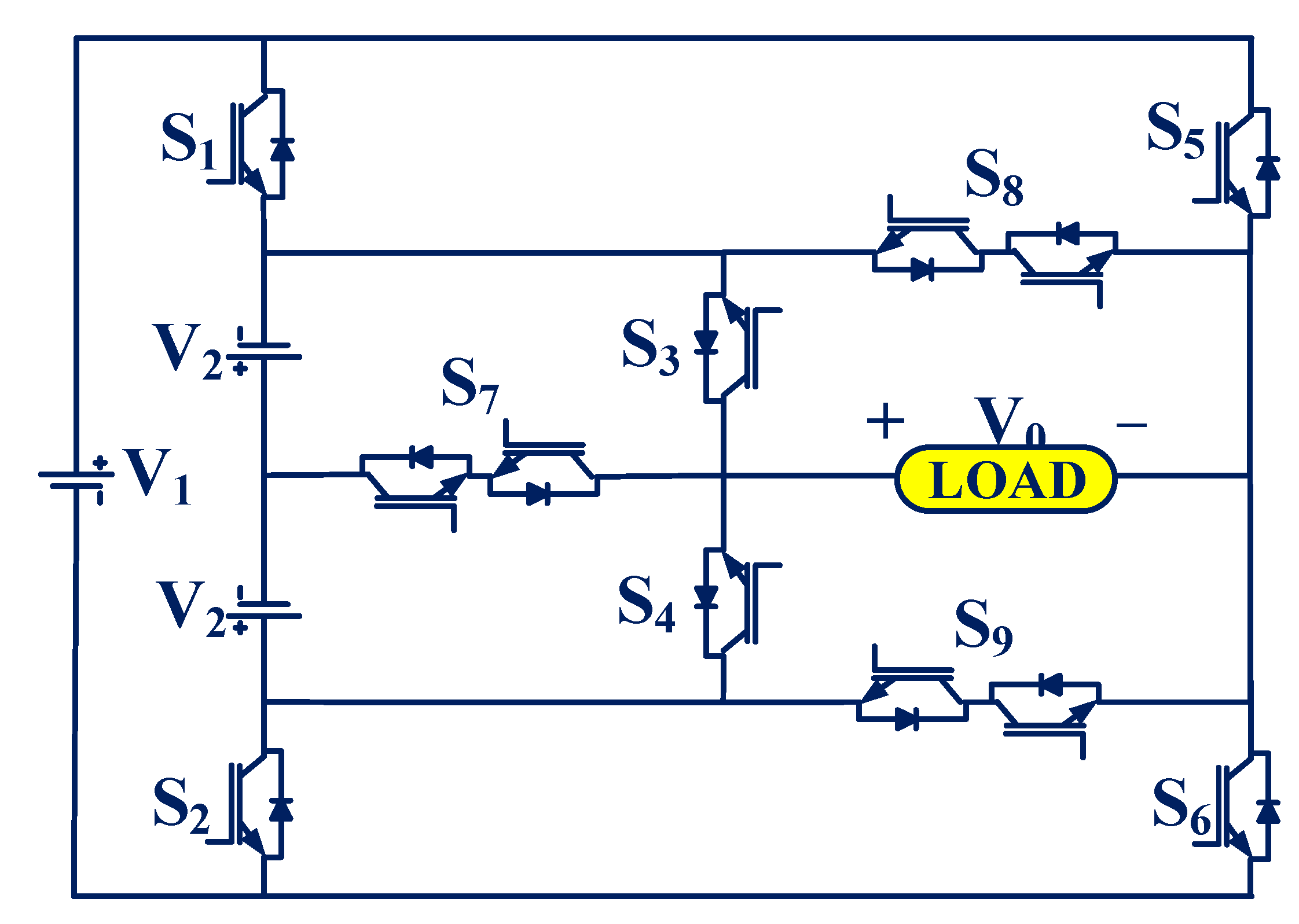

The proposed 11-level topology is depicted in

Figure 1. Observably, the structure comprises six unidirectional switches and three bidirectional switches, requiring 12 IGBT components. A pair of bidirectional switches S

8 and S

9 are redundant, with these switches being used exclusively under faulty states. The structure utilizes three DC sources with per unit magnitudes of 0.5, 1, and 1, respectively. The structure can generate an 11-level output voltage waveform, with five levels each of positive and negative polarity, respectively, and a zero level. The switching strategy under healthy operation is described in

Table 1, and the corresponding conduction diagram is presented in

Figure 2. The ratio of the magnitude of the dc sources is as V

2 = V

dc and V

1 = 0.5V

dc. The total standing voltage (TSV) of the structure is 20V

dc, with the per-unit TSV having a magnitude of 20/2.5 = 8V

dc.

5. Comparative Analysis

In this section, the proposed topology is assessed competitively concerning fault-tolerant MLIs mentioned the in recent literature. Multiple parameters for assessment include the number of DC sources, power semiconductor switches, and levels generated. The comparison can be visualized using

Table 4. The proposed topology shows advantages in terms of per-unit level device utilization and component requirements with the additional benefit of improved reliability. The literature works compared with the proposed topology include [

16,

17,

18,

37,

38,

39,

40,

41]. While the DC source requirement in [

18,

39] are same as the proposed topology, still they can produce only seven level output voltage. The topologies presented in [

17,

38,

40,

41] utilizes two DC sources, but they can only produce a maximum level of 5, 5, 7, and 9 respctively. Moreover, although the switch requirement in [

17,

37,

38,

39,

40] is less compared to proposed topology, the ouptut voltage levels generated are also quite a bit lower. Comparison with a CHB topology with DC sources ±V

dc, ±2V

dc, ±2V

dc is also included. The CHB topology exhibits only partial fault tolerance in terms of post-fault peak level availability and reduced performance in case of faults in multiple switches while requiring 12 active IGBTs compared to 8, as in the case of the proposed topology. Consider a three-CHB with DC sources ±Vdc, ±2V

dc, ±2V

dc. The proposed topology can continue to produce a five-level output of 0, ±2V

dc, ±4V

dc in the event of both S

1-S

2, both S

5-S

6, and even all four S

1, S

2, S

5, and S

6 simultaneous failure by employing the redundant switches S

8 and S

9, while the loss of four switches will catastrophically affect the performance of the CHB inverter. Moreover, only eight IGBTs are active in the proposed topology during healthy conditions, and the other four are redundant, which results in higher reliability than the three-CHB inverter comprising 12 active IGBTs.

Table 4.

Comparative assessment.

Table 4.

Comparative assessment.

| Topology | No. of Dc Sources | No. of Capacitors | No. of Power Diodes | No. of Switches | Fault Tolerant/Reliable | No. of Levels |

|---|

| Binary CHB (1-2-2) | 3 | 0 | 0 | 12 | YES (partial) | 11 |

| [16] | 4 | 0 | 0 | 20 | YES | 5 |

| [17] | 2 | 0 | 2 | 8 | YES | 5 |

| [37] | 1 | 2 | 2 | 8 | YES | 5 |

| [38] | 2 | 0 | 0 | 8 | YES | 5 |

| [18] | 3 | 0 | 0 | 12 | YES | 7 |

| [39] | 3 | 0 | 0 | 10 | YES | 7 |

| [40] | 2 | 2 | 0 | 9 | YES | 7 |

| [41] | 2 | 1 | 0 | 12 | YES | 9 |

| Proposed | 3 | 0 | 0 | 12 | YES | 11 |

6. Fault Detection

The proposed fault detection technique involves the acquisition of the mean load voltage and Root Mean Square (RMS) load voltage supplied by the MLI. The detection problem is a Multiclass Classification problem in machine learning, with fault location as the output and mean and RMS voltages as inputs. Various supervised learning classification algorithms have been developed, namely expert systems, linear regression, artificial neural networks (ANNs), a support vector machine (SVM), k-nearest neighbour (KNN), fuzzy logic, and decision trees (DTs). This work implements a decision tree model for the classification problem. DTs are one of the most versatile and popular models which can perform both classification and regression. A decision tree is in the structure of a tree, where each feature is represented as a node. A decision rule is represented as a branch (link), and each leaf classifies the output. The structure of a DT is depicted in

Figure 9. The basic principle involves asking a series of true/false questions or decisions. Data are further categorized across every step. Each branch corresponds to a result of the test. Each leaf node assigns a classification of the output. DTs often mimic the human thinking flow, making them simple to understand and they help one in interpreting the implications of the data. The three steps performed are dataset preparation, training, and testing.

Assuming training vectors

with a label vector

, the functioning of a decision tree involves recursively partitioning the features such that identically labelled or similar target outputs are aggregated together. Consider the data composed of

Nm samples at node m and symbolised by

Qm. A split

with

j and

tm as the feature and partition, respectively, partitions the data into the subsets

) and

).

The obtained candidate split is verified by its quality using a loss function

H(),

The impurity minimisation is performed by the following parameter:

Recursion is performed for the subsets

and

until the maximum allowable depth is achieved that is

or

. For a classification application implementing 0…(

K − 1) outputs for node m, assume that the proportions of class

k outputs in node

m given by

Then, the loss function corresponding to the Gini classification index is given by

6.1. Dataset Preparation

The mean and RMS values are acquired and are used as input to the model. Multiple inputs are obtained by varying the DC source voltages by 0%, ±1%, ±2%, ±5%, and ±10% to account for variations in load and dynamic behavior. Moreover, the above procedure is repeated for modulation indexes of 1, 0.9, 0.8, 0.7, 0.6, and 0.5. Distinct values across these parameters are obtained for fault in all seven switches and healthy operation. This gives a total of 432 input datasets, of which 75% are used for training the model. Selected sample datasets are displayed in

Table 5 for S

3 fault conditions. A plot of the total dataset obtained is shown in

Figure 10. Classification 1 to 7 is used for respective faults in switches, with ‘0′ for no fault.

6.2. Training

The training was implemented on a Colab

TM computational environment using the Python Scikit-learn library. Gini index classification was used as a metric. The importance of the features can be visualized in

Figure 11. Observably, the mean voltage is a more important feature than the RMS values. The obtained decision tree structure is shown in

Figure 12. The tree has 39 nodes and 38 branches with eight leaf nodes determining the fault location as the output.

6.3. Testing and Results

After training, testing was carried out to verify the performance of the prediction model. The Confusion matrix obtained post-training is given as:

The diagonal values are the correct predictions, and the non-diagonal elements are false positives and false negatives. As a result, the testing accuracy as a ratio of the number of correct predictions and total predictions was approximately 98.14%. An error of 1.86% is within satisfactory ranges for load and modulation index variation. Thus, the model can predict open-circuit fault locations with acceptable accuracy and low computational and hardware requirements.

The trained classification model was implemented in the MATLAB-Simulink environment for fault detection on the inverter model. The obtained simulation results are given in

Figure 13. The simulation results indicate that the fault is detected within one fundamental period.

The method can also be expanded for multiple switch faults. The advantages of the given method include the requirement of only two measured signals, mean and RMS voltage, from the inverter, thus requiring minimal additional sensor and signal processing hardware requirements. Thus, the proposed method can work with minimal cost and complexity.