A Novel Space Vector Modulation Scheme for a 10-Switch Converter

Abstract

1. Introduction

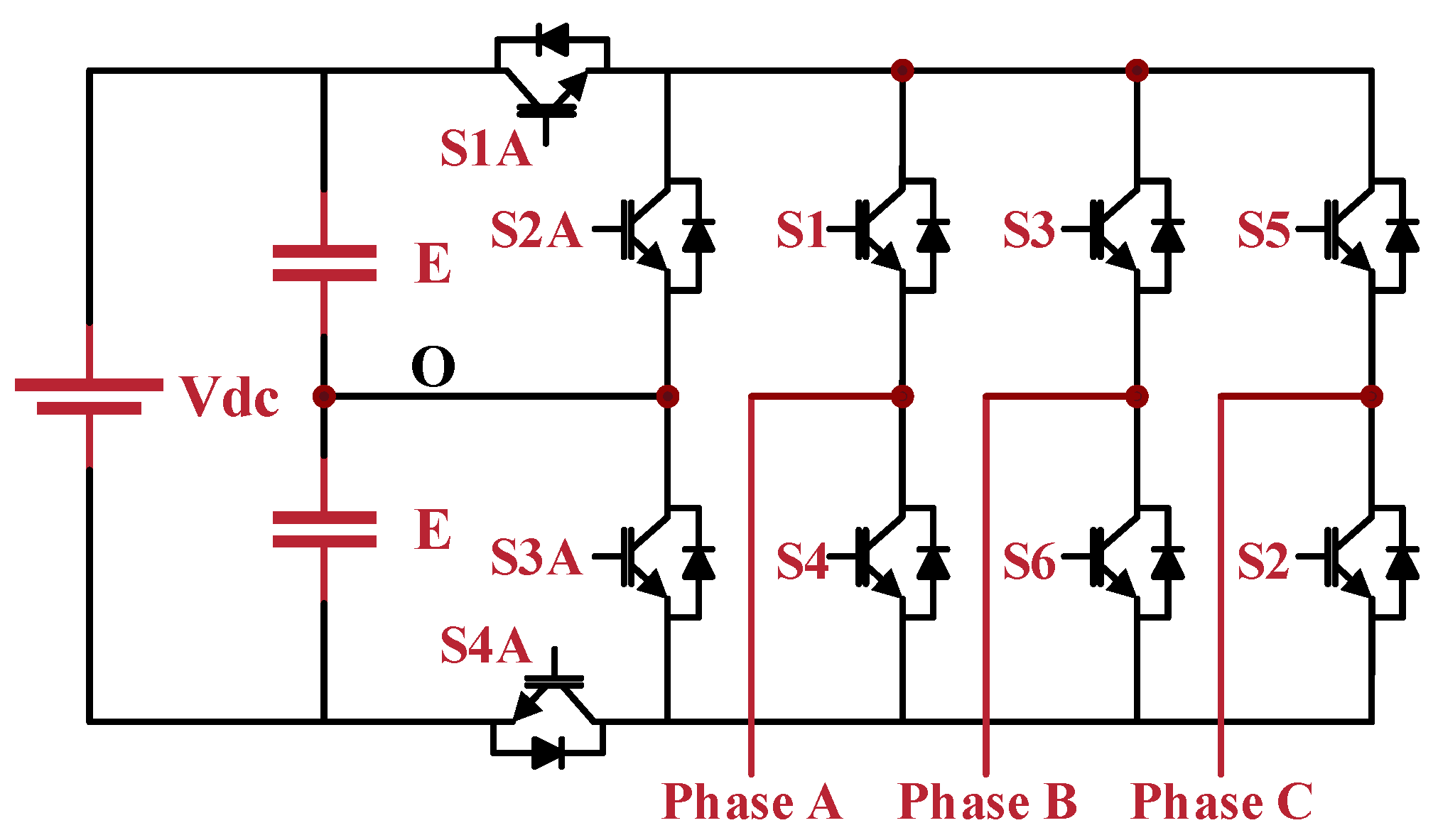

2. Characteristics of a 10-Switch Converter

2.1. Evaluation of a 10-Switch Converter Application Based on Available Challenges in Two- and Three-Level Converters

- The difference in switching loss energies between IGBTs of the same current class and adjacent voltage class is the key factor to reach low switching losses.

- The three-level converter enables substantially higher switching frequencies applying devices of the same technology and current compared to the two-level converter.

- The low on-state voltage of IGBTs has higher leverage on three-level converters compared to two-level converters which is an essential factor for calculating the conduction losses.

- Reduction of the filter size, weight and cost are possible in three-level converters due to their lower voltage harmonics.

- Reliability concerns in three-level converters can be resolved by appropriate design choices. The reduction of semiconductor losses will help to reduce the average temperature at the components and thus, decrease the failure rate.

- Application of three-level converters is economically feasible in high energy cost markets, even at low switching frequencies.

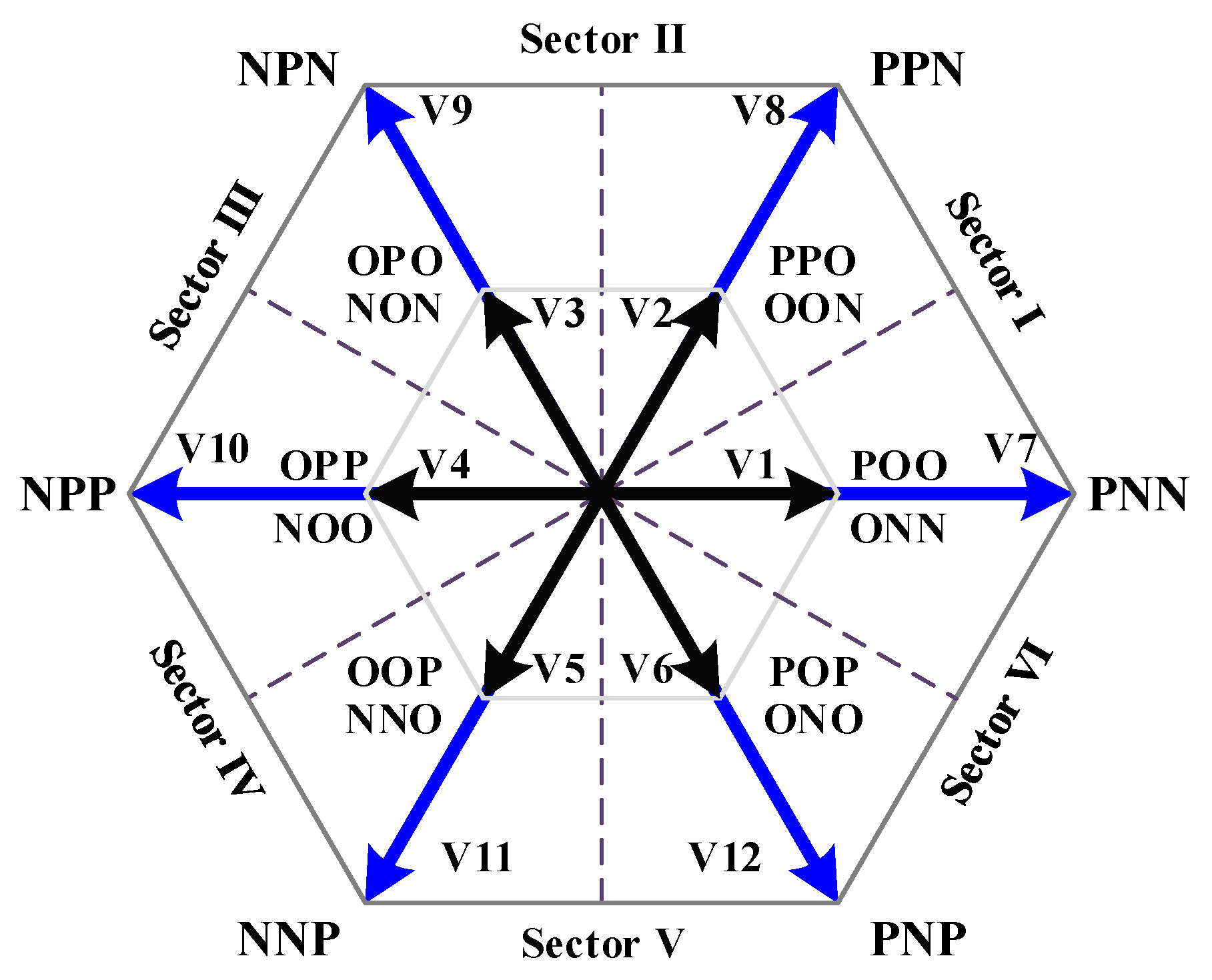

2.2. The Procedure of Feasible Modulation Methods on a 10-Switch Converter

3. Novel SVM Method for a 10-Switch Converter

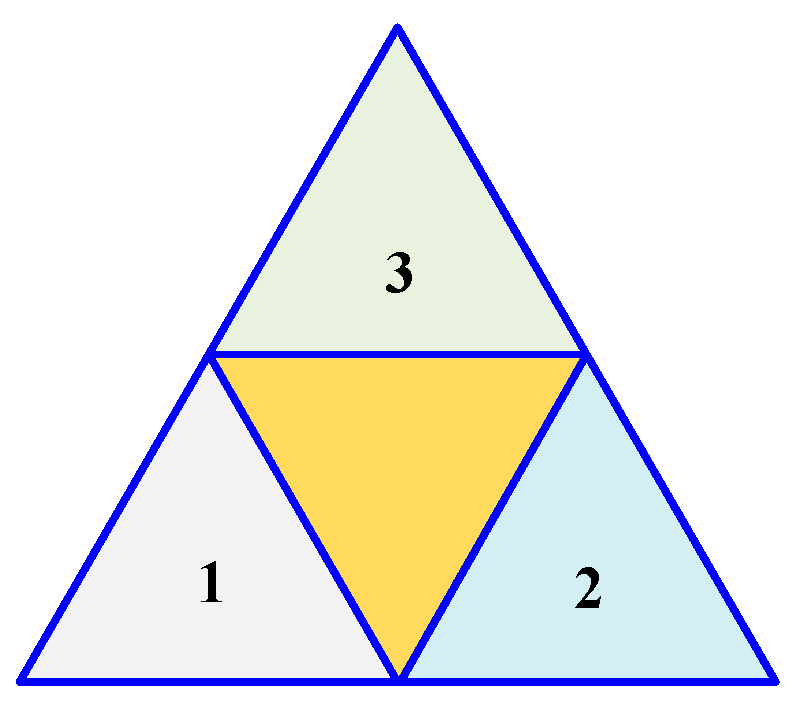

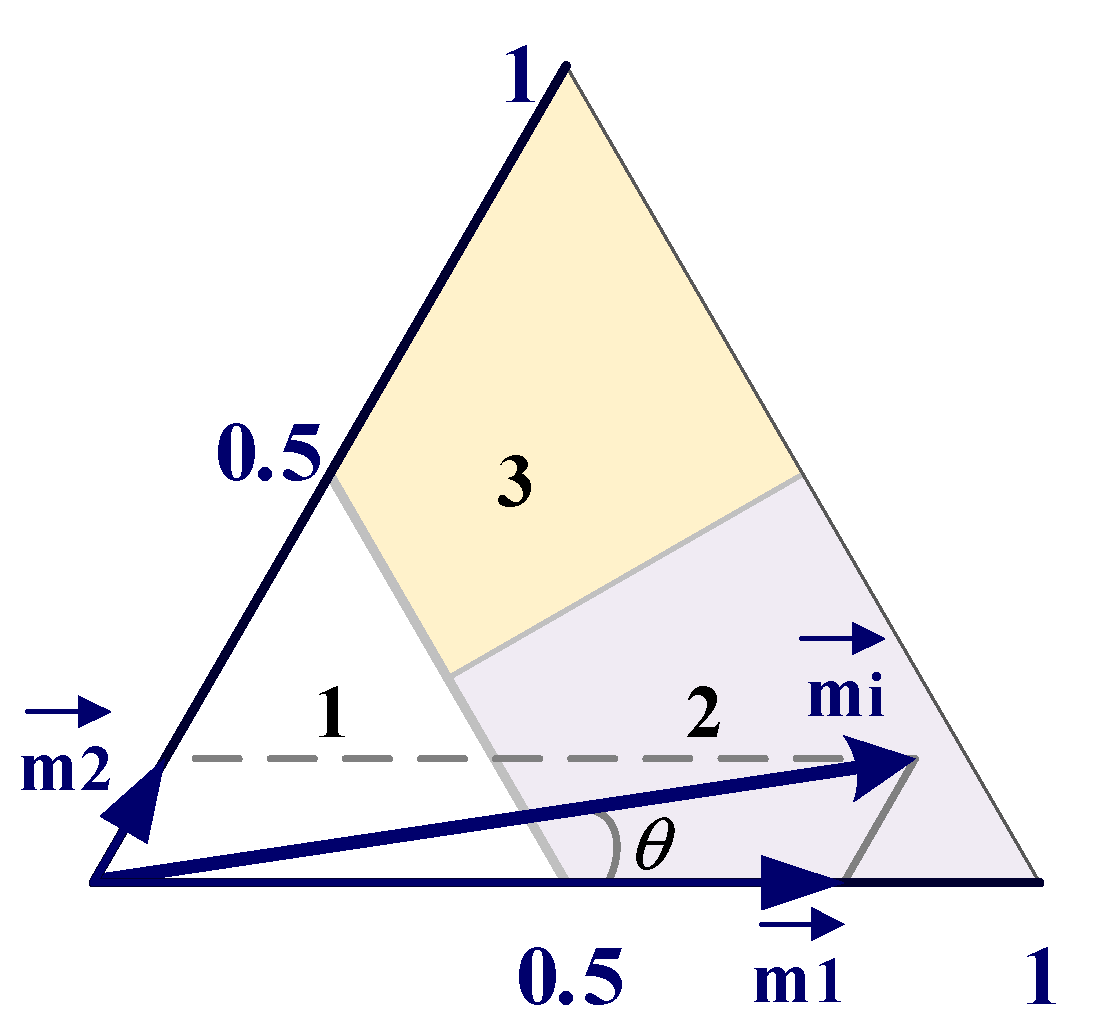

3.1. Region Determination

3.2. Voltage Vector Selection and Dwell Time Calculation

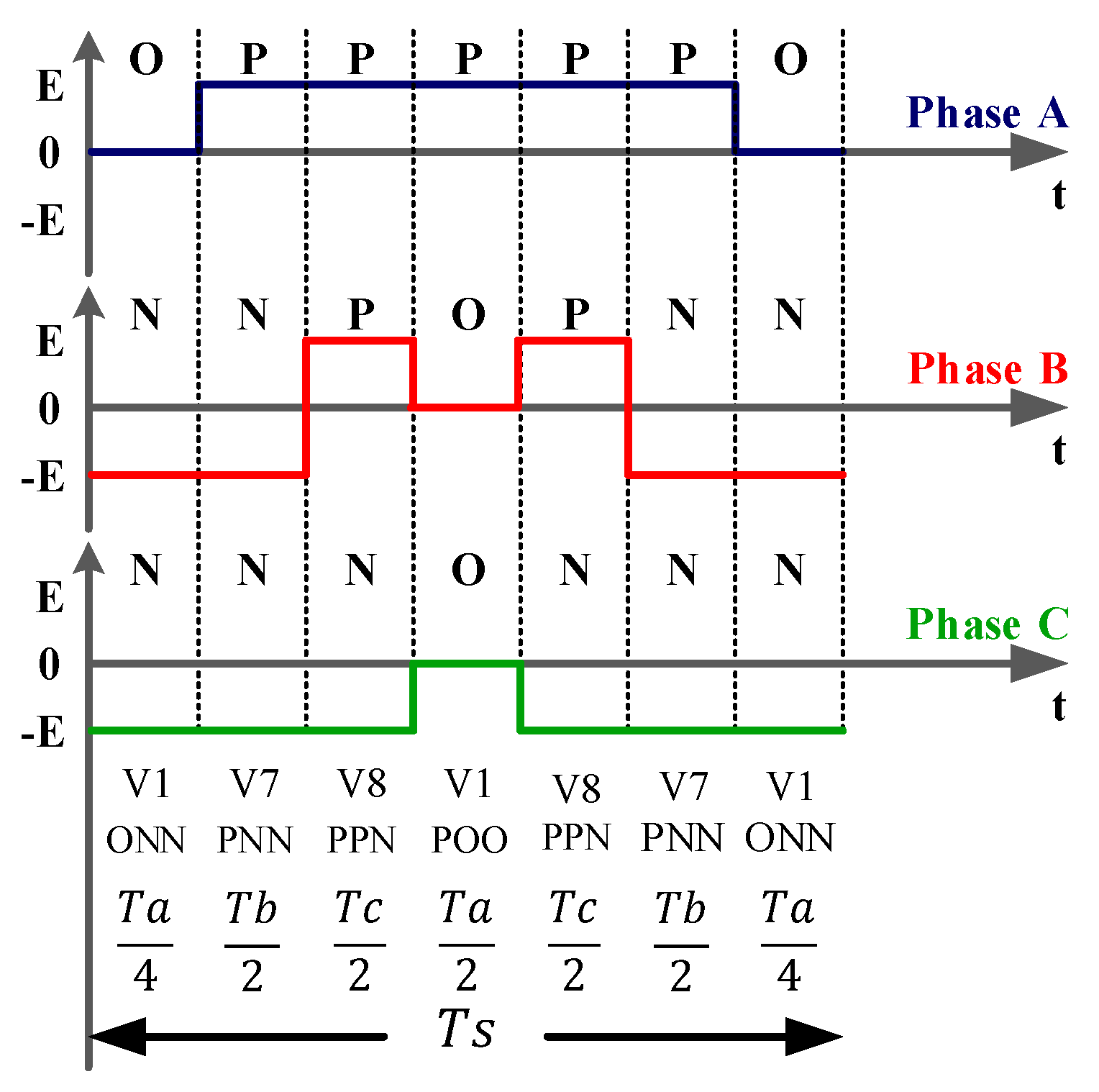

3.3. Symmetrical Switching Sequence

4. Simulation and Experimental Results

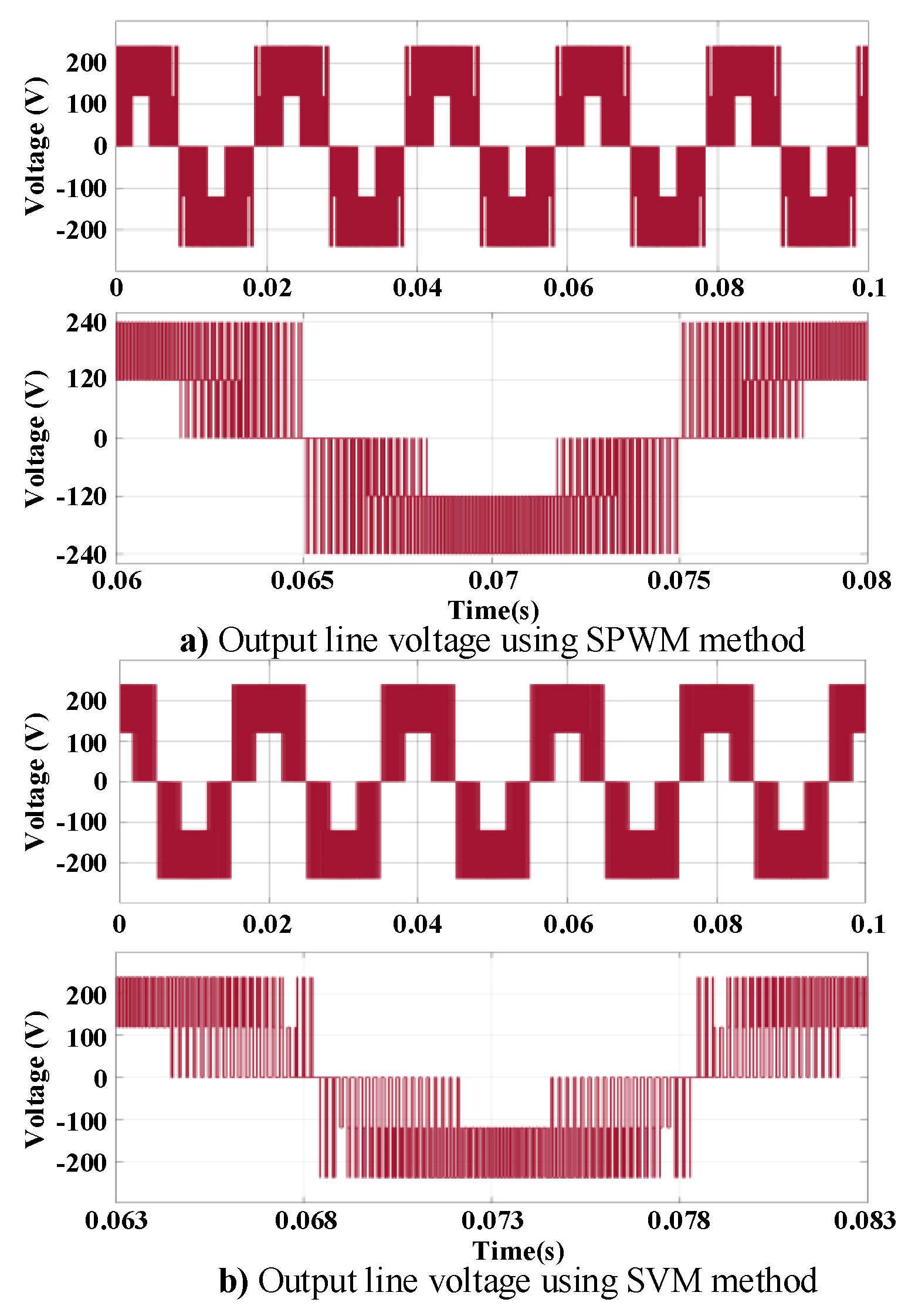

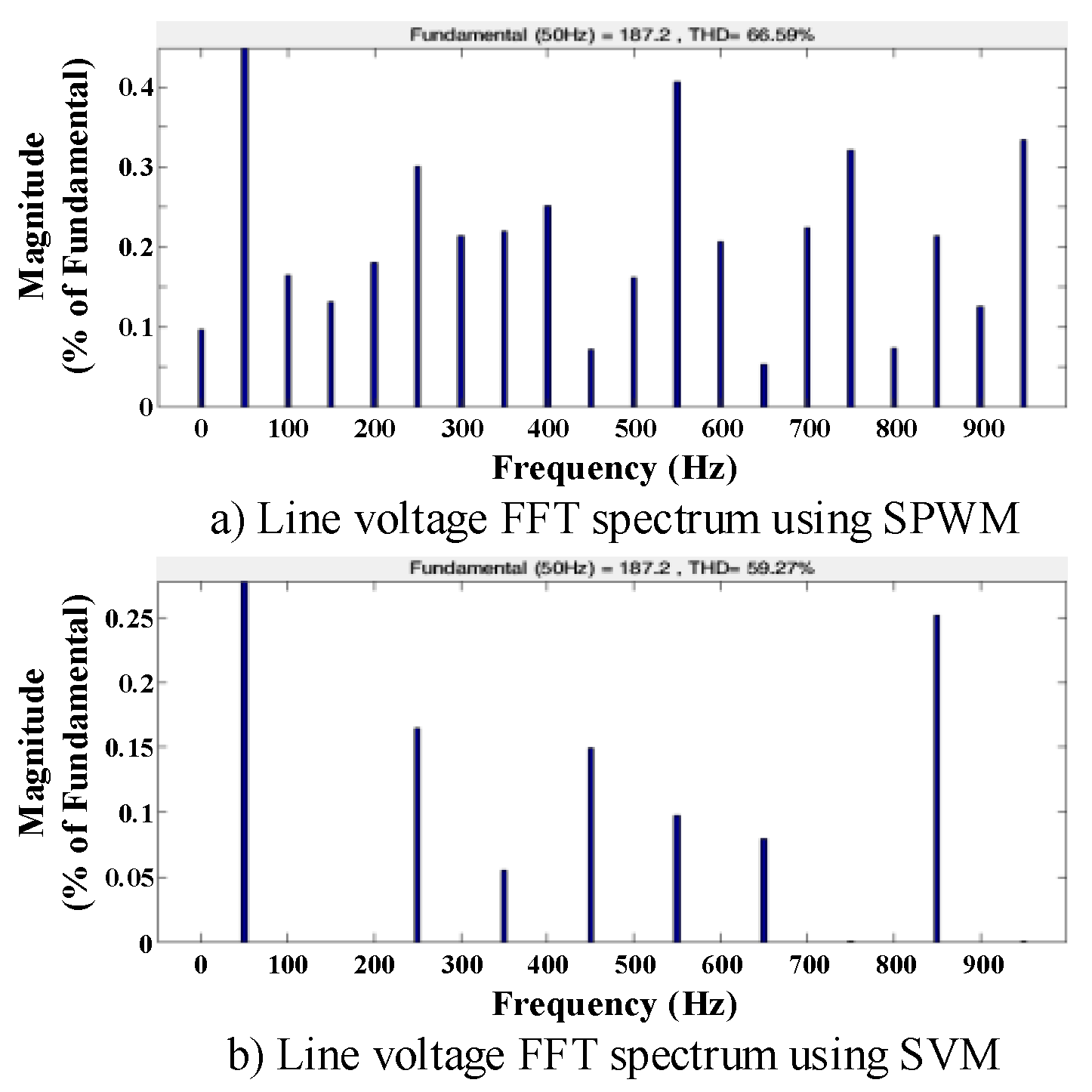

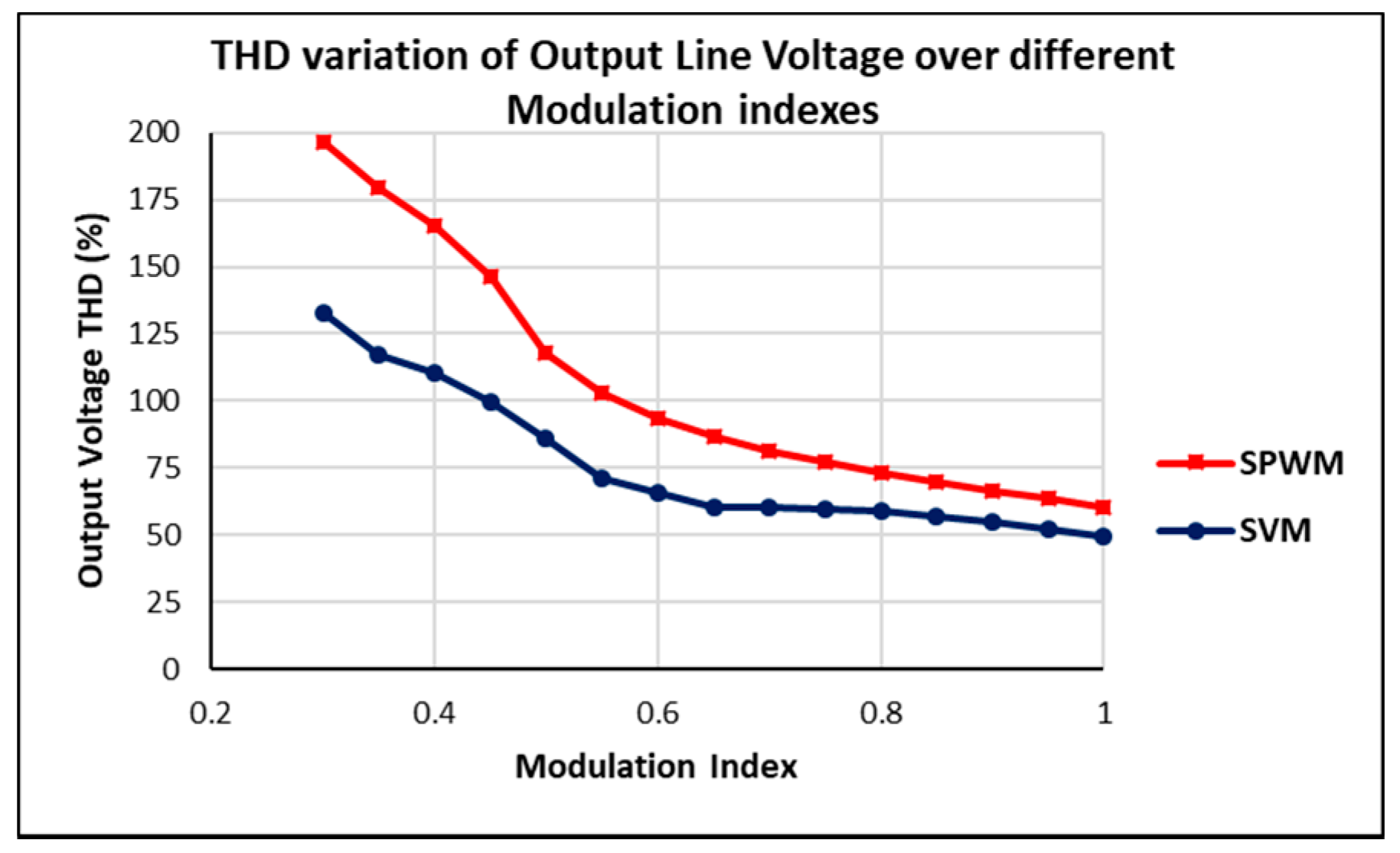

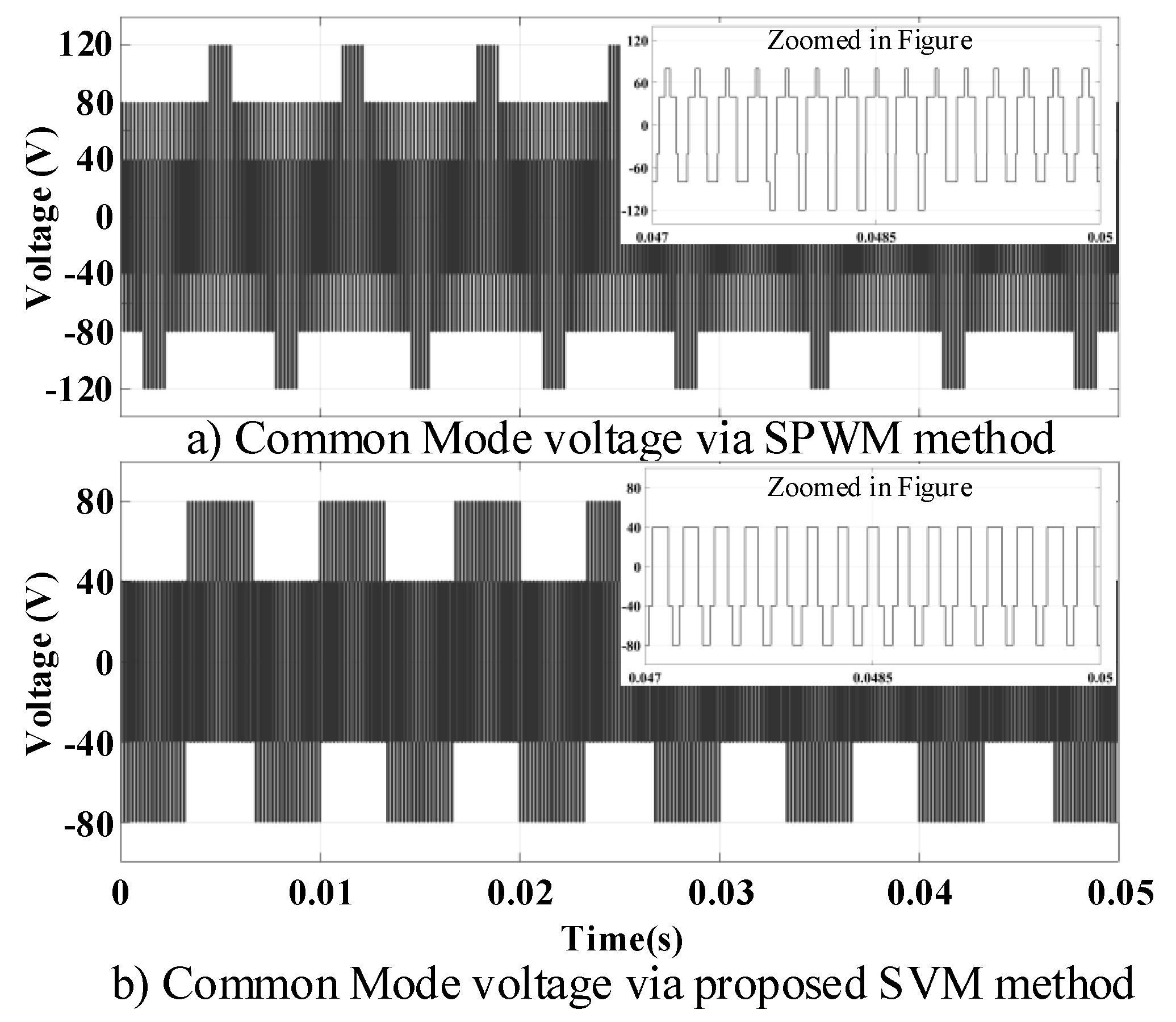

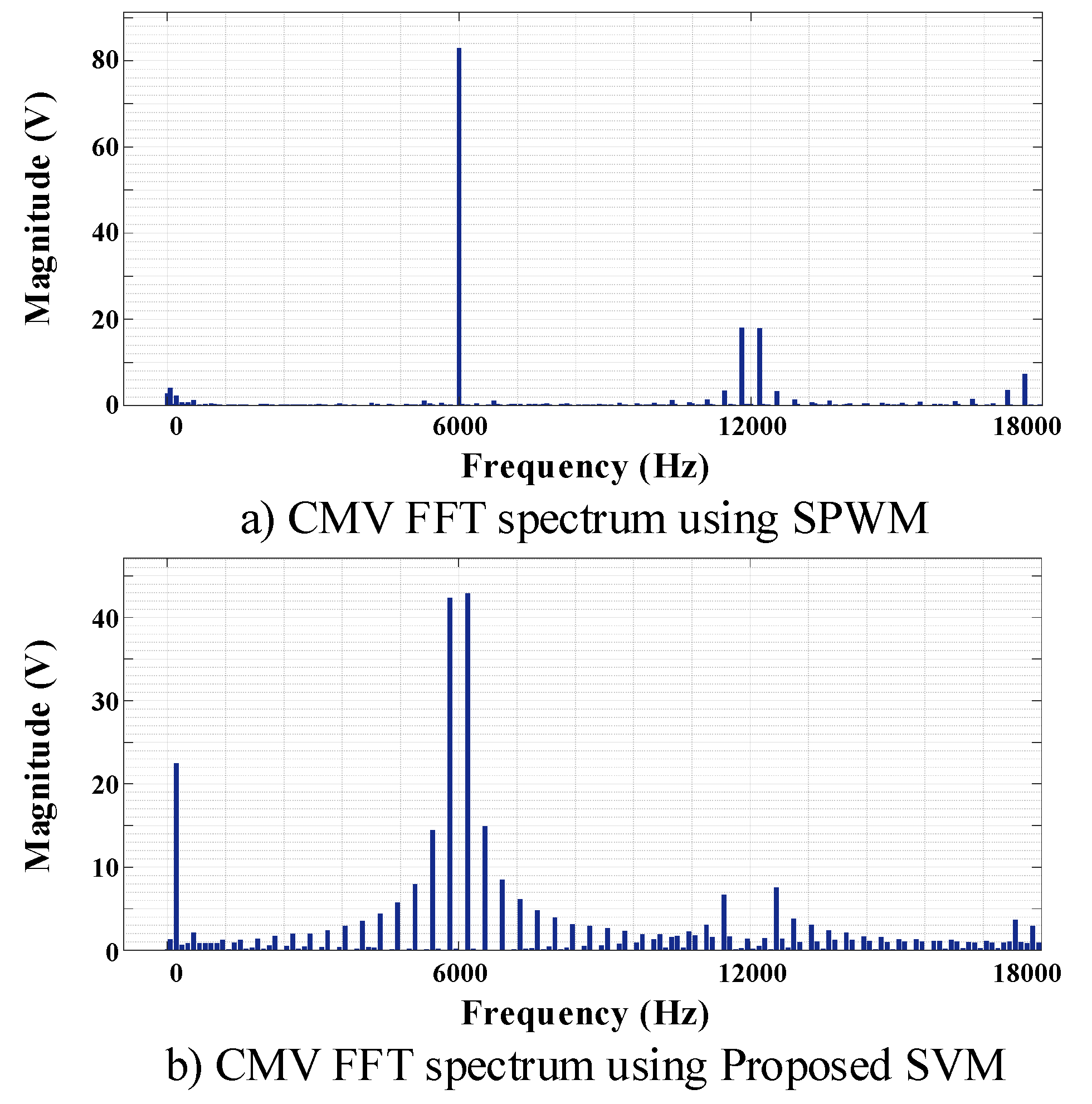

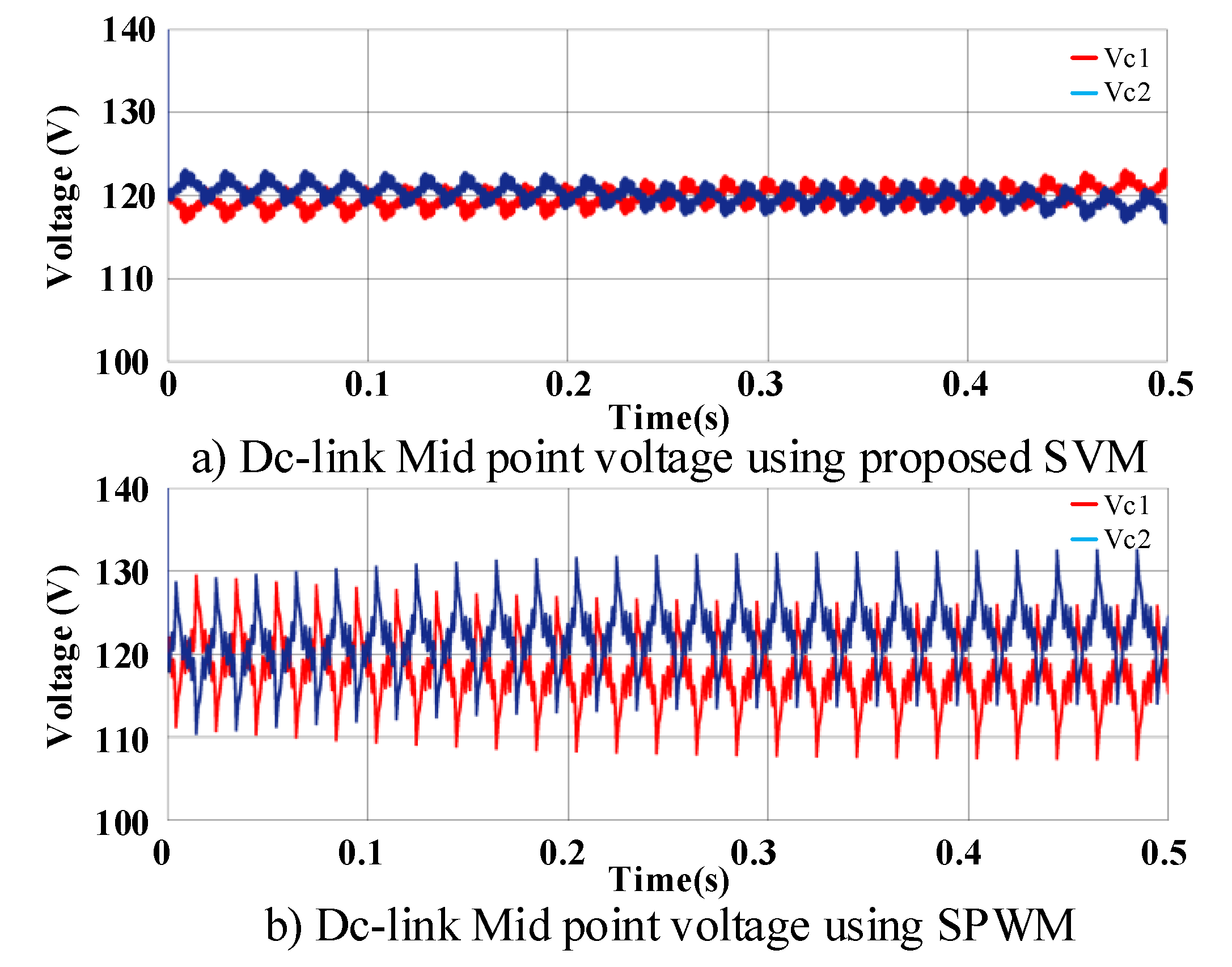

4.1. Simulation Results

4.2. Simulation in the Unbalanced AC Load Condition

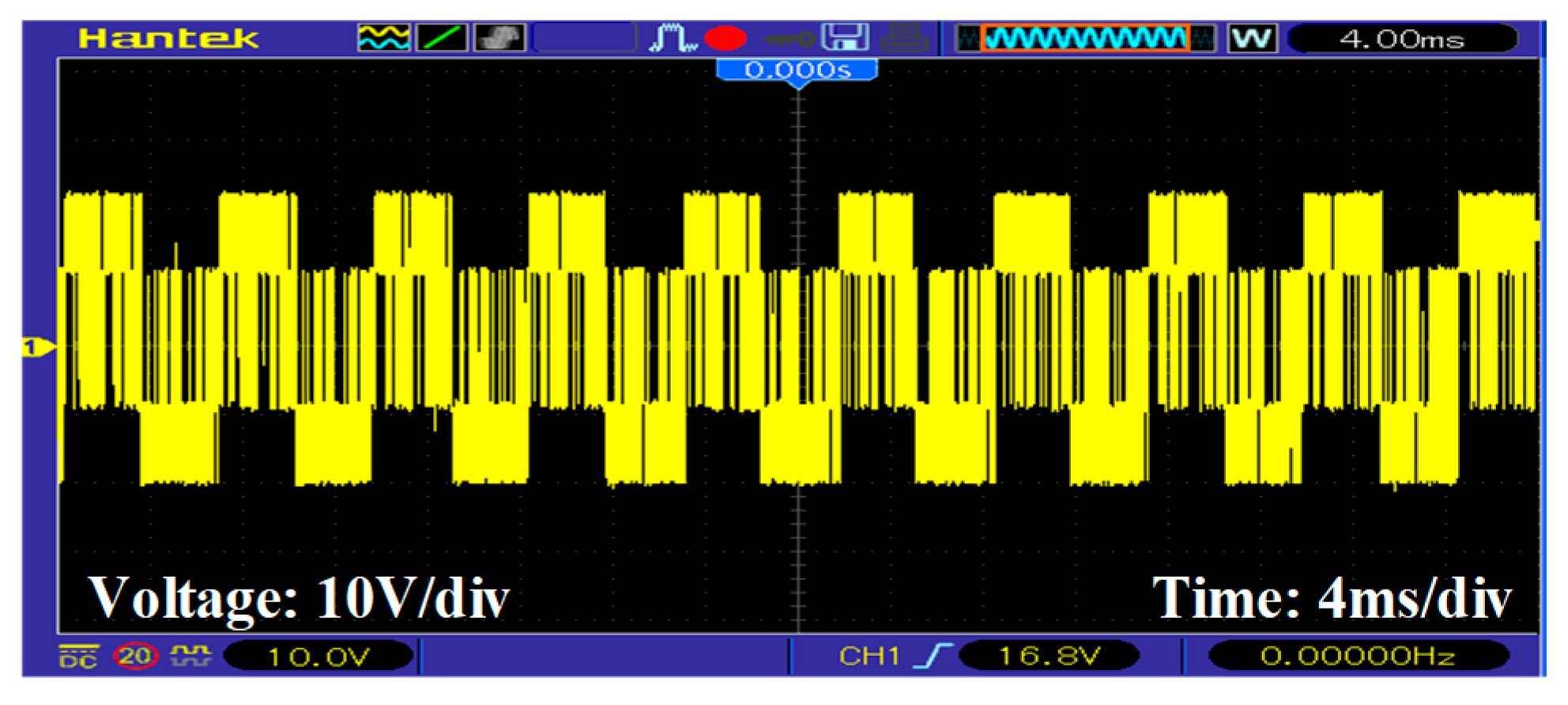

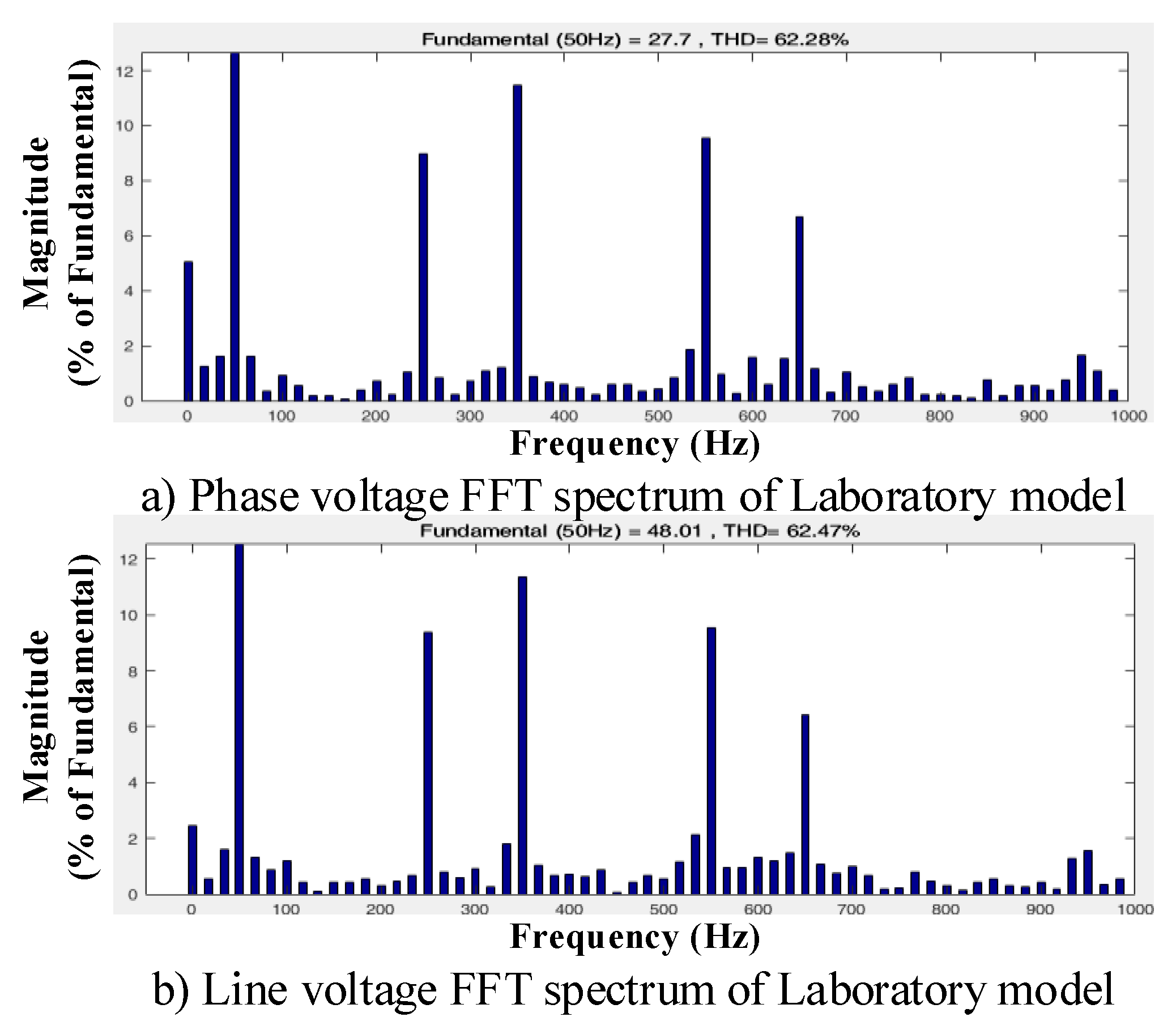

4.3. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Jagabar, J.S.; Krishnaswamy, V. An assessment of recent multilevel inverter topologies with reduced power electronics components for renewable applications. Renew. Sustain. Energy Rev. 2018, 82, 3379–3399. [Google Scholar]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E. Impedance-source networks for electric power conversion Part I: A topological review. IEEE Trans. Power Electron. 2015, 30, 699–716. [Google Scholar] [CrossRef]

- Strasser, T.; Member, S.; Andrén, F.; Kathan, J.; Cecati, C.; Buccella, C.; Member, S.; Siano, P.; Member, S.; Leitão, P.; et al. A Review of Architectures and Concepts for Intelligence in Future Electric Energy Systems. IEEE Trans. Ind. Electron. 2015, 62, 2424–2438. [Google Scholar] [CrossRef]

- Dragičević, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids—Part II: A Review of Power Architectures, Applications, and Standardization Issues. IEEE Trans. Power Electron. 2016, 31, 3528–3549. [Google Scholar] [CrossRef]

- Hasan, N.S.; Rosmin, N.; Osman, D.A.A.; Musta’amal@Jamal, A.H. Reviews on multilevel converter and modulation techniques. Renew. Sustain. Energy Rev. 2017, 80, 163–174. [Google Scholar] [CrossRef]

- Schweizer, M.; Friedli, T.; Kolar, J.W. Comparative evaluation of advanced three-phase three-level inverter/converter topologies against two-level systems. IEEE Trans. Ind. Electron. 2013, 60, 5515–5527. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel inverter topologies with reduced device count: A review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter for low-voltage applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Mihalache, L. A hybrid 2/3 level converter with minimum switch count. In Proceedings of the 2006 IEEE Industry Applications Conference Forty-First IAS Annual Meeting, Tampa, FL, USA, 8–12 October 2006; Volume 2, pp. 611–618. [Google Scholar]

- Sharifzadeh, M.; Vahedi, H.; Sheikholeslami, A.; Labbé, P.A.; Al-Haddad, K. Hybrid SHM-SHE Modulation Technique for a Four-Leg NPC Inverter With DC Capacitor Self-Voltage Balancing. IEEE Trans. Ind. Electron. 2015, 62, 4890–4899. [Google Scholar] [CrossRef]

- Muniz, J.H.G.; Da Silva, E.R.C.; Da Nobrega, R.B.; Dos Santos, E.C. An improved pulse-width-modulation for the modified hybrid 2/3-level converter. In Proceedings of the 2013 Brazilian Power Electronics Conference, Gramado, Brazil, 27–31 October 2013; pp. 248–253. [Google Scholar]

- Wu, B.; Narimani, M. High-power Converters and AC Drives; John Wiley & Sons: Hoboken, NJ, USA, 2017; Volume 59, ISBN 1119156033. [Google Scholar]

- Narendrababu, A.; Agarwal, P. Virtual Vector Modulated Hybrid 2/3-Level Z-source VSI for PV Applications. In Proceedings of the 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, USA, 25–28 June 2018; pp. 1–7. [Google Scholar]

- Rahimi, R.; Moradi, G.R.; Afshari, E.; Farhangi, B.; Farhangi, S. Study of Leakage Current Phenomena in Hybrid 2/3-Level Three-Phase Transformerless Photovoltaic Grid-Connected Inverters. In Proceedings of the 1st International Conference on New Research Achievements in Electrical and Computer Engineering (ICNRAECE), Tehran, Iran, 13 May 2016. [Google Scholar]

- Teichmann, R.; Bernet, S. A Comparison of Three-Level Converters Versus Two-Level Converters for Low-Voltage Drives, Traction, and Utility Applications. IEEE Trans. Ind. Appl. 2005, 41, 855–865. [Google Scholar] [CrossRef]

- Zhou, K.; Wang, D. Relationship between space-vector modulation and three-phase carrier-based PWM: A comprehensive analysis. IEEE Trans. Ind. Electron. 2002, 49, 186–196. [Google Scholar] [CrossRef]

- Hava, A.M.; Ün, E. Performance analysis of reduced common-mode voltage PWM methods and comparison with standard PWM methods for three-phase voltage-source inverters. IEEE Trans. Power Electron. 2009, 24, 241–252. [Google Scholar] [CrossRef]

- Najafi, P.; Hooshmand Viki, A.; Shahparasti, M. Novel space vector-based control scheme with DC-link voltage balancing capability for 10-switch converter in bipolar hybrid microgrid. Sustain. Energy Grids Netw. 2019, 20, 100256. [Google Scholar] [CrossRef]

| Switching State | ON Switches | Terminal Voltage | |

|---|---|---|---|

| P | S1A | S1 or S3 or S5 | E () |

| O | S2A | S1 or S3 or S5 | 0 |

| S3A | S2 or S4 or S6 | ||

| N | S4A | S2 or S4 or S6 | −E () |

| Vector Classification | Space Vector | Switching State | Vector Magnitude | |

|---|---|---|---|---|

| Zero Vector | V0 | PPP OOO NNN | 0 | |

| Small Vector (V1 to V6) | P-Type | N-Type | ||

| V1P | POO | |||

| V1N | ONN | |||

| Large Vector (V7 to V12) | V7 | PNN | ||

| Case | Angle (θ) | Region |

|---|---|---|

| & & | NA | 1 |

| or or | 2 | |

| 3 |

| Dwell Time Region | Ta | Tb | Tc | |||

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | ||||||

| 3 | ||||||

| Segments of Switching Sequence in Carrier-Based Modulation at the Three Intervals of Sector I. | |||||||

| Interval 1 | ONN | PNN | PPN | PPP | PPN | PNN | ONN |

| Interval 2 | ONN | PNN | PPN | PPO | PPN | PNN | ONN |

| Interval 3 | NNN | PNN | PPN | PPO | PPN | PNN | NNN |

| Segments of Switching Sequence in the Proposed SVM in Regions 2 and 3 of Sector I. | |||||||

| Region 2 | ONN | PNN | PPN | POO | PPN | PNN | ONN |

| Region 3 | PPO | PPN | PNN | OON | PNN | PPN | PPO |

| System Parameter | Value |

|---|---|

| Switching Frequency | 6 kHz |

| Total DC-link Voltage | 240 V |

| System Frequency | 50 Hz |

| Three-phase AC Load | 1.5 kW 11.506 Ω |

| Sampling Time | 2 µs |

| Modulation Index | 0.78 (SVM) 0.9 (SPWM) |

| Unbalanced Simulation Parameters | Parameter Values |

|---|---|

| Three-Phase AC Load | Phase A R = 11.506 Ω L = 5 mH |

| Phase B R = 3 Ω L = 5mh | |

| Phase C R = 11.506 Ω L = 5 mH | |

| Dc-link Capacitors | C1 = 220 µF C2 = 220 µF |

| DC Source Voltage | 240 V |

| Internal Resistance of DC source | R = 0.01 Ω |

| System Parameter | Value |

|---|---|

| IGBT Model Number | HGTG10N120BND |

| Gate Drive Optocoupler | HCPL-3120 |

| Switching Frequency | 6 kHz |

| Total DC-link Voltage | 60 V |

| System Frequency | 50 Hz |

| Three phase AC Load | 56 Ω |

| Timer Clock | 12 MHz |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Najafi, P.; Houshmand Viki, A.; Shahparasti, M.; Seyedalipour, S.S.; Pouresmaeil, E. A Novel Space Vector Modulation Scheme for a 10-Switch Converter. Energies 2020, 13, 1855. https://doi.org/10.3390/en13071855

Najafi P, Houshmand Viki A, Shahparasti M, Seyedalipour SS, Pouresmaeil E. A Novel Space Vector Modulation Scheme for a 10-Switch Converter. Energies. 2020; 13(7):1855. https://doi.org/10.3390/en13071855

Chicago/Turabian StyleNajafi, Parviz, Abbas Houshmand Viki, Mahdi Shahparasti, S. Sajjad Seyedalipour, and Edris Pouresmaeil. 2020. "A Novel Space Vector Modulation Scheme for a 10-Switch Converter" Energies 13, no. 7: 1855. https://doi.org/10.3390/en13071855

APA StyleNajafi, P., Houshmand Viki, A., Shahparasti, M., Seyedalipour, S. S., & Pouresmaeil, E. (2020). A Novel Space Vector Modulation Scheme for a 10-Switch Converter. Energies, 13(7), 1855. https://doi.org/10.3390/en13071855