Modified Impedance-Source Inverter with Continuous Input Currents and Fault-Tolerant Operations

Abstract

:1. Introduction

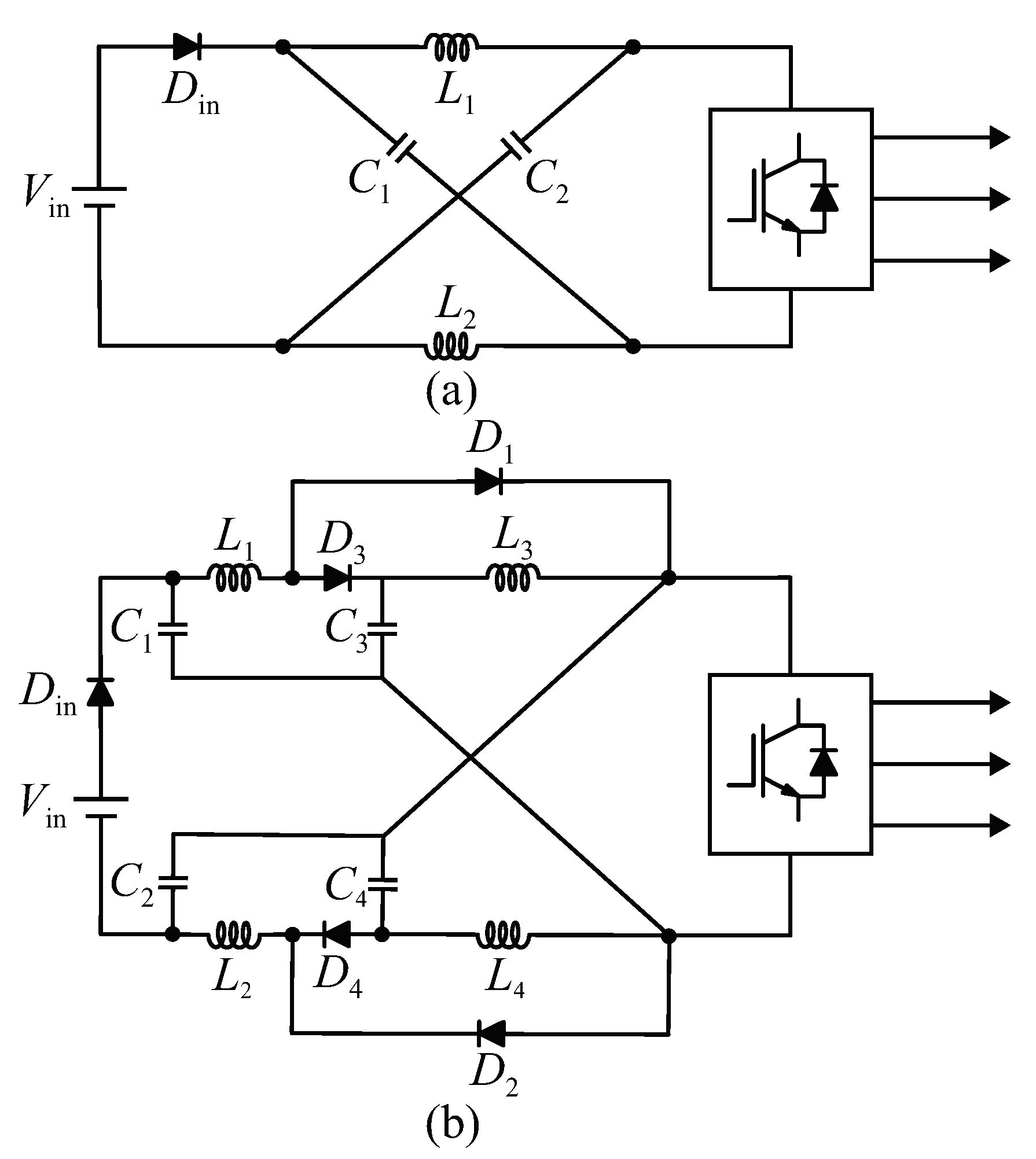

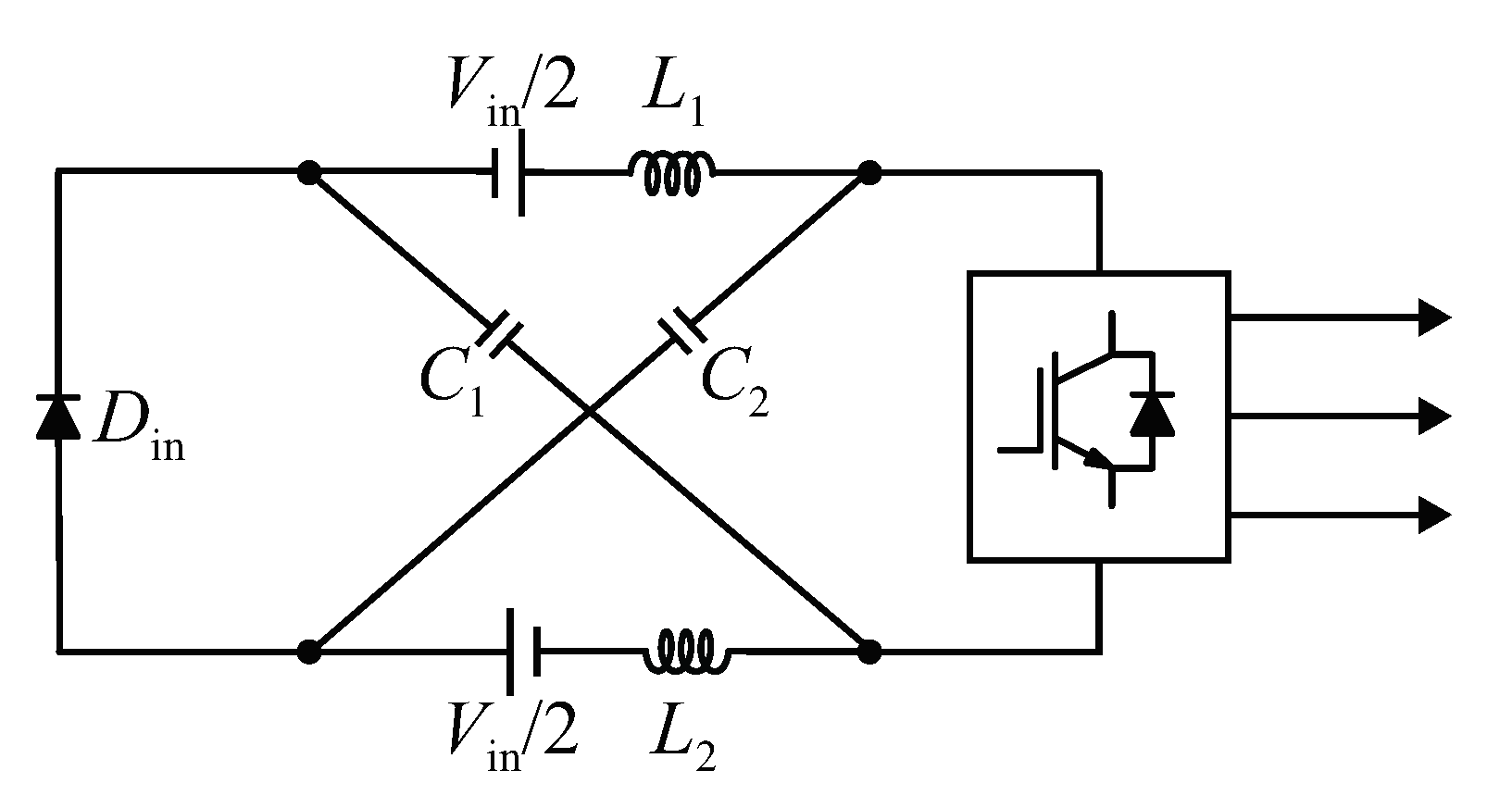

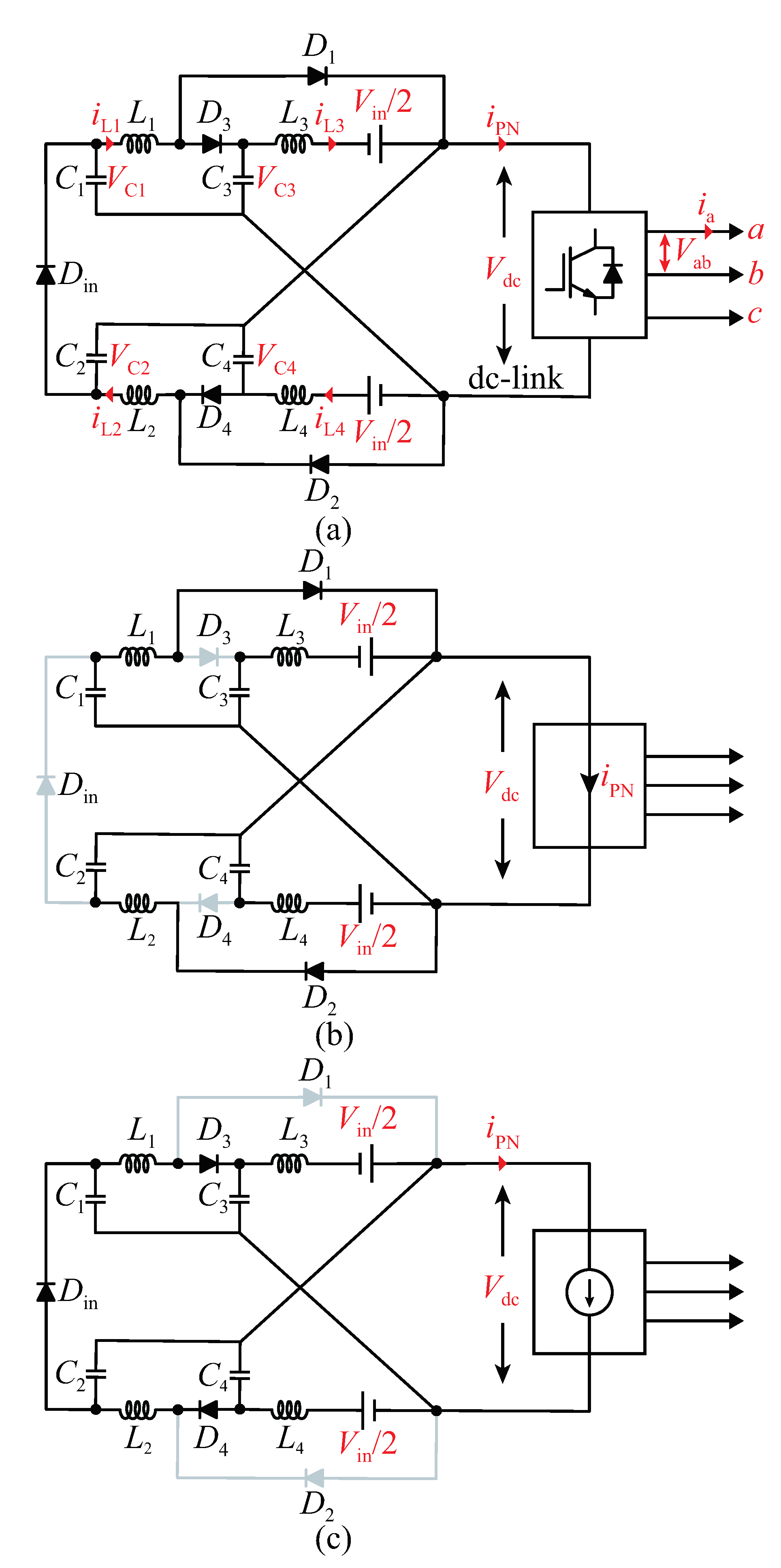

2. Proposed Embedded Enhanced-Boost Z-Source Inverter

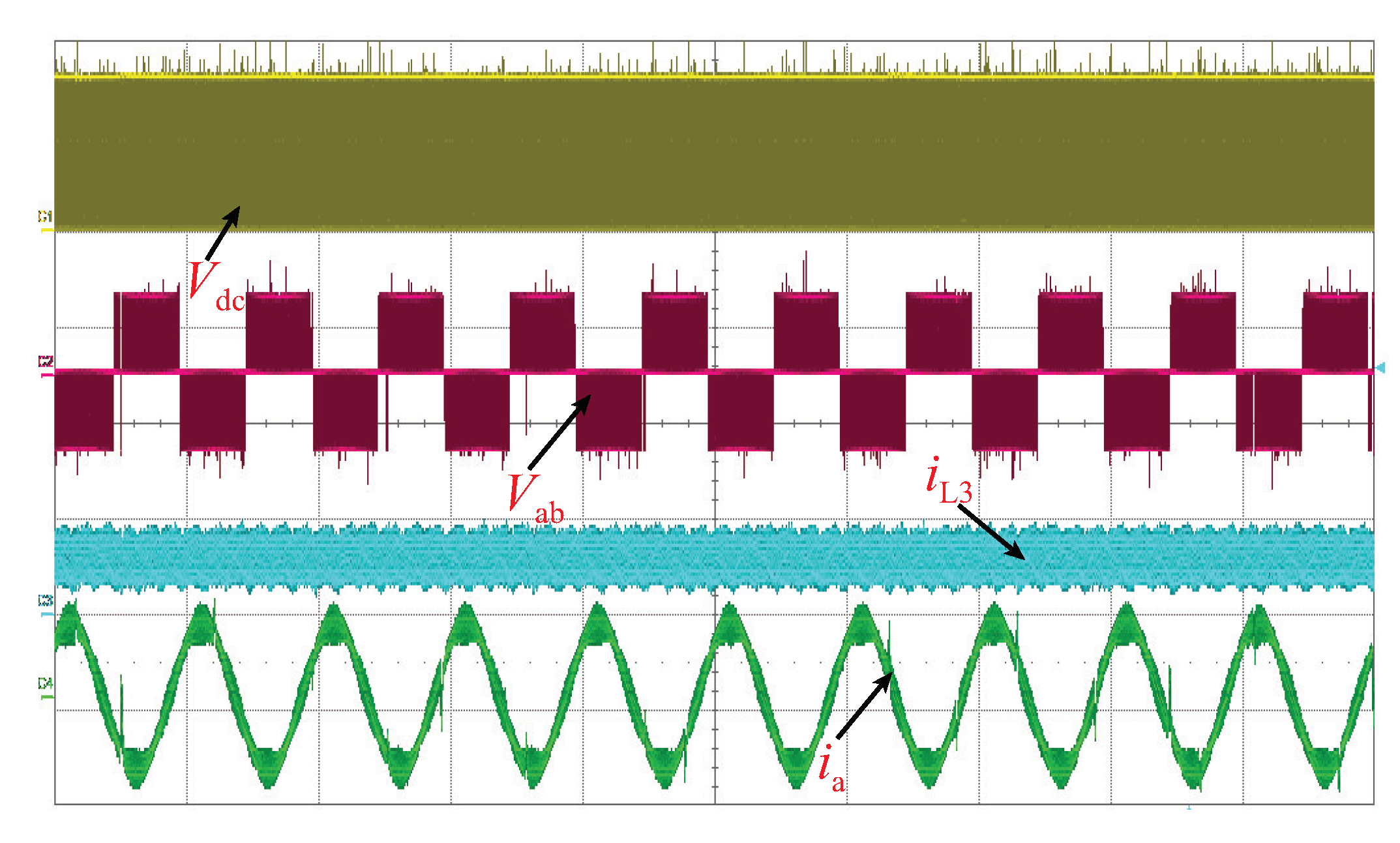

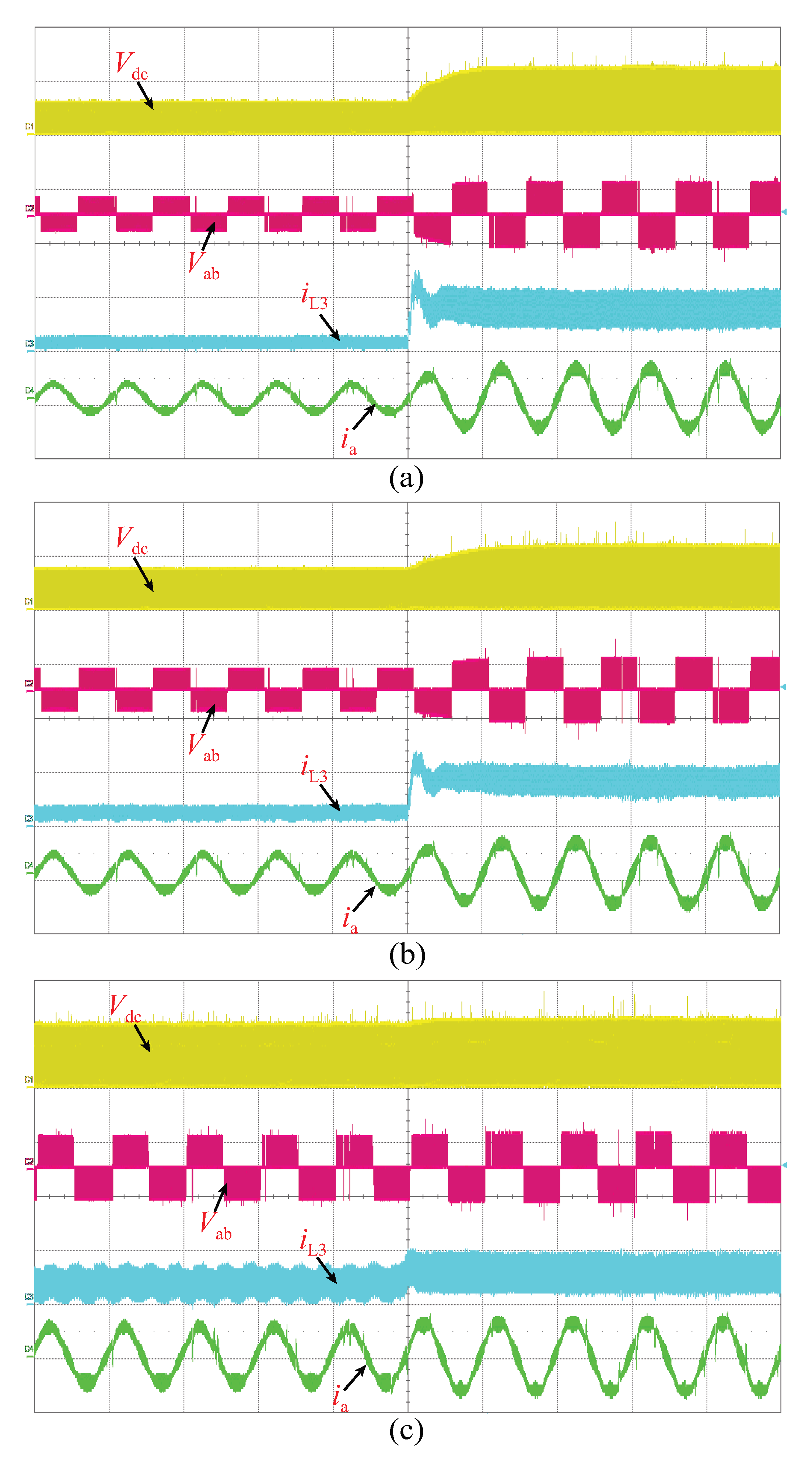

2.1. Operation Principle

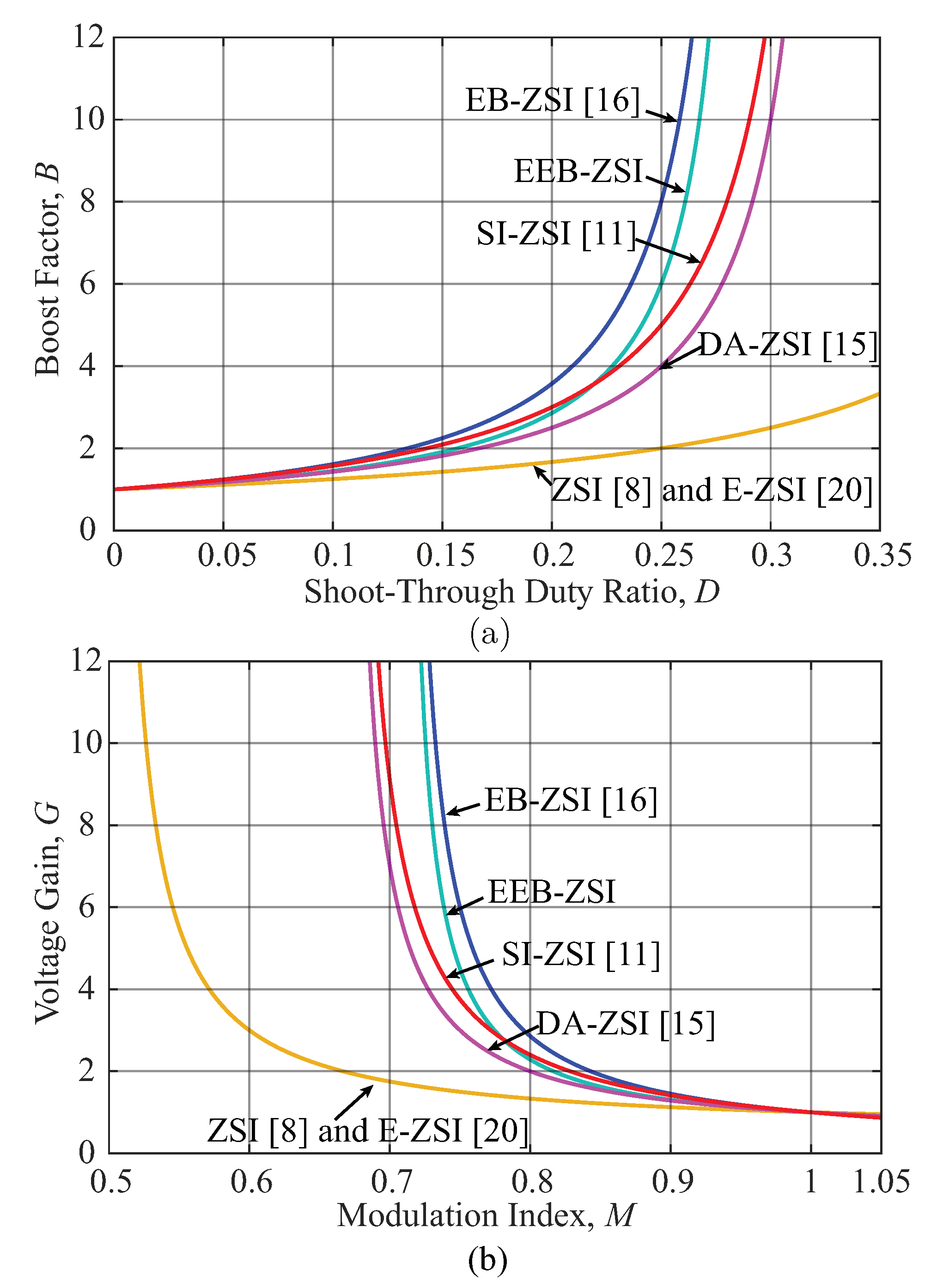

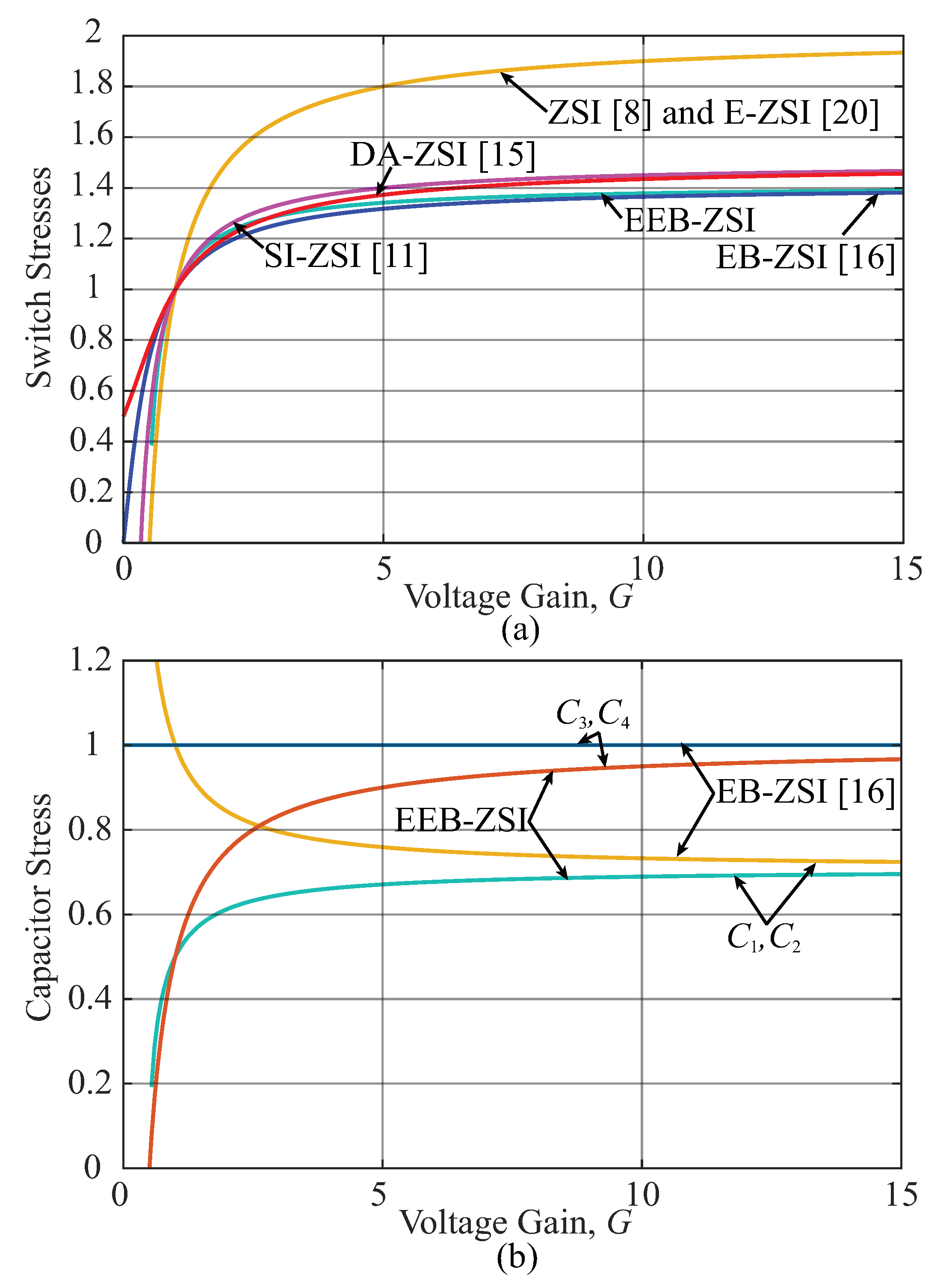

2.2. Boost Capability Comparison

2.3. Voltage Stresses Comparison

2.4. Inductor and Capacitor Design

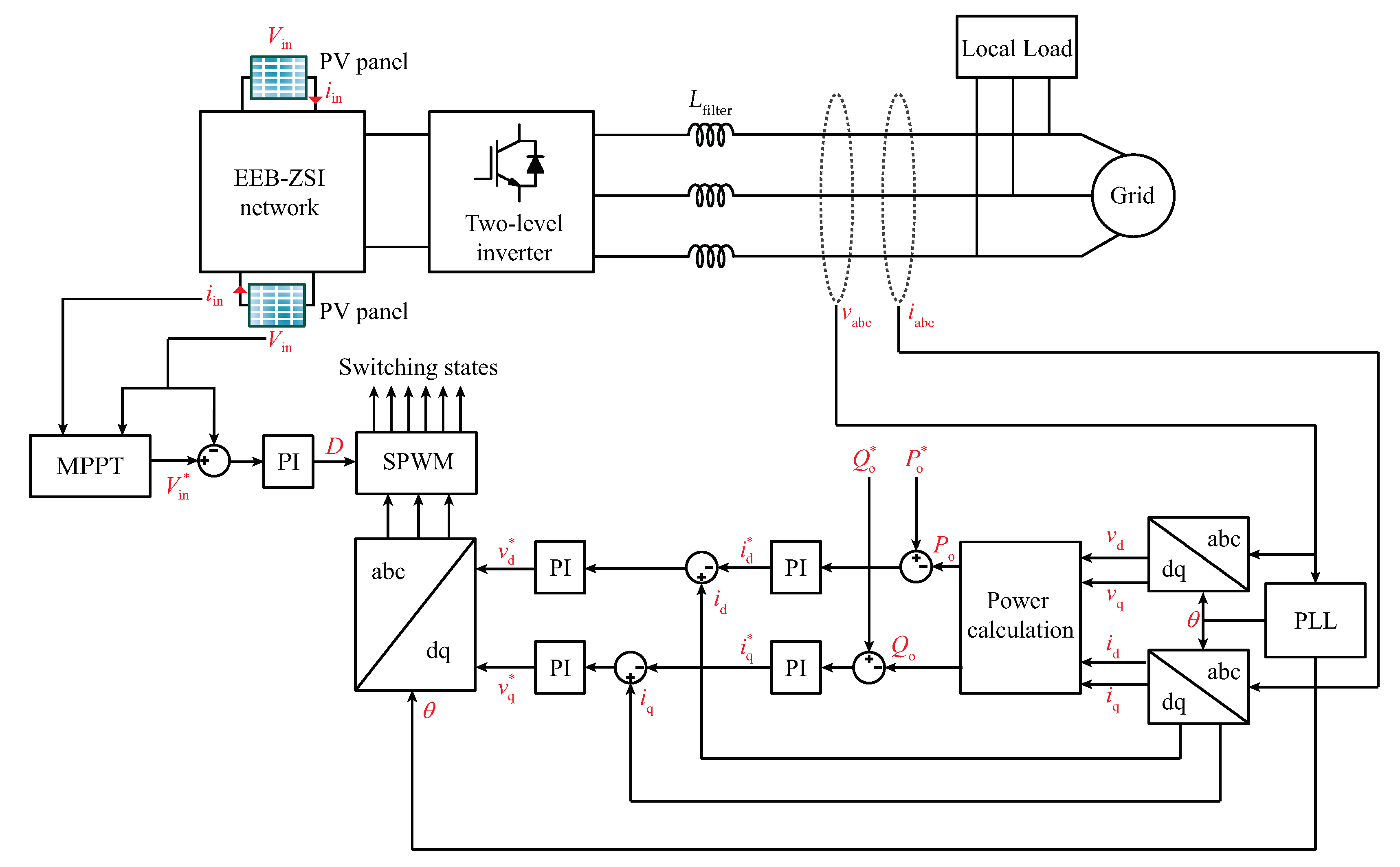

2.5. Control Method

3. Fault-Tolerant Analysis

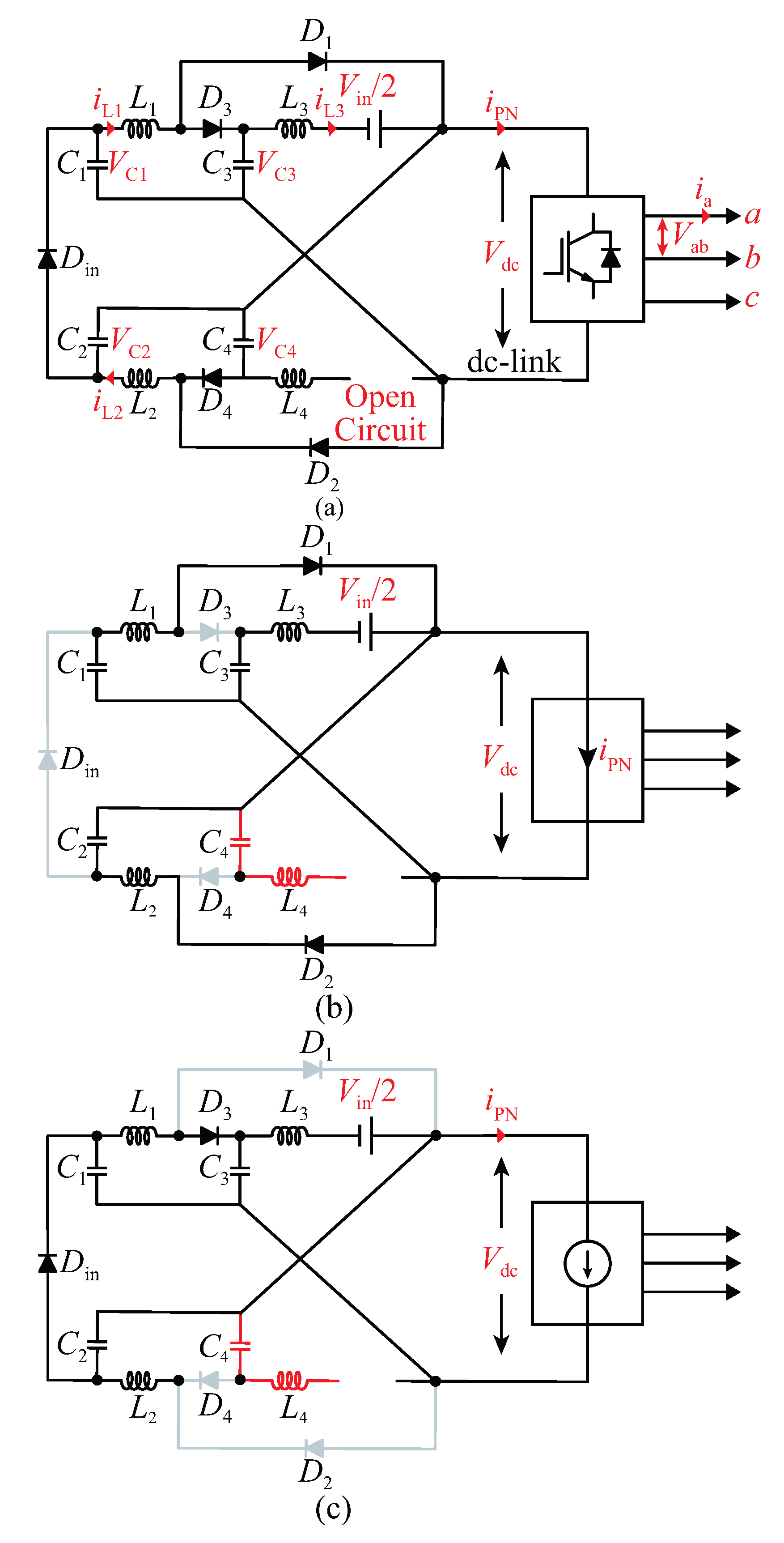

3.1. Open-Circuit Analysis

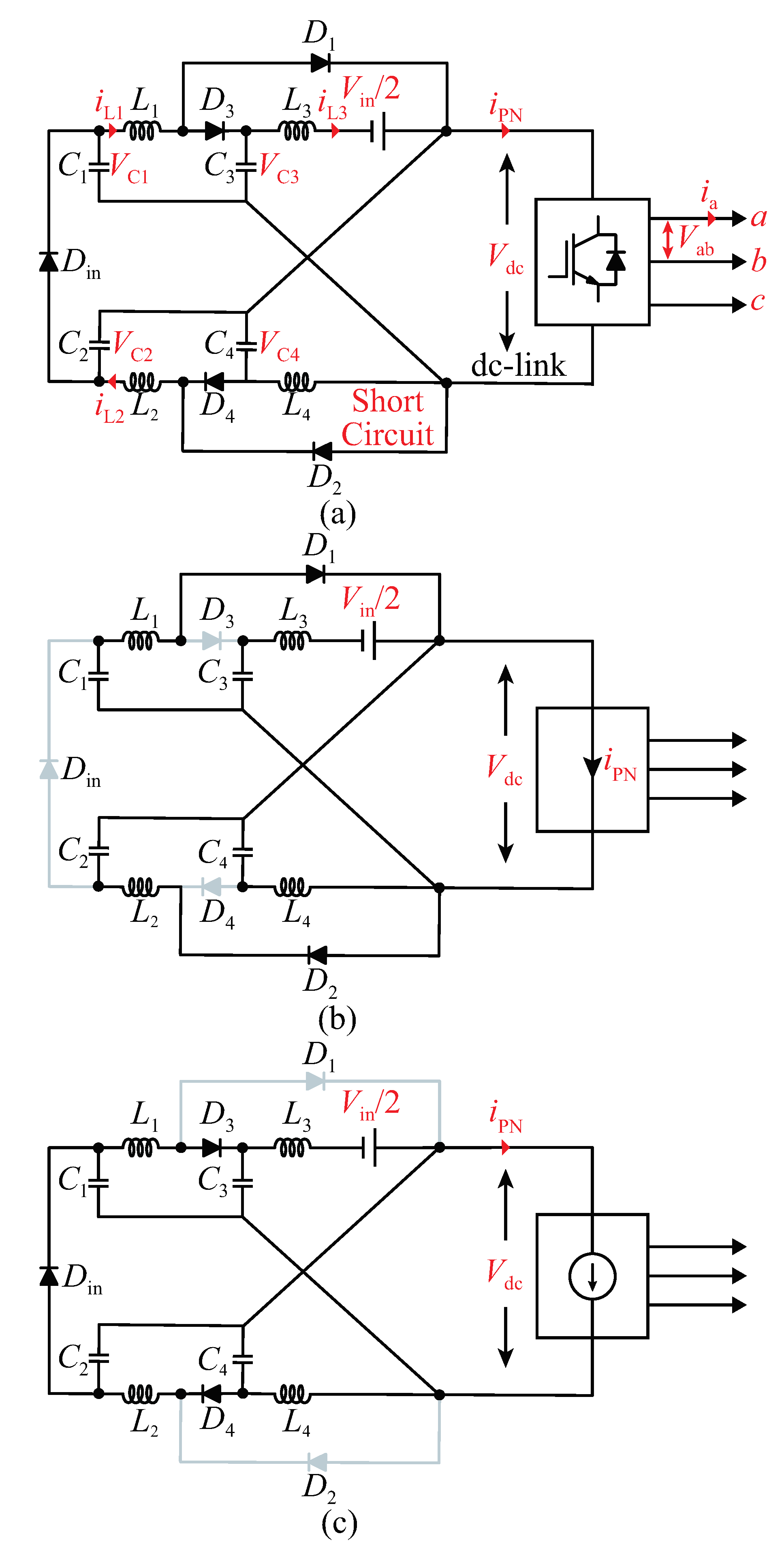

3.2. Short-Circuit Analysis

3.3. Source-Unbalance Analysis

4. Experimental Verification

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Liu, Y.; Abu-Rub, H.; Ge, B.; Blaabjerg, F.; Ellabban, O.; Loh, P.C. Impedance Source Power Electronic Converters; John Wiley & Sons: Hoboken, NJ, USA, 2016. [Google Scholar]

- Yang, Y.; Kim, K.A.; Blaabjerg, F.; Sangwongwanich, A. Advances in Grid-Connected Photovoltaic Power Conversion Systems; Woodhead Publishing: Cambridge, UK, 2018. [Google Scholar]

- Yuan, J.; Yang, Y.; Liu, P.; Shen, Y.; Qiu, Z.; Blaabjerg, F. An embedded enhanced-boost Z-source inverter. In Proceedings of the IEEE PEAC, Shenzhen, China, 4–7 November 2018; pp. 1–6. [Google Scholar]

- Yuan, J.; Yang, Y.; Blaabjerg, F. A switched quasi-Z-Source inverter with continuous input currents. Energies 2020, 13, 1390. [Google Scholar] [CrossRef] [Green Version]

- Yuan, J.; Mostaan, A.; Yang, Y.; Siwakoti, Y.P.; Blaabjerg, F. A modified Y-Source DC/DC converter with high voltage-gains and low switch stresses. IEEE Trans. Power Electron. 2020, 35, 7716–7720. [Google Scholar] [CrossRef]

- Mostaan, A.; Yuan, J.; Siwakoti, Y.P.; Esmaeili, S.; Blaabjerg, F. A trans-Inverse coupled-inductor semi-SEPIC DC/DC converter with full control range. IEEE Trans. Power Electron. 2019, 34, 10398–10402. [Google Scholar] [CrossRef]

- Singh, S.A.; Carli, G.; Azeez, N.A.; Williamson, S.S. Modeling, design, control, and implementation of a modified Z-source integrated PV/Grid/EV DC charger/inverter. IEEE Trans. Ind. Electron. 2018, 65, 5213–5220. [Google Scholar] [CrossRef]

- Peng, F.Z. Z-source inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Abdelhakim, A.; Blaabjerg, F.; Mattavelli, P. Modulation schemes of the three-phase impedance source inverters part I: Classification and review. IEEE Trans. Ind. Electron. 2018, 65, 6309–6320. [Google Scholar] [CrossRef]

- Anderson, J.; Peng, F.Z. Four quasi-Z-Source inverters. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 2743–2749. [Google Scholar]

- Zhu, M.; Yu, K.; Luo, F.L. Switched inductor Z-Source inverter. IEEE Trans. Power Electron. 2010, 25, 2150–2158. [Google Scholar]

- Li, D.; Loh, P.C.; Zhu, M.; Gao, F.; Blaabjerg, F. Generalized multicell switched-inductor and switched-capacitor Z-Source inverters. IEEE Trans. Power Electron. 2013, 28, 837–848. [Google Scholar] [CrossRef]

- Nguyen, M.; Lim, Y.; Cho, G. Switched-inductor quasi-Z-source inverter. IEEE Trans. Power Electron. 2011, 26, 3183–3191. [Google Scholar] [CrossRef]

- Gajanayake, C.J.; Gooi, H.B.; Luo, F.L.; So, P.L.; Siow, L.K.; Vo, Q.N. Simple modulation and control method for new extended boost quasi Z-source. In Proceedings of the TENCON Conference, Singapore, 23–26 January 2009; pp. 1–6. [Google Scholar]

- Gajanayake, C.J.; Luo, F.L.; Gooi, H.B.; So, P.L.; Siow, L.K. Extended-boost Z-source inverters. IEEE Trans. Power Electron. 2010, 25, 2642–2652. [Google Scholar] [CrossRef]

- Fathi, H.; Madadi, H. Enhanced-boost Z-source inverters with switched Z-impedance. IEEE Trans. Ind. Electron. 2015, 62, 7569–7577. [Google Scholar] [CrossRef]

- Mazumder, S.K.; Burra, R.K.; Acharya, K. A ripple-mitigating and energy-efficient fuel cell power-conditioning system. IEEE Trans. Power Electron. 2006, 22, 1437–1452. [Google Scholar] [CrossRef]

- Khateb, A.E.; Rahim, N.A.; Selvaraj, J.; Williams, B.W. The effect of input current ripple on the photovoltaic panel efficiency. In Proceedings of the IEEE CEAT, Lankgkawi, Malaysia, 18–20 November 2013; pp. 478–481. [Google Scholar]

- Jagan, V.; Kotturu, J.; Das, S. Enhanced-boost quasi-Z-source inverters with two-switched impedance networks. IEEE Trans. Ind. Electron. 2017, 64, 6885–6897. [Google Scholar] [CrossRef]

- Loh, P.C.; Gao, F.; Blaabjerg, F. Embedded EZ-source inverters. IEEE Trans. Ind. Appl. 2010, 46, 256–267. [Google Scholar]

- Babaei, E.; Asl, E.S.; Babayi, M.H.; Laali, S. Developed embedded switched-Z-source inverter. IET Power Electron. 2016, 9, 1828–1841. [Google Scholar] [CrossRef]

- Gao, F.; Loh, P.C.; Li, D.; Blaabjerg, F. Asymmetrical and symmetrical embedded Z-source inverters. IET Power Electron. 2011, 4, 181–193. [Google Scholar] [CrossRef]

- Pires, V.F.; Cordeiro, A.; Foito, D.; Martins, J.F. Quasi-Z-source inverter with a T-type converter in normal and failure mode. IEEE Trans. Power Electron. 2016, 31, 7462–7470. [Google Scholar] [CrossRef]

- Pires, V.F.; Foito, D.; Cordeiro, A. Three-phase qZ-source inverter with fault tolerant capability. IET Power Electron. 2017, 10, 1852–1858. [Google Scholar] [CrossRef]

- Sivakumar, K. A fault-tolerant single-phase five-level inverter for grid-independent PV systems. IEEE Trans. Ind. Electron. 2015, 62, 7569–7577. [Google Scholar]

- Shen, M.; Wang, J.; Joseph, A.; Peng, F.Z.; Tolbert, L.M.; Adams, D.J. Constant boost control of the Z-source inverter to minimize current ripple and voltage stress. IEEE Trans. Ind. Appl. 2006, 42, 770–778. [Google Scholar] [CrossRef]

- Huang, Y.; Shen, M.; Peng, F.Z.; Wang, J. Z-Source Inverter for Residential Photovoltaic Systems. IEEE Trans. Power Electron. 2006, 21, 1776–1782. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E.; Yang, S. Impedance-Source Networks for Electric Power Conversion Part II: Review of Control and Modulation Techniques. IEEE Trans. Power Electron. 2015, 30, 1887–1906. [Google Scholar] [CrossRef]

- Subudhi, B.; Pradhan, R. A Comparative Study on Maximum Power Point Tracking Techniques for Photovoltaic Power Systems. IEEE Trans. Sustain. Energy 2013, 4, 89–98. [Google Scholar] [CrossRef]

- Ge, B.; Abu-Rub, H.; Peng, F.Z.; Lei, Q.; de Almeida, A.T.; Ferreira, F.J.T.E.; Sun, D.; Liu, Y. An Energy-Stored Quasi-Z-Source Inverter for Application to Photovoltaic Power System. IEEE Trans. Ind. Electron. 2013, 60, 4468–4481. [Google Scholar] [CrossRef]

| Symbol | ZSI [8] | E-ZSI [20] | DA-ZSI [16] | SI-ZSI [16] | EB-ZSI [16] | EEB-ZSI | |

|---|---|---|---|---|---|---|---|

| Boost Factor | B | ||||||

| Voltage Gain | G | ||||||

| Switch Stress | |||||||

| , Stress | NA | NA | NA | NA | |||

| , Stress | NA | NA | NA | NA | 1 |

| Normal Condition | Open-Circuit Condition | Short-Circuit Condition | |

|---|---|---|---|

| B | |||

| Parameter | Symbol | Value |

|---|---|---|

| DC input voltage | V | |

| EEB-ZSI inductance | H | |

| EEB-ZSI capacitor | F | |

| Load inductance | mH | |

| Load resistance | ||

| Switching frequency | 5 kHz |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yuan, J.; Yang, Y.; Liu, P.; Shen, Y.; Blaabjerg, F. Modified Impedance-Source Inverter with Continuous Input Currents and Fault-Tolerant Operations. Energies 2020, 13, 3408. https://doi.org/10.3390/en13133408

Yuan J, Yang Y, Liu P, Shen Y, Blaabjerg F. Modified Impedance-Source Inverter with Continuous Input Currents and Fault-Tolerant Operations. Energies. 2020; 13(13):3408. https://doi.org/10.3390/en13133408

Chicago/Turabian StyleYuan, Jing, Yongheng Yang, Ping Liu, Yanfeng Shen, and Frede Blaabjerg. 2020. "Modified Impedance-Source Inverter with Continuous Input Currents and Fault-Tolerant Operations" Energies 13, no. 13: 3408. https://doi.org/10.3390/en13133408