Analysis and Implementation of a Phase-Shift Pulse-Width Modulation Converter with Auxiliary Winding Turns

Abstract

1. Introduction

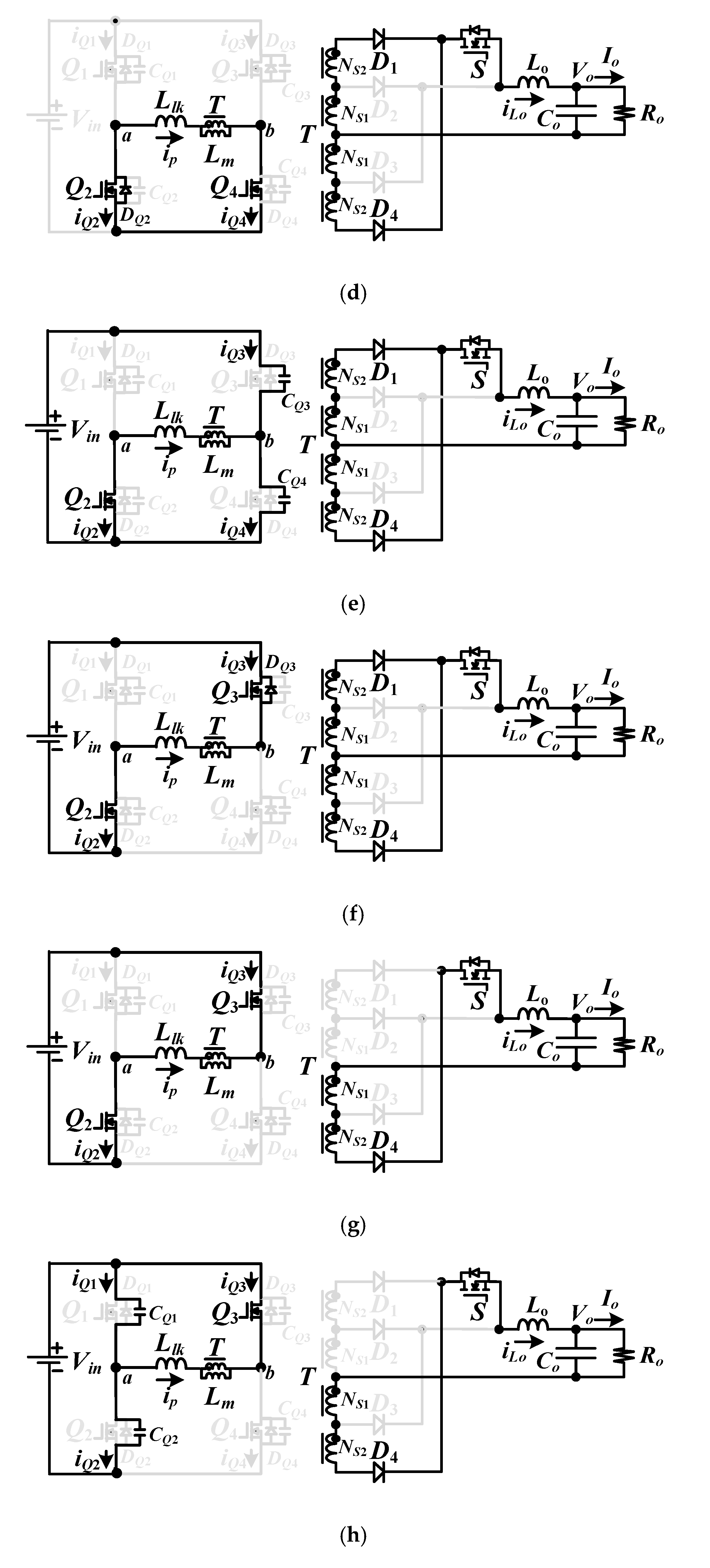

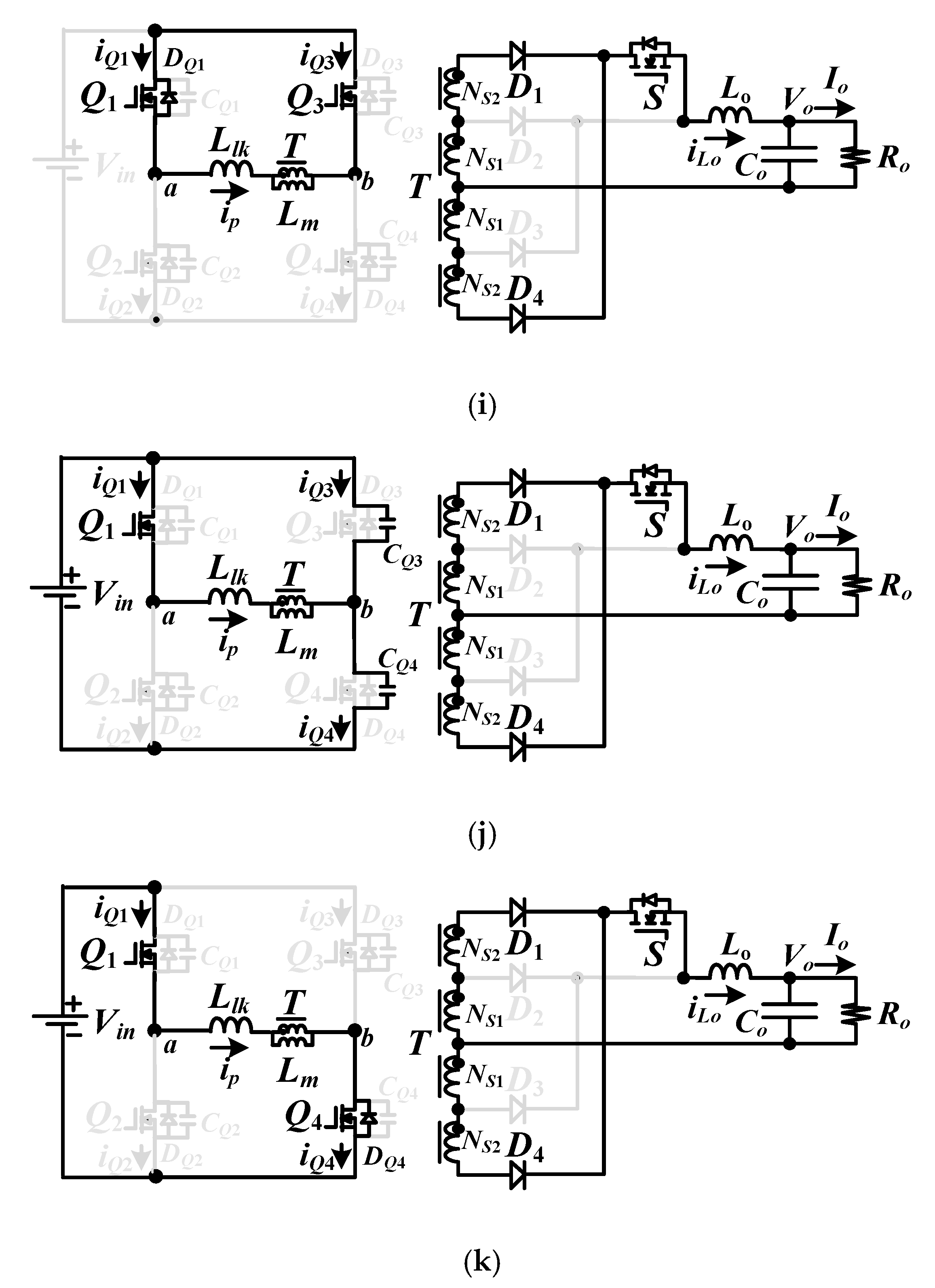

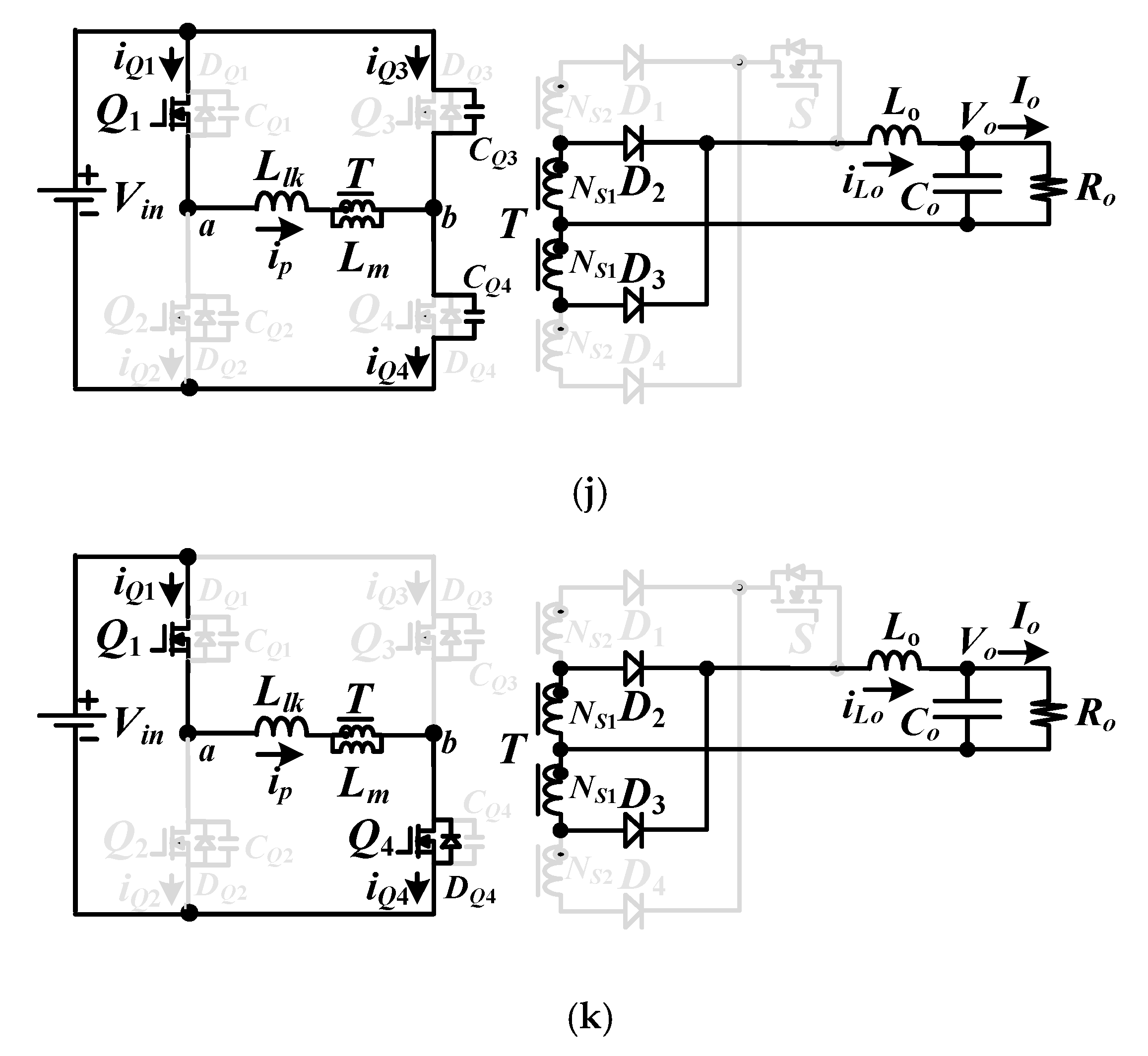

2. Circuit Structure

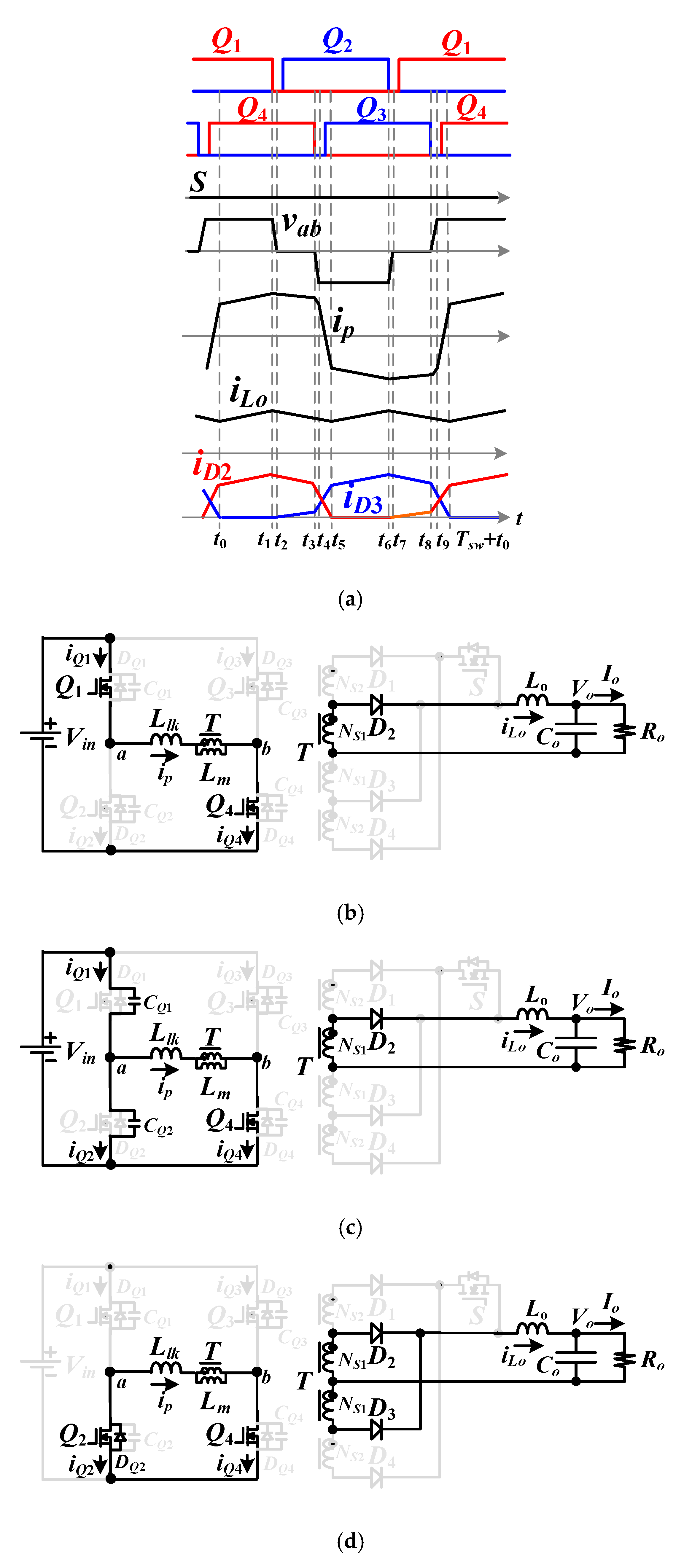

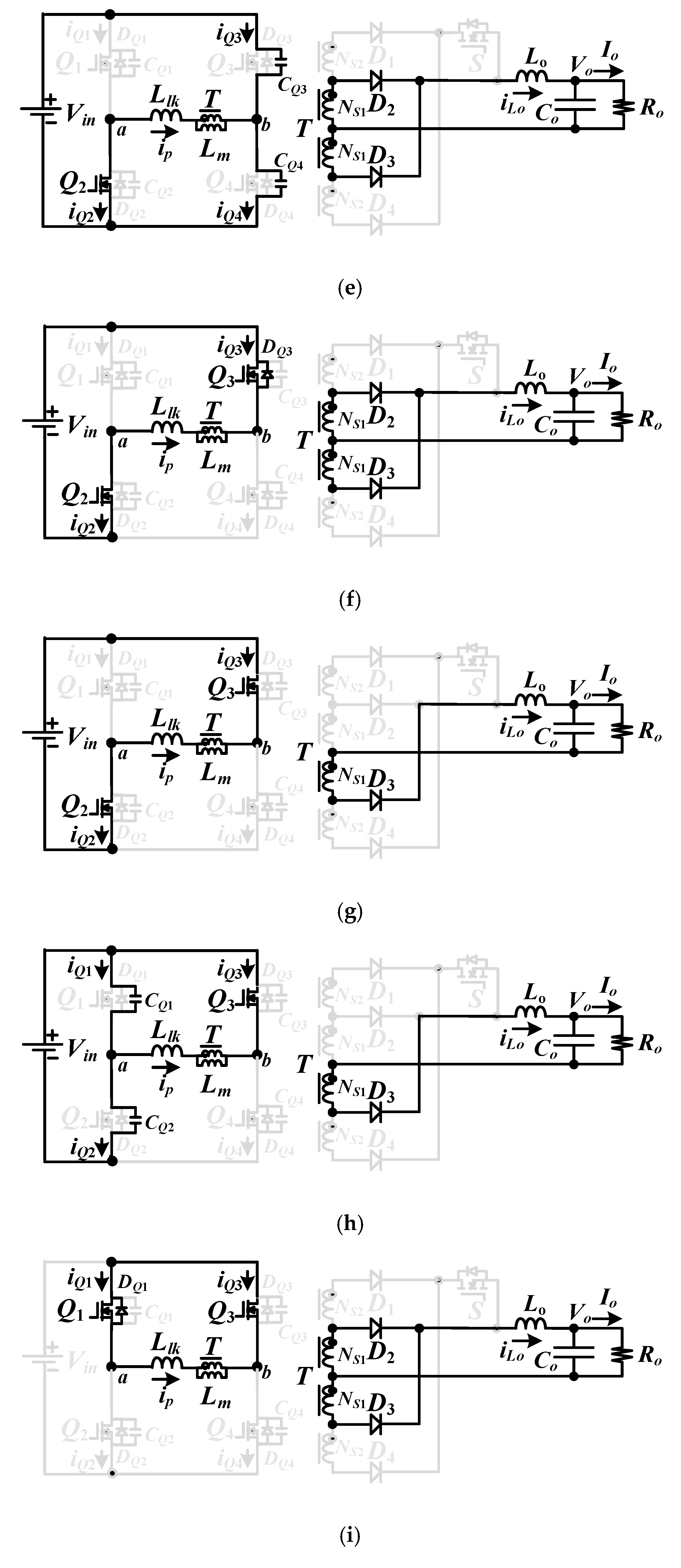

3. Operation Principle

3.1. Low Voltage Range (S on)

3.2. High Voltage Range (S off)

4. Circuit Characteristics and Design Example

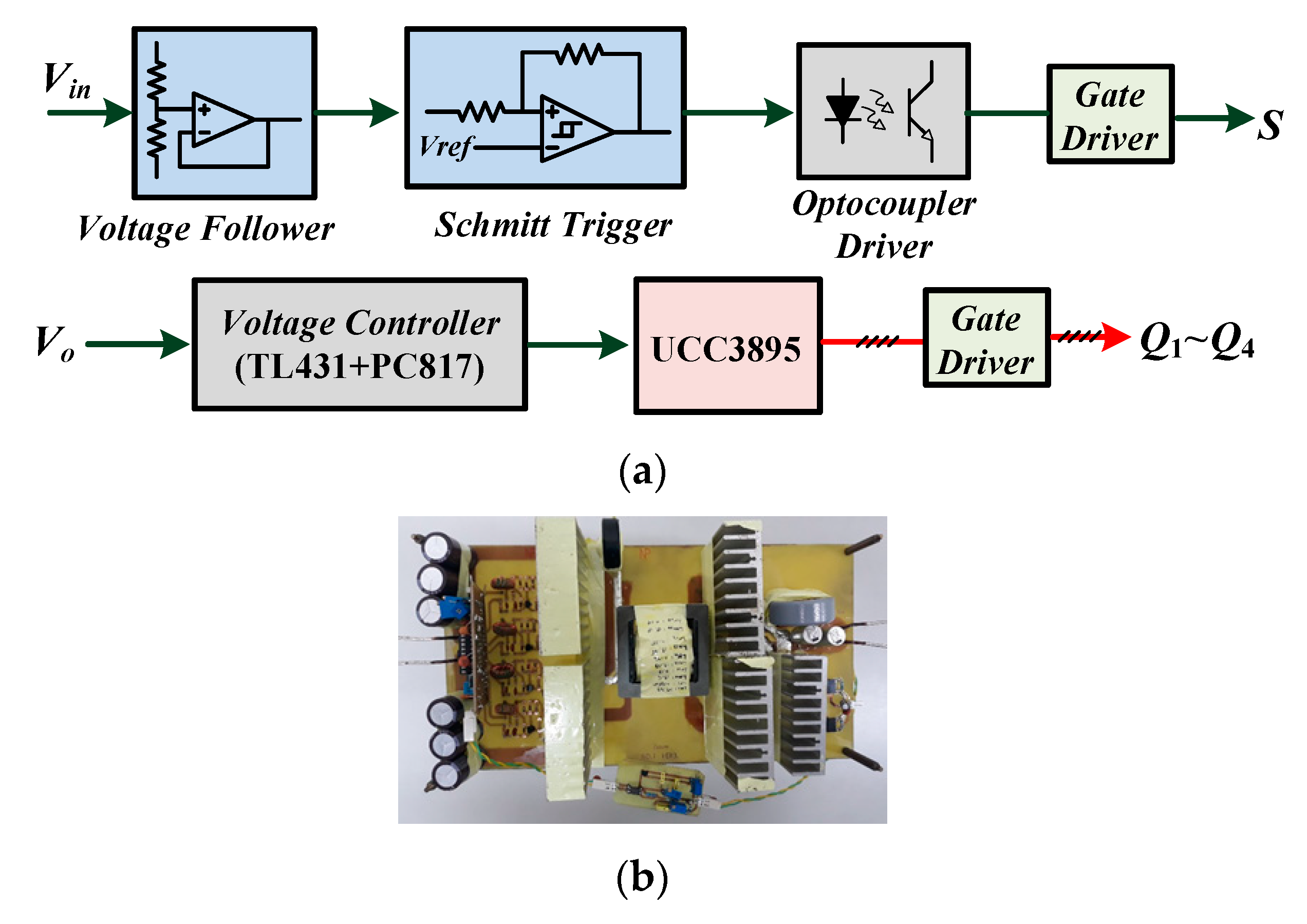

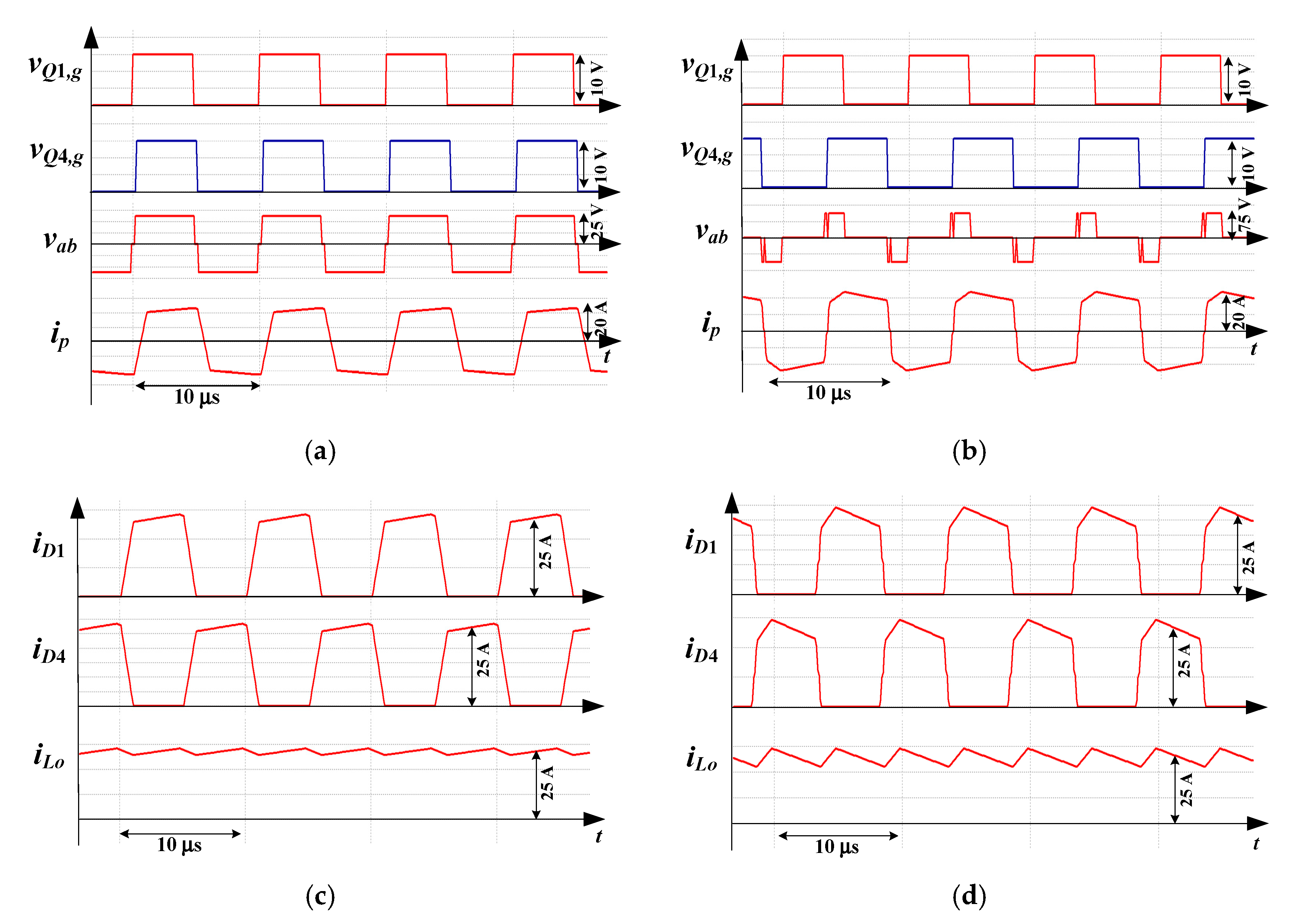

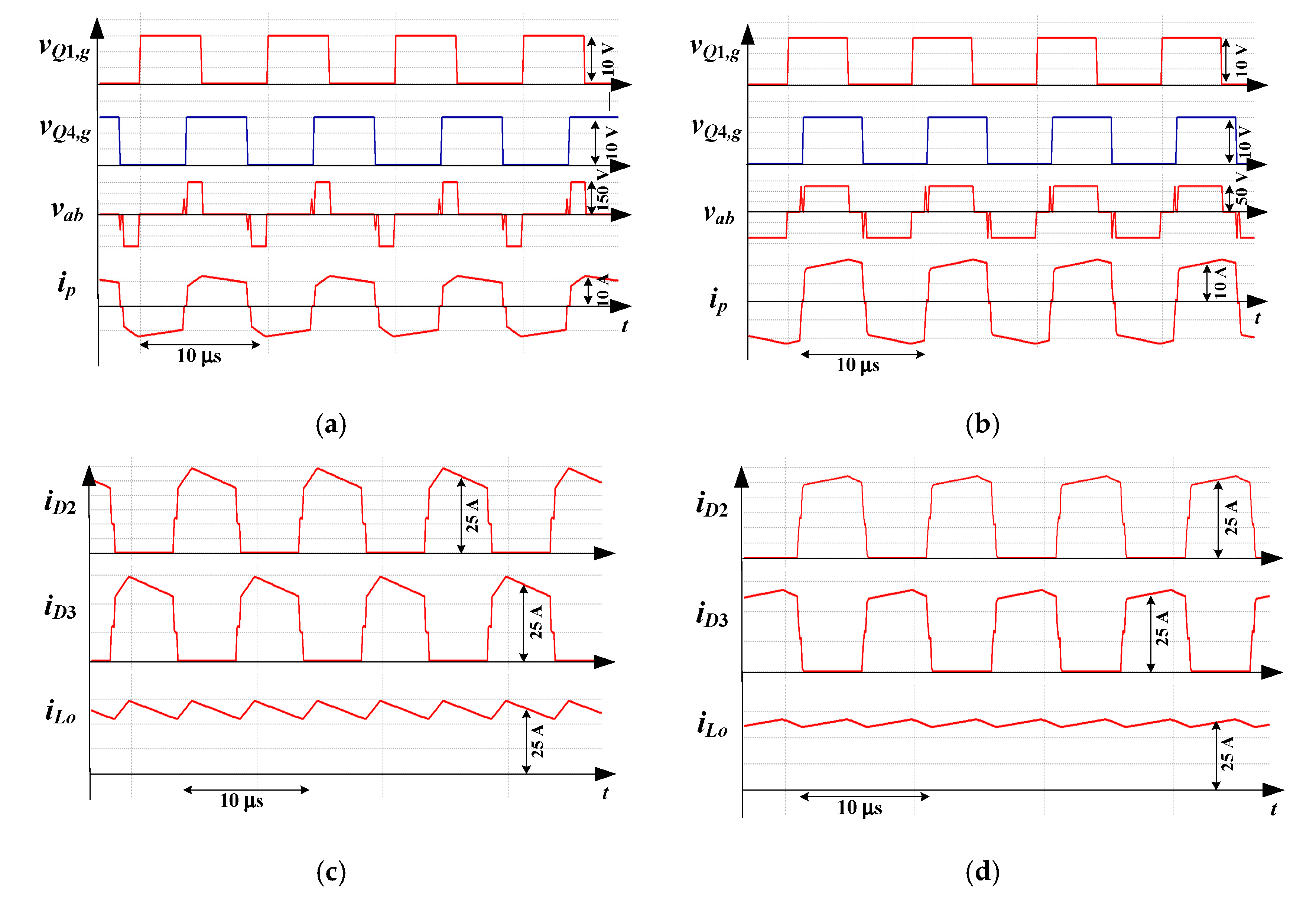

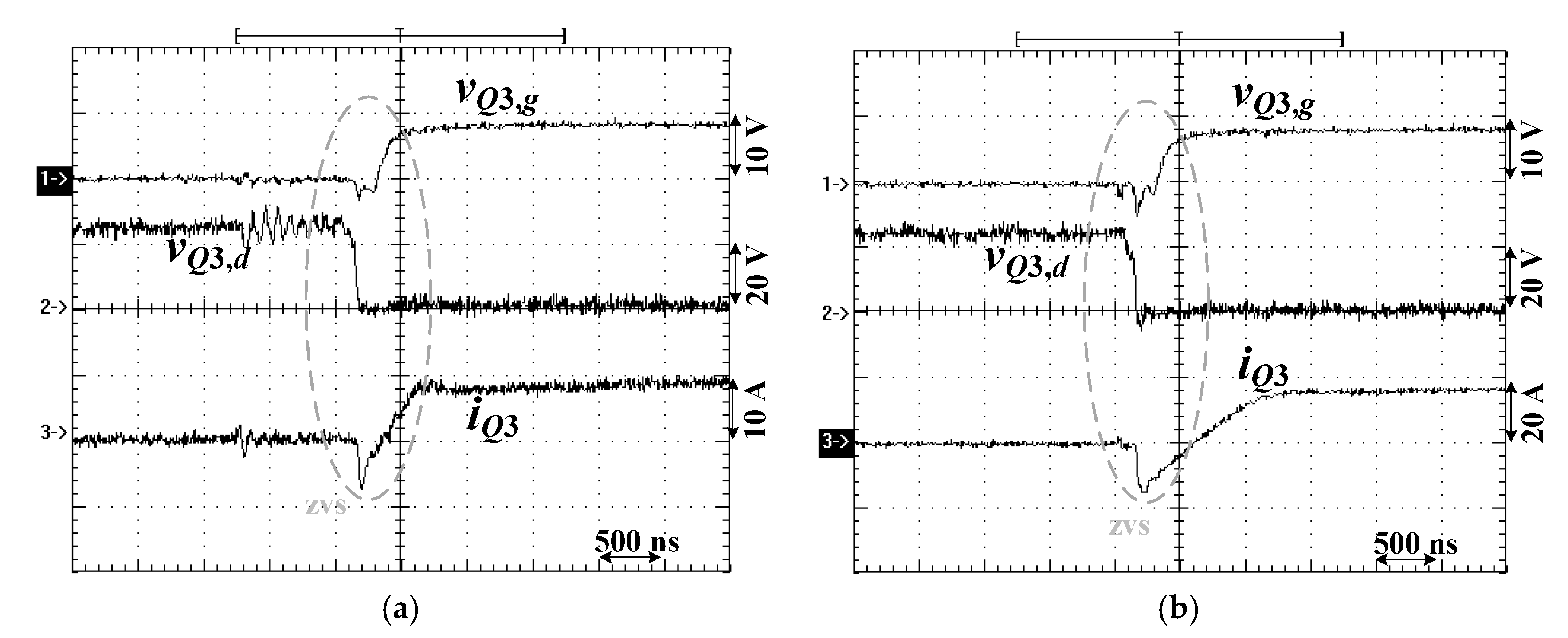

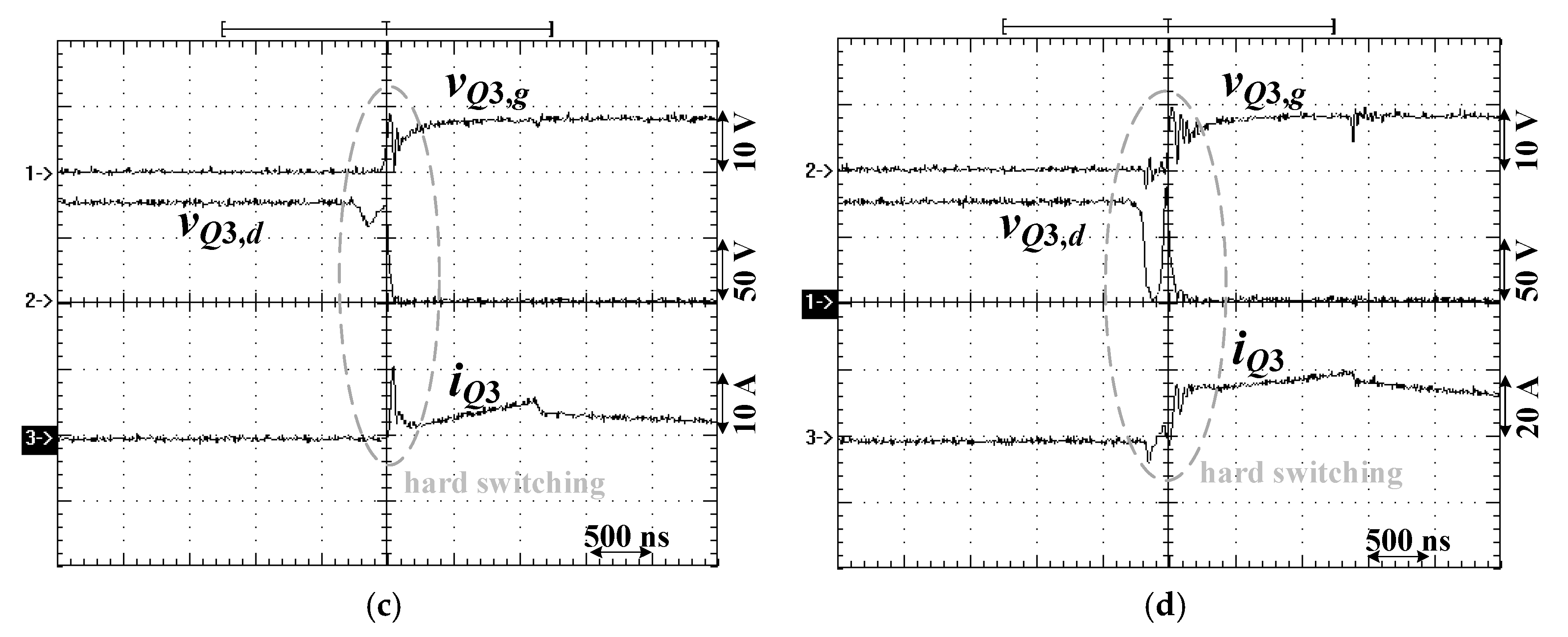

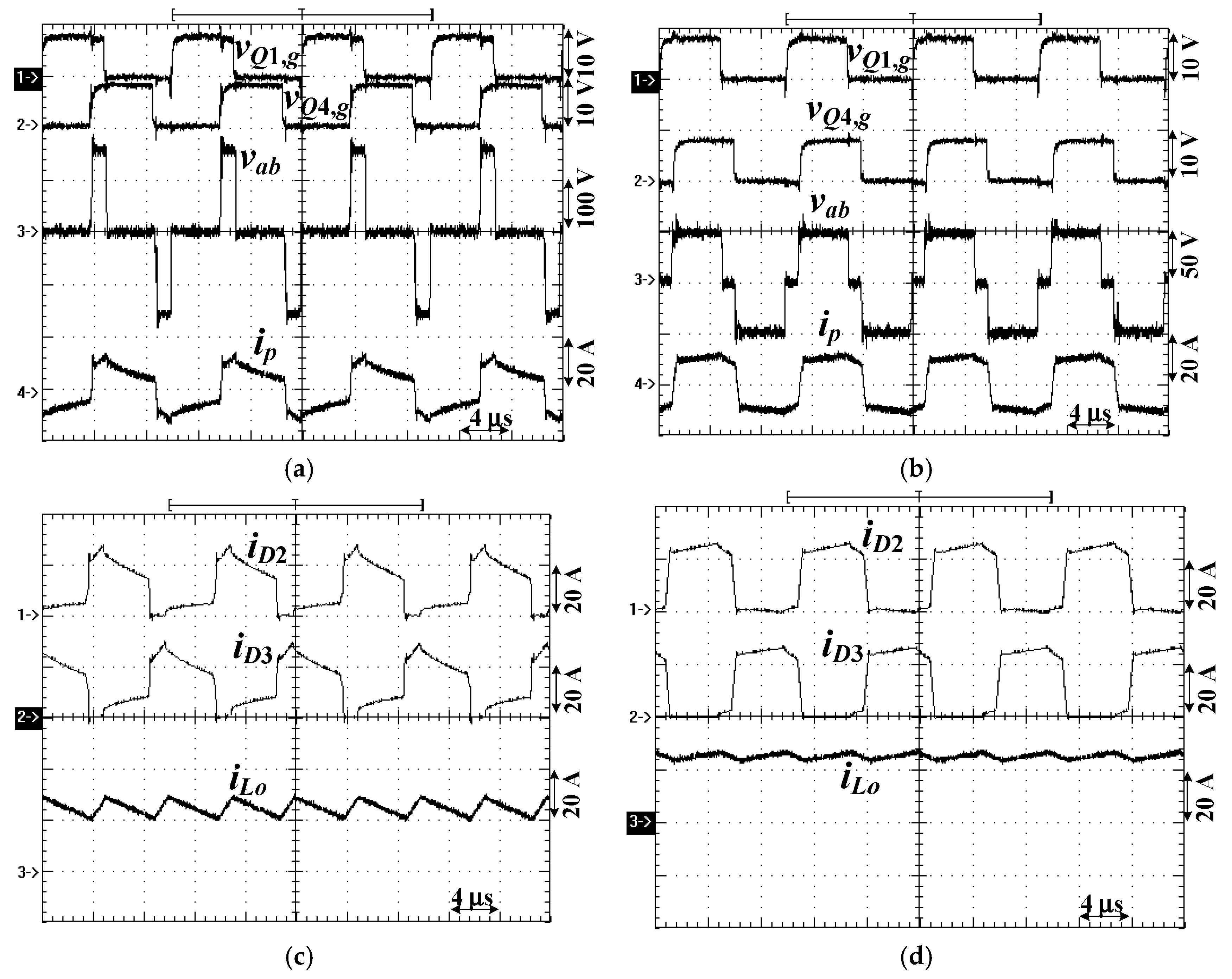

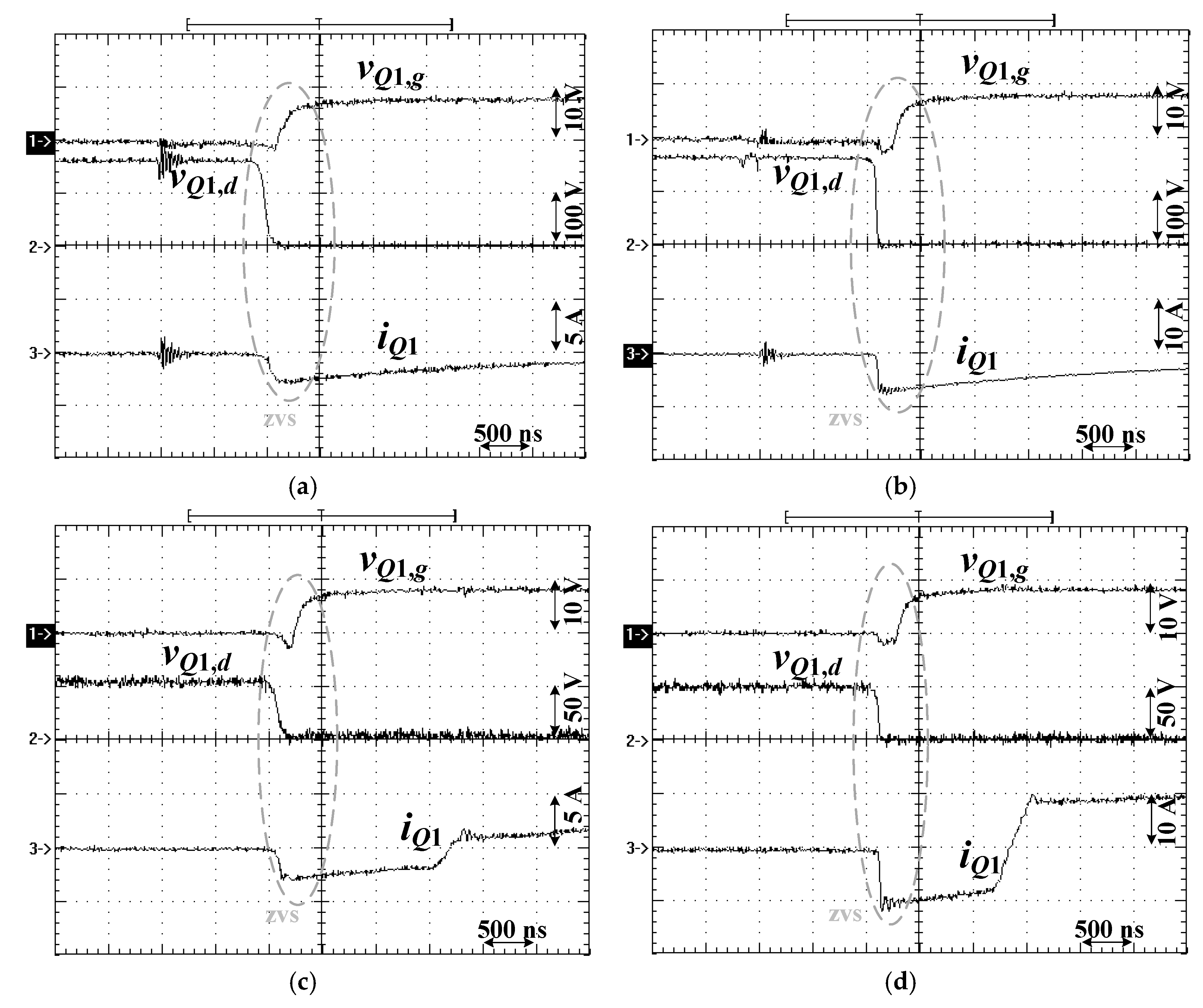

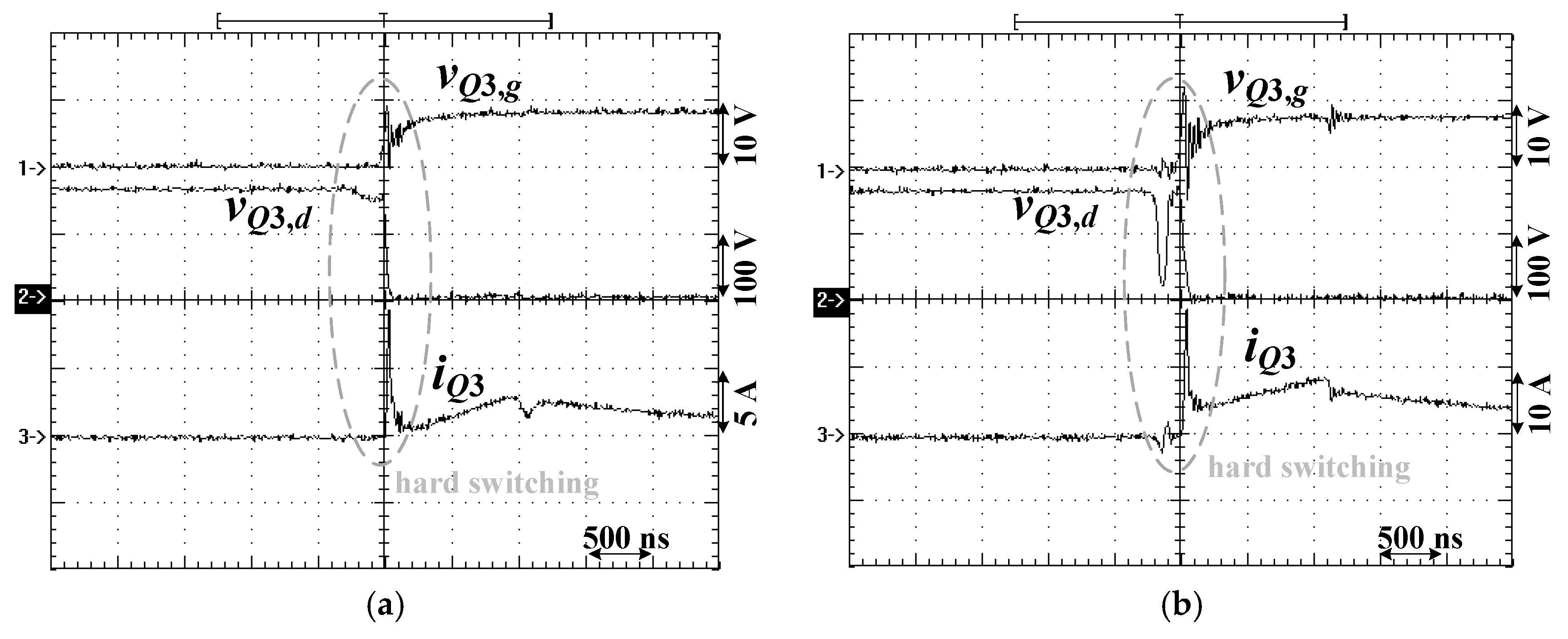

5. Simulated and Experimental Results

6. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Shang, C.; Liu, L.; Liu, M.; Men, S. A highly-efficient two-stage DC-DC converter with wide input voltage. In Proceedings of the 2015 IEEE International Telecommunications Energy Conference (INTELEC), Osaka, Japan, 18–22 October 2015; pp. 1–6. [Google Scholar]

- Zhou, G.; Ruan, X.; Wang, X. Input voltage feed-forward control strategy for cascaded DC/DC converters with wide input voltage range. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 603–608. [Google Scholar]

- Jeong, Y.; Kim, J.K.; Lee, J.B.; Moon, G.W. An asymmetric half-bridge resonant converter having a reduced conduction loss for DC/DC power applications with a wide range of low input voltage. IEEE Trans. Power Electron. 2017, 32, 7795–7804. [Google Scholar]

- Wang, P.; Zhou, L.; Zhang, Y.; Li, J.; Sumner, M. Input-parallel output-series DC-DC boost converter with a wide input voltage range, for fuel cell vehicles. IEEE Trans. Veh. Technol. 2017, 66, 7771–7781. [Google Scholar] [CrossRef]

- Zhang, Y.; Fu, C.; Sumner, M.; Wang, P. A wide input-voltage range quasi-Z-source boost DC–DC converter with high-voltage gain for fuel cell vehicles. IEEE Trans. Ind. Electron. 2018, 65, 5201–5212. [Google Scholar] [CrossRef]

- Yao, Z.; Xu, J. A three-phase DC-DC converter for low and wide input-voltage range application. In Proceedings of the 2016 the IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Busan, Korea, 1–4 June 2016; pp. 208–213. [Google Scholar]

- Sunddararaj, S.P.; Rangarajan, S.S.; Gopalan, S. Neoteric Fuzzy Control Stratagem and Design of Chopper fed Multilevel Inverter for Enhanced Voltage Output Involving Plug-In Electric Vehicle (PEV) Applications. Electronics 2019, 8, 1092. [Google Scholar] [CrossRef]

- Lu, J.; Kumar, A.; Afridi, K.K. Step-down impedance control network resonant DC-DC converter utilizing an enhanced phase-shift control for wide-input-range operation. IEEE Trans. Ind. Appl. 2013, 54, 4523–4536. [Google Scholar] [CrossRef]

- Li, W.; Zong, S.; Liu, F.; Yang, H.; He, X.; Wu, B. Secondary-side phase-shift-controlled ZVS DC/DC converter with wide voltage gain for high input voltage applications. IEEE Trans. Power Electron. 2013, 28, 5128–5139. [Google Scholar] [CrossRef]

- Wang, X.; Tian, F.; Batarseh, I. High efficiency parallel post regulator for wide range input DC–DC converter. IEEE Trans. Power Electron. 2008, 23, 852–858. [Google Scholar] [CrossRef]

- Wu, H.; Wan, C.; Sun, K.; Xing, Y. A high step-down multiple output converter with wide input voltage range based on quasi two-stage architecture and dual-output LLC resonant converter. IEEE Trans. Power Electron. 2015, 30, 1793–1796. [Google Scholar] [CrossRef]

- Zong, S.; Fan, G.; Yang, X. Double voltage rectification modulation for bidirectional CLLLC resonant converter for wide voltage range operation. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018; pp. 1–6. [Google Scholar]

- Cha, H.; Peng, F.Z.; Yoo, D. Z-source resonant DC-DC converter for wide input voltage and load variation. In Proceedings of the 2010 International Power Electronics Conference - ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 995–1000. [Google Scholar]

- Kim, B.; Kim, S.; Hun, D.Y.; Choi, J.H.; Kim, M. Hybrid resonant half-bridge DC/DC converter with wide input voltage range. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1876–1881. [Google Scholar]

- Lin, B.R.; Lin, G.H. Frequency-Controlled Current-Fed Resonant Converter with No Input Ripple Current. Energies 2018, 11, 1–13. [Google Scholar]

- Liu, B.; Jones, E.A.; Wang, F.F.; Zhang, Z.; Costinett, D.; Ren, R. Capacitor-clamped, three-level Gan-based dc-dc converter with dual voltage outputs for battery charger applications. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 841–853. [Google Scholar]

- Lin, B.R.; Wu, G.Y. Bidirectional Resonant Converter with Half-Bridge Circuits: Analysis, Design, and Implementation. Energies 2018, 11, 2450. [Google Scholar] [CrossRef]

- Antonio, J.B.; Barbi, I. Input-series and output-series connected modular output capacitor full-bridge PWM DC–DC converter. IEEE Trans. Ind. Electron. 2015, 62, 6213–6221. [Google Scholar]

- Lin, B.R.; Lin, G.H.; Jian, A. Resonant converter with voltage-doubler rectifier or full-bridge rectifier for wide-output voltage and high-power applications. Electronics 2019, 8, 3. [Google Scholar] [CrossRef]

© 2020 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, B.-R. Analysis and Implementation of a Phase-Shift Pulse-Width Modulation Converter with Auxiliary Winding Turns. Energies 2020, 13, 222. https://doi.org/10.3390/en13010222

Lin B-R. Analysis and Implementation of a Phase-Shift Pulse-Width Modulation Converter with Auxiliary Winding Turns. Energies. 2020; 13(1):222. https://doi.org/10.3390/en13010222

Chicago/Turabian StyleLin, Bor-Ren. 2020. "Analysis and Implementation of a Phase-Shift Pulse-Width Modulation Converter with Auxiliary Winding Turns" Energies 13, no. 1: 222. https://doi.org/10.3390/en13010222

APA StyleLin, B.-R. (2020). Analysis and Implementation of a Phase-Shift Pulse-Width Modulation Converter with Auxiliary Winding Turns. Energies, 13(1), 222. https://doi.org/10.3390/en13010222