FPGA Based Real-Time Emulation System for Power Electronics Converters

Abstract

1. Introduction

2. Modelling Method Description

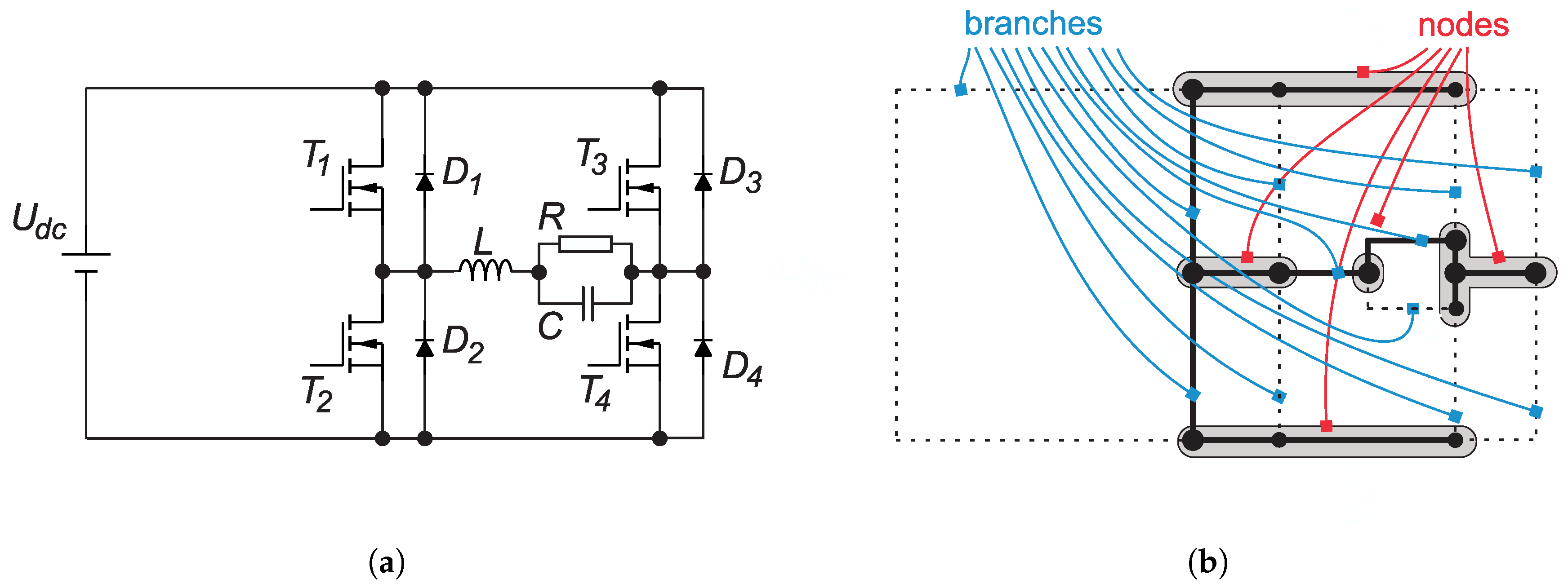

2.1. Basic Terminology for the Graph Theory

- Tree is a connected sub-graph of a given graph, where branches only connect graph nodes. Tree is shown in Figure 2b indicated by bold lines. The branches of a tree are called twigs. A tree consists of only branches that do not form loops. The number of tree branches () that form a graph tree can be calculated:where n represents the number of nodes.

- Co-Tree is a sub-graph, which is formed with the branches that are removed while forming a tree. It is indicated in Figure 2b by dashed lines. If branches from the co-tree are connected to the tree, loops are formed. Hence, it is called a complement of a tree. For every tree, there will be a corresponding co-tree, and its branches are called links or chords.

- Incidence matrix is description of any oriented graph in a compact matrix form. The incident matrix translates the graphical data of a network into algebraic form. For a graph with n nodes and b branches, the complete incidence matrix is an matrix with elements defined by:Using Kirchhoff’s Current Law (KCL), the rules can be obtained for an incidence matrix. For the chosen circuit graph shown in Figure 2a, it follows:where – represent the branch currents, which are depicted in Figure 3a. Equation (2) can be expressed in the matrix form as follows:where represents the incidence matrix. If one complete row is removed from an incidence matrix, it results in a reduced incidence matrix, which is appropriate for further calculations. By choosing the node as a reference node, and according to the graph shown in Figure 3a, the reduced incidence matrix is:and using the matrix notations, it follows:where represents the reduced incidence matrix and is the branch current vector. Equation (5) also gives the maximum possible number of linearly-independent KCL equations for a connected circuit. The numbers of rows (N) in the reduced incidence matrix is:where n is number of all graph nodes. To calculate the nodes voltages, Kirchhoff’s Voltage Law (KVL) can be used to connect branch and nodes voltages as follows:which leads to:and in the matrix form

- Tie-set matrixFor a given tree of a graph, the addition of each link between any two nodes forms a loop called the fundamental loop. In a loop, there exists a closed path and a circulating current, which is called the link current. The fundamental loop formed by one link has a unique path in the tree joining the two nodes of the link. This loop is also called a f-loop or a tie-set. The current in any branch of a graph can be found by using link currents. Consider the connected graph shown in Figure 3a, which has five nodes and twelve branches. In general, the tree branches are chosen arbitrarily, and are indicated by a bold line, as shown in Figure 3a. The twigs of this tree are branches 9–12. The links corresponding to this tree are branches 1–8. Every link defines a fundamental loop of the network. The number of graph links (or f-loops) can be calculated as follows:Thus, for a given oriented graph (Figure 3), the next set of parameters are defined: the number of nodes (), number of branches (), number of tree branches or twigs (), and number of link branches (). KVL can be applied to the f-loops to get a set of linearly independent equations. Consider Figure 3b, where there are eight fundamental loops corresponding to the link branches 1–8, respectively. If are the branch voltages, the KVL equations for the tree f-loops can be written as:and in matrix form, Equation (11) becomes:orwhere is a so-called tie-set matrix or fundamental loop matrix, and is a column vector of the branch voltages.

- Tie-set matrix and branch currentsLet be the branch currents with directions as shown in Figure 3a. Then, add the links in their proper places to the tree, as shown in Figure 3b. It can be seen that the loops currents are formed by the tree branches 9–12. There is a formation of link currents indicated in Figure 3b by Roman numbers . By convention, the f-loops currents are given the same orientation as their defining links currents, i.e., the link current coincides with the branch current direction , the link current coincides with the branch current direction , and so on until the link current coincides with the branch current direction , and, according to tree branches, the branches currents are combinations of f-loops currents. Thus, based on these assumptions, branches currents related with the loops currents can be expressed as:

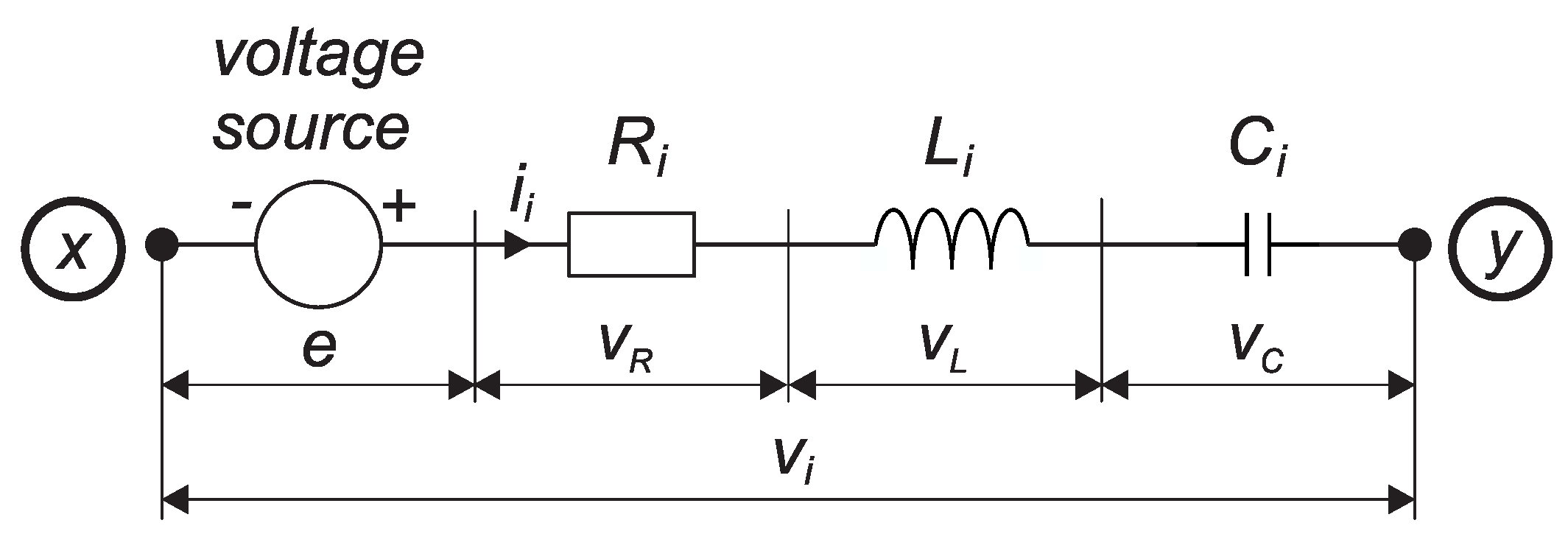

2.2. General “Construction” of Circuit Differential Equations

Loop Current Differential Equations

2.3. Consideration of Circuit Loops Matrices

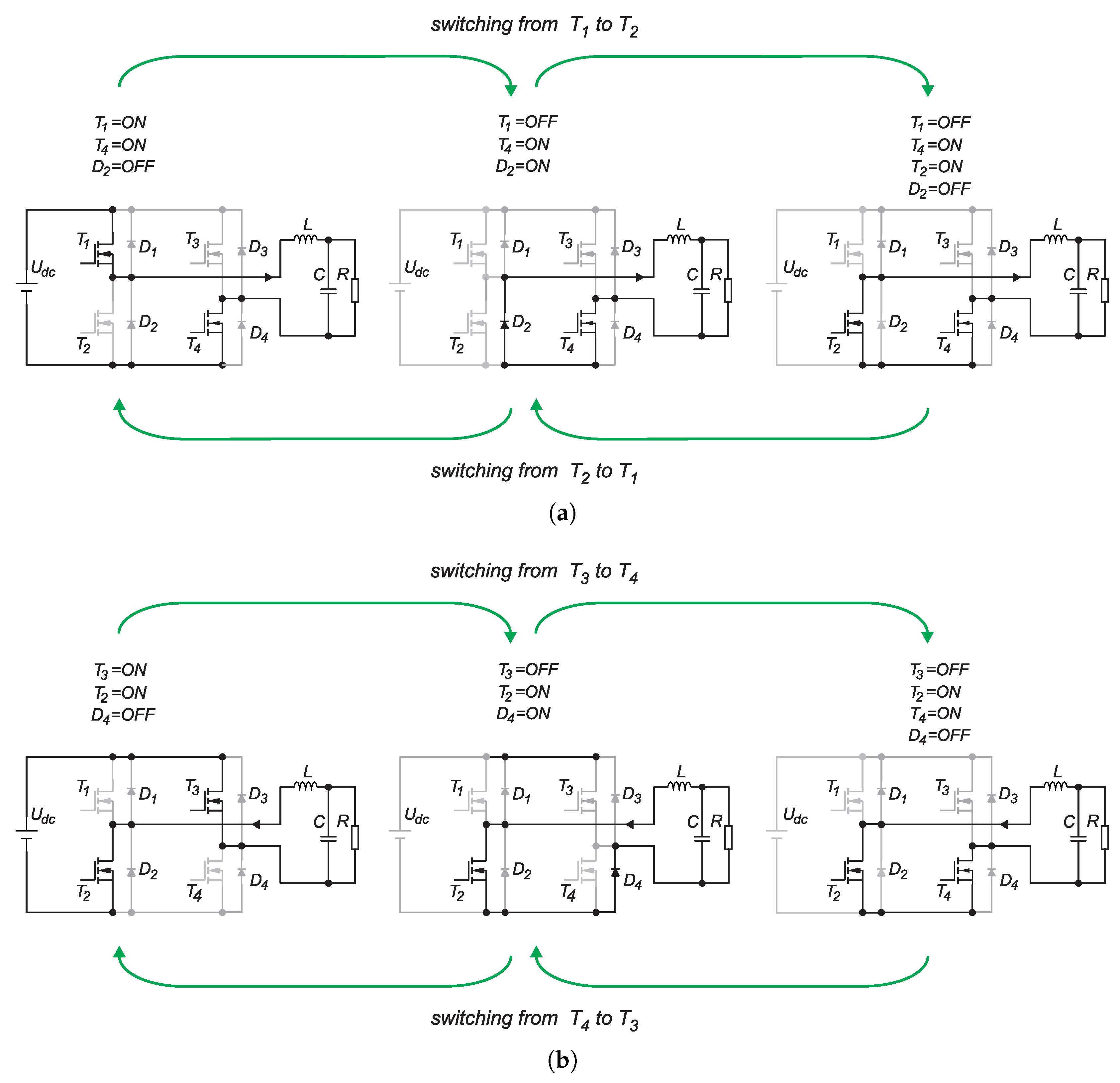

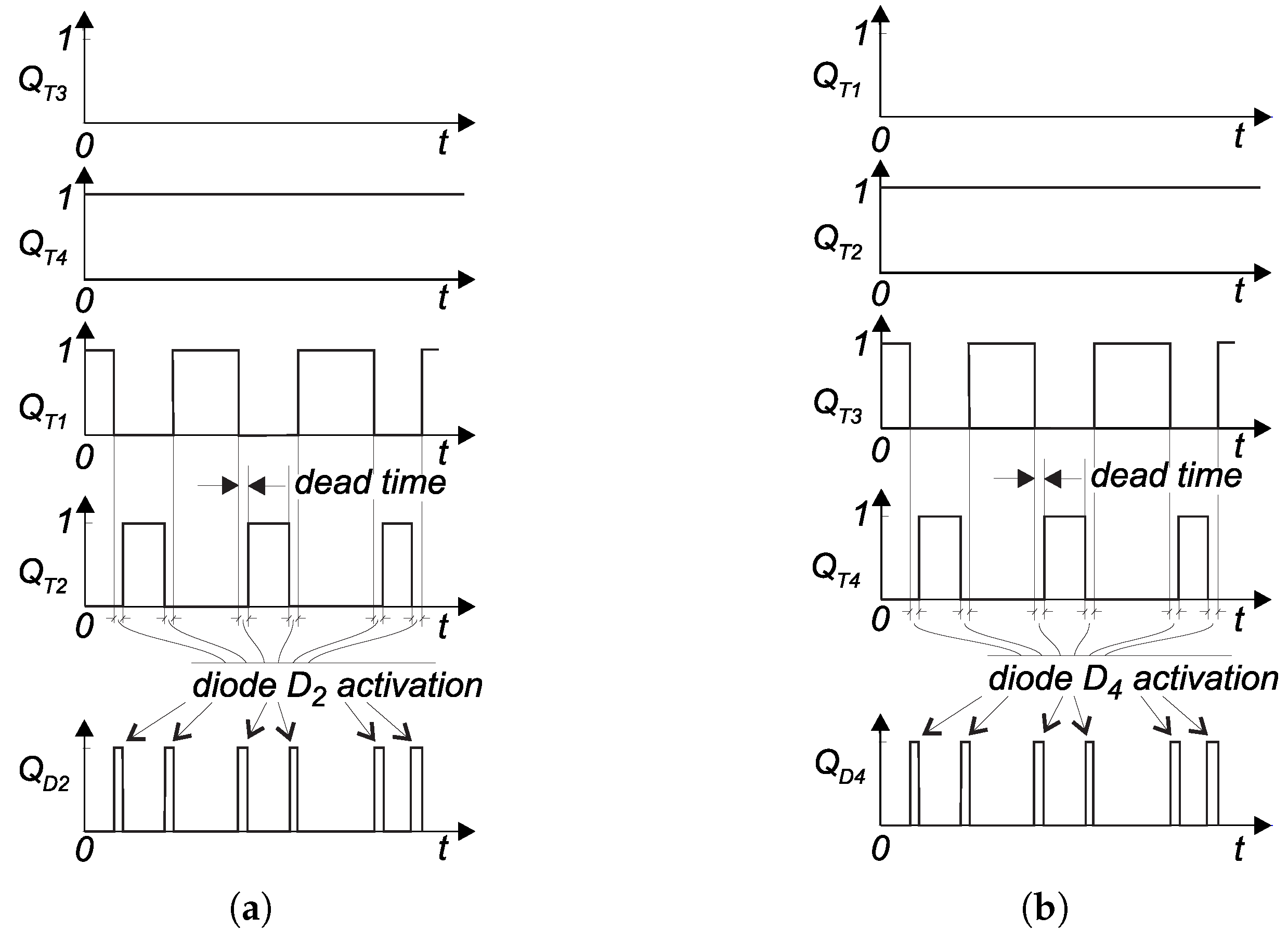

2.3.1. Control of Branches Containing Transistors

2.3.2. Control of Branches Containing Diodes

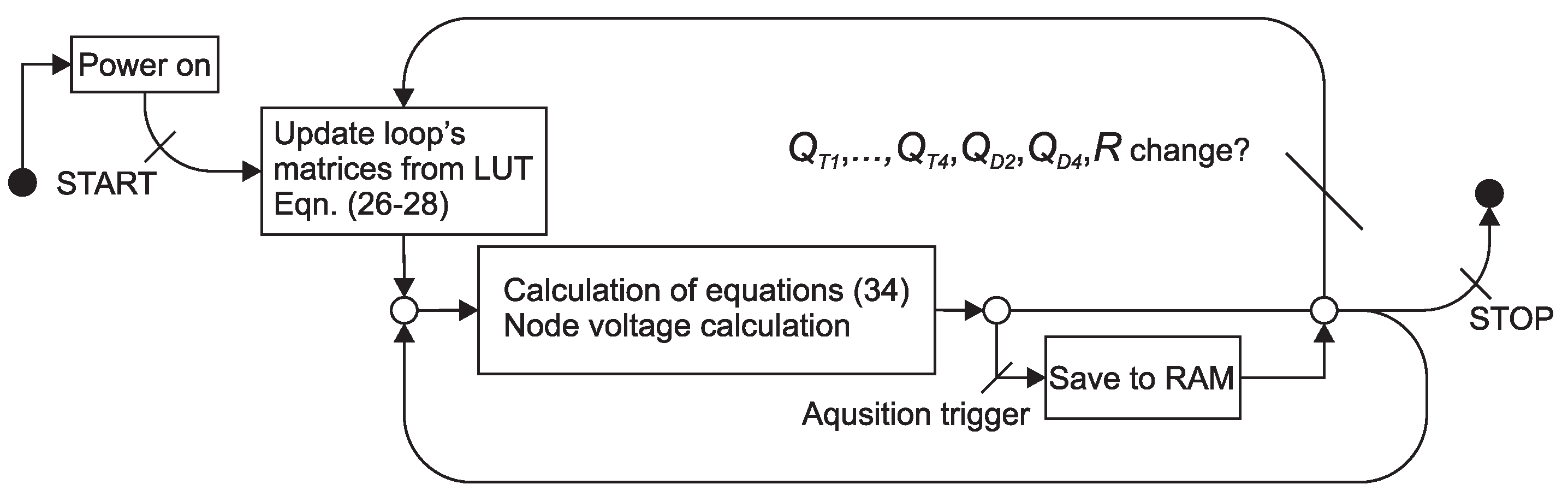

2.4. Off-Line Data Calculation

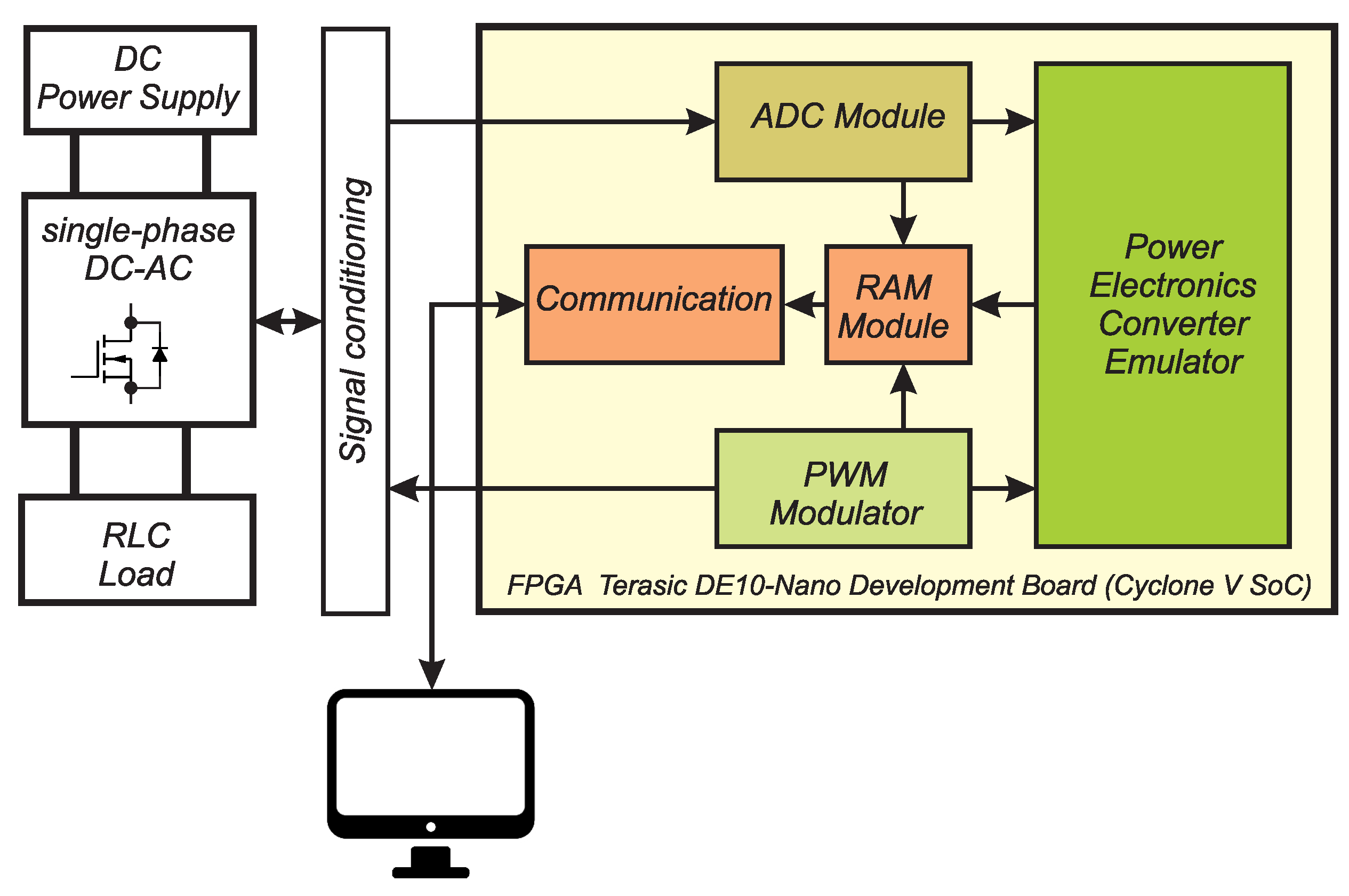

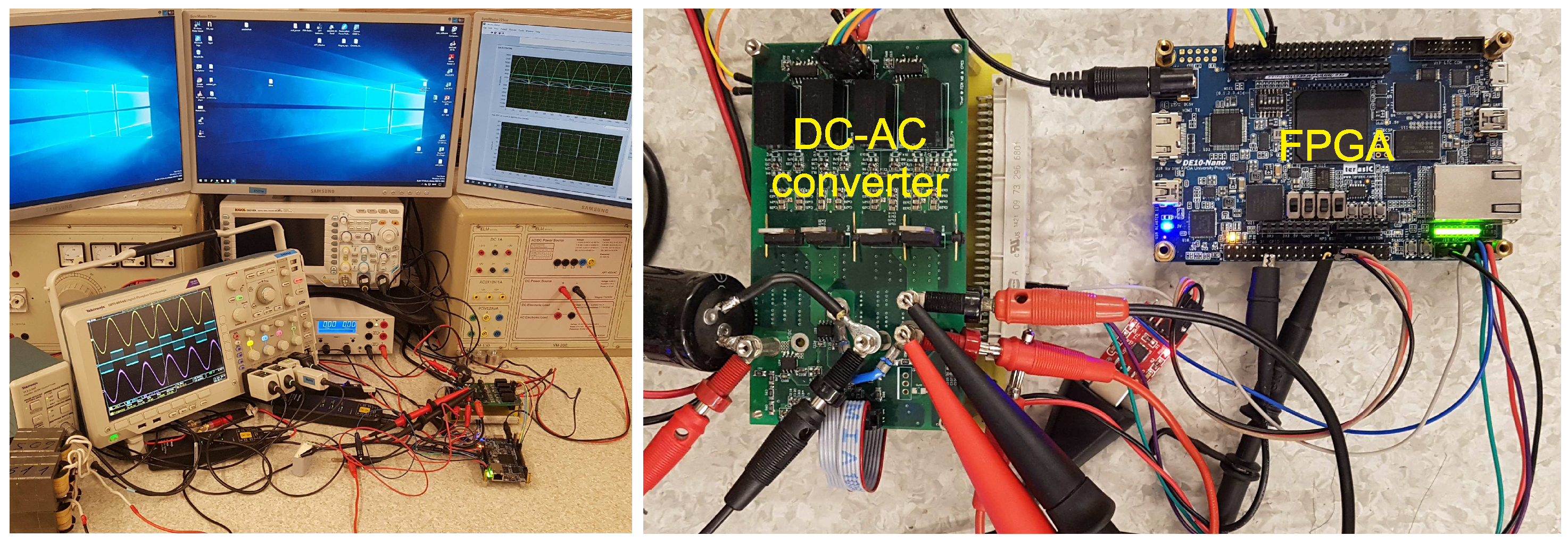

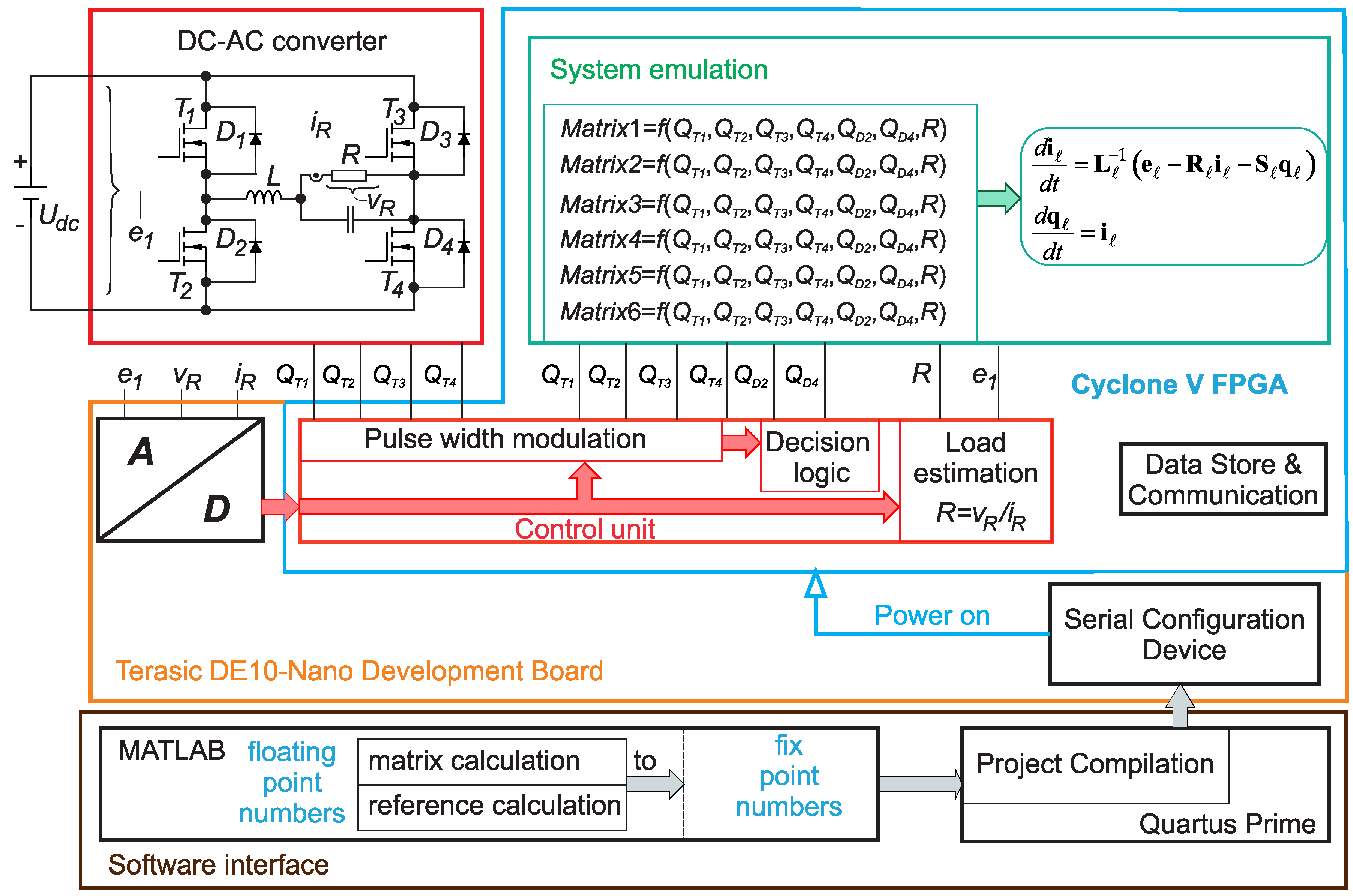

3. Setup for Algorithm Verification

3.1. FPGA Unit

3.2. Single-Phase DC-AC Converter

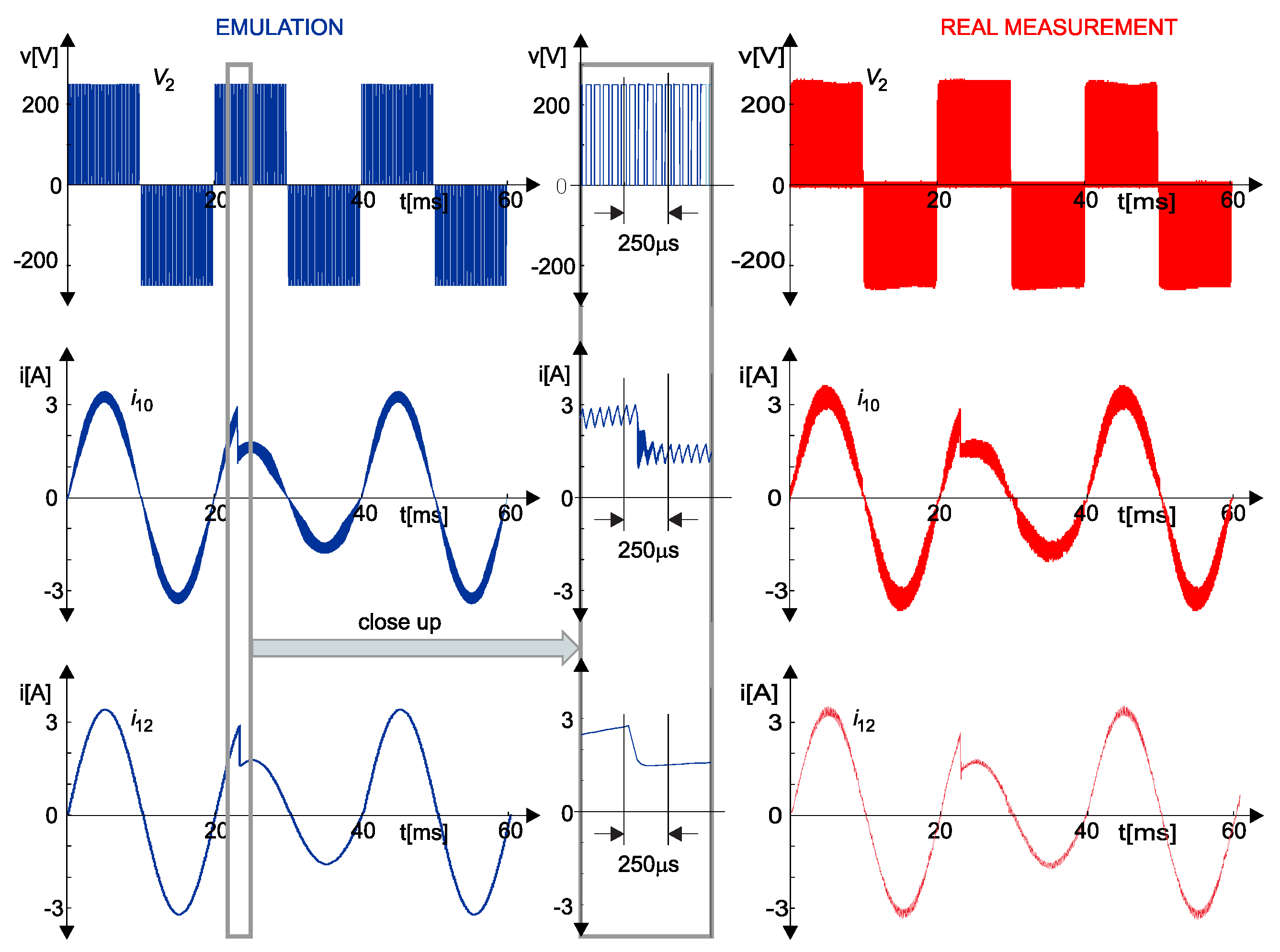

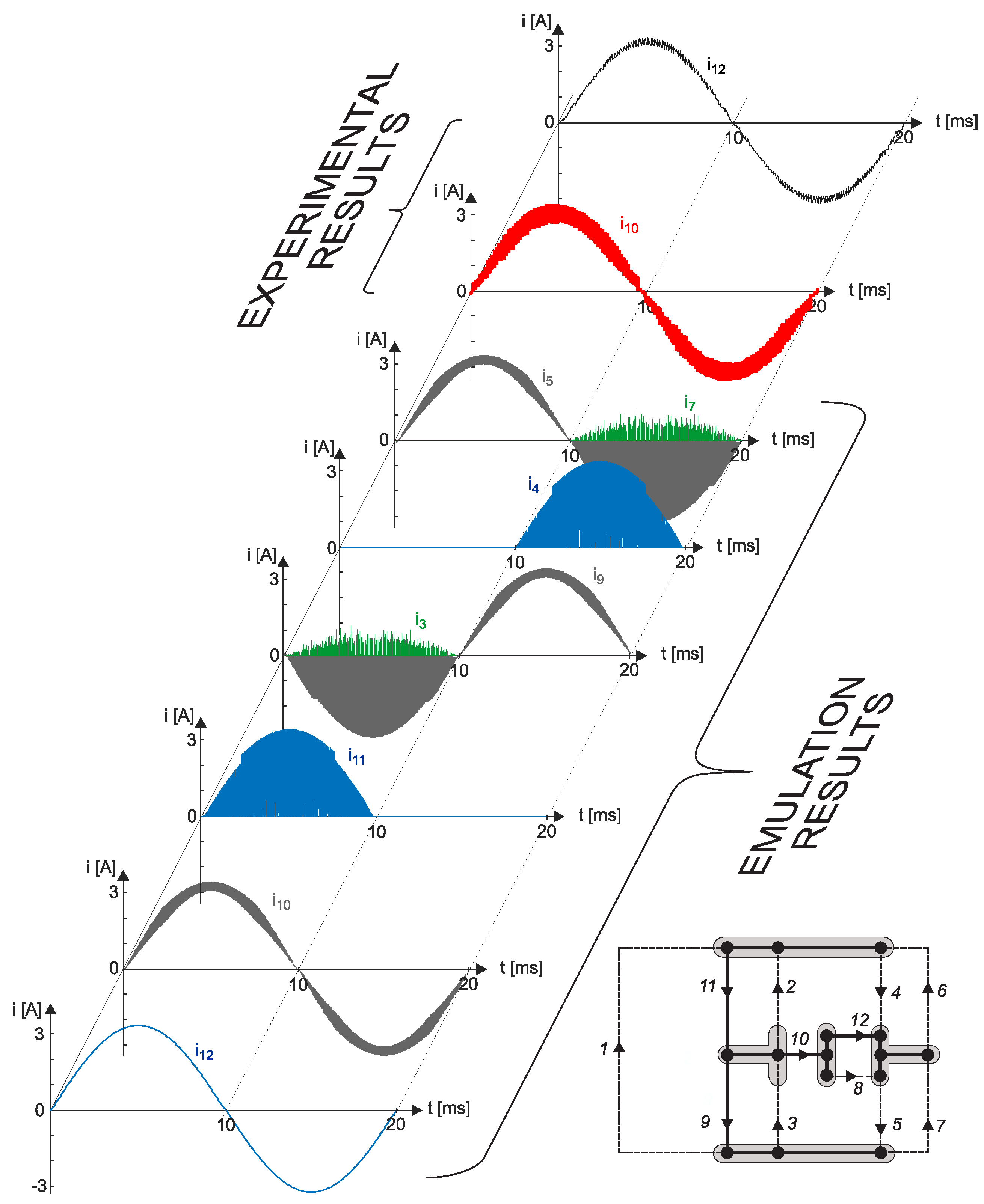

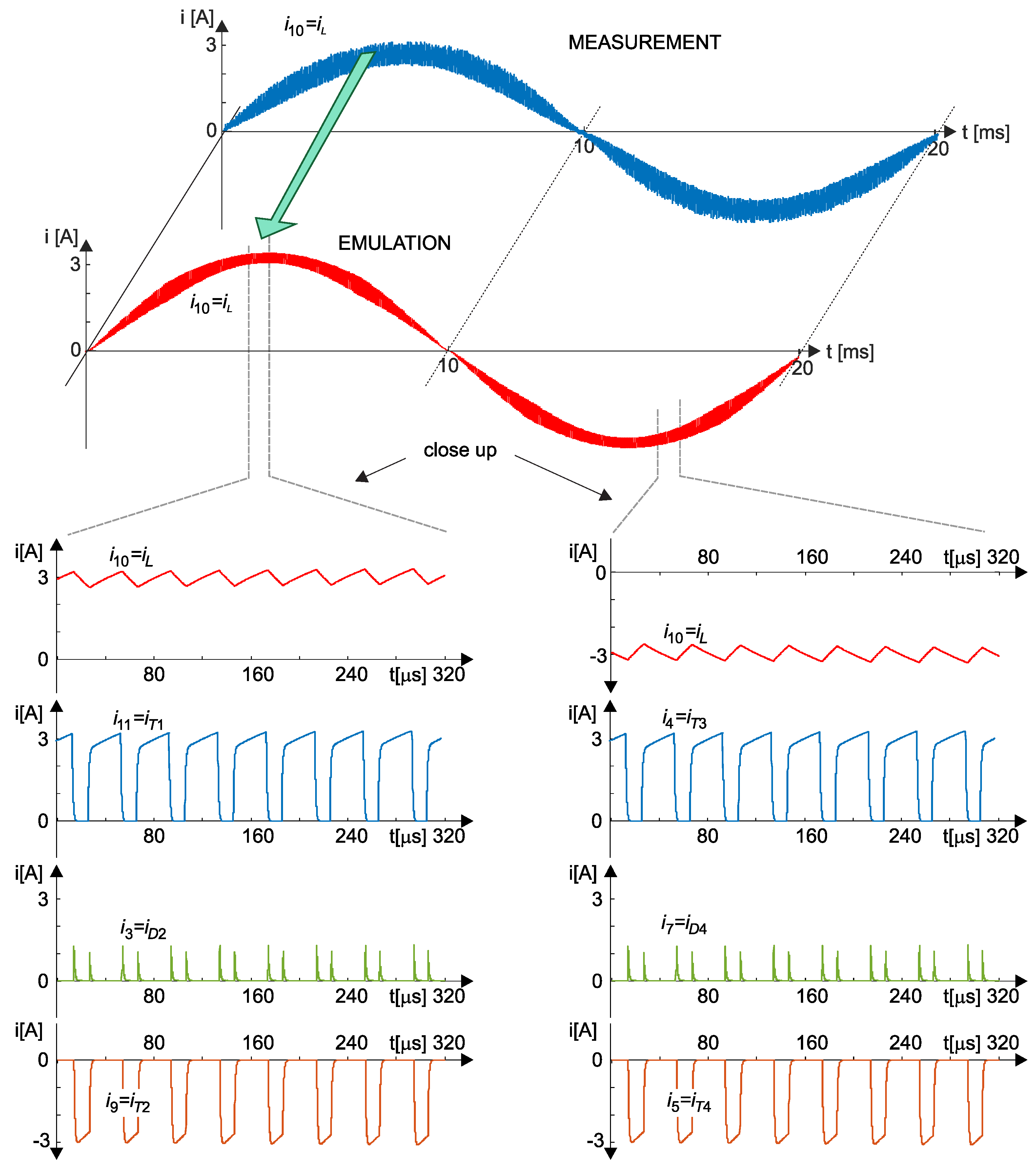

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| PEC | Power Electronics Converter |

| FPGA | Field-Programmable Gate Array |

| PWM | Pulse-Width Modulation |

| FD | Fault Diagnosis |

| HiL | Hardware in the loop |

| LUT | Look-Up Table |

| PES | Power Electronics System |

| DSP | Digital-Signal-Processor |

| KCL | Kirchhoff’s Current Law |

| KVL | Kirchhoff’s Voltage Law |

| ADC | Analog to Digital Converter |

| Constant Power Source (DC) Voltage | |

| , , , | Converter MOSFET switches |

| , , , | MOSFETs body diodes |

| L, R, C | Converter output filter and load |

| number of tree branches (or twigs) | |

| n | number of graph nodes |

| b | number of graph branches |

| Incidence matrix | |

| Reduced incidence matrix | |

| Transpose of reduced incidence matrix | |

| N | Number of rows in reduced incidence matrix |

| Incidence matrix element (, ) | |

| Branch current vector | |

| Graph branch voltages | |

| Graph nodes voltages | |

| Branch voltage vector | |

| Node voltage vector | |

| Number of graph links (or f-loops) | |

| Tie-set matrix or fundamental loop matrix | |

| Transpose of tie-set matrix or fundamental loop matrix | |

| Graph branch currents | |

| Graph link (or f-loops) currents (j in Roman numbers) | |

| Link (or f-loops) current vector | |

| Branch voltage sources | |

| Branch resistances | |

| Branch inductances | |

| Branch elastances () | |

| Branch charges (i.e., branch capacitor voltages) | |

| Branch voltage sources vector | |

| Branch resistances diagonal matrix | |

| Branch inductances diagonal matrix | |

| Branch elastances diagonal matrix | |

| Branch charges vector (i.e., capacitor voltages vector) | |

| Loops voltage sources vector | |

| Loops resistances matrix | |

| Loops inductances matrix | |

| Loops elastances matrix | |

| Loops charges vector (i.e., capacitor voltages vector) | |

| , , , | Transistor gate signals and diode switching signals, respectively |

| , , | |

| and | |

| , | Conducting model value of resistance and inductance for MOSFETs and diodes |

| , | Non-conducting model value of resistance and inductance for MOSFETs and diodes |

| PWM Frequency | |

| PWM period | |

| Modulation reference voltage function | |

| Peak value of reference output sine voltage | |

| Sine reference output signal angular frequency | |

| f | FPGA clock frequency |

| h | Integration step |

| PC | Personal Computer |

| RAM | Random-Access Memory |

| CSV | Comma-Separated Values |

References

- Kinsy, M.; Khan, O.; Celanovic, I.; Majstorovic, D.; Celanovic, N.; Devadas, S. Time-Predictable Computer Architecture for Cyber-Physical Systems: Digital Emulation of Power Electronics Systems. In Proceedings of the 2011 IEEE 32nd Real-Time Systems Symposium, Vienna, Austria, 29 November–2 December 2011; pp. 305–316. [Google Scholar] [CrossRef]

- Yang, L.; Wang, J.; Ma, Y.; Wang, J.; Zhang, X.; Tolbert, L.M.; Wang, F.F.; Tomsovic, K. Three-Phase Power Converter-Based Real-Time Synchronous Generator Emulation. IEEE Trans. Power Electron. 2017, 32, 1651–1665. [Google Scholar] [CrossRef]

- Geng, Z.; Hong, T.; Qi, K.; Ambrosio, J.; Gu, D. Modular Regenerative Emulation System for DC–DC Converters in Hybrid Fuel Cell Vehicle Applications. IEEE Trans. Veh. Technol. 2018, 67, 9233–9240. [Google Scholar] [CrossRef]

- De Lillo, L.; Empringham, L.; Wheeler, P.W.; Khwan-On, S.; Gerada, C.; Othman, M.N.; Huang, X. Multiphase Power Converter Drive for Fault-Tolerant Machine Development in Aerospace Applications. IEEE TIE 2010, 57, 575–583. [Google Scholar] [CrossRef]

- Zhou, H.; Zhao, W.; Liu, G.; Cheng, R.; Xie, Y. Remedial Field-Oriented Control of Five-Phase Fault-Tolerant Permanent-Magnet Motor by Using Reduced-Order Transformation Matrices. IEEE TIE 2017, 64, 169–178. [Google Scholar] [CrossRef]

- Steurer, M.; Edrington, C.S.; Sloderbeck, M.; Ren, W.; Langston, J. A Megawatt-Scale Power Hardware-in-the-Loop Simulation Setup for Motor Drives. IEEE Trans. Ind. Electron. 2010, 57, 1254–1260. [Google Scholar] [CrossRef]

- Hazra, S.; Shrivastav, A.S.; Gujarati, A.; Bhattacharya, S. Dynamic emulation of oscillating wave energy converter. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 1860–1865. [Google Scholar] [CrossRef]

- Kesler, M.; Ozdemir, E.; Kisacikoglu, M.C.; Tolbert, L.M. Power Converter-Based Three-Phase Non-linear Load Emulator for a Hardware Testbed System. IEEE Trans. Power Electron. 2014, 29, 5806–5812. [Google Scholar] [CrossRef]

- Chai, E.; Celanovic, I.; Poon, J. Validation of Frequency- and Time-domain Fidelity of an Ultra-low Latency Hardware-in-the-Loop (HIL) Emulator. In Proceedings of the 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), Salt Lake City, UT, USA, 23–26 June 2013; pp. 1–5. [Google Scholar] [CrossRef]

- Pietrusewicz, K. Metamodelling for Design of Mechatronic and Cyber-Physical Systems. Appl. Sci. 2019, 9, 376. [Google Scholar] [CrossRef]

- Dassios, I.; Keane, A.; Cuffe, P. Calculating Nodal Voltages Using the Admittance Matrix Spectrum of an Electrical Network. Mathematics 2019, 7, 106. [Google Scholar] [CrossRef]

- Sun, Y.; Tang, X.; Zhang, G.; Miao, F.; Wang, P. Dynamic Power Flow Cascading Failure Analysis of Wind Power Integration with Complex Network Theory. Energies 2018, 11, 63. [Google Scholar] [CrossRef]

- Arboleya, P.; González-Morán, C.; Coto, M. Unbalanced Power Flow in Distribution Systems With Embedded Transformers Using the Complex Theory in αβ0 Stationary Reference Frame. IEEE Trans. Power Syst. 2014, 29, 1012–1022. [Google Scholar] [CrossRef]

- Zhang, L.; Abur, A. Single and Double Edge Cutset Identification in Large Scale Power Networks. IEEE Trans. Power Syst. 2012, 27, 510–516. [Google Scholar] [CrossRef]

- Wang, C.; Zhang, T.; Luo, F.; Li, P.; Yao, L. Fault Incidence Matrix Based Reliability Evaluation Method for Complex Distribution System. IEEE Trans. Power Syst. 2018, 33, 6736–6745. [Google Scholar] [CrossRef]

- Saleh, M.; Esa, Y.; Mohamed, A. Applications of Complex Network Analysis in Electric Power Systems. Energies 2018, 11, 1381. [Google Scholar] [CrossRef]

- Ma, F.; O’Hare, G.M.P.; Zhang, T.; O’Grady, M.J. Model Property Based Material Balance and Energy Conservation Analysis for Process Industry Energy Transfer Systems. Energies 2015, 8, 12283–12303. [Google Scholar] [CrossRef]

- Mostacciuolo, E.; Vasca, F.; Baccari, S. Differential Algebraic Equations and Averaged Models for Switched Capacitor Converters with State Jumps. IEEE Trans. Power Electron. 2018, 33, 3472–3483. [Google Scholar] [CrossRef]

- Dörfler, F.; Simpson-Porco, J.W.; Bullo, F. Electrical Networks and Algebraic Graph Theory: Models, Properties, and Applications. Proc. IEEE 2018, 106, 977–1005. [Google Scholar] [CrossRef]

- Chen, R.R.; Davis, M. Network Laws and Theorems. In The Circuit and Filters Handbook; Chen, W.-K., Ed.; CRC Press LLC: Boca Raton, FL, USA; London, UK; New York, NY, USA; ashington, DC, USA, 2003; pp. 529–583. [Google Scholar]

- Milanovic, M. PWM spectrum evaluation and over-modulation phenomena in a three-phase inverters-analytical approach. In Proceedings of the 2008 13th International Power Electronics and Motion Control Conference, Poznan, Poland, 1–3 September 2008; pp. 301–306. [Google Scholar]

- Eisenack, H.; Hofmeister, H. Digitale Nachbildung von elektrischen Netzwerken mit Dioden und Thyristoren. Archiv far Elektrotechnik 1972, 55, 32–43. [Google Scholar] [CrossRef]

- Mohagheghi, E.; Gabash, A.; Li, P. A Framework for Real-Time Optimal Power Flow under Wind Energy Penetration. Energies 2017, 10, 535. [Google Scholar] [CrossRef]

- Mohagheghi, E.; Gabash, A.; Alramlaw, M.; Li, P. Real-time optimal power flow with reactive power dispatch of wind stations using a reconciliation algorithm. Renew. Energy 2018, 126, 509–523. [Google Scholar] [CrossRef]

| Gate Signals | ||||

|---|---|---|---|---|

| # | Error | ||||||

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | x | x | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | x | 0 |

| 2 | 0 | 0 | 1 | 0 | x | x | 1 |

| 3 | 0 | 0 | 1 | 1 | x | x | 1 |

| 4 | 0 | 1 | 0 | 0 | x | 1 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | x | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | x | x | 1 |

| 8 | 1 | 0 | 0 | 0 | x | x | 1 |

| 9 | 1 | 0 | 0 | 1 | 0 | x | 0 |

| 10 | 1 | 0 | 1 | 0 | x | x | 1 |

| 11 | 1 | 0 | 1 | 1 | x | x | 1 |

| 12 | 1 | 1 | 0 | 0 | x | x | 1 |

| 13 | 1 | 1 | 0 | 1 | x | x | 1 |

| 14 | 1 | 1 | 1 | 0 | x | x | 1 |

| 15 | 1 | 1 | 1 | 1 | x | x | 1 |

| Gate Signals | ||

|---|---|---|

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Marguč, J.; Truntič, M.; Rodič, M.; Milanovič, M. FPGA Based Real-Time Emulation System for Power Electronics Converters. Energies 2019, 12, 969. https://doi.org/10.3390/en12060969

Marguč J, Truntič M, Rodič M, Milanovič M. FPGA Based Real-Time Emulation System for Power Electronics Converters. Energies. 2019; 12(6):969. https://doi.org/10.3390/en12060969

Chicago/Turabian StyleMarguč, Jaka, Mitja Truntič, Miran Rodič, and Miro Milanovič. 2019. "FPGA Based Real-Time Emulation System for Power Electronics Converters" Energies 12, no. 6: 969. https://doi.org/10.3390/en12060969

APA StyleMarguč, J., Truntič, M., Rodič, M., & Milanovič, M. (2019). FPGA Based Real-Time Emulation System for Power Electronics Converters. Energies, 12(6), 969. https://doi.org/10.3390/en12060969