1. Introduction

The use of rectifiers operating with high power factor (HPF) is a mandatory issue today in AC-DC conversion [

1]. This fact reduces the negative impact on the power quality of AC distribution networks caused by the increasing introduction of new energy processing technologies such as electric mobility and efficient lighting, among others. For example, hybrid electric vehicles need battery chargers, which must not only provide high power density and plug-and-play operation [

2], but also meet the requirements of the power quality international standards. In the same context, it is possible to integrate the HPF rectification function in multi-mode converters, which can provide bidirectional power transfer capability or multiple power conversion types (AC-DC, DC-DC, and DC-AC), which eventually has an important impact on the power density of the converter in the electric vehicle [

3]. At lower power levels, HPF rectifiers allow improving the input power quality and the general performance of LED lamps, which currently constitute the leading lighting technology in the market [

4].

Utilization of HPF rectifiers is also fundamental in the newest applications related to feeding DC loads [

5], DC distribution, and microgrids. On the basis of the high efficiency and flexibility of the low voltage direct current (LVDC) distribution systems [

6], HPF rectifiers take part of the main DC source because they incorporate control systems that can help to meet the strict requirements of grid compatibility, safety [

7], and power quality [

8]. This type of power distribution is also currently integrated in microgrids, which constitutes a popular research topic in several industrial electronics areas [

9]. Hybrid or AC-DC microgrids are extensively used and are supplied from renewable resources such as photovoltaic and wind, besides AC sources, namely, either the AC mains, electric machines, or fuel generators [

10]. Although bidirectional power flow is a desired feature in many applications, unidirectional power flow is efficiently used in wind power integration, speed regulation, plug-in electric vehicles, and other two-quadrant applications [

11]. In all cases, it is intended that the AC powered devices accomplish the international power quality standards in terms of total harmonic distortion (THD) and power factor [

12].

The HPF rectifiers can be classified in a simple way as isolated and non-isolated. Non-isolated topologies, in turn, can be classified regarding the use of diode bridges. In particular, if a topology does not require one or more diode bridges, it is denominated bridgeless [

13]. The bridgeless topologies generally exhibit a better performance because the number of semiconductor elements in a circulating current path is low. The conventional bridgeless single ended primary inductor converter (SEPIC) was presented by Ismail et al. [

14], providing the basis for subsequent works developed by the same authors. This converter was studied in the work of [

15] in discontinuous conduction mode (DCM), which resulted in a relatively simple control and a reduced size of the components at the expense of increased stress in semiconductors. More recently, in the works of [

16,

17], the bridgeless SEPIC rectifier topology was modified by adding multiplier cells in order to extend the operational input voltage range. Although the efficiency in the work of [

16] was considerably improved (values above 98%), no increased performance was reported in the power quality indicators such as THD and power factor.

Although galvanic isolation between the AC source and DC distribution bus is not a mandatory issue in HPF rectifiers, it is clear that this feature can contribute to improving the system reliability, especially when the use of DC distribution buses implies the interconnection of multiple sources, different loads, and ancillary elements. For that reason, there is a particular interest in the development of HPF rectifiers with isolated topologies. For example, in the works of [

18,

19], an isolated rectifier topology is obtained by means of a special configuration of low-frequency transformers (Scott transformer), in which two separated bridge rectifiers based on either boost or buck converters are used to feed a split DC-bus. In another paper [

20], isolation is obtained by integrating two isolated Cûk rectifiers configuring a bridgeless topology. A relevant feature of that configuration is the use of coupled inductors operating at high frequency, which eventually results in a significant improvement in the cost, size, and weight of the converter in comparison with the use of low-frequency transformers.

Different isolated architectures based on the SEPIC converter have been proposed in the literature for HPF rectifiers. An interesting alternative with interleaved configuration and a bridge- based SEPIC rectifier topology is presented in the work of [

21], attaining unity power factor for a wide range of the output voltage. Nonetheless, the reported THD increases up to nearly 10% for some operation conditions. The isolation in that case is provided by a second conversion stage based on an LLC converter. Also, an active clamp topology operating in both continuous conduction mode (CCM) and DCM has been reported another paper [

22], showing an acceptable performance at the expense of an additional input filter and high current stress in semiconductors. The three-phase architecture of isolated SEPIC rectifier presented in the work of [

23] uses three high- frequency transformers and three bridge-based bidirectional switches, improving the performance of the single-phase bridgeless SEPIC rectifier. In the latter work, DCM operation is used to obtain a THD of 4% and unity power factor. However, the mentioned parameters were not evaluated in the entire range of operation rated for the converter. It is worth mentioning that the resulting efficiency in the aforementioned cases ranges from 75% to 90%.

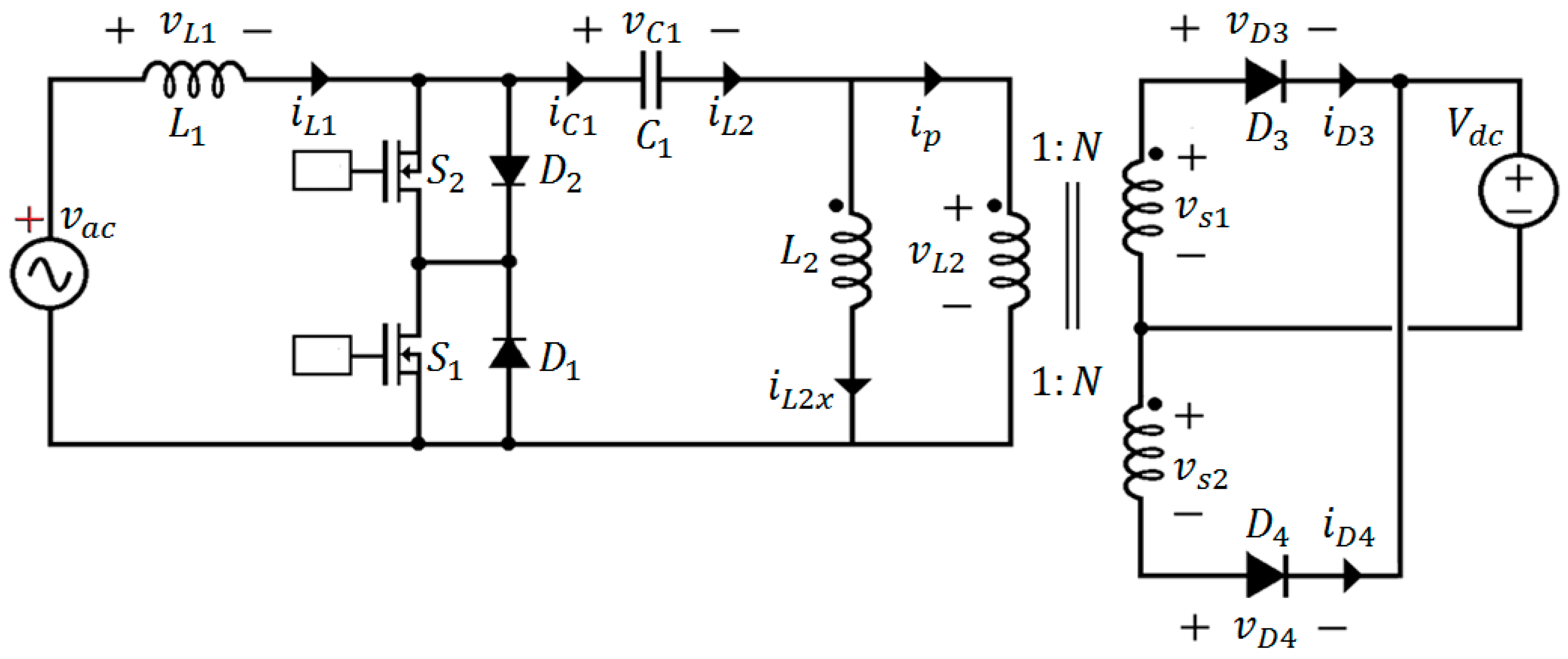

The bridgeless configuration of the HPF SEPIC rectifier depicted in

Figure 1 has been presented in the work of [

24], working at constant switching frequency, which is imposed by a pulse width modulation (PWM) operation in the control loop. Besides the galvanic isolation, the authors of that work have highlighted the relatively low number of components and the low levels of resulting Electro Magnetic Interference (EMI) as the main advantages of the topology. The main features in the isolated version of the SEPIC converter are as follows: (i) the existence of a series inductor in the input port imposing a continuous behavior to the input current, (ii) the capability to either step-up or step-down the input voltage, and (iii) the enhancement of the input voltage range with respect to other topologies.

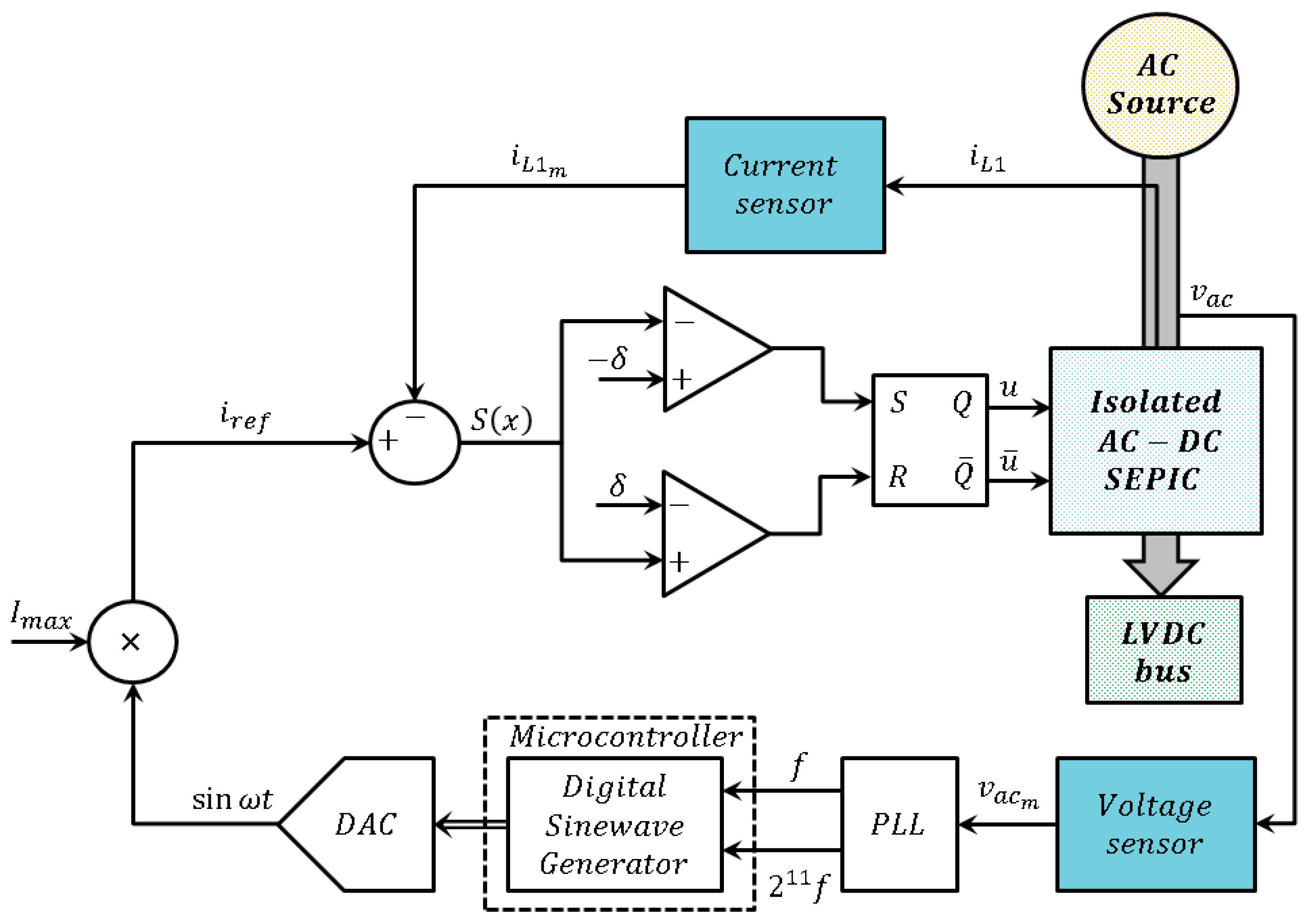

The control of HPF rectifiers based on the SEPIC converter can be easily implemented using continuous-time linear methods and PWM. The wave-shaping, as defined by Tanitteerapan et al. in the literature [

25,

26], leads to low values of THD, while a good reference generation method allows achieving power factor correction. This is carried out by an inner control loop that normally processes the input current and is complemented by an outer loop regulating the output voltage in the case of rectifiers operating as pre-regulators. In addition, discrete-time control techniques such as repetitive control have been applied to control the SEPIC rectifier [

27]. With this technique, the THD is high at low power levels, but enters in the permissive range for 50% of the nominal power, which suggests that there is still an important gap to improve the rectifier performance in terms of THD. Besides, in the work of [

28], a linear control approach is compared with a feedback linearization technique, demonstrating a better performance of the linear technique in power factor and THD for nominal power. The nonlinear technique shows a slightly advantageous performance by regarding the THD distribution along the whole range of the converter power. In the same work, the robustness of the control system is improved by applying an adaptive passivity-based feedback linearization approach.

Sliding-mode control (SMC) has been also applied to control the SEPIC rectifier using a PWM implementation [

29]. The power factor obtained with this technique in always higher than 0.97, while the current THD is only lower than 5% around the nominal power. It can be observed again that the decrease of the THD is an open problem in the SEPIC rectifier.

SMC using a hysteresis implementation results in variable switching frequency, but offers robustness, fast response, reliability, and simple implementation using either analog or digital electronics. It has been demonstrated that this technique is able to track periodic references, forcing loss-free resistor behavior. This implies resistive behavior at the input port and power source behavior at the output port of a power converter [

30], which in fact transforms the set rectifier-load into a virtual resistance, as it is successfully developed for a semi-bridge-less pre-regulator in the work of [

31] and a three-phase HPF Vienna rectifier in the work of [

32]. As in the case of the grid-connected inverters, the control must track a reference, which can be directly provided by a measurement of the input voltage or indirectly by a synchronized reference generator [

33]. On the other hand, as the output voltage of the rectifier (voltage of the DC bus) is not regulated, the power injected into the DC bus is given by the amplitude of the input current. This amplitude is in turn provided by an outer control loop that can be a part of a high-level layer of hierarchical control architectures [

34].

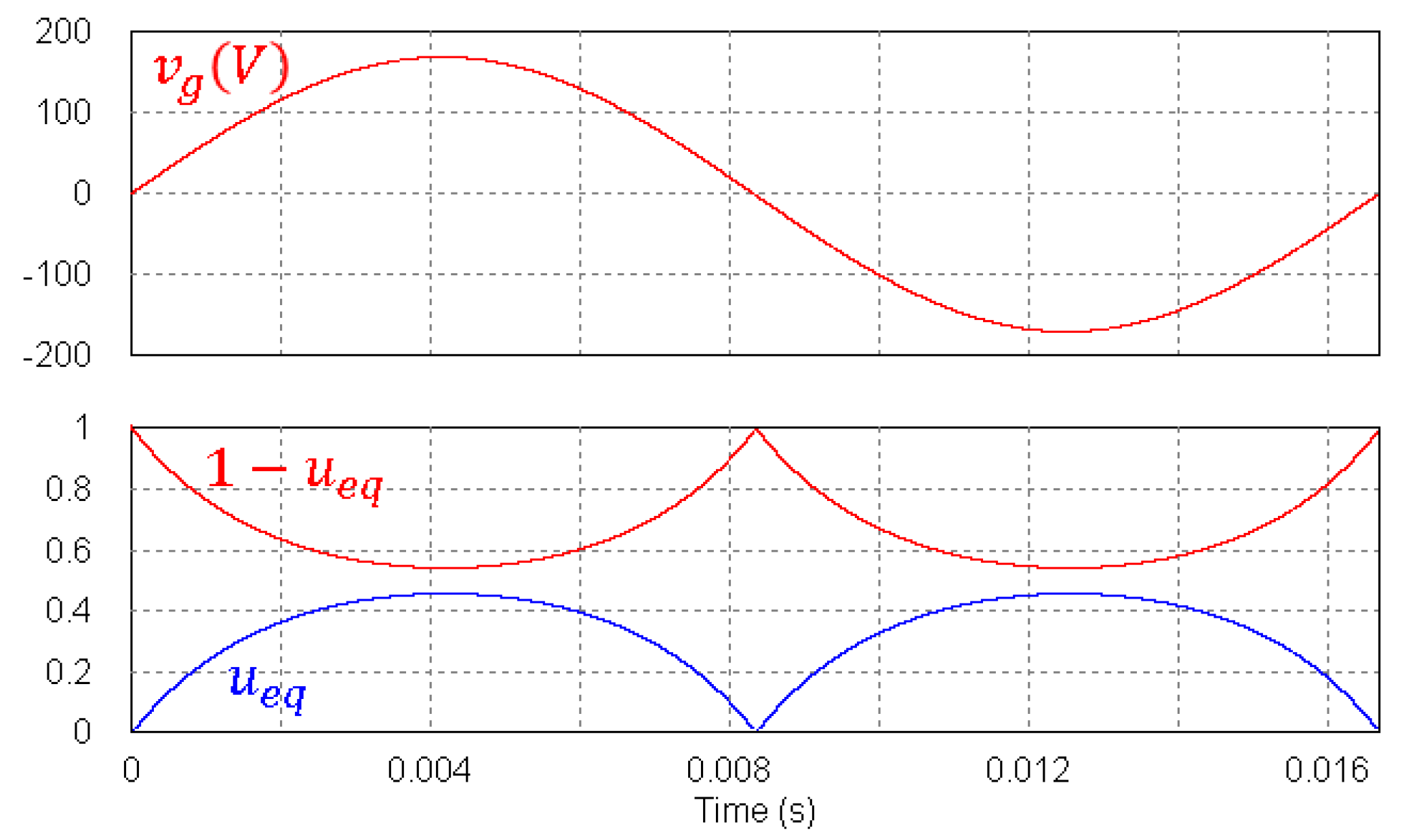

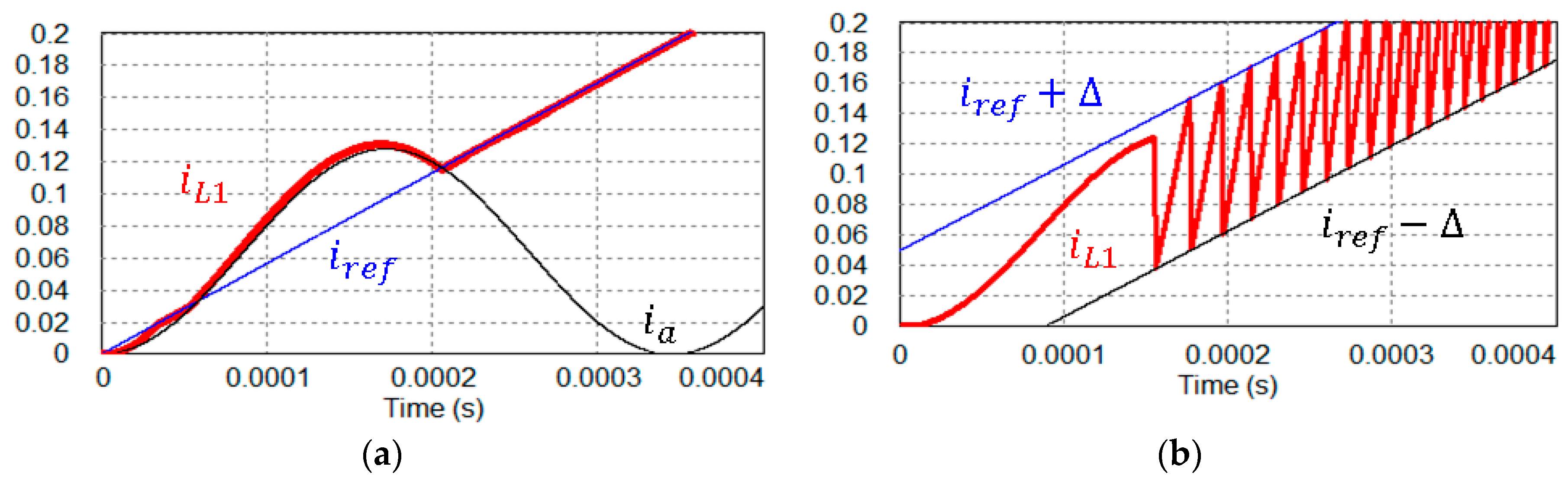

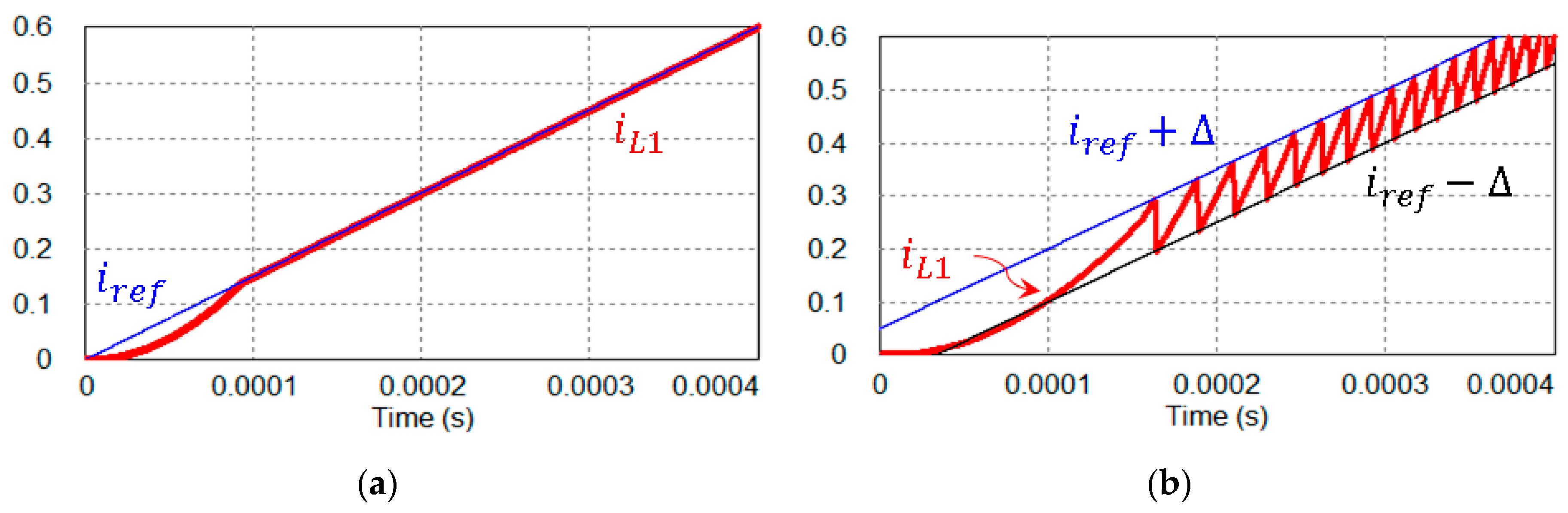

The main goal of this work is to apply a hysteresis-based implementation of the sliding mode control approach to improve the performance of the isolated SEPIC converter, increasing the range of power in which the international standards are fulfilled.

Unlike the approach in the work of [

24], the SEPIC converter analyzed in this paper feeds a non-resistive load and operates at a variable switching frequency. The first constraint has not been studied in any of the reported SEPIC-based rectifier topologies. More specifically, the main differences of the topology depicted in

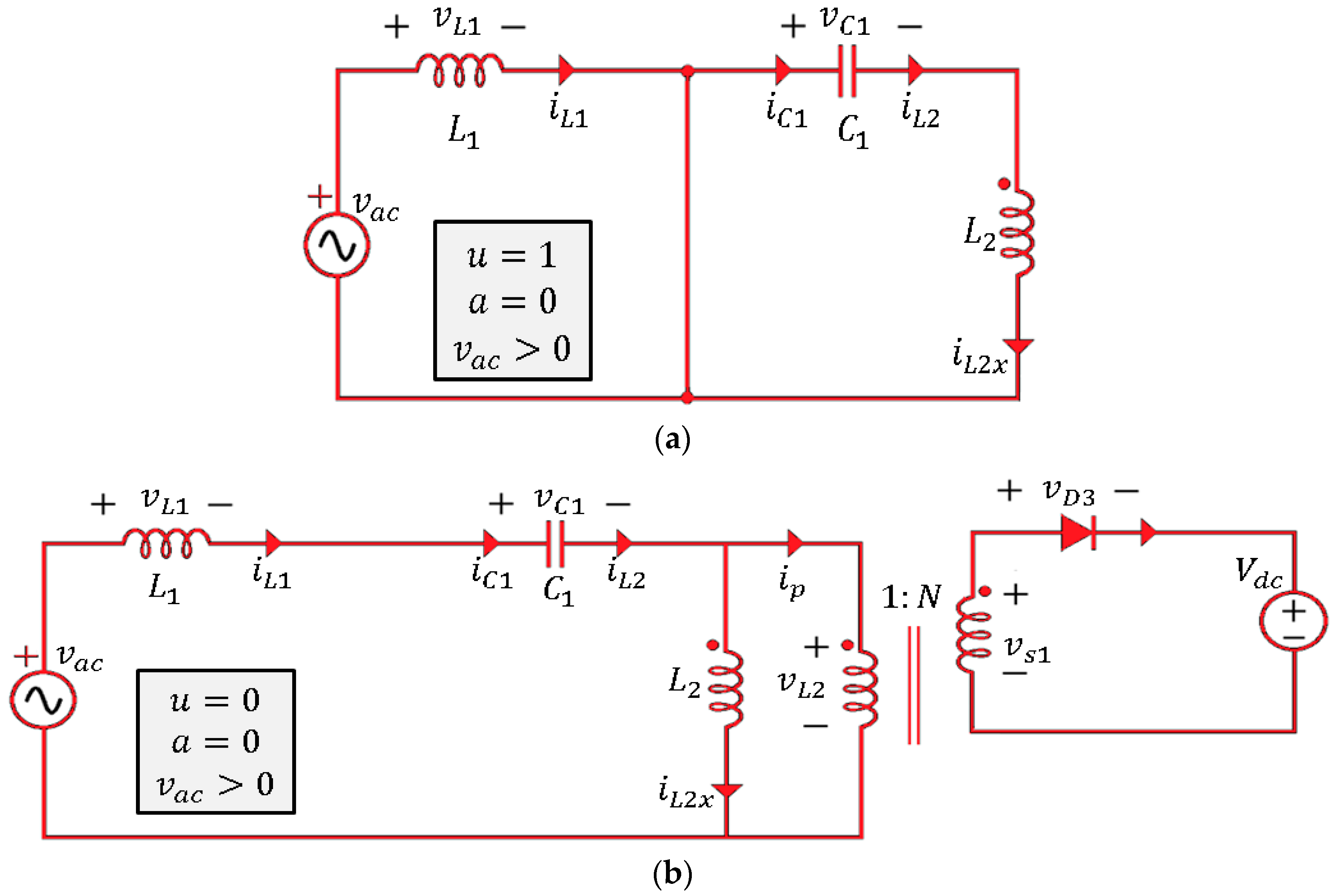

Figure 1 with respect to the conventional SEPIC are as follows:

- -

The single controlled switch was changed by a bidirectional switch (, ) providing control for voltage and current in both half-cycles of the grid voltage.

- -

A transformer with three windings, the first one being the primary, replaces the second inductor. The secondary is split in two identical windings, which are interconnected through a central tap. The transformer ratio is 1:N.

- -

No output capacitor is used because the converter is directly connected to a voltage regulated DC bus.

Moreover, this paper considers the sliding mode-based current control of a bridgeless isolated SEPIC rectifier tracking a sinusoidal reference and injecting power to an LVDC bus without considering additional control outer loops. The rest of the paper is organized as follows. Modeling and analysis of the sliding-mode current control are developed in

Section 2. The implementation of the proposed control is described in

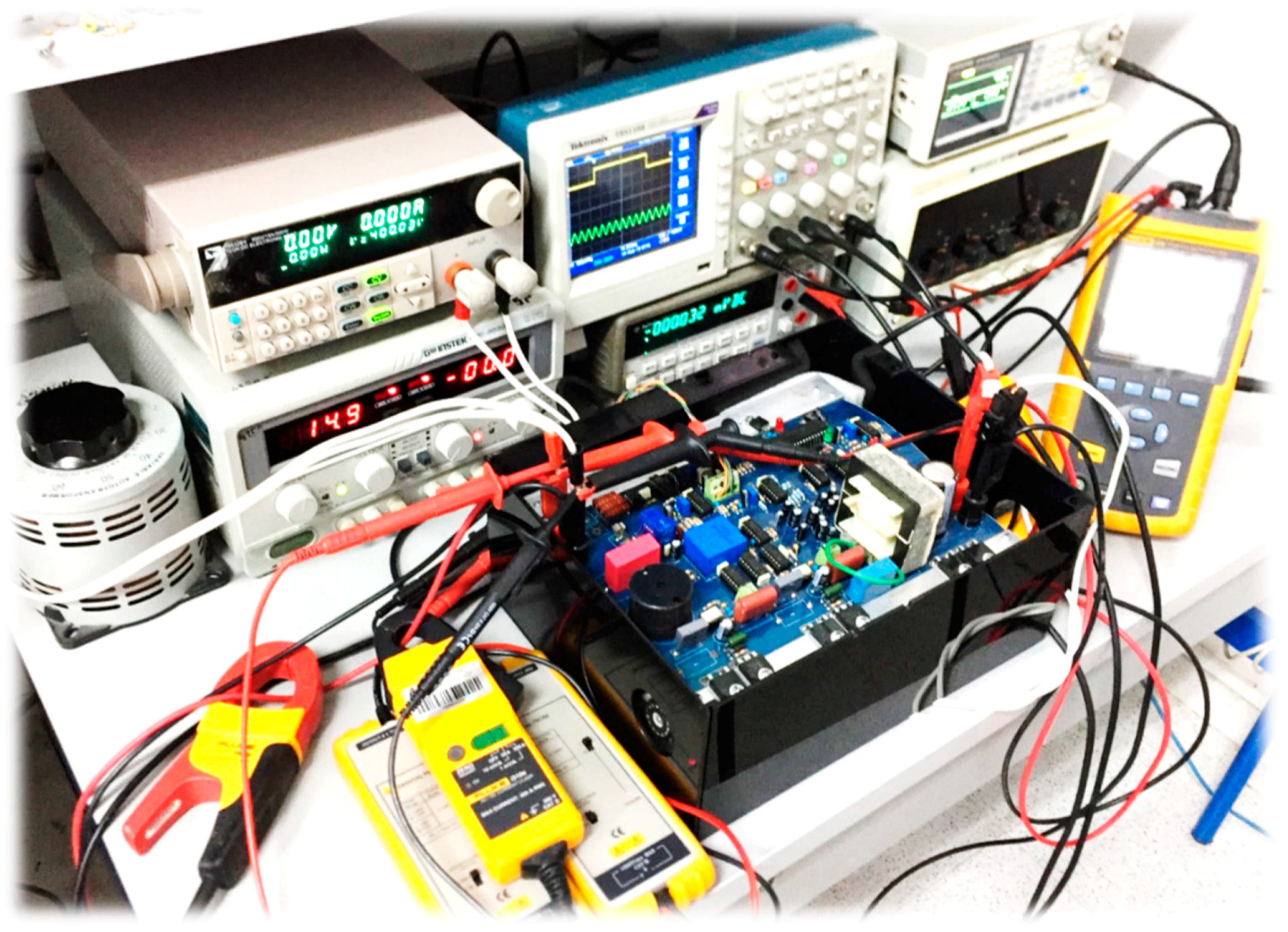

Section 3. Simulation and experimental results are shown in

Section 4. Finally, conclusions are given in

Section 5.

5. Conclusions

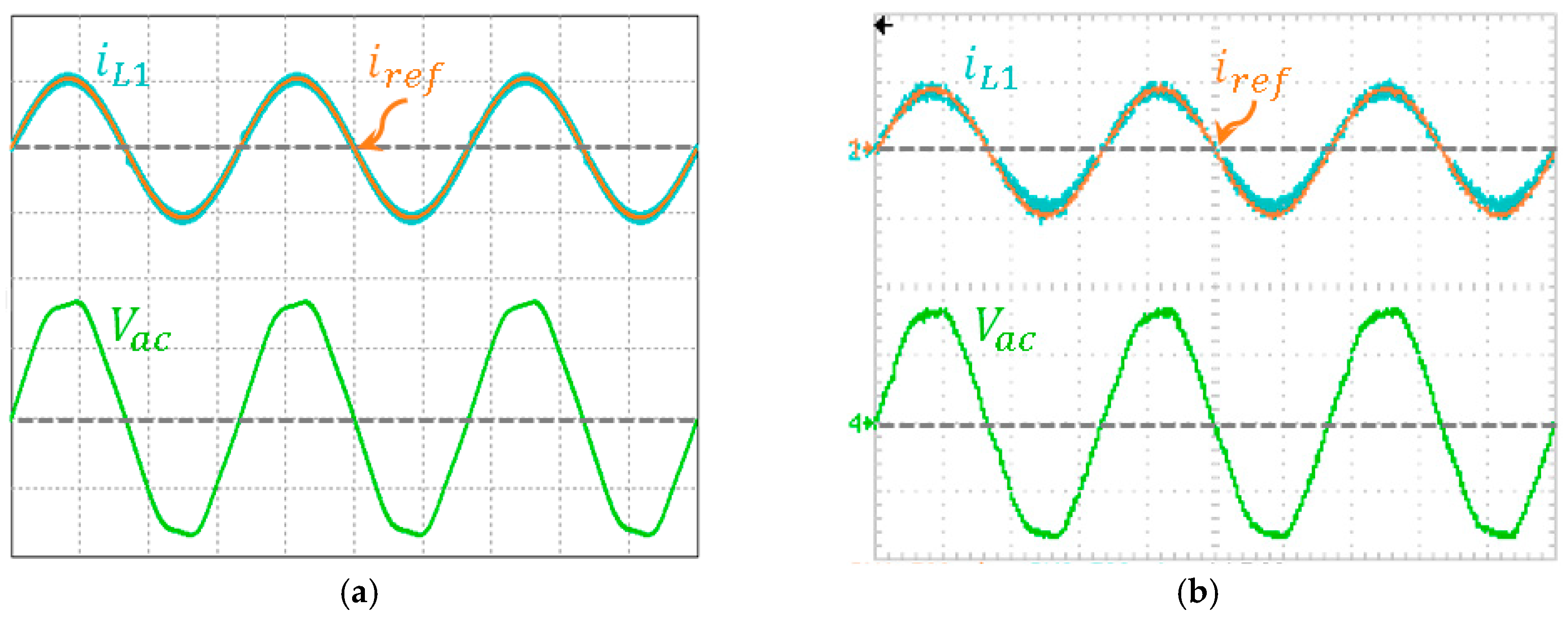

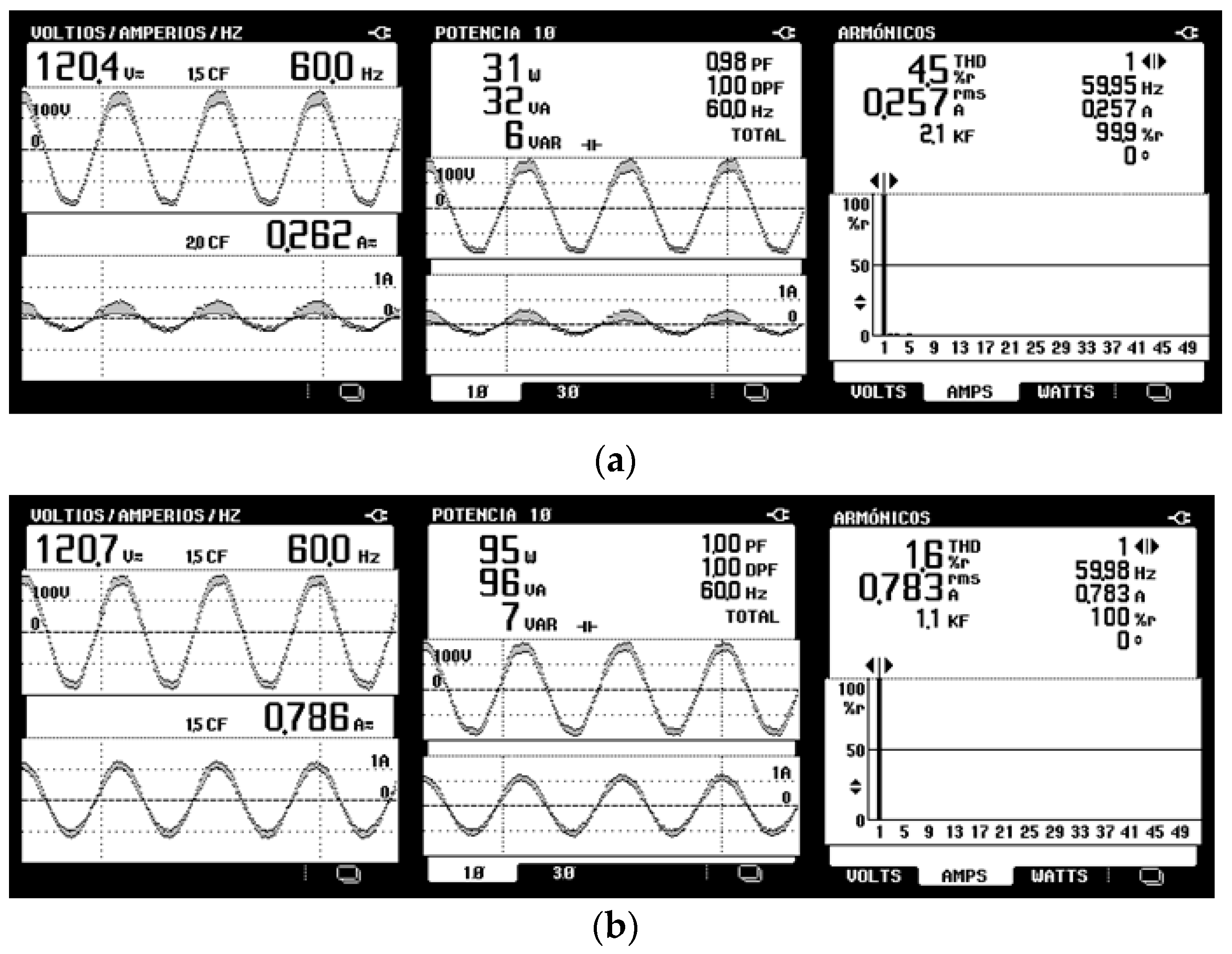

In this paper, the modeling and nonlinear control of the isolated bridgeless SEPIC rectifier interfacing an AC source with an LVDC bus were presented. The use of a hysteresis-based sliding mode control approach to ensure the tracking of a high quality current reference yielded very satisfactory results. A simple sliding surface allowed us to ensure high power quality and robustness in the isolated SEPIC rectifier with an easy electronic implementation. The correct operation of the proposed control was validated using several simulation and experimental results. It was demonstrated that the proposed solution exhibits adequate performance in power quality indicators such as THD always being lower than 3.5% (1.6% for the best case) and a PF higher than 0.95 (0.99 for the best case).

The simplicity of the implementation and the low levels of THD demonstrated that the proposed control method is comparable to the best strategies reported in the literature. Hence, the studied SEPIC converter with the proposed control is a promising alternative for the insertion of HPFs in emerging energy processing applications.

Moreover, the analysis carried out in the paper tackled—for the first time—the behavior of the isolated SEPIC circuit at zero crossing points. This additional mode cannot be considered as a trivial finding, because it differs from the known behavior of the conventional SEPIC topology used in DC–DC conversion. Nonetheless, in spite of the existence of this additional mode, the proposed sliding mode controller results to be immune to it because, after a brief dwell time in that mode, the sliding surface is quickly attained.

Our future work contemplates the study of the converter control when the coupled inductor operates in discontinuous conduction mode. This would introduce a substantial theoretical difference for the sliding motion, but it could result practically in important advantages in both the whole performance and converter power density.