1. Introduction

Model predictive control (MPC) has become an attractive alternative for controlling power electronic applications, such as motor drives and power converters [

1]. There are two main categories of MPC: (1) continuous MPC (CMPC), in which output is generated and delivered to a modulator, and (2) finite-set MPC (FS-MPC), which can control a finite number of feasible switching states using a predefined cost function [

2,

3,

4,

5]. Among the two types, FS-MPC is preferable, owing to its many advantages, such as the fast dynamic response, intuitive appeal, inclusion of constraints and nonlinearities, and easy implementation. However, an important drawback of the original method is its variable switching frequency and large current ripples, which requires the use of large passive filter components [

2,

6].

Numerous studies aiming to improve the performance of classical FS-MPC for both power converters and motor drives have been performed. To reduce current ripples and alleviate harmonic distortion, an attempt was made in [

7,

8] to increase the prediction horizon of FS-MPC. Although good performance was achieved, intensive experimentation is still necessary for determination of correct weighting factors and control horizons [

8], which is computationally demanding [

9]. A deadbeat solution was suggested in Reference [

10] for a two-level voltage-source inverter, which allows the computational load of FS-MPC to be reduced by reducing the complete enumeration for the whole voltage vectors. Although this solution helped to address the problem of computational intensity, the large torque ripples could not be eliminated.

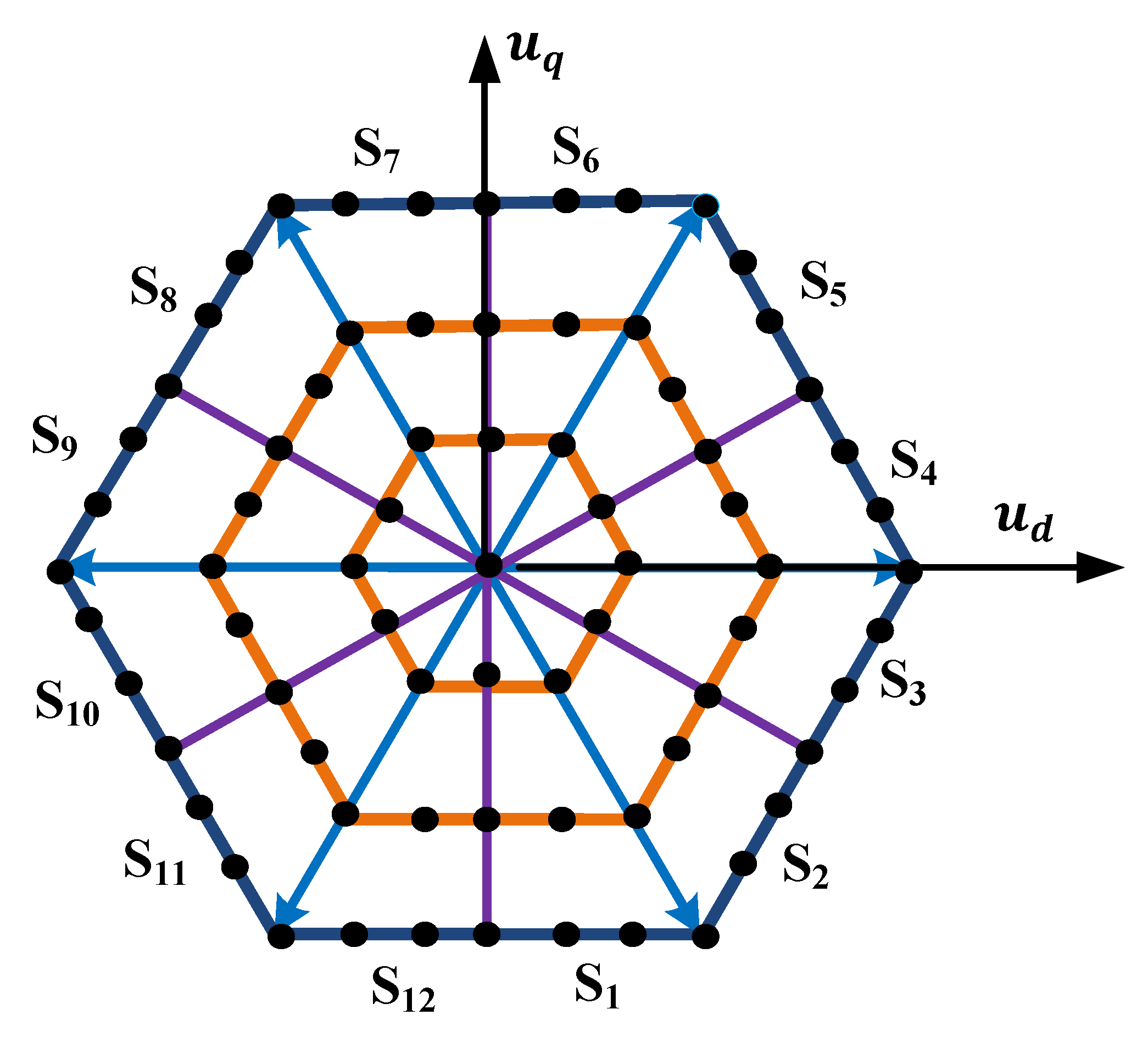

FS-MPC based on discrete space vector modulation (DSVM) was proposed in References [

11,

12] to reduce current ripples and guarantee a constant switching frequency. The main advantage of DSVM is that it allows the number of degrees of freedom to be increased by synthesizing various virtual voltage vectors in the space vector diagram [

12]. Similarly to classical FS-PTC, the optimal voltage vector is selected to minimize the objective error in the respective cost function, and is applied to the inverter using space vector modulation (SVM). Nevertheless, the main issue associated with the DSVM approach is its high computational burden, owing to a large lookup table that holds the initialized virtual voltage vectors. To solve this problem, deadbeat control was utilized to consider a limited number of virtual voltage vectors, regardless of their number [

13]. In this way, the calculation time was significantly reduced, making the method suitable for realistic applications.

Although two-level inverters (2L inverters) are extensively used for power converters and motor drives for generation of voltage vectors applied to terminals [

14], they suffer from some issues. Two-level inverters require a very high switching frequency; hence, a higher harmonic current distortion is generated, owing to the limitation of voltage levels. In addition, the maximal DC link voltage is constrained due to the rating of the semiconductors. Therefore, multilevel inverters (ML inverters) have been considered an attractive solution capable of solving the above-mentioned problems and synthesizing output voltages with several discrete levels. Three-level inverters (3L inverters), such as neutral-point clamped (NPC) and T-type inverters, are the most prominent topologies of ML inverters. Compared with 2L inverters, the number of degrees of freedom for obtaining the voltage vectors is higher, which yields better current quality and better control. Despite the advantages of 3L inverters, neutral-point voltage balancing seriously affects their control performance [

15], causing higher ripples and distortion of stator currents. Hence, 3L inverters require high-rated capacitors, owing to their unequal voltage distribution, which, in turn, results in a higher voltage stress on the semiconductor switches.

It is worth mentioning it is complicated to include a NPC voltage balance variable in the cost function when implementing DBC. Thus, an algorithm for the DC link capacitor voltage balance should be separately applied for proper 3L inverter operation [

16,

17,

18,

19,

20]. For example, in Reference [

16], a calculated zero-voltage sequence was used for neutral-point balancing, while in Reference [

18], the time-offset injection method was used for the same purpose. In Reference [

20], a deadbeat model of predictive control combined with the discrete space vector modulation method was used for grid-connected systems using T-type 3L inverters. Two cost functions were used: one for selecting the optimal voltage, and another for the compensated voltage offset, because the neutral-point voltage problem of 3L inverters cannot be included as a variable in the cost function, due to the use of DBC method. The optimal voltage vectors were then synthesized using the SVM method for the entire sampling duration. Nevertheless, the use of two cost functions increased the computational burden of the control system.

This paper proposes a simplified control method for balancing the neutral point in the FS-MPC with the DSVM and DBC of grid-connected systems. Therefore, unlike the approach in Reference [

20], the proposed method does not require additional cost functions for balancing the capacitance voltage. The proposed method led to a significant reduction in computation time while maintaining the current quality performance. This method was simulated and experimentally verified on a grid-connected, three-level T-type voltage source inverter.

2. System Modeling

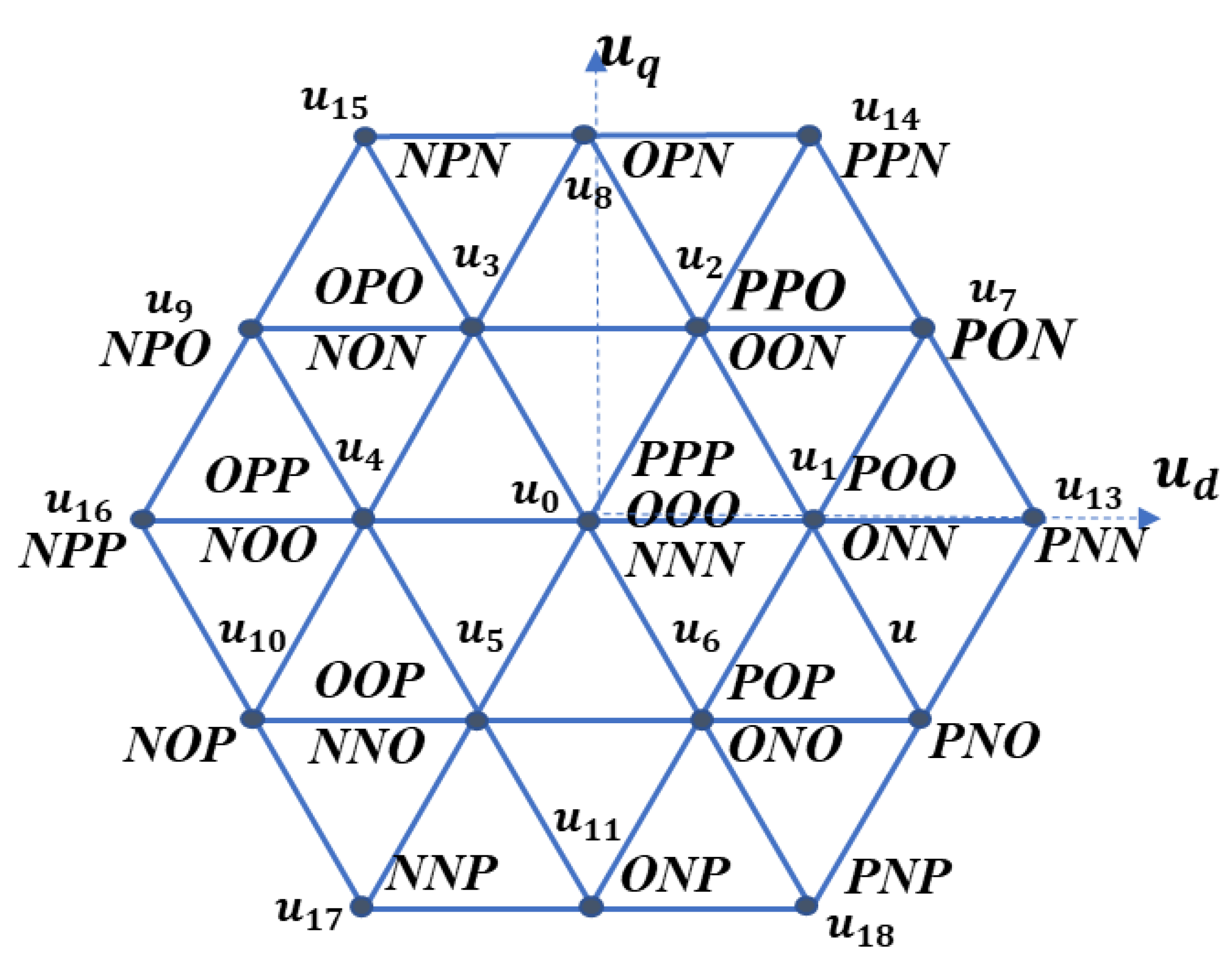

Essentially, there are three switching states for three-level topologies such as neutral-point clamped (NPC) and T-type inverters.

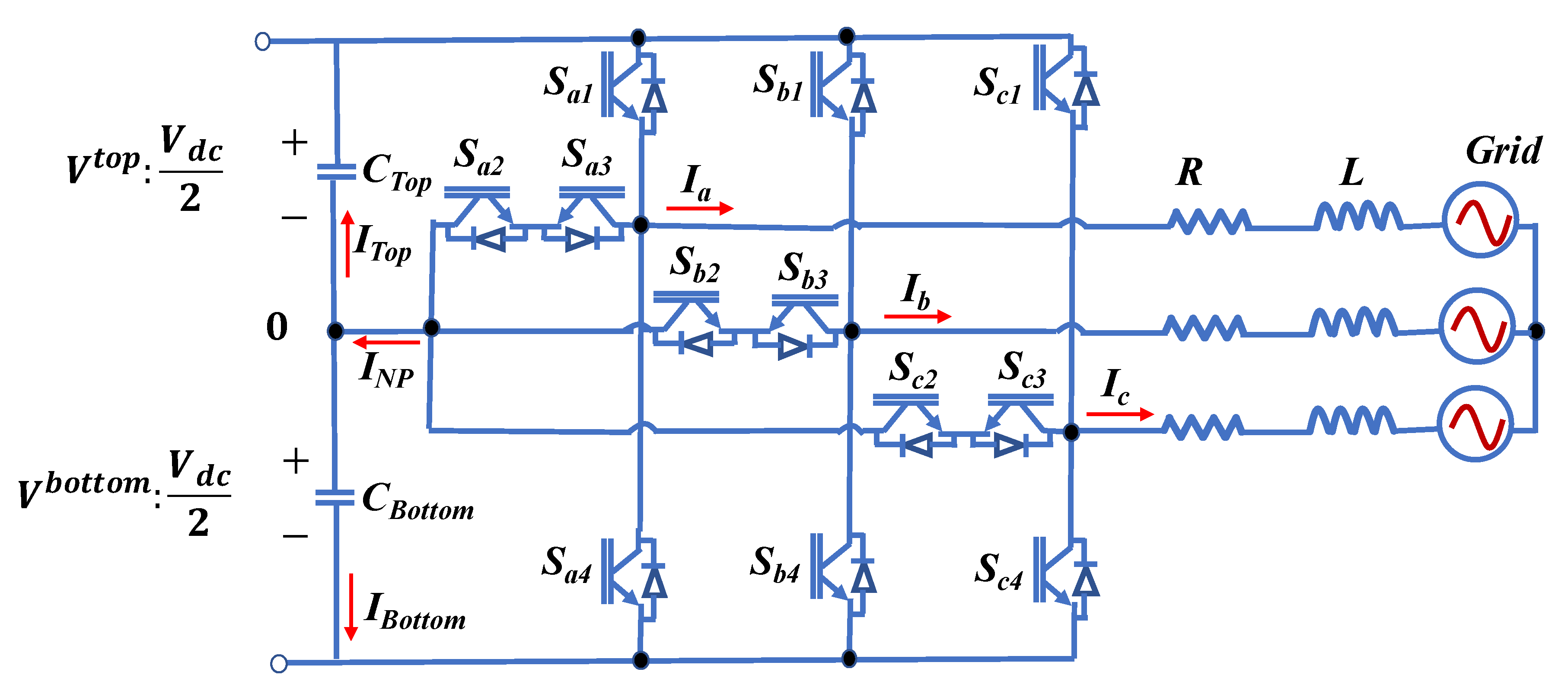

Figure 1 shows the topology of a grid-connected, three-level T-type voltage source inverter. The output poles of the T-type inverter can be connected to three different levels of the source voltage, namely the positive bus bar “

P,” the negative bus bar “

N,” and the neutral point “

0” [

21]. With three-phase to two-phase transformation, the model of the inverter in the stationary

d–q frame is given by:

In Equation (1),

R, L, u, i, and

e, are the load resistance, filter inductance, inverter voltage vector, output current vector, and grid voltage vector, respectively. Because the top capacitance voltage (

Vtop) and the bottom capacitance voltage (

Vbottom) can become unequal in the three-level voltage source inverter (VSI) (and hence will produce poor-quality output current and distorted output voltage), the capacitor voltages should be observed and taken into account at every time step, to ensure that they become balanced. The dynamic equations of the two capacitor voltages are given by:

where

C is the capacitance of each capacitor,

is the sampling time, and

INP is the neutral-point current.

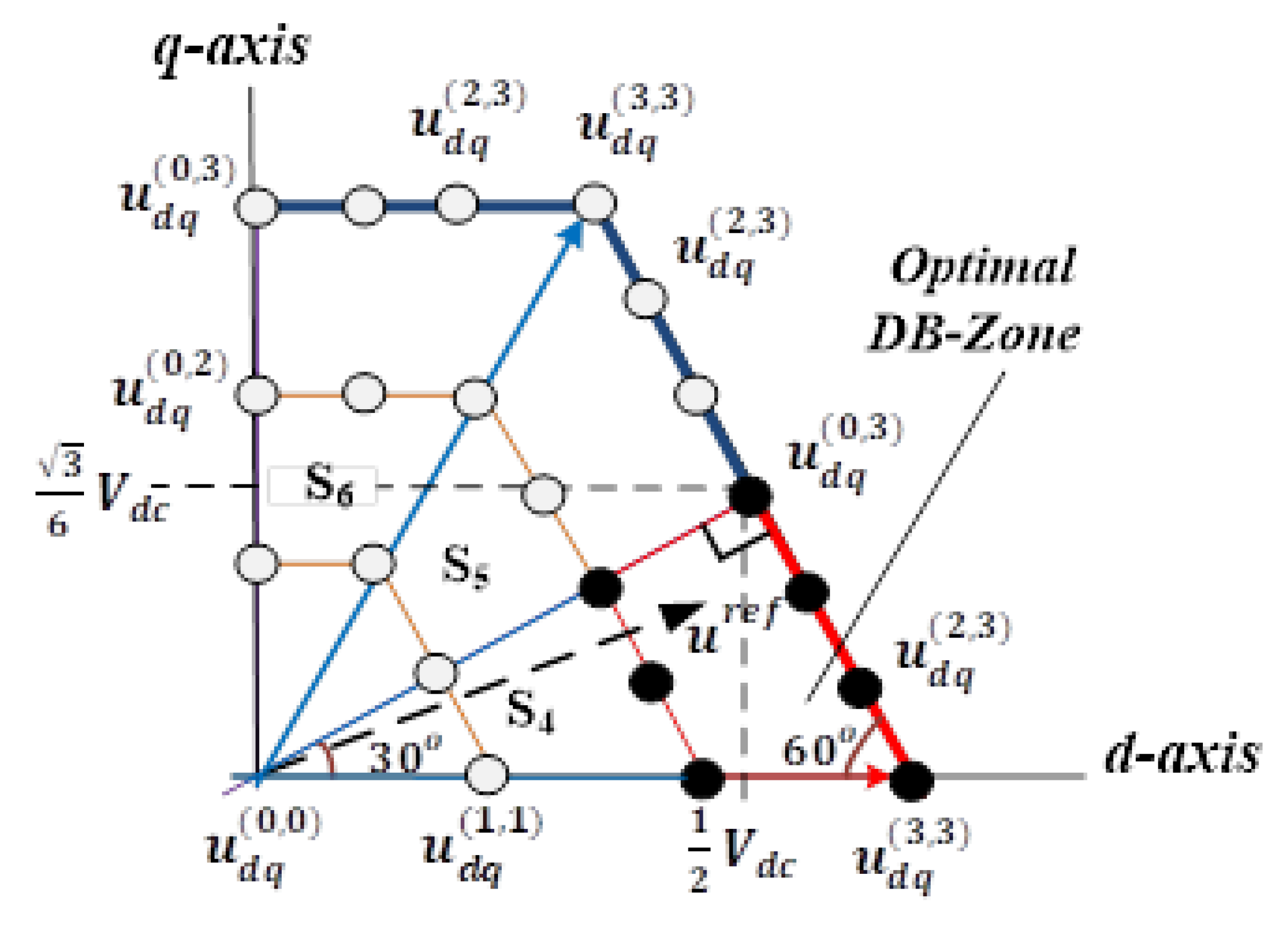

4. Deadbeat DSVM-MPC with Proposed Neural Point Balancing Method

In this paper, the deadbeat DSVM-MPC used virtual voltage vectors obtained using the DSVM strategy, and their values were calculated instantly for the current prediction [

20]. Although good performance can be obtained with deadbeat DSVM-MPC, the 3L T-type VSI topology can lead to an unbalanced neutral-point voltage, which increases the voltage stress on the switching device. It also increases the total harmonic distortion (THD) of the output current, because a low-order harmonic will appear in the output voltage. A large deviation of the DC link capacitance voltage is caused by the inconsistency in switching or imbalance of DC capacitors, owing to the manufacturing tolerance [

22].

It is worth mentioning that there are various modulation strategies to synthesize output voltages, which can be categorized into two common types: continuous-based modulation (CPWM), such as sine pulse-width modulation (SPWM), and discontinuous-based modulation, namely discontinuous pulse-width modulation (DPWM). To optimize the performance of the 3L T-type VSI system, the voltages of the in-series connected DC link capacitors should be balanced. Unlike our previous work [

20], wherein the problem of balancing the capacitor voltages was treated using a separate cost function to modify the offset voltage in SPWM (increasing the computational burden), the proposed deadbeat DSVM-MPC implements a modification in DPWM using a hysteresis capacitance voltage control. The main advantage of this proposed method is that it is straightforward and easily implemented, without additional hardware or extensive computation. Furthermore, it is known that by using DPWM, the switching losses are reduced, and better harmonic characteristics can be obtained for high modulation indices, compared with inverters that use continuous pulse-width modulation [

23,

24,

25,

26]. Although there are several different DPWM methods, conventional 60° DPWM is most commonly used for systems with the unity power factor. The idea behind the 60° DPWM method is schematically shown in

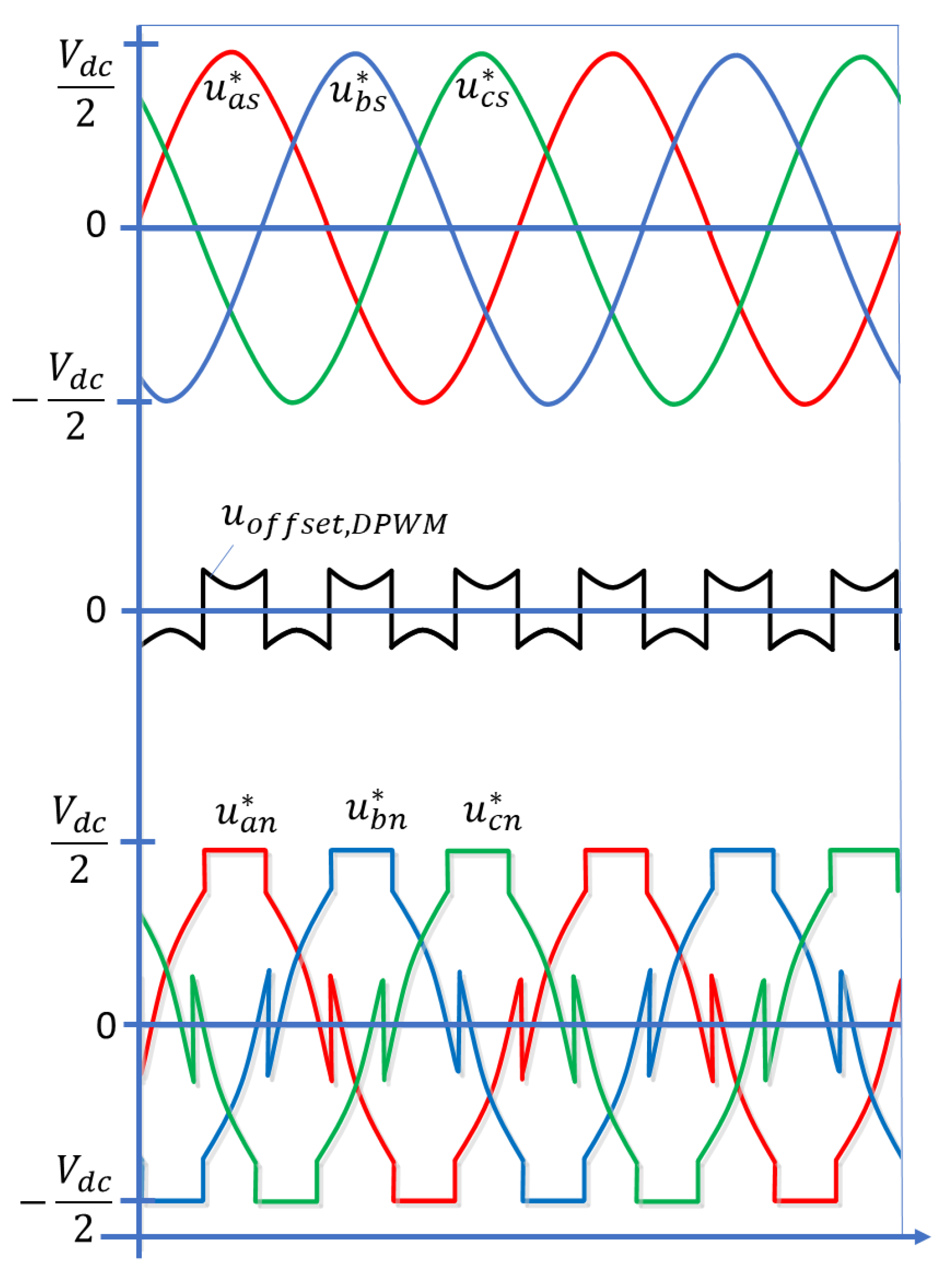

Figure 5. Therefore, the pole reference voltages to be applied to the VSI are described by:

where

u*an,

u*bn, and

u*cn are the pole reference voltages to be applied to the VSI, whereas

u*as,

u*bs, and

u*cs are the optimal reference voltages by deadbeat DSVM-MPC of each phase, respectively. The voltage

uoffset,DPWM is the offset voltage used in the DPWM, which is calculated as follows:

where

umax and

umin are, respectively, the maximum and the minimum values among the phase reference voltages.

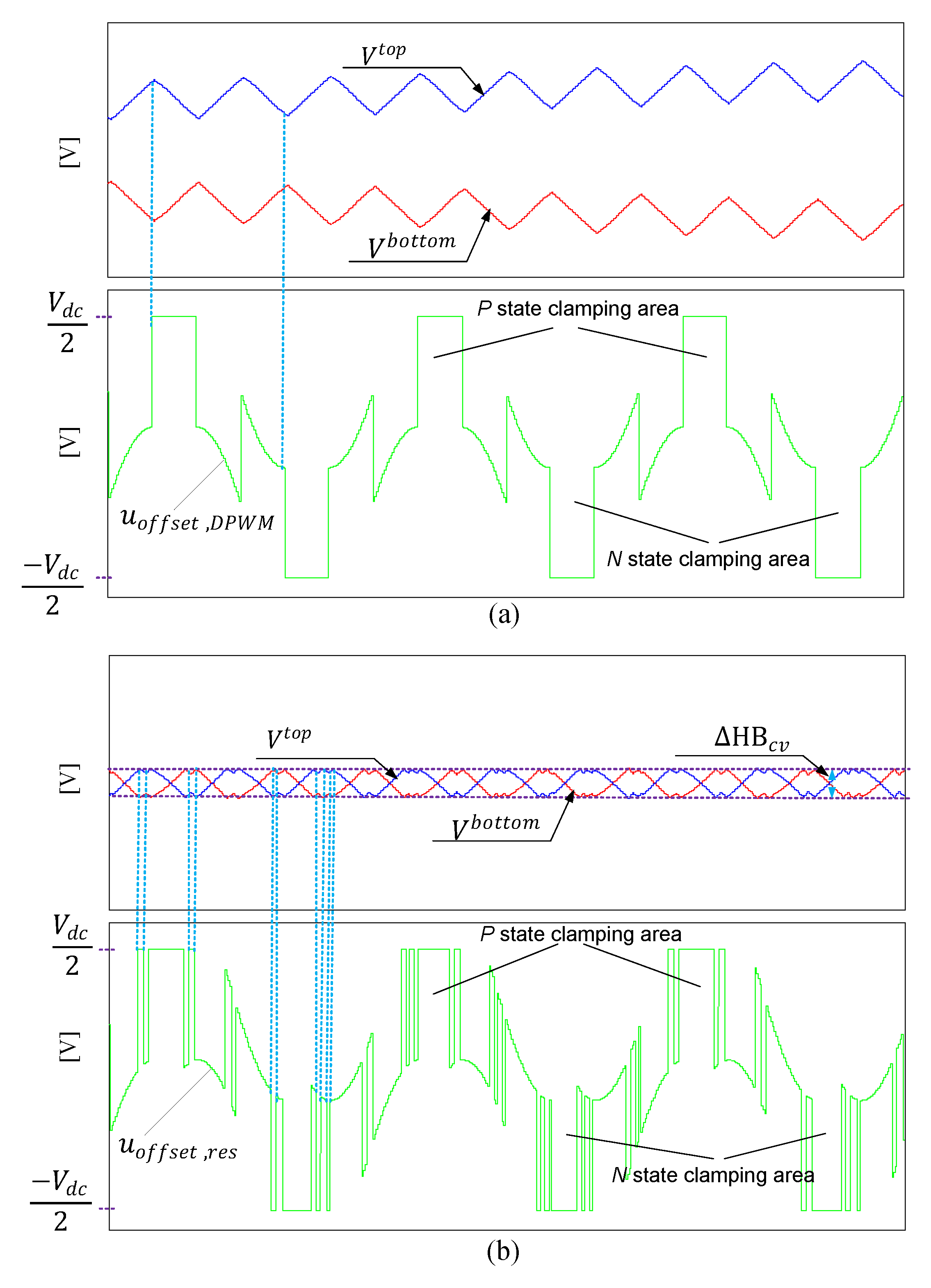

Figure 6a depicts the imbalance of the DC link capacitor voltage for the 3L T-type VSI. Note that when the switch of the either phase is locked in the P state, the top DC link capacitor voltage

Vtop is decreased and the bottom DC link capacitor voltage

Vbottom is increased. Conversely, if the switch of the same switch is locked in the N state, the top and the bottom DC link capacitor voltages are increased and decreased, respectively. Thus, clamping plays a major role in decreasing or increasing the top and bottom capacitance voltages.

Figure 6b shows the proposed DPWM method using the hysteresis capacitance voltage band (

). The proposed neutral-point voltage balancing method uses a compensated voltage offset (

uoffset,cv) depending on the top and bottom capacitor voltages in the linear modulation range. The

uoffset,cv has an opposite influence from

uoffset,DPWM on changing the direction of the top and bottom voltages, which is given as:

The proposed method seeks to maintain the advantage of diminishing the stress on transistors and minimizing the power loss, while simultaneously achieving a balanced DC link capacitance voltage with a stable and acceptable capacitance voltage error

, which is defined as

The capacitance voltage error

is inevitable; thus, it should be limited to an acceptable error band

, to avoid large deviations of the DC link capacitance voltage and high switching. The limited error band is defined as

. The resultant voltage offset (

uoffset,res) can then be designed depending on the following condition:

According to Equation (22), if the capacitance voltage error exceeds the limited error band, the uoffset,cv will be injected into the uoffset,DPWM to have an opposite effect on the clamped voltage, otherwise, the uoffset,DPWM will continue with its normal operation.

The effect of the resultant voltage offset

uoffset,res on one of the pole reference voltages to be applied to the VSI is seen in

Figure 6b. Note that the clamping areas are almost similar to the conventional DPWM; at the same time, the error of the DC link capacitance voltage is stable. In addition, there is a short clamping area injected by the

uoffset,cv to maintain the capacitance error range. It is noteworthy that the switching frequency of

uoffset,res and the non-switching area depend mainly on the setting of

; increasing the limited error band will result in a lower switching of

uoffset,res and will deteriorate the quality of the current, whereas reducing the limited error band will cause undesirable switching frequency of

uoffset,res and a small clamping area. Thus, it is recommended that the tradeoff error band limit for achieving desirable current control performance be determined.

5. Simulation Results

Simulations using the PSIM software tool were conducted to validate the proposed method. The system configuration was similar to that shown in

Figure 1. The DC link voltage (

Vdc) was 300 V, and was distributed equally between the top capacitance voltage (

Vtop) and the bottom capacitance voltage (

Vbottom). The total DC link capacitance was 2200 µF and the switching frequency was 10 kHz. The value of

was set empirically at 2.6 V. The simulation parameters are given in

Table 2. After synthesizing the reference voltage vectors with the minimized cost function using the deadbeat DSVM-MPC system, the reference voltage vector was applied to the grid-connected 3L T-type VSI.

Figure 7 shows the simulation results for the optimal voltage vectors in the

d–q frame for the deadbeat DSVM-MPC, which followed the reference current using only four candidate voltage vectors [

20].

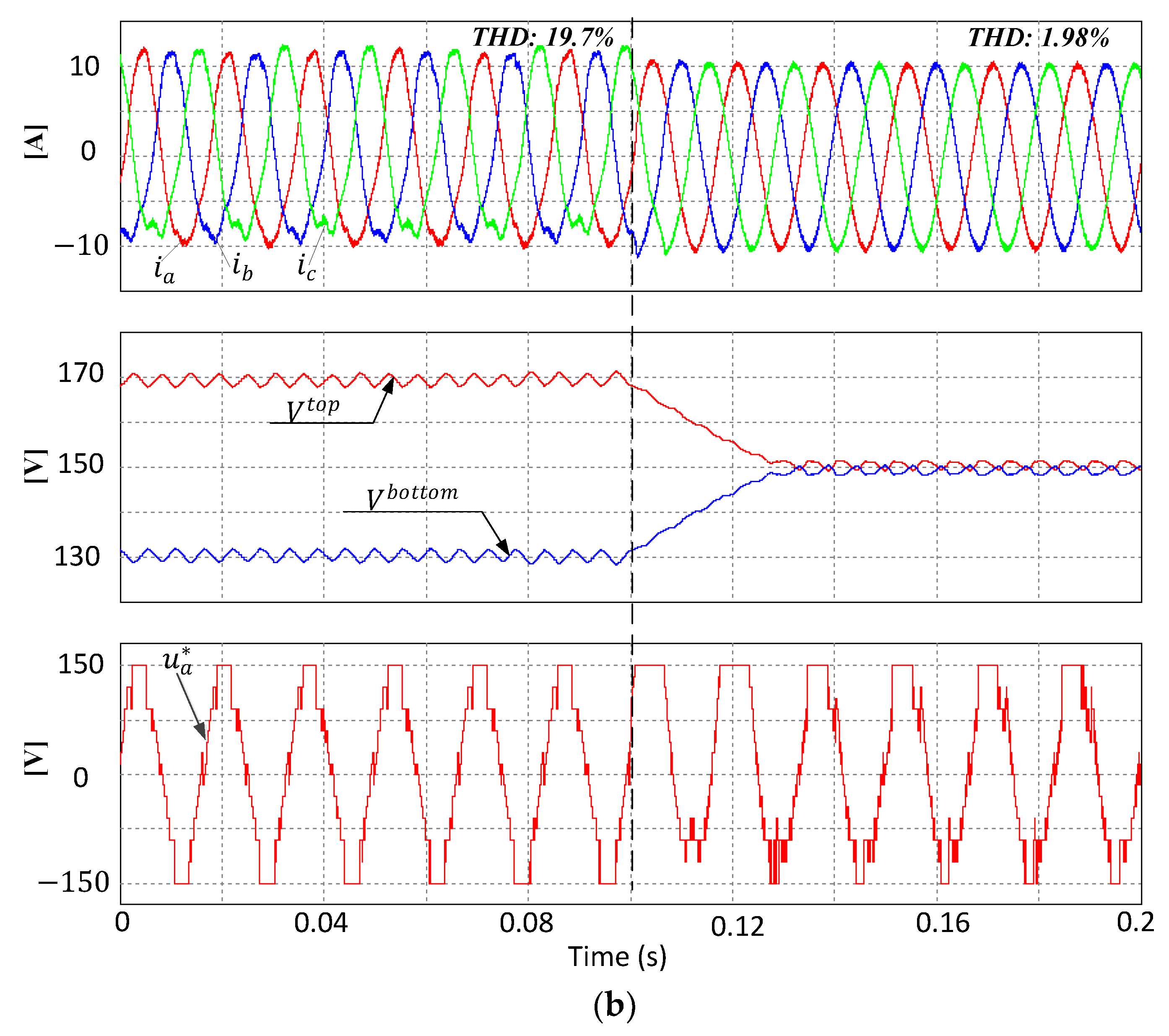

Figure 8 shows the simulation results for the deadbeat DSVM-MPC using the balancing method in Reference [

20] and using the proposed DPWM method. It can be seen that the current waveforms became highly distorted before implementation of the neutral-point balancing of capacitance voltage, owing to large voltage deviations. Obviously, the total harmonic distortion (THD was is significantly reduced using either one of the balancing methods. Nevertheless, the proposed balancing method performed better in terms of THD, as shown in

Figure 8b.

Figure 9 shows the simulation results for dynamic response for the deadbeat DSVM-MPC system, using the two balancing methods. As can be seen, both methods exhibited a fast dynamic current response, because the MPC method was used. On the other hand, the proposed method exhibited smaller THD compared with the method in Reference [

20].

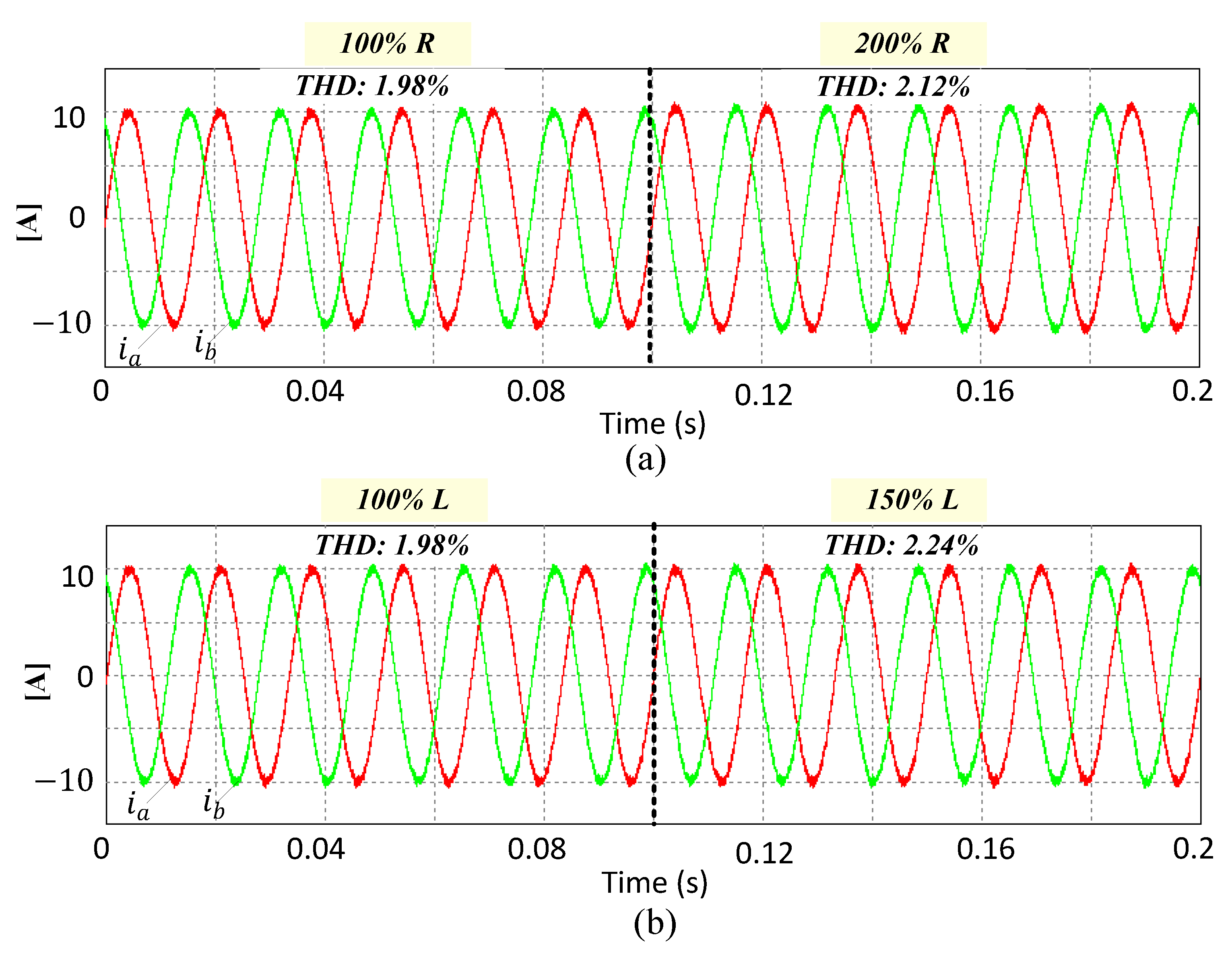

The robustness of the proposed method was shown by varying the impedances of the grid connected system including the inductance (L) and resistance (R) (

Figure 10). The values of resistance and inductance were increased (at t = 0.1 s) by 100% and 50% of the nominal values, respectively. It can be obviously seen that there was a negligible increase in the THD. Therefore, it was confirmed that the proposed balancing method in FS-MPC with DSVM and DBC is robust to the variations of impedances.

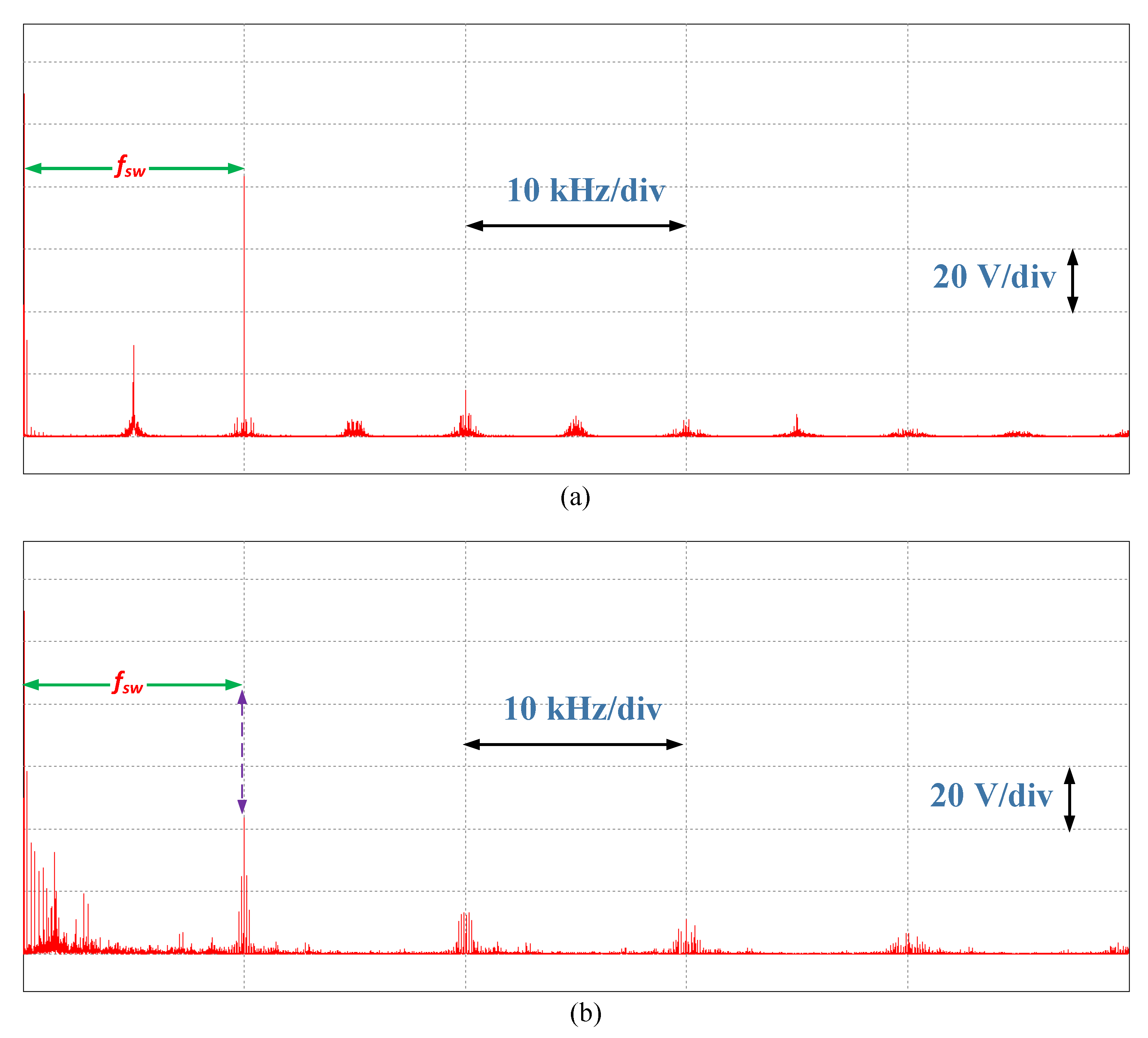

Figure 11a,b depicts the frequency spectrum of the phase voltage for the conventional method and proposed method, respectively. Apparently, the first harmonic component (i.e., switching frequency (

fsw)) was greatly reduced with the proposed algorithm, compared to the conventional method. This indicates the proposed method has less switching frequency owing to the use of the DPWM modulator, as mentioned previously.

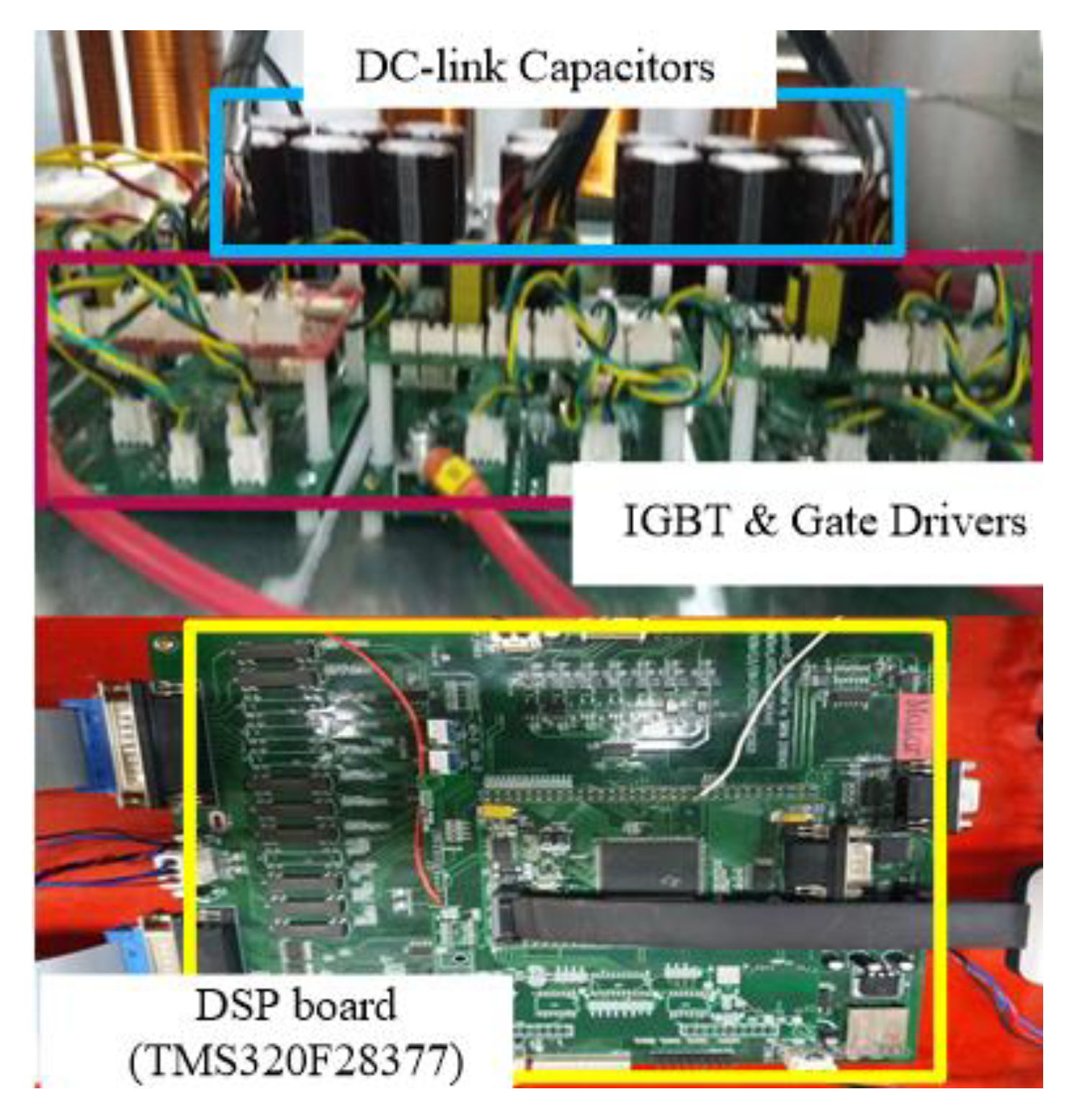

6. Experimental Results

The proposed control system was further validated on a prototype grid-connected VSI that was used in a laboratory setup, as shown in

Figure 12. The experimental parameters of the prototype were similar to those that were assumed in the simulation study, as shown in

Table 2. The control system was configured using a DSP named TMS320F28377. In addition, 10-FZ12NMA080SH01-M260F-3 from Vincotech was employed to configure the three-level inverter system. To ensure a fair comparison of these methods, the experimental conditions were the same as those that were assumed in the simulation study. Thus, the limited error band

was also set at 2.6 V, which was similar to that in the simulation. To verify the effectiveness of the proposed method in the deadbeat DSVM-MPC, it was compared against the conventional neutral-point balancing method [

20].

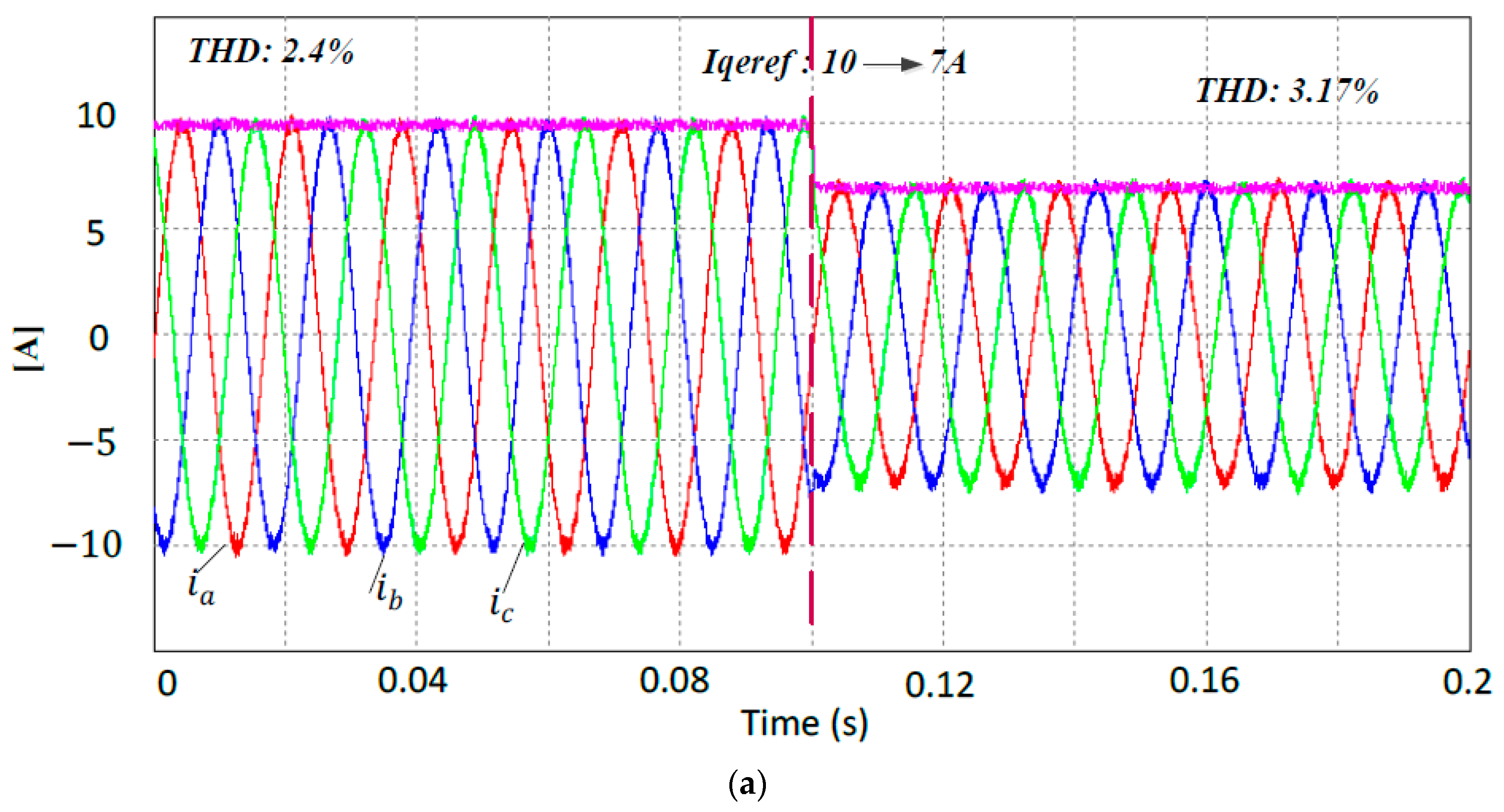

Figure 13 shows the experimental results for the grid current of the deadbeat DSVM-MPC, for both balancing methods. Similarly to the simulation results, it was observed that the proposed balancing method demonstrated a good capability of balancing the deviation of the top and bottom capacitance voltages. As can be seen, before applying either of the balancing methods, the difference between the top and bottom capacitor voltages was very high, and the output current became distorted owing to the neutral-point voltage imbalance. However, when the neutral-point voltage was balanced, the distortion of the output current disappeared.

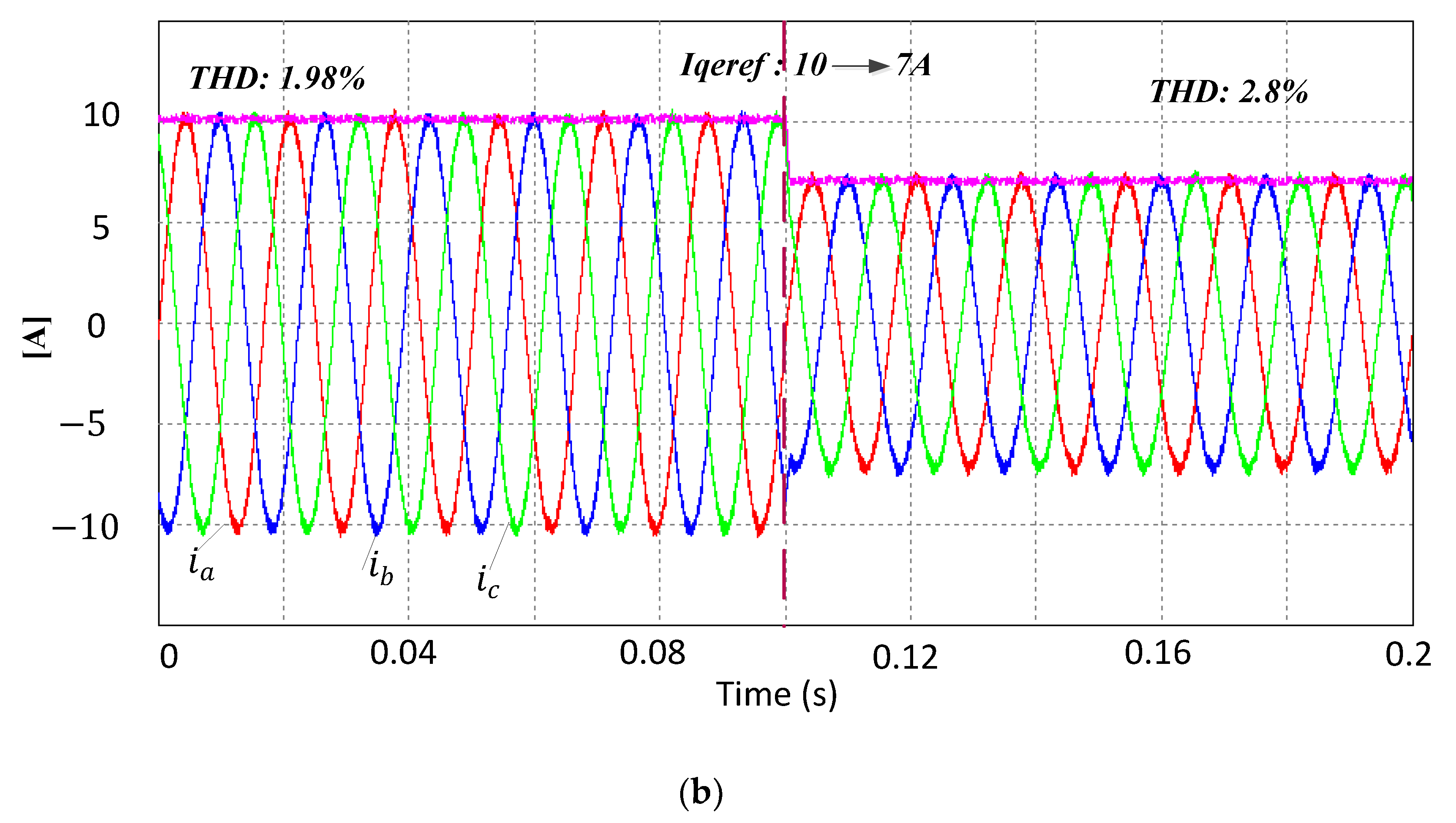

Figure 14 shows the experimental results for the dynamic current performance from 10 A to 7 A for the deadbeat DSVM-MPC system, using both the conventional and the proposed balancing methods. As can be seen, the settling time was very short because the MPC method was used. However, the proposed balancing method exhibited lower THD by around 4.9% before and after the current reference change, when compared with the conventional neutral-point balancing method [

20].

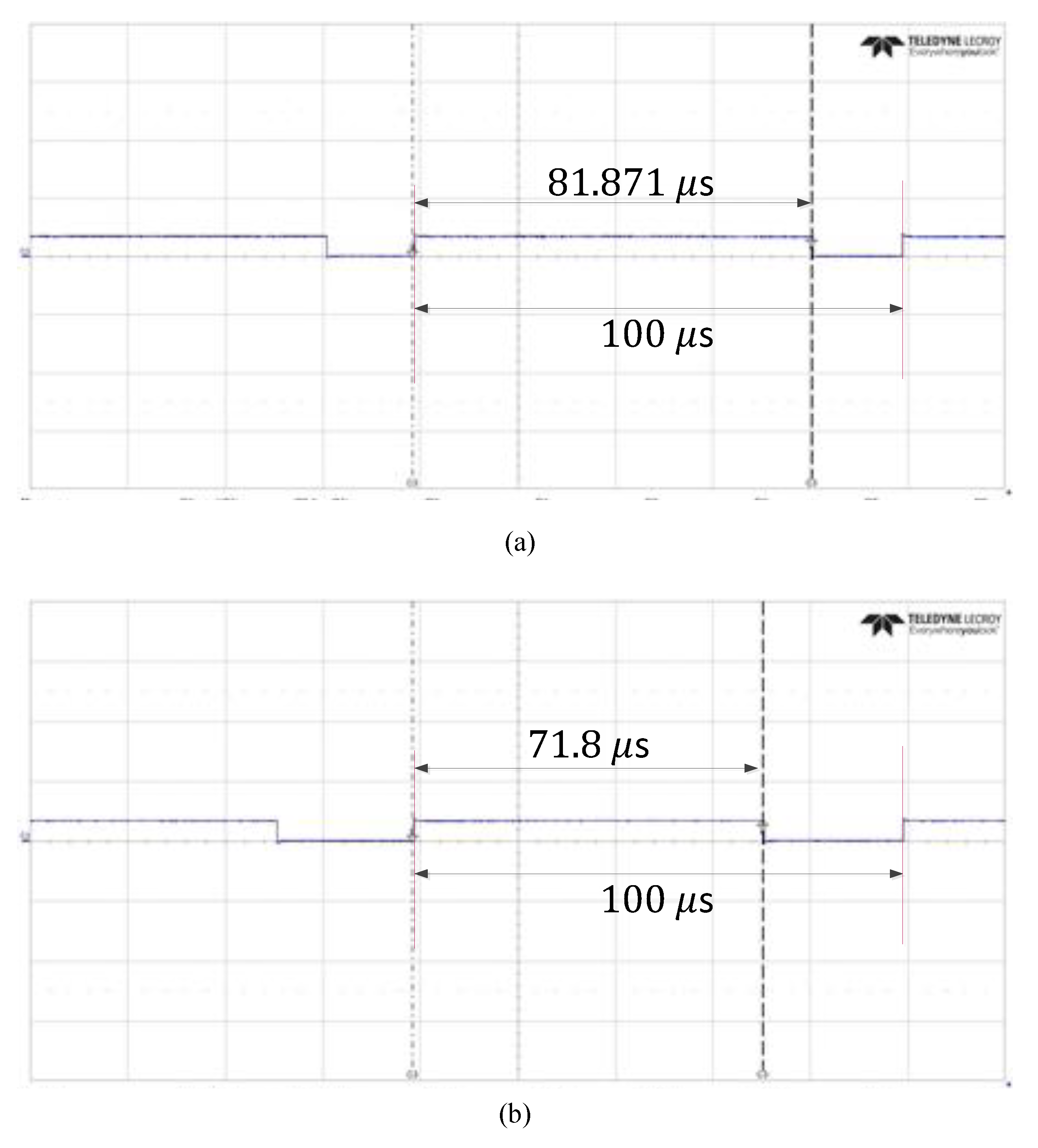

Figure 15 shows the comparison of the hardware computation time of the deadbeat DSVM-MPC system, without weighting factors, for the control method in Reference [

20] and the proposed method. As can be seen, the computation time required by the proposed deadbeat DSVM-MPC method was reduced by 12.30% when compared to the method from Reference [

20]. This indicates the simplicity of the proposed algorithm.