A Hybrid DC Circuit Breaker with Fault-Current-Limiting Capability for VSC-HVDC Transmission System

Abstract

1. Introduction

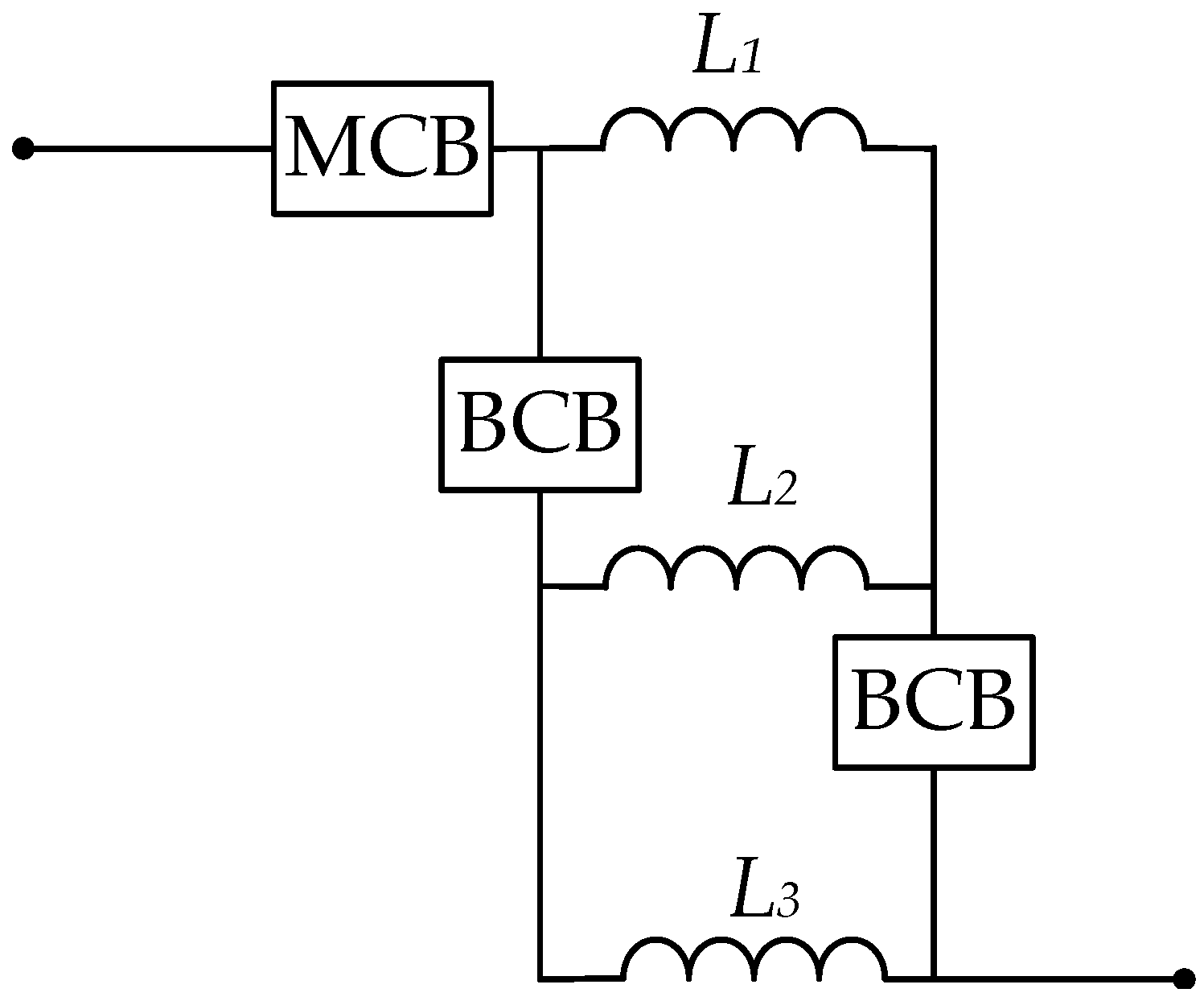

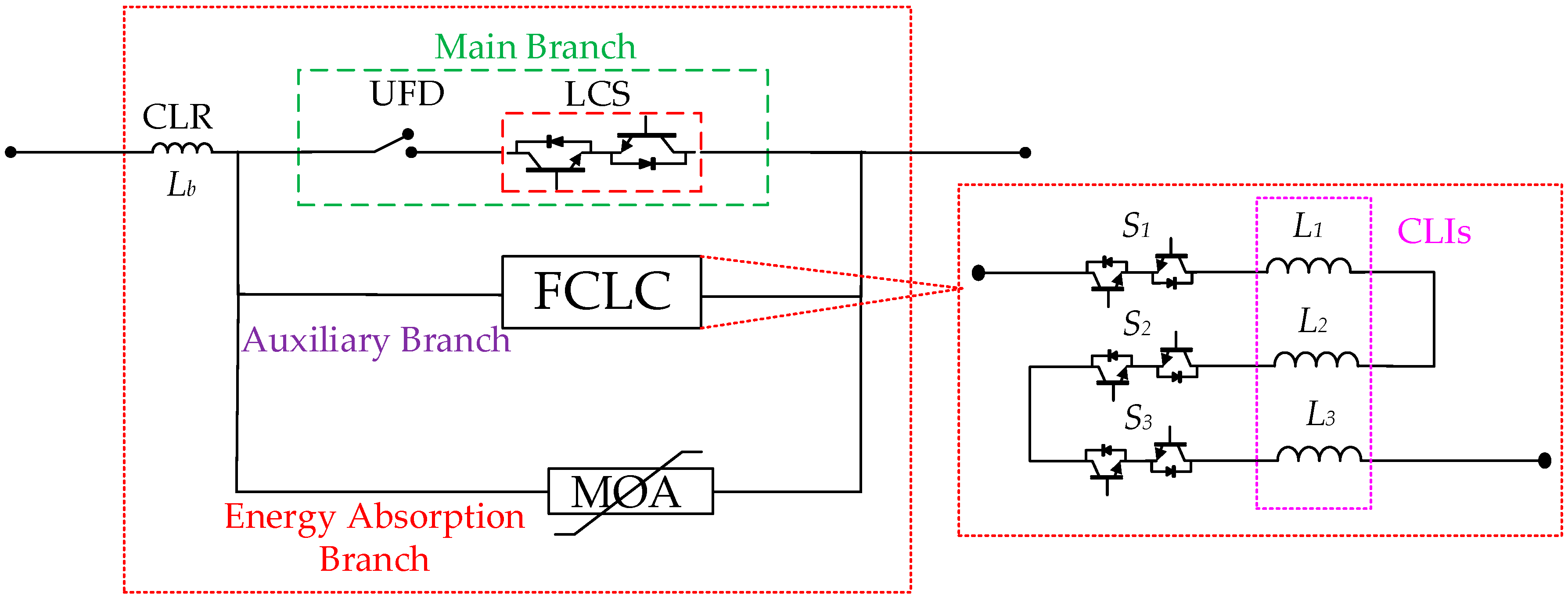

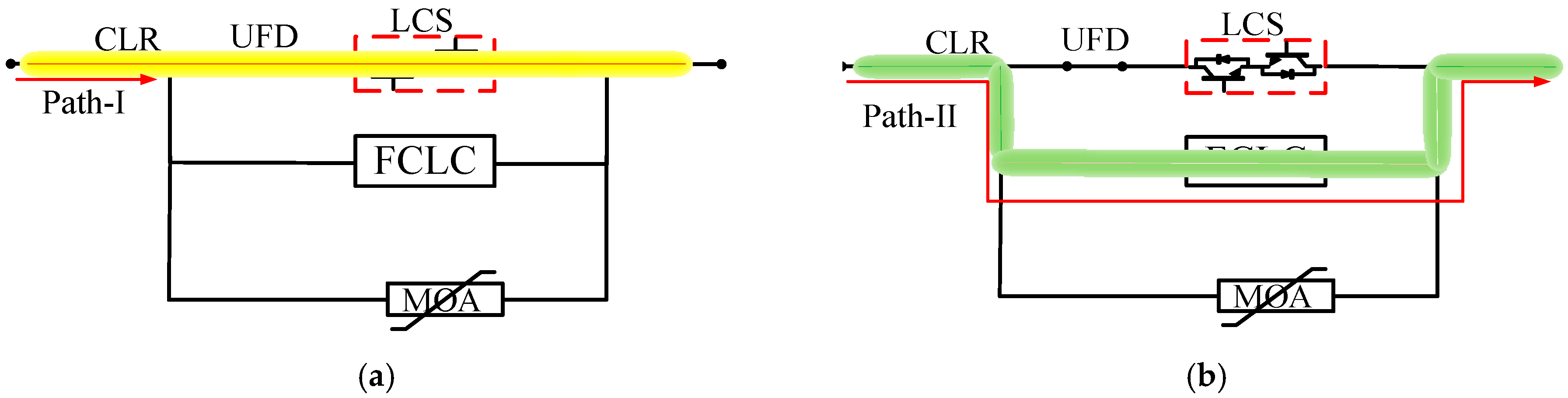

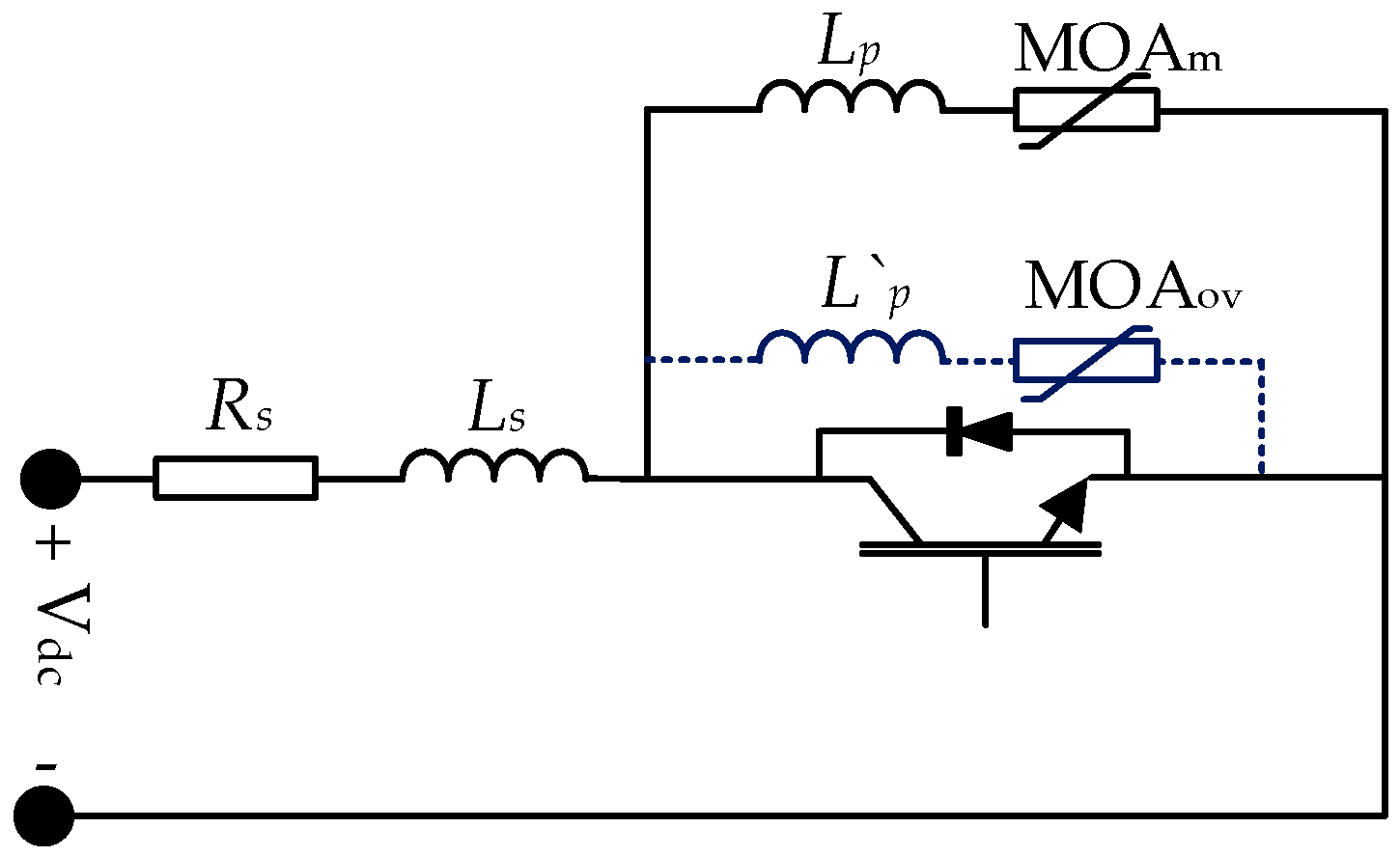

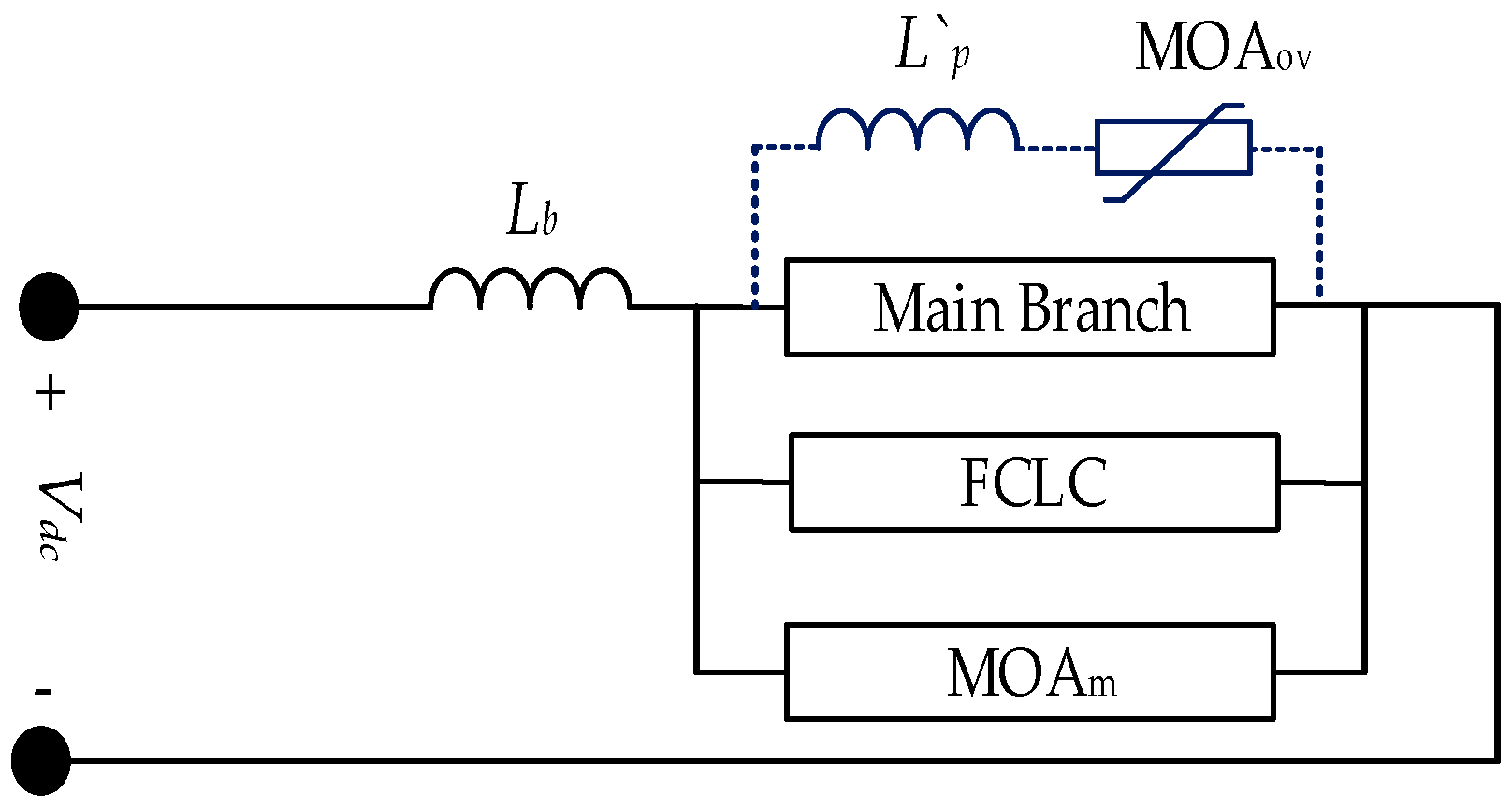

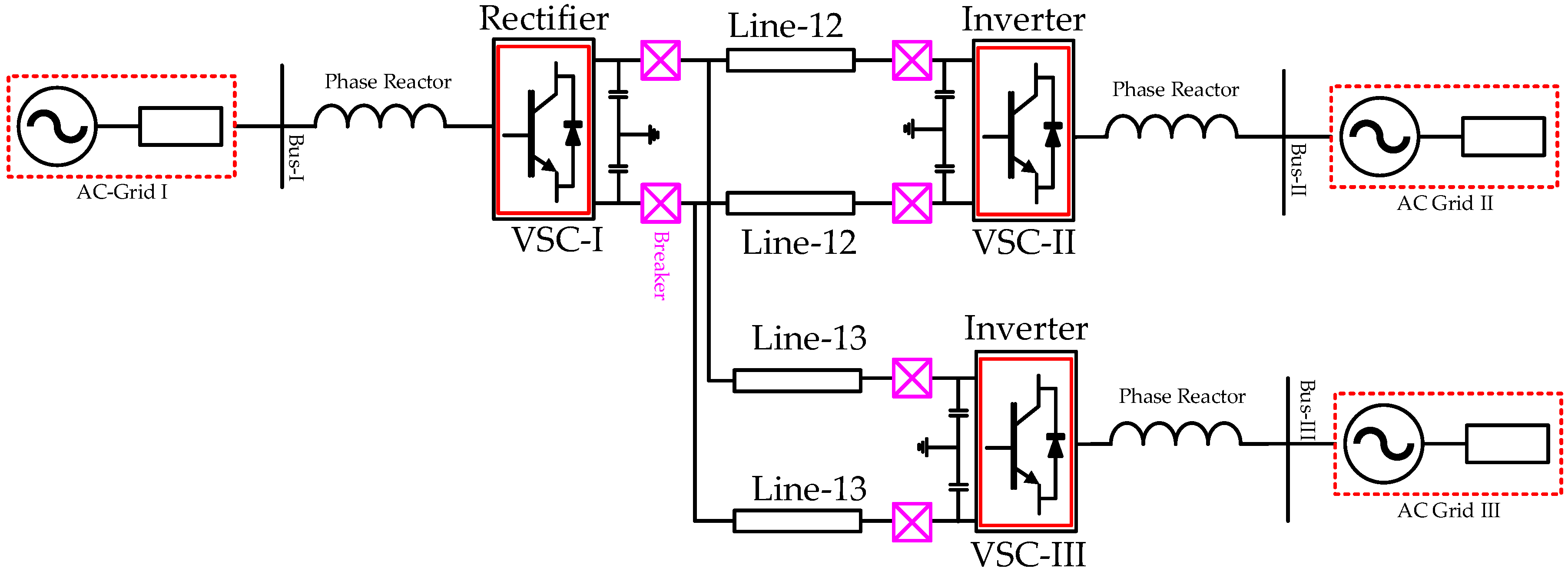

2. Proposed Topology

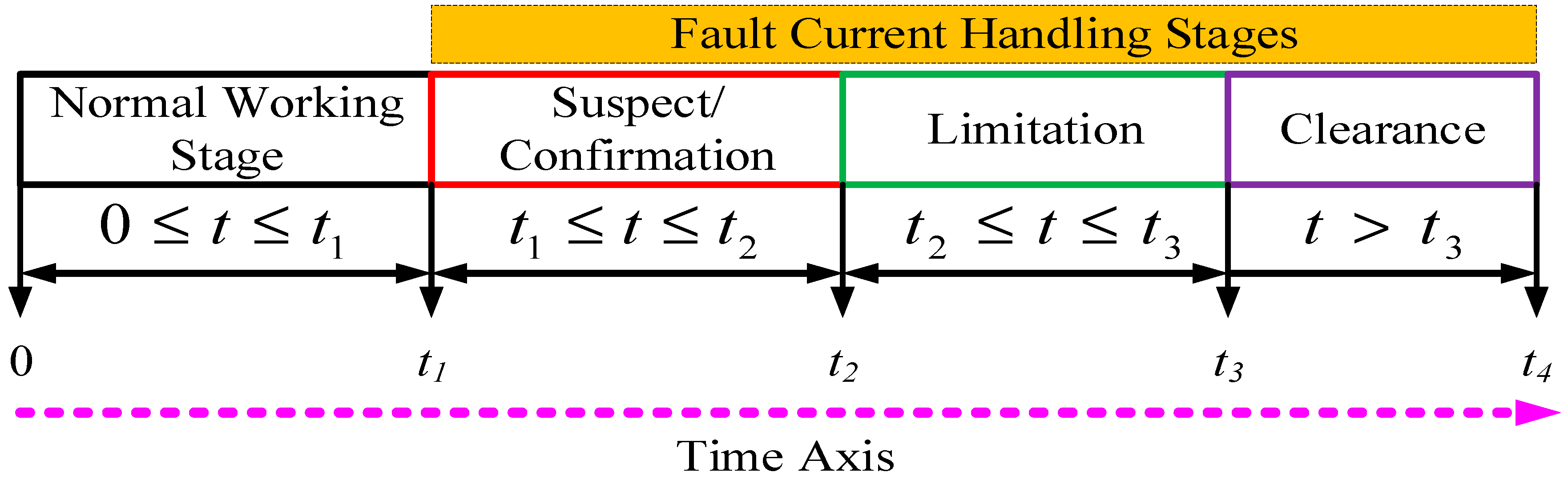

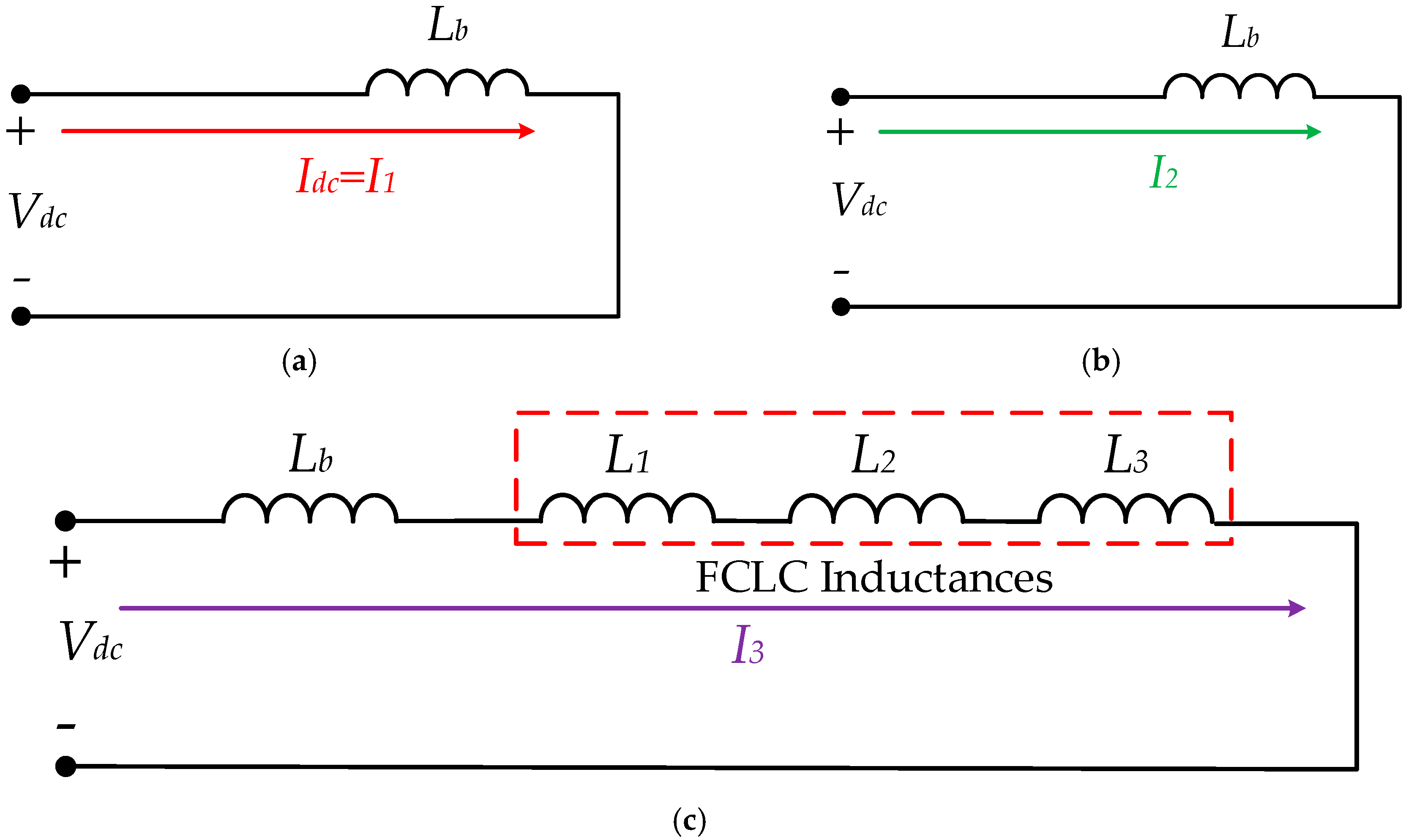

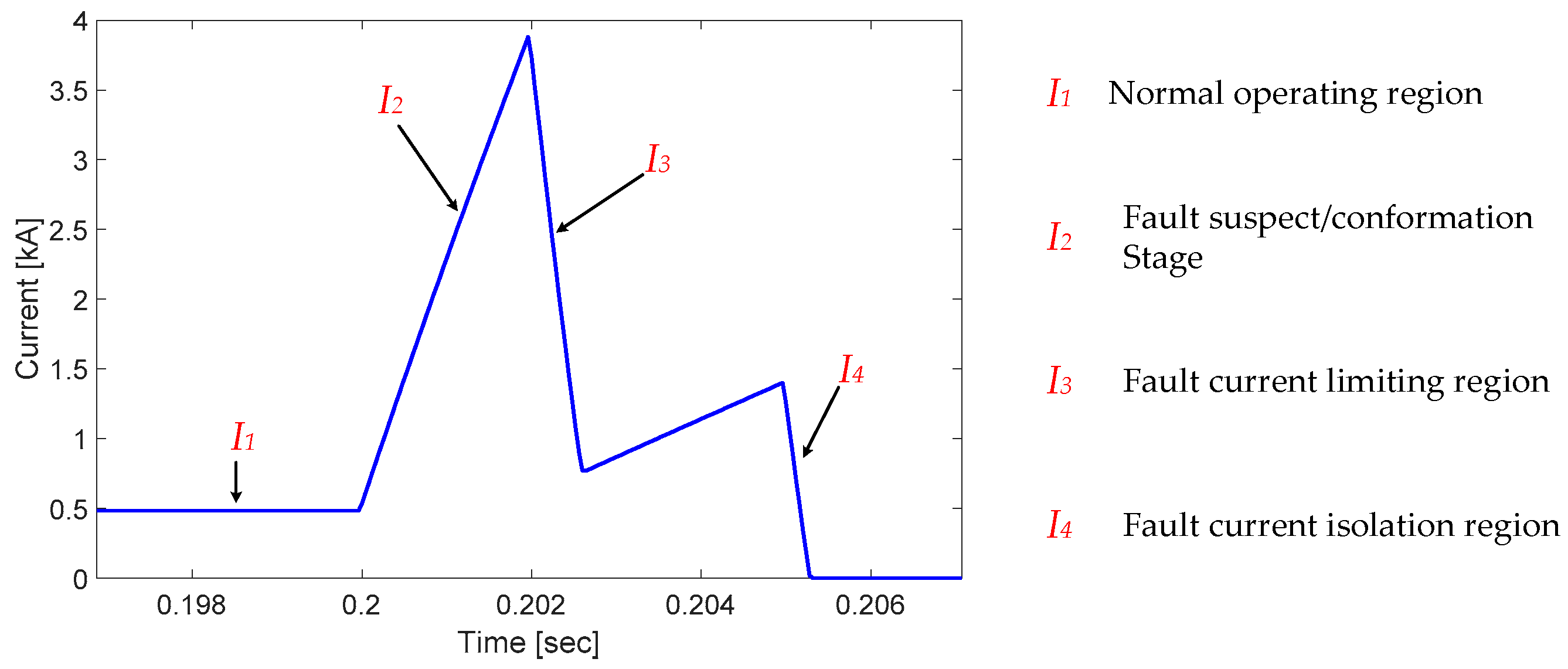

2.1. Working Principle

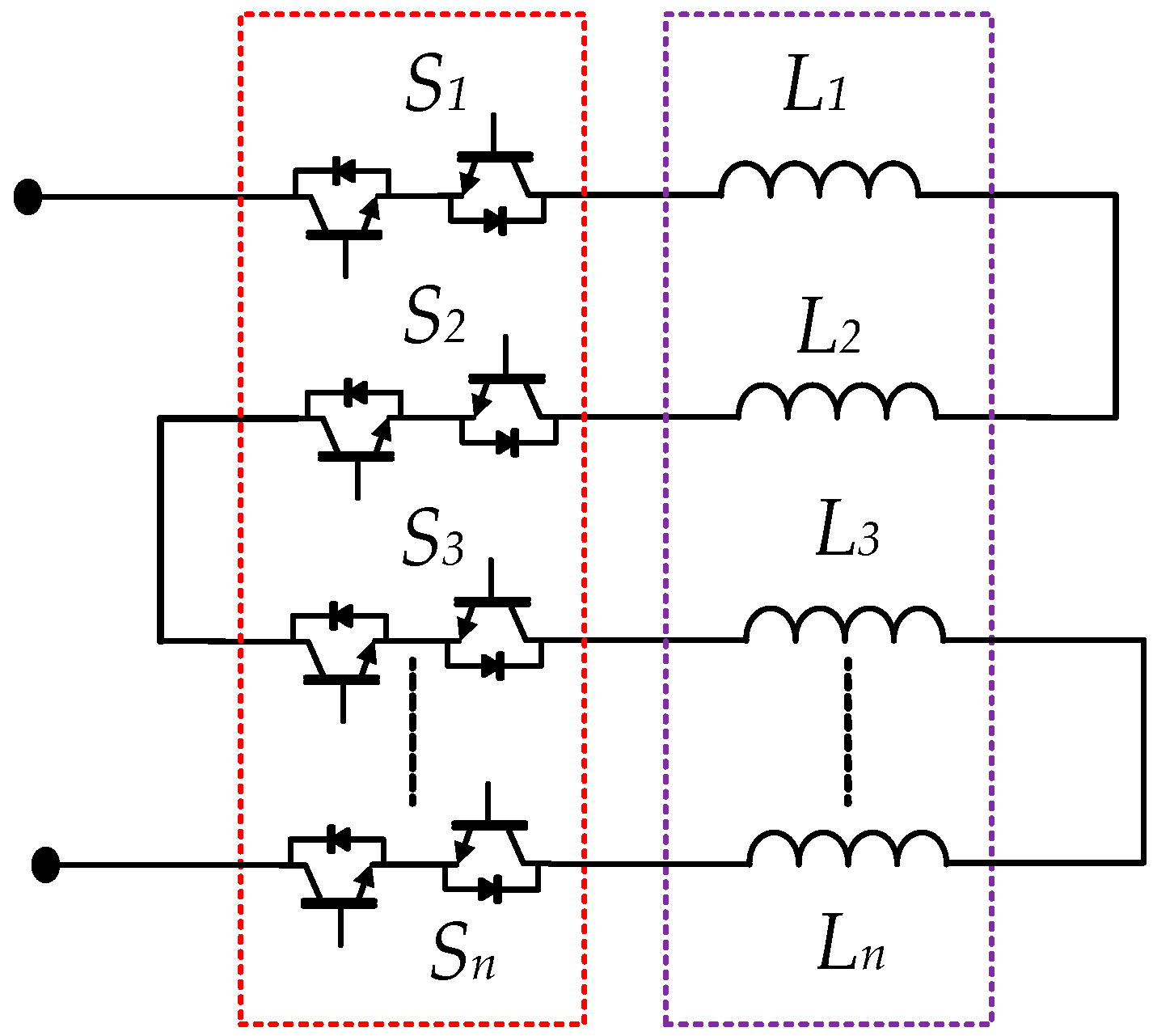

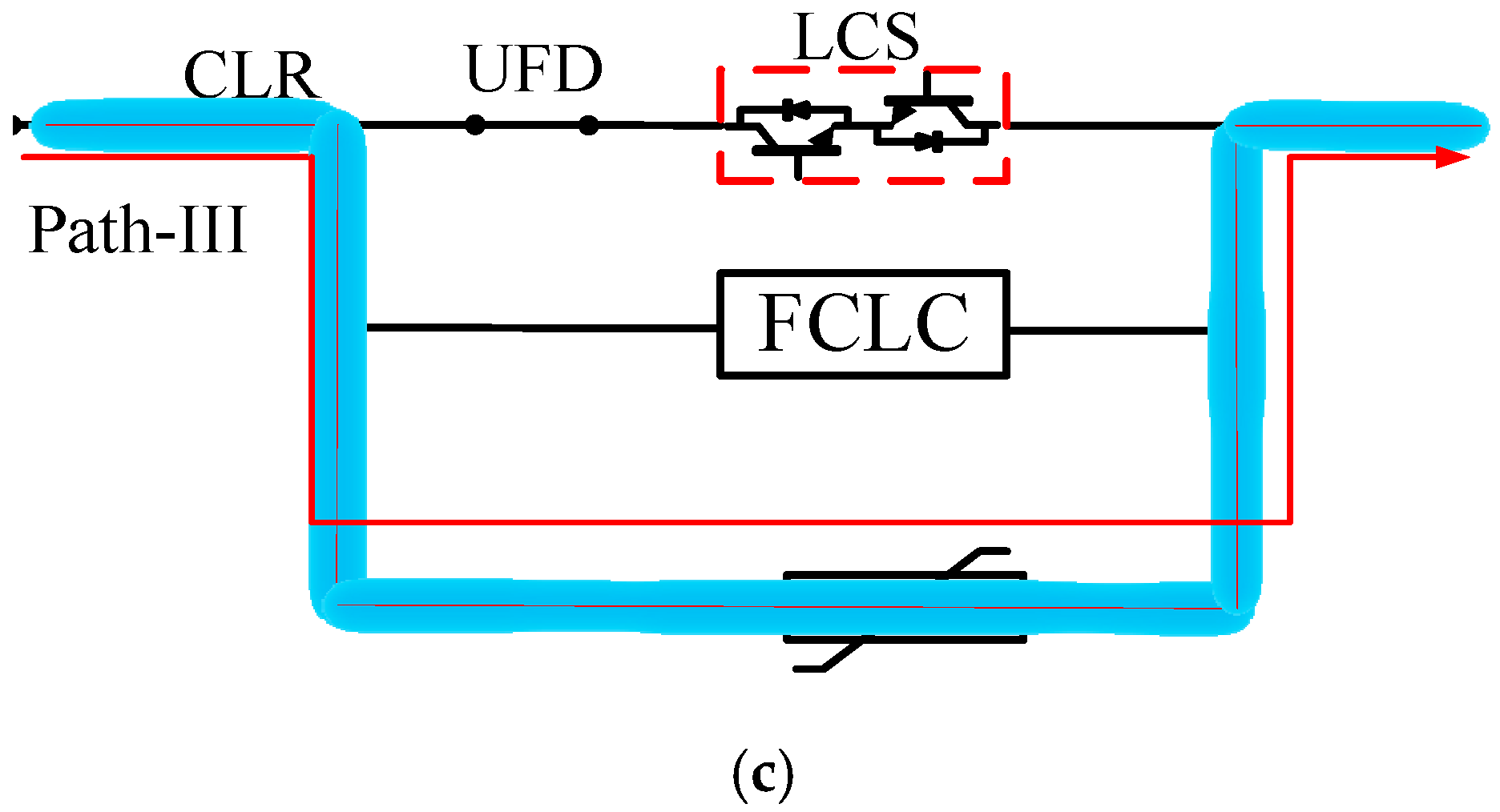

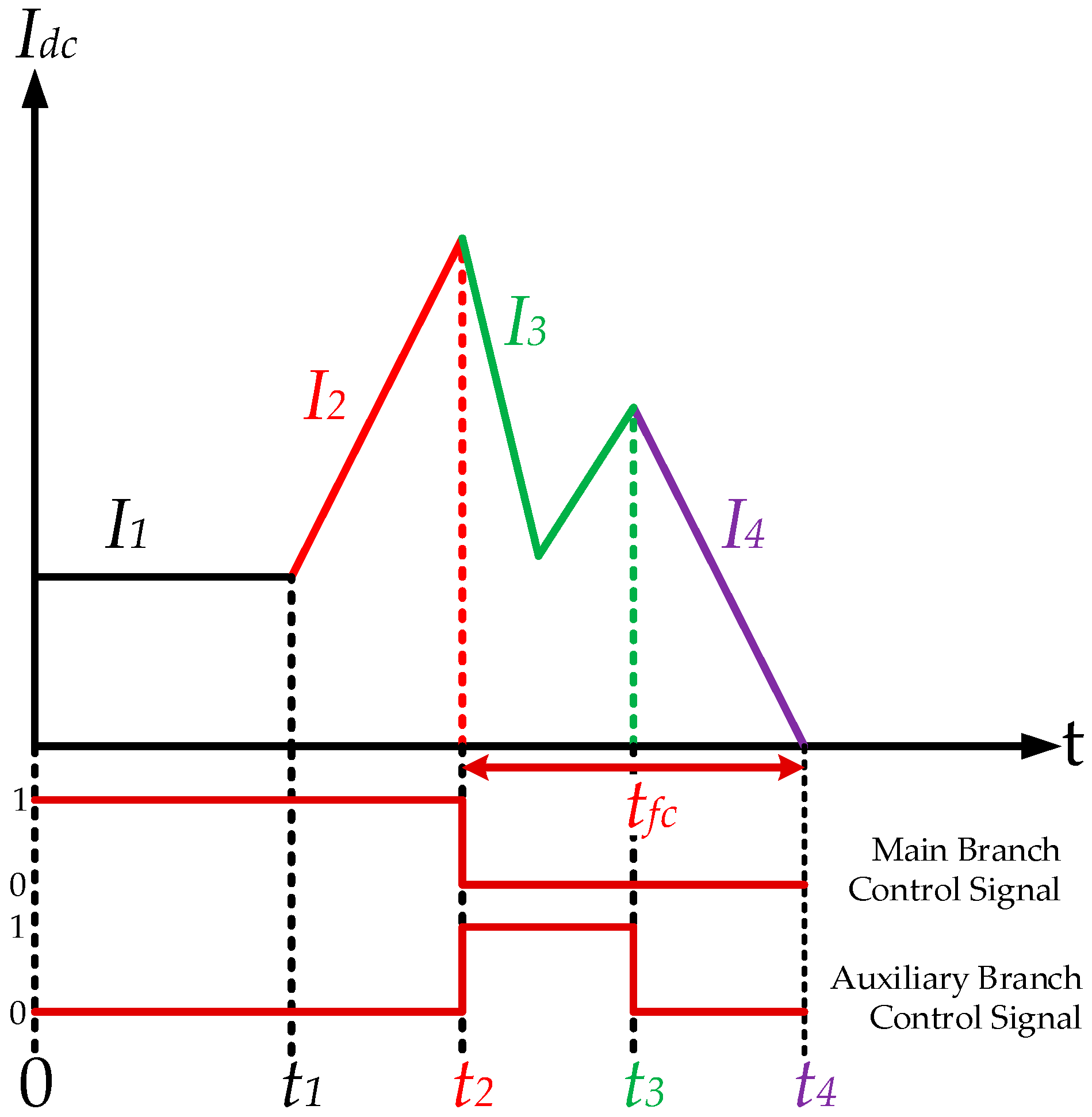

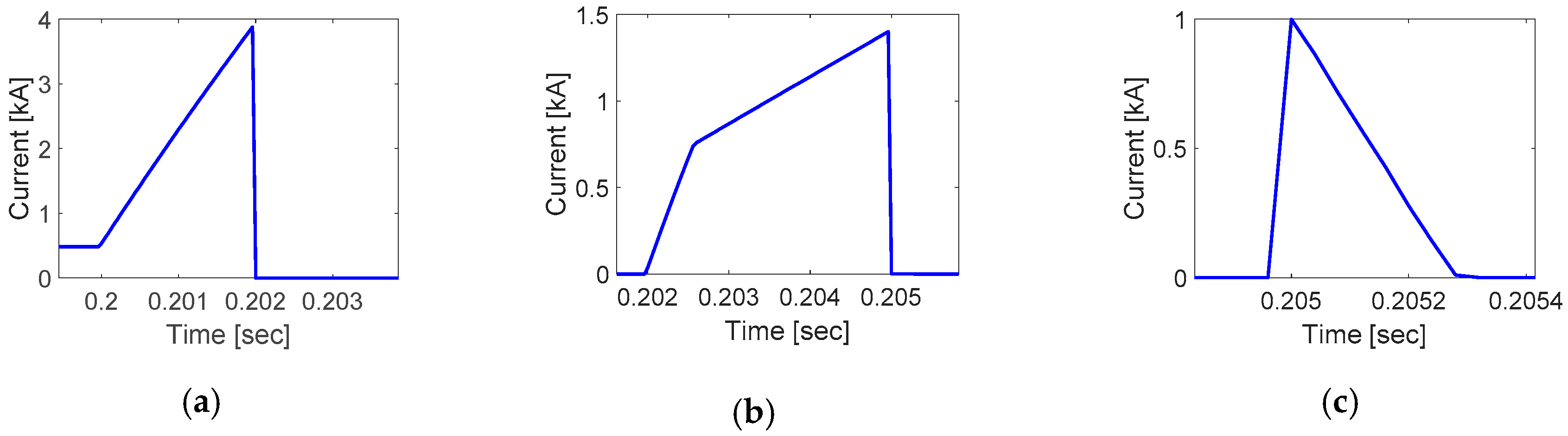

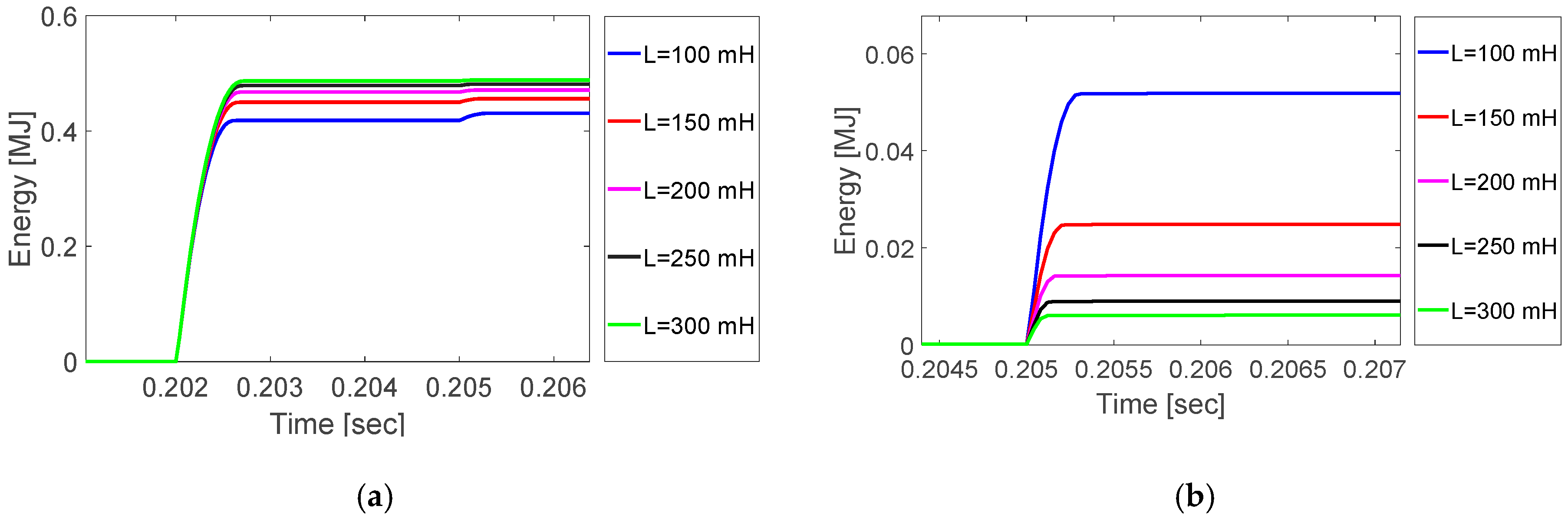

2.2. Determination of Current and Size of Current-Limiting Inductors

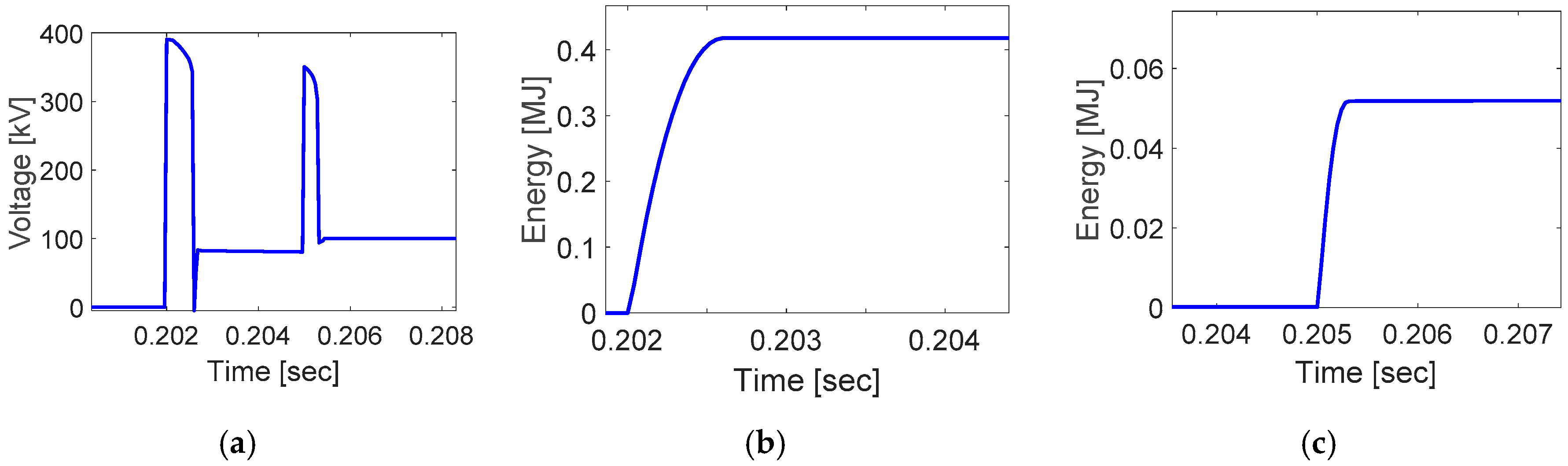

2.3. Transient Overvoltage Analysis

3. Results and Discussion

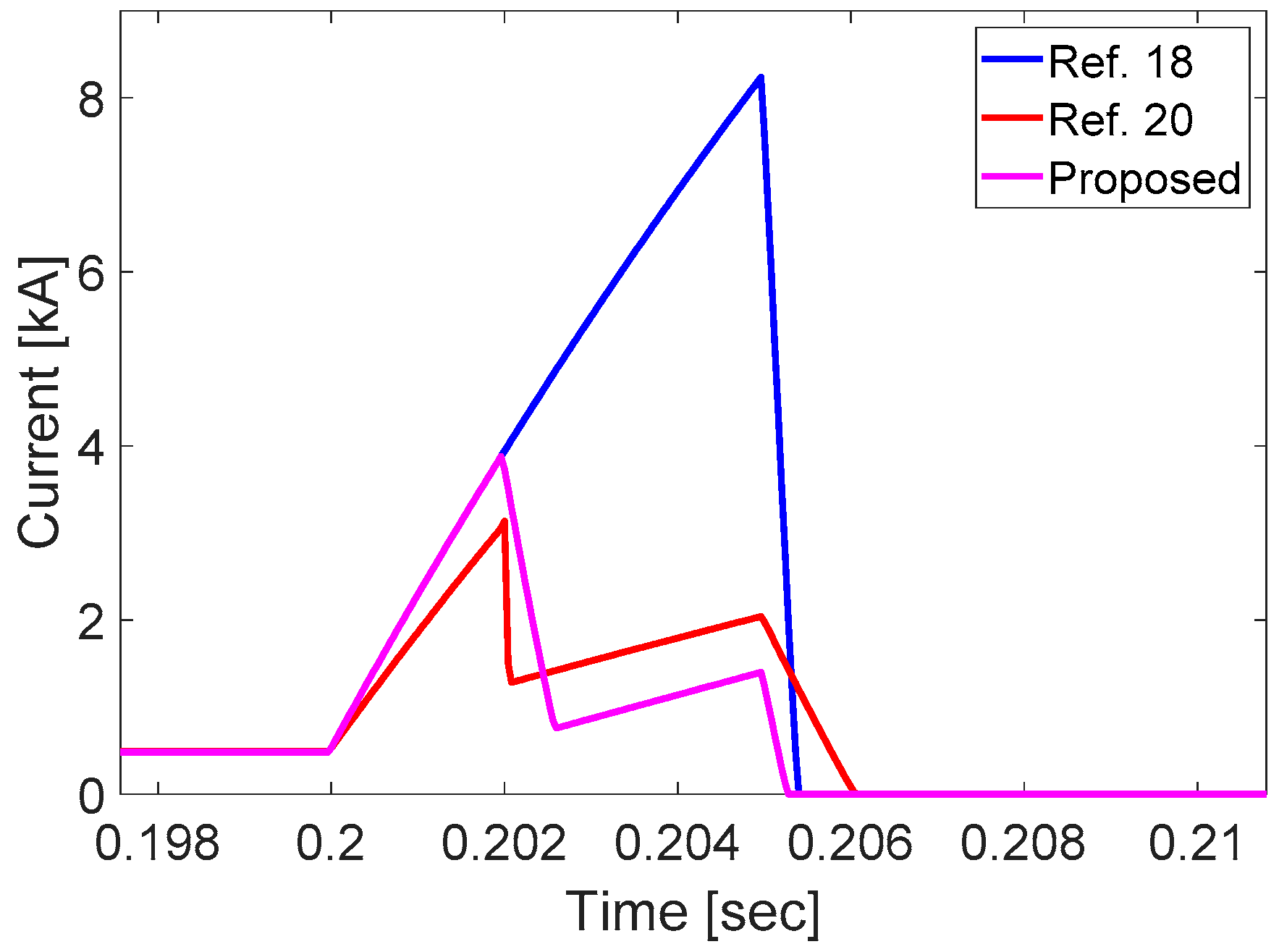

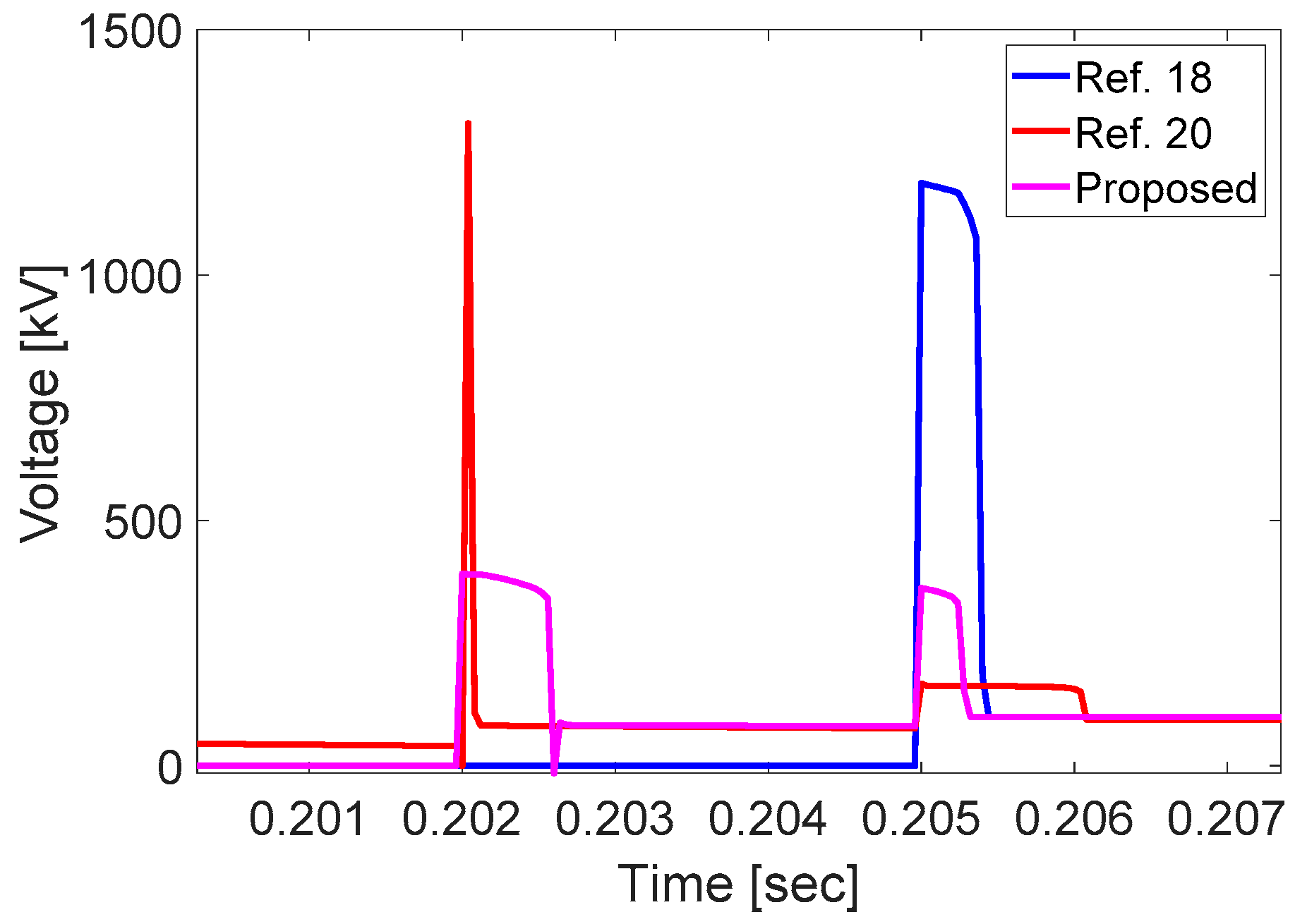

4. Comparative Analysis of Proposed Breaker and Other Topologies

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| BCCB | Branch circuit breaker | LCC | Line-commutated converters |

| CLR | Current-limiting reactance | LCS | Load commutation switch |

| CLIs | Current-limiting inductors | L-G | Line-to-ground |

| CB | Circuit breaker | MOA | Metal oxide arrester |

| DC | Direct current | MCB | Main circuit breaker |

| DCCB | Direct current circuit breaker | ms | Milliseconds |

| FCLC | Fault-current-limiting circuit | MJ | Megajoule |

| FCL | Fault current limiters | NSFCLs | Non-superconducting FCL |

| HVDC | High-voltage direct current | PE | Power electronics |

| HVAC | High-voltage alternating current | SFCLs | Superconducting FCL |

| HCB | Hybrid circuit breaker | VSC | Voltage source converter |

Appendix A

| Parameters | Values | |

|---|---|---|

| DC link parameters | DC voltage Vdn | ±200 kV |

| DC current Idn | 0.5 kA | |

| DC link capacitor | 300 µF | |

| Active power | Terminal-1 (P1) | 0 MW |

| Terminal-2 (P2) | +200 MW | |

| Terminal-3 (P3) | −200 MW | |

| DC line parameters | Length of cable 12 | 200 km |

| Length of cable 13 | 100 km | |

| Resistance per unit length (R) | 0.035 Ω/kM | |

| Inductance per unit length (L) | 0.156 mH/kM | |

| AC grid | Grid-1 voltage | 420 kV |

| Grid-2 voltage | 500 kV | |

| Grid-3 voltage | 420 kV | |

| Parameters | Values | |

|---|---|---|

| CLR | Lb | 38.4 mH |

| CLIs | Inductor-1 L1 | 100 mH |

| Inductor-2 L2 | 100 mH | |

| Inductor-3 L3 | 100 mH | |

| Parasitic inductance | L’p | 2 µH |

References

- Zappa, W.; Junginger, M.; van den Broek, M. Is a 100% renewable European power system feasible by 2050? Appl. Energy 2019, 233–234, 1027–1050. [Google Scholar] [CrossRef]

- The International Renewable Energy Agency (IRENA). Renewable Energy Statistics 2018. Available online: http://www.ren21.net/wp-content/uploads/2018/06/17-8652_GSR2018_FullReport_web_final_.pdf (accessed on 1 March 2019).

- World Economic Forum (WEF). Three Countries Are Leading the Renewable Energy Revolution. Available online: https://www.weforum.org/agenda/2018/02/countries-behind-global-renewable-energy-growth/ (accessed on 1 March 2019).

- Renewable Energy Network (REN) for the 21st Century. Renewables 2018 Global Status. Available online: http://www.ren21.net/wp-content/uploads/2018/06/17-8652_GSR2018_FullReport_web_final_.pdf (accessed on 1 March 2019).

- Rudervall, R.; Charpentier, J.P.; Sharma, R. High Voltage Direct Current (HVDC) Transmission Systems Technology Review Paper. Presented at the Energy Week 2000, Washington, DC, USA, 7–8 March 2000. [Google Scholar]

- Muhammad Rashid. In Power Electronics Hand Book, 4th ed.; BH Publications: Oxford, UK, 2018; pp. 849–851.

- ABB. High-Voltage Direct Current Transmission Enabling Single EU Energy Market. Available online: http://www.eem18.eu/gfx/eem-network/userfiles/_public/eem18_lodz_krontiris.pdf (accessed on 1 March 2019).

- IEEE Transmission and Distribution Committee. HVDC Project Listing. Available online: http://www.ece.uidaho.edu/hvdcfacts/Projects/HVDCProjectsListingDec2006.pdf (accessed on 1 March 2019).

- Yang, Q.; Le Blond, S.; Liang, F. Design and Application of Superconducting Fault Current Limiter in a Multiterminal HVDC System. IEEE Trans. Appl. Supercond. 2017, 27, 1–5. [Google Scholar] [CrossRef]

- Lee, H.Y.; Asif, M.; Park, K.H.; Lee, B.W. Feasible Application Study of Several Types of Superconducting Fault Current Limiters in HVDC Grids. IEEE Trans. Appl. Supercond. 2018, 28, 1–5. [Google Scholar] [CrossRef]

- Li, B.; Jing, F.; Li, B.; Chen, X.; Jia, J. Study of the application of active saturated iron-core superconductive fault current limiters in the VSC-HVDC system. IEEE Trans. Appl. Supercond. 2018, 28, 1–6. [Google Scholar] [CrossRef]

- Chen, L.; Tang, F.; Ren, L. Comparative study of inductive and resistive SFCL to mitigate the DC fault current in a VSC-HVDC system integrated with wind power farms. In Proceedings of the 2015 IEEE International Conference on Applied Superconductivity and Electromagnetic Devices (ASEMD), Shanghai, China, 20–23 November 2015. [Google Scholar]

- Sujuan, X.; Yufeng, Q.; Tianshu, B. Resistive DC fault current limiter. IET J. Eng. 2017, 2017, 1682–1685. [Google Scholar] [CrossRef]

- Wang, M.; Leterme, W.; Beerten, J.; van Hertem, D. Using fault current limiting mode of a hybrid DC breaker. IET J. Eng. 2018, 2018, 818–823. [Google Scholar] [CrossRef]

- Keshavarzi, D.; Farjah, E.; Ghanbari, T. Hybrid DC Circuit Breaker and Fault Current Limiter with Optional Interruption Capability. IEEE Trans. Power Electron. 2018, 33, 2330–2338. [Google Scholar] [CrossRef]

- Franck, C.M. HVDC Circuit Breakers: A Review Identifying Future Research Needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef]

- Hassanpoor, A.; Häfner, J.; Jacobson, B. Technical Assessment of Load Commutation Switch in Hybrid HVDC Breaker. IEEE Trans. Power Electron. 2015, 30, 5393–5400. [Google Scholar] [CrossRef]

- Callavik, M.; Blomberg, A.; Häfner, J.; Jacobson, B. Break-through!: ABB’s hybrid HVDC breaker, an innovation breakthrough enabling reliable HVDC grids. Abb Rev. 2013. Available online: https://www.researchgate.net/publication/297049686_Break-through_ABB’s_hybrid_HVDC_breaker_an_innovation_breakthrough_enabling_reliable_HVDC_grids (accessed on 1 March 2019).

- Nguyen, A.D.; Nguyen, T.T.; Kim, H.M. A comparison of different hybrid direct current circuit breakers for application in HVDC system. Int. J. Control Autom. 2016, 9, 381–394. [Google Scholar] [CrossRef]

- Li, S.; Zhang, J.; Xu, J.; Zhao, C. A new topology for current limiting HVDC circuit breaker. Int. J. Electr. Power Energy Syst. 2019, 104, 933–942. [Google Scholar] [CrossRef]

- Liu, J.; Tai, N.; Fan, C.; Chen, S. A Hybrid Current-Limiting Circuit for DC Line Fault in Multiterminal VSC-HVDC System. IEEE Trans. Ind. Electron. 2017, 64, 5595–5607. [Google Scholar] [CrossRef]

- Heidary, A.; Radmanesh, H.; Bakhshi, A. A Compound Current Limiter and Circuit Breaker. Electronics 2019, 8, 551. [Google Scholar] [CrossRef]

- Nguyen, V.-V.; Son, H.-I.; Nguyen, T.-T.; Kim, H.-M.; Kim, C.-K. A Novel Topology of Hybrid HVDC Circuit Breaker for VSC-HVDC Application. Energies 2017, 10, 1675. [Google Scholar] [CrossRef]

- Thomas, J.; Geraint, P.C.; Christian, M.F. Small-scale HVDC circuit breaker. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1058–1068. [Google Scholar] [CrossRef]

- Kontos, E.; Schultz, T.; Mackay, L. Multiline breaker for HVdc applications. IEEE Trans. Power Deliv. 2017, 33, 1469–1478. [Google Scholar] [CrossRef]

- Li, C.; Liang, J.; Wang, S. Interlink hybrid DC circuit breaker. IEEE Trans. Ind. Electron. 2018, 65, 8677–8686. [Google Scholar] [CrossRef]

- Liu, W.; Liu, F.; Zhuang, Y. A multiport circuit breaker-based multiterminal DC system fault protection. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 118–128. [Google Scholar] [CrossRef]

- Nadeem, M.H.; Zheng, X.; Tai, N.; Gul, M. Identification and Isolation of Faults in Multi-terminal High Voltage DC Networks with Hybrid Circuit Breakers. Energies 2018, 11, 1086. [Google Scholar] [CrossRef]

- Cwikowski, O.; Wood, A.; Miller, A. Operating DC Circuit Breakers with MMC. IEEE Trans. Power Deliv. 2018, 33, 260–270. [Google Scholar] [CrossRef]

- Xiang, B.; Liu, Z.; Geng, Y.; Yanabu, S. DC Circuit Breaker Using Superconductor for Current Limiting. IEEE Trans. Appl. Supercond. 2015, 25, 1–7. [Google Scholar] [CrossRef]

- Pei, X.; Cwikowski, O.; Smith, A.C.; Barnes, M. Design and Experimental Tests of a Superconducting Hybrid DC Circuit Breaker. IEEE Trans. Appl. Supercond. 2018, 28, 1–5. [Google Scholar] [CrossRef]

- Alam, M.S.; Abido, M.A.Y.; El-Amin, I. Fault Current Limiters in Power Systems: A Comprehensive Review. Energies 2018, 11, 1025. [Google Scholar] [CrossRef]

- Filipović-Grčić, B.; Uglešić, I.; Pavic, I. Energy Stress of Surge Arresters Due to Temporary Overvoltages. In Proceedings of the International Conference on Power Systems Transients (IPST), Delft, The Netherlands, 14–17 June 2011. [Google Scholar]

- Magnusson, J.; Saers, R.; Liljestrand, L.; Engdahl, G. Separation of the Energy Absorption and Overvoltage Protection in Solid-State Breakers by the Use of Parallel Varistors. IEEE Trans. Power Electron. 2014, 29, 2715–2722. [Google Scholar] [CrossRef]

| Size of L (mH) | Fault Clearance Time (ms) | Peak Current in Fault Current Limitation Stage (kA) | Energy Absorbed by MOAov (MJ) | Energy Absorbed by MOAm (MJ) |

|---|---|---|---|---|

| 100 | 3.25 | 1.40 | 0.4306 | 0.052 |

| 150 | 3.15 | 1.00 | 0.4558 | 0.024 |

| 200 | 3.11 | 0.76 | 0.4705 | 0.014 |

| 250 | 3.08 | 0.62 | 0.4810 | 0.009 |

| 300 | 3.05 | 0.52 | 0.4881 | 0.006 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahmad, M.; Wang, Z. A Hybrid DC Circuit Breaker with Fault-Current-Limiting Capability for VSC-HVDC Transmission System. Energies 2019, 12, 2388. https://doi.org/10.3390/en12122388

Ahmad M, Wang Z. A Hybrid DC Circuit Breaker with Fault-Current-Limiting Capability for VSC-HVDC Transmission System. Energies. 2019; 12(12):2388. https://doi.org/10.3390/en12122388

Chicago/Turabian StyleAhmad, Muhammad, and Zhixin Wang. 2019. "A Hybrid DC Circuit Breaker with Fault-Current-Limiting Capability for VSC-HVDC Transmission System" Energies 12, no. 12: 2388. https://doi.org/10.3390/en12122388

APA StyleAhmad, M., & Wang, Z. (2019). A Hybrid DC Circuit Breaker with Fault-Current-Limiting Capability for VSC-HVDC Transmission System. Energies, 12(12), 2388. https://doi.org/10.3390/en12122388