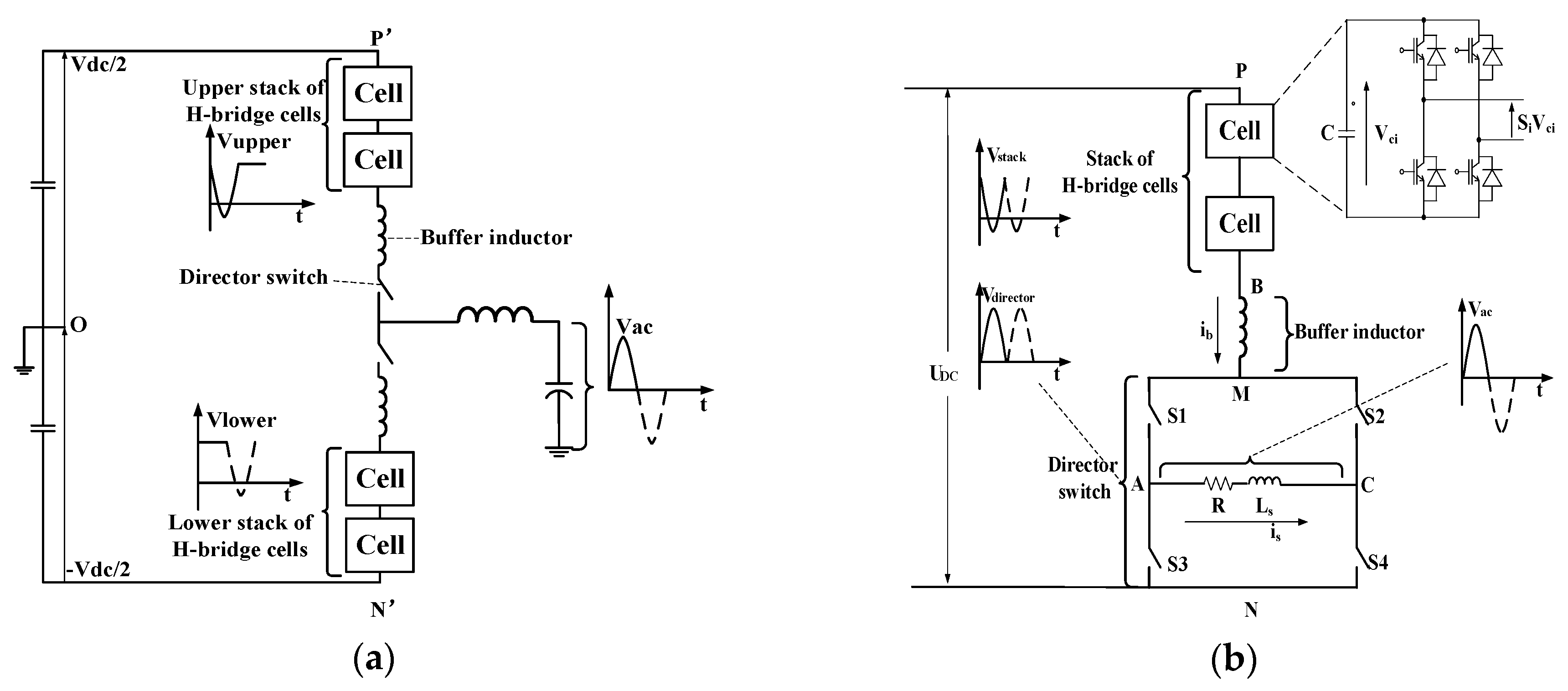

Figure 1.

Schematic representation of the two topologies: (a) alternate-arm multilevel converter (AAMC); (b) full bridge director switches based alternate-arm multi-level converter (FA-MMC).

Figure 1.

Schematic representation of the two topologies: (a) alternate-arm multilevel converter (AAMC); (b) full bridge director switches based alternate-arm multi-level converter (FA-MMC).

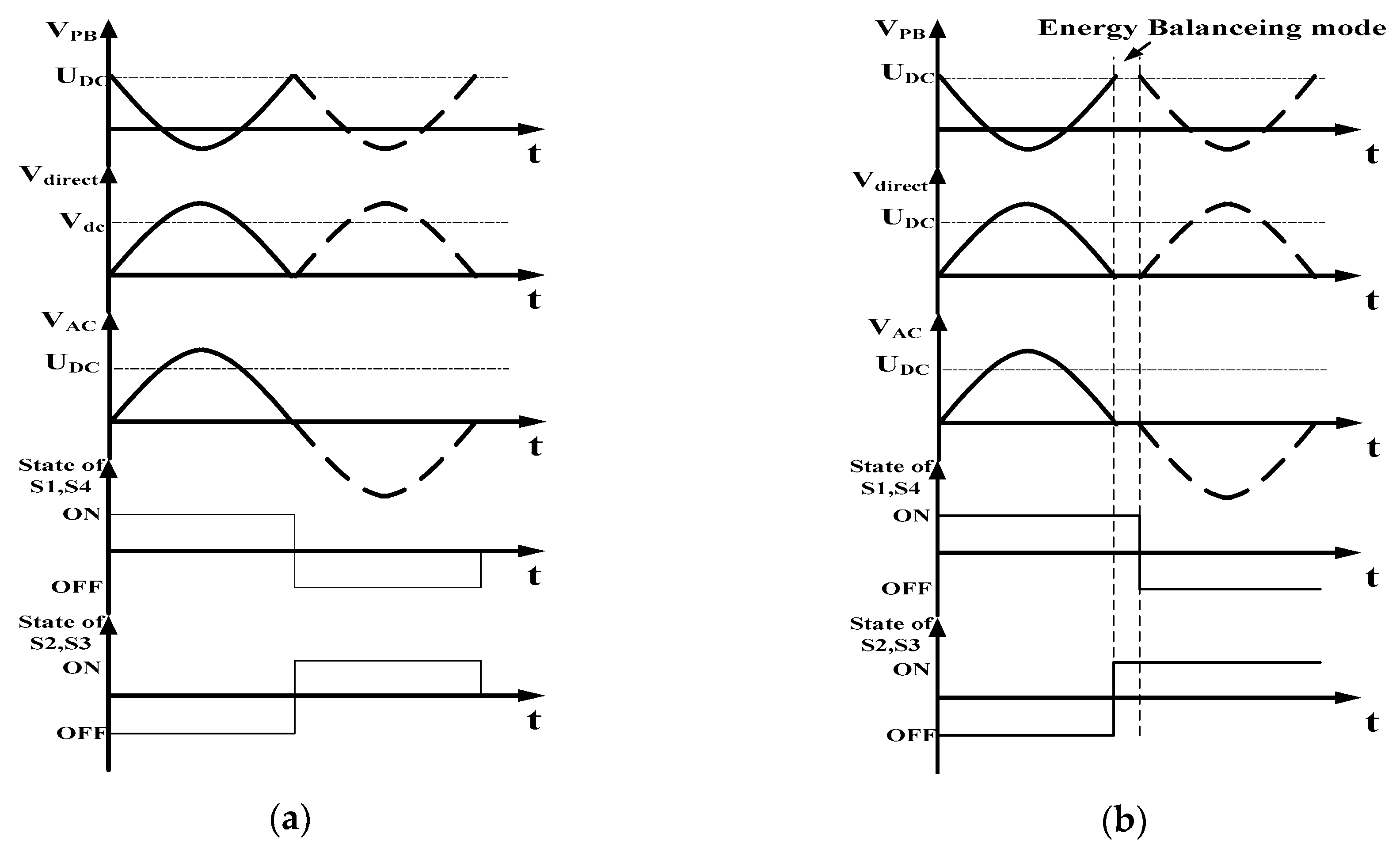

Figure 2.

The voltage waveform and state of S1–S4: (a) without energy balance mode; (b) with energy balance mode.

Figure 2.

The voltage waveform and state of S1–S4: (a) without energy balance mode; (b) with energy balance mode.

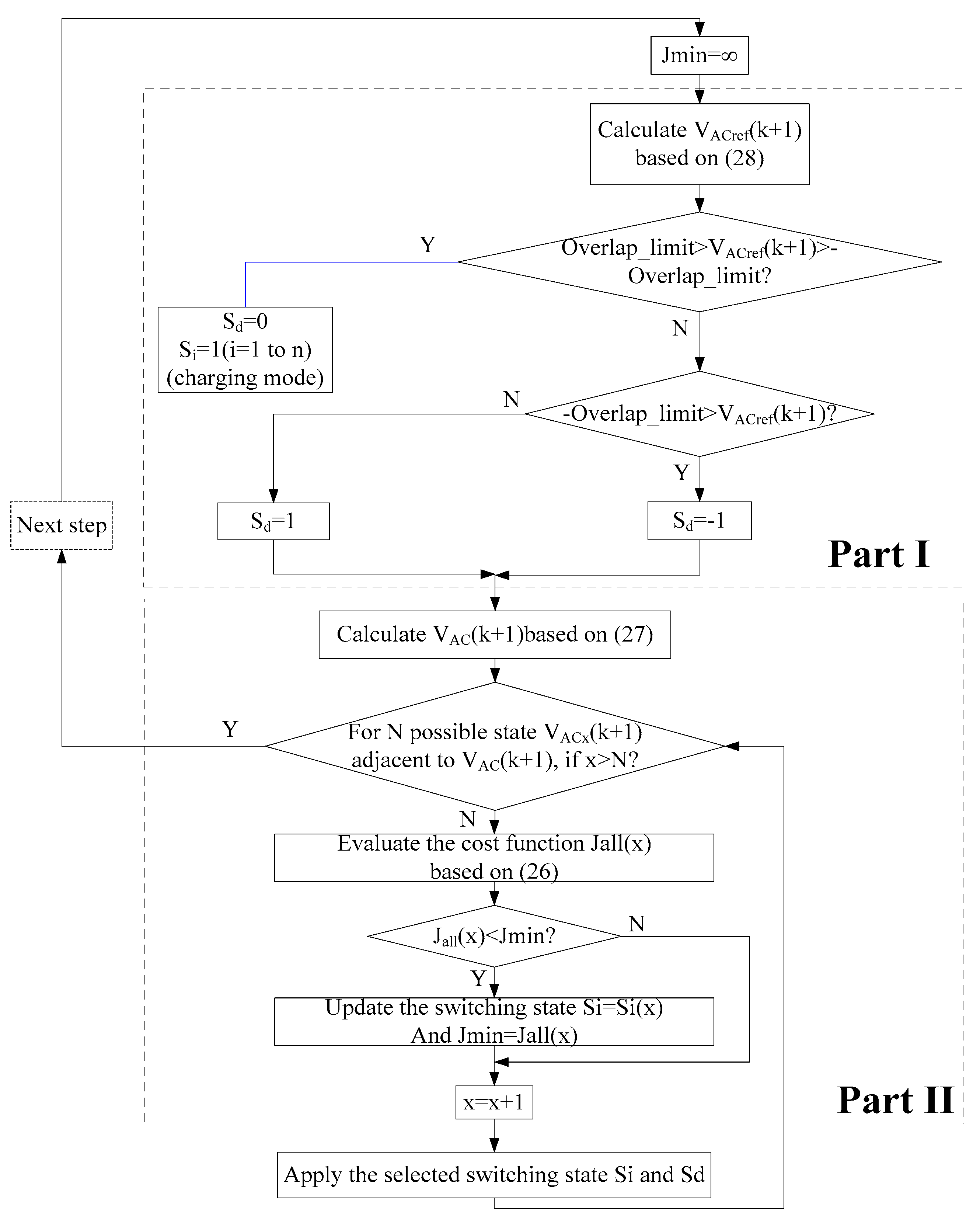

Figure 3.

Block diagram of the predictive control strategy

Figure 3.

Block diagram of the predictive control strategy

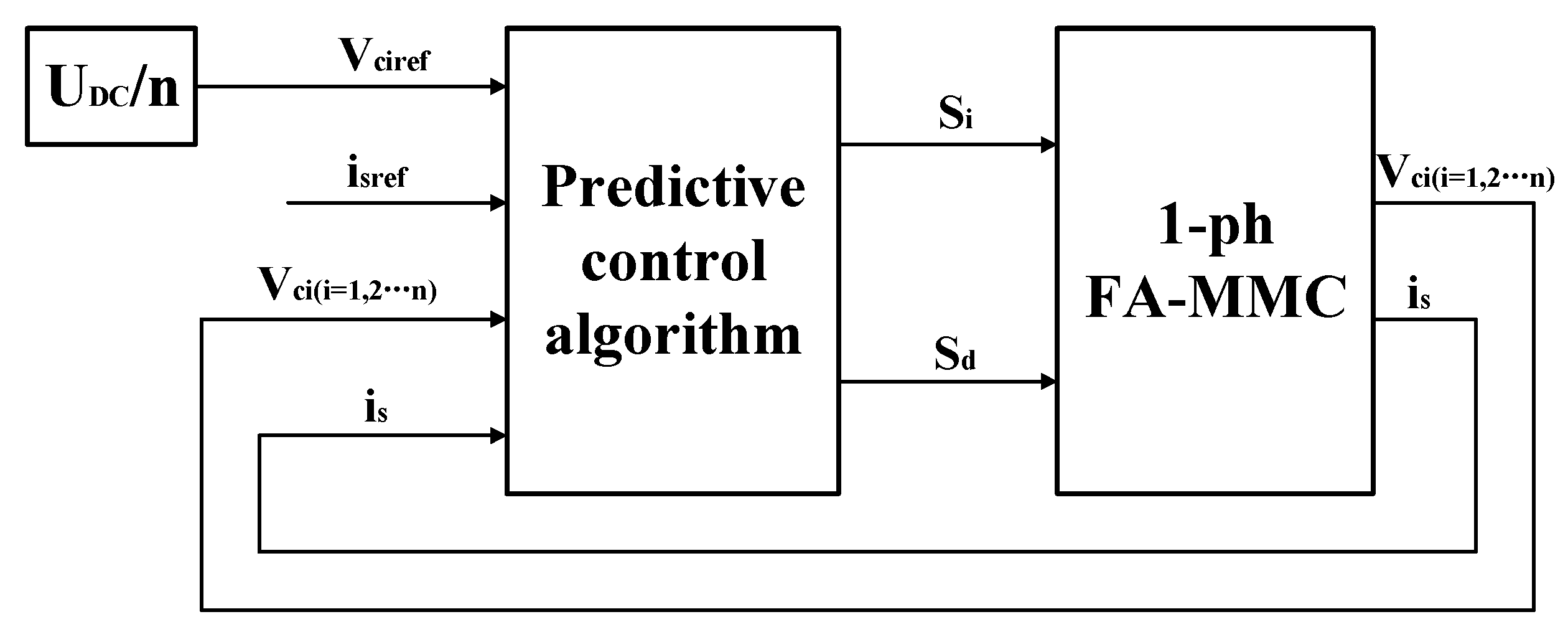

Figure 4.

Schematic diagram of the control system.

Figure 4.

Schematic diagram of the control system.

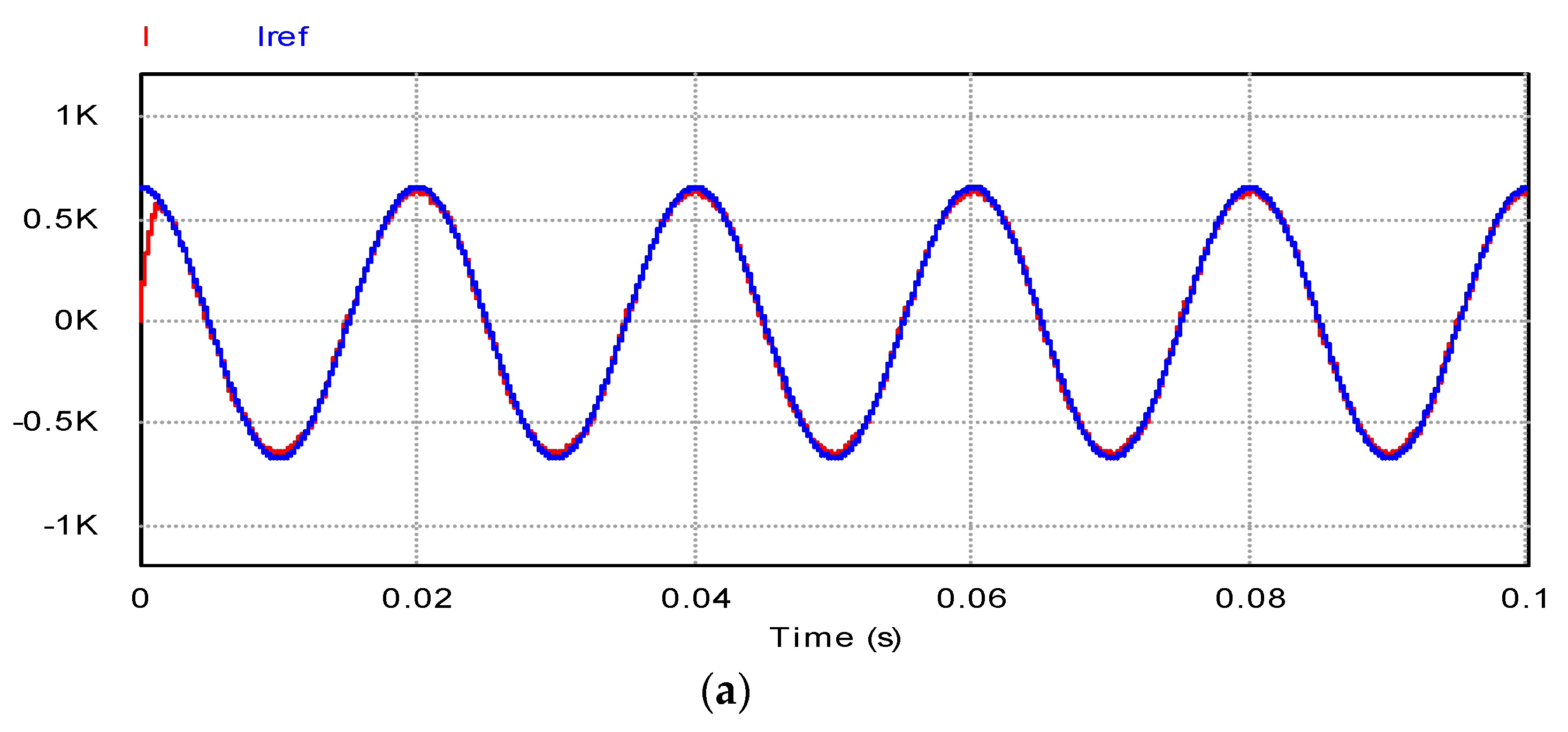

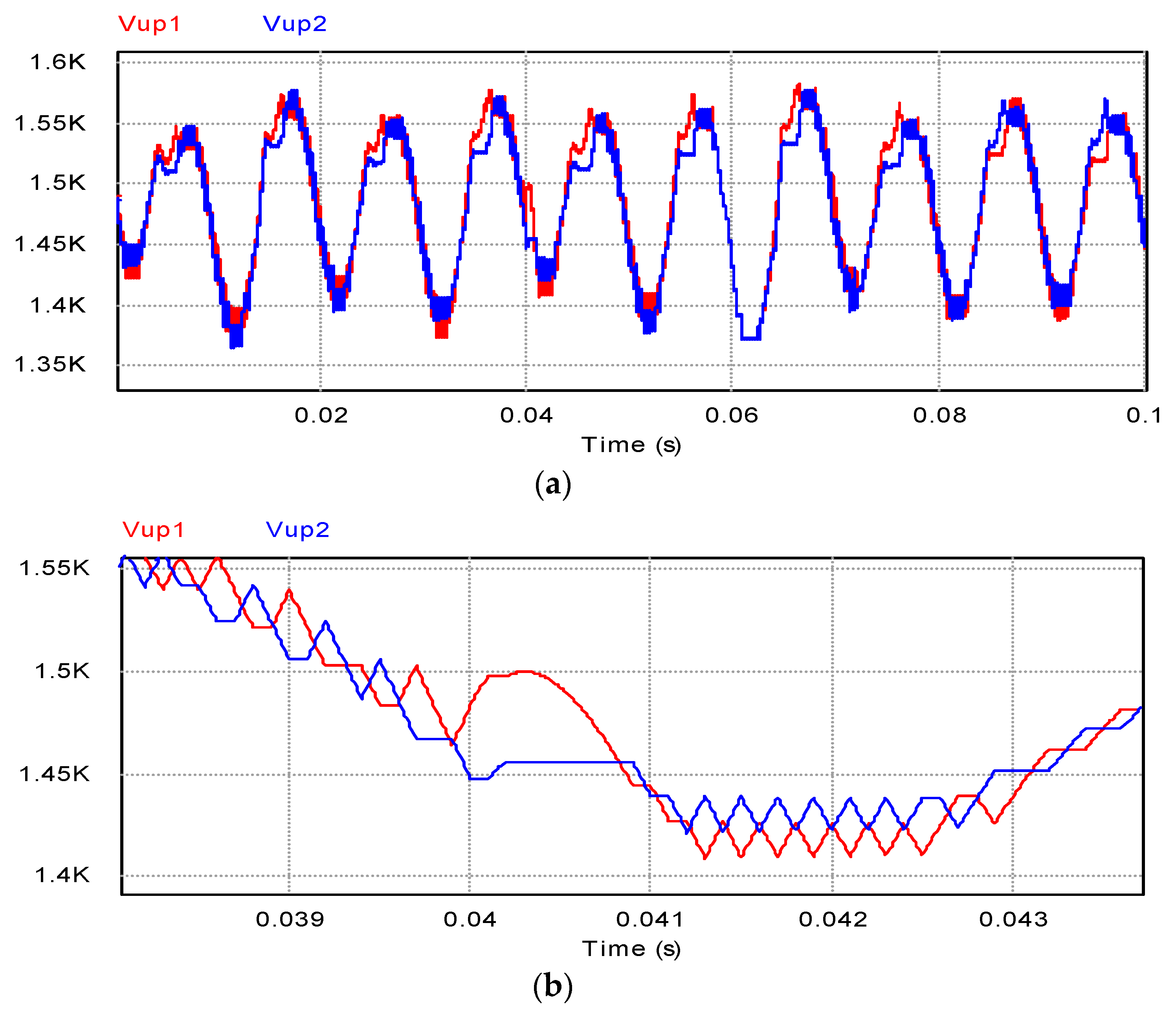

Figure 5.

Simulation waveform of the single-phase FA-MMC in steady state operation: (a) Load current and reference current; (b) output AC voltage; (c) voltage of the stack of H-bridges; (d) voltage across the director switches S1–S4.

Figure 5.

Simulation waveform of the single-phase FA-MMC in steady state operation: (a) Load current and reference current; (b) output AC voltage; (c) voltage of the stack of H-bridges; (d) voltage across the director switches S1–S4.

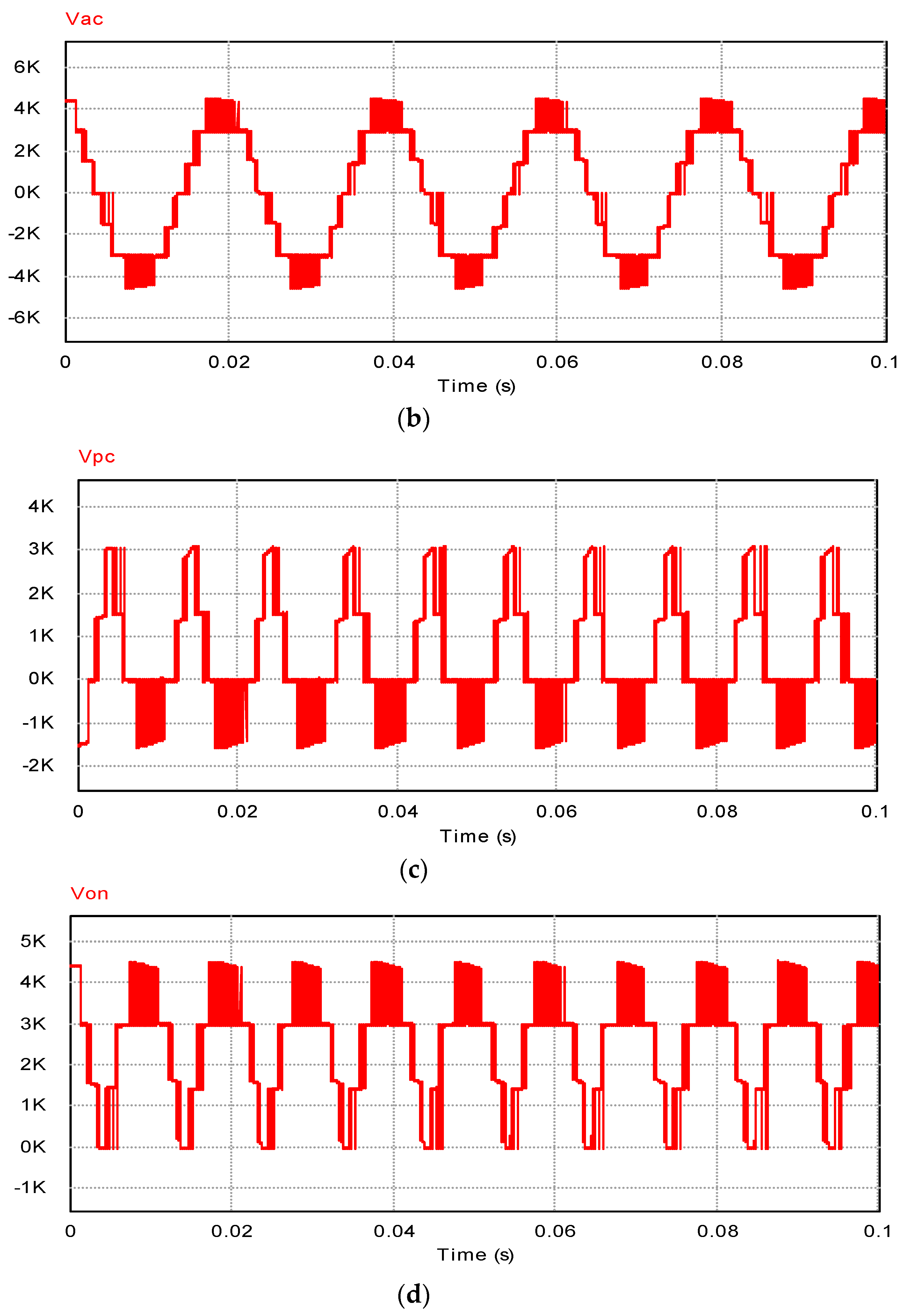

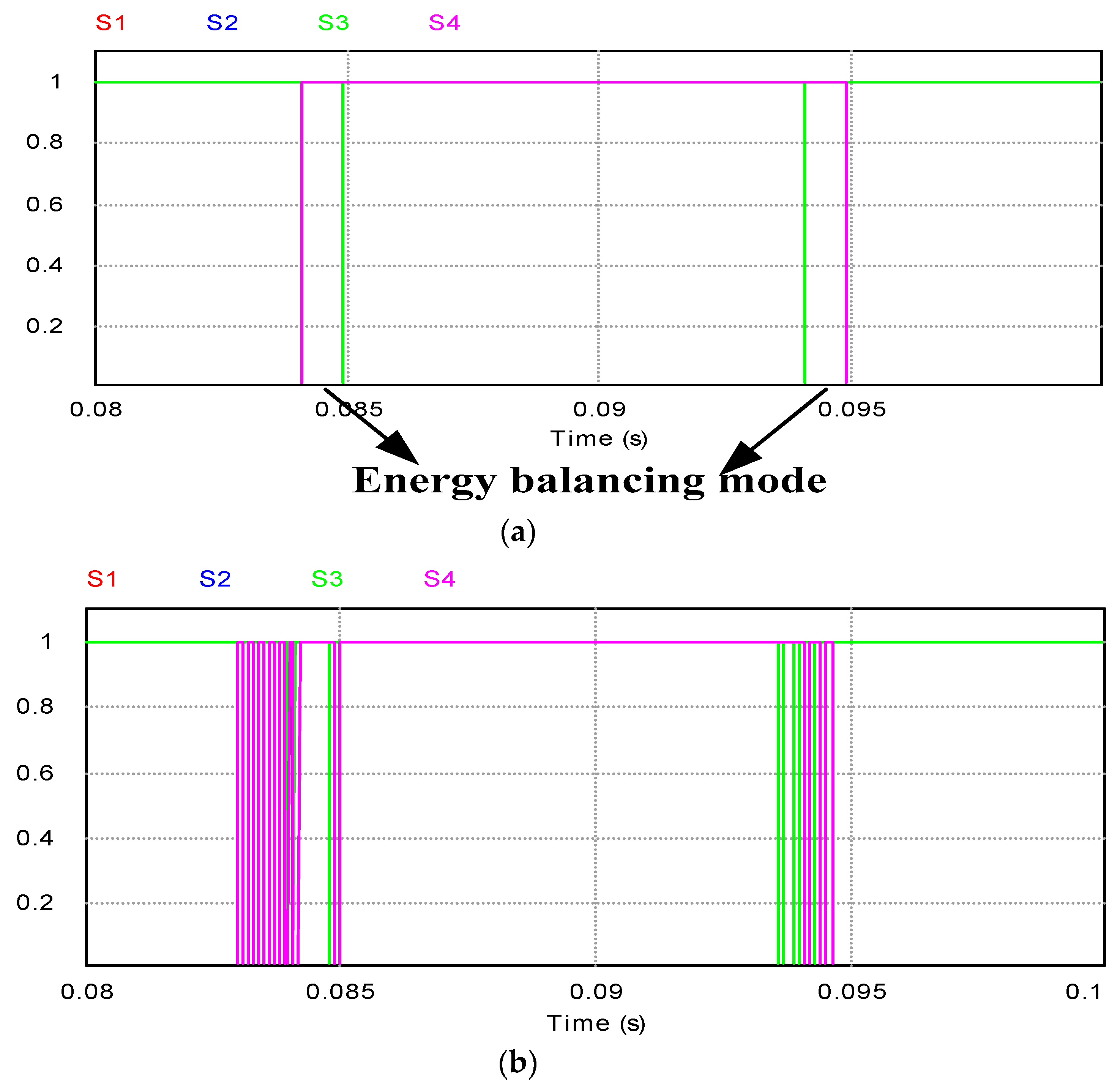

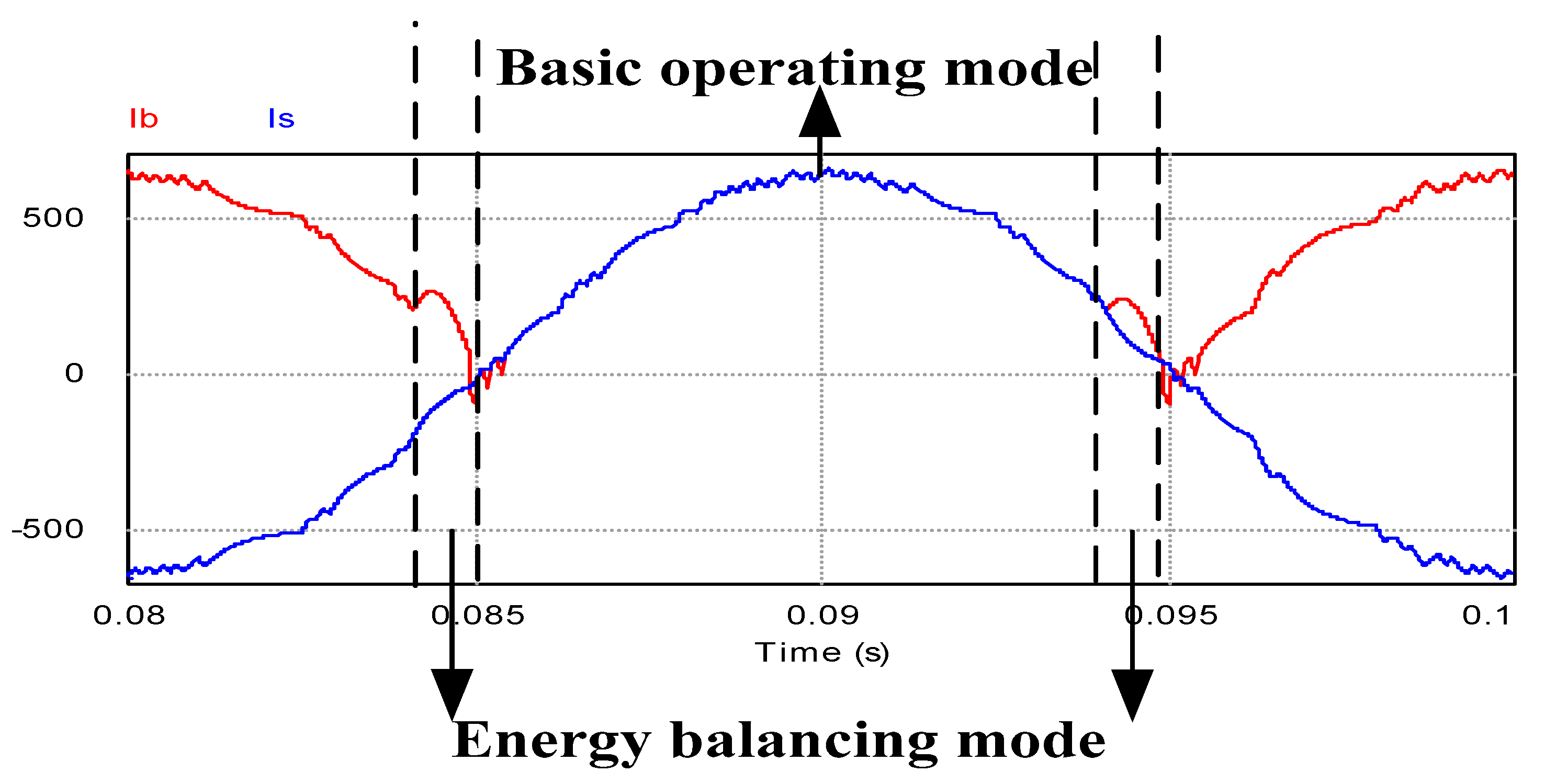

Figure 6.

Capacitor voltages of the cells.

Figure 6.

Capacitor voltages of the cells.

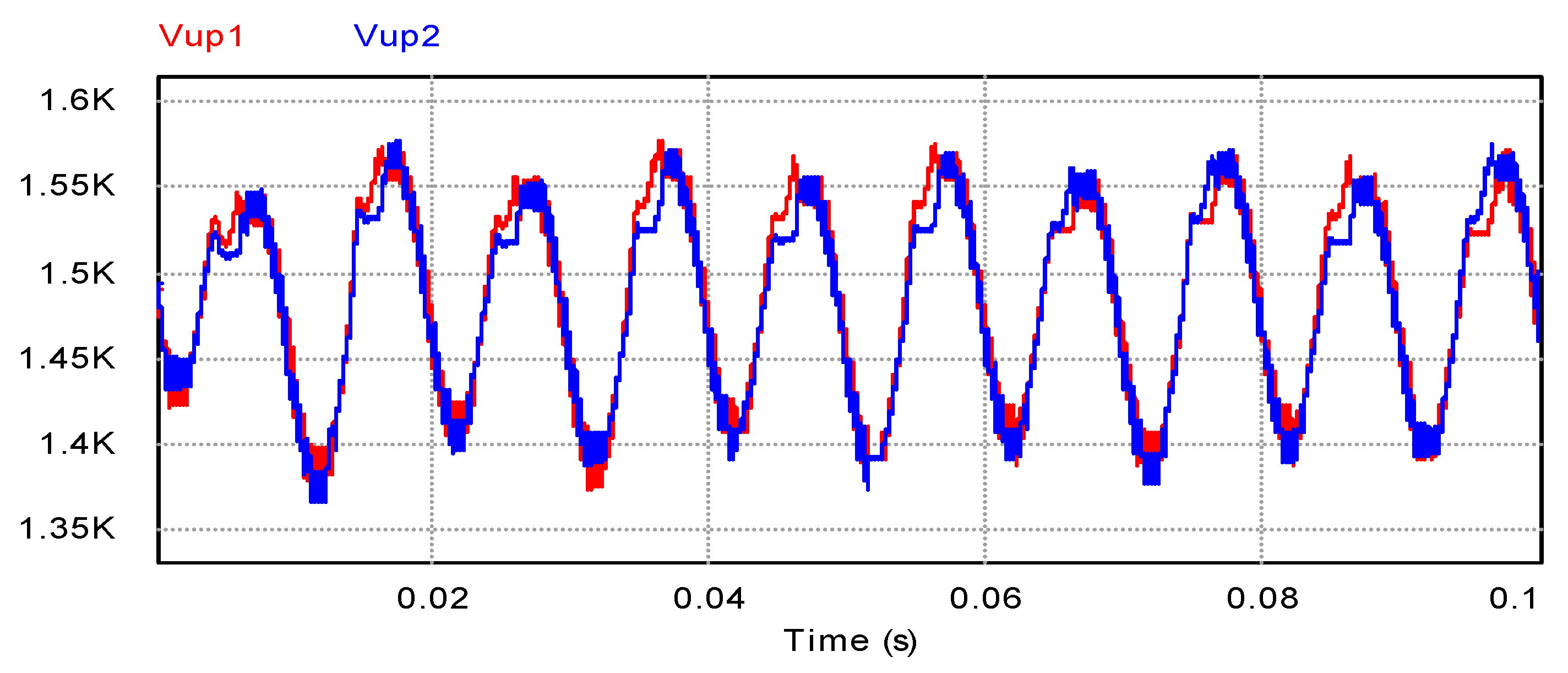

Figure 7.

Director switch control signal of S1–S4: (a) Control signal based on Vacref(t+Ts); (b) control signal based on Vac(t + Ts).

Figure 7.

Director switch control signal of S1–S4: (a) Control signal based on Vacref(t+Ts); (b) control signal based on Vac(t + Ts).

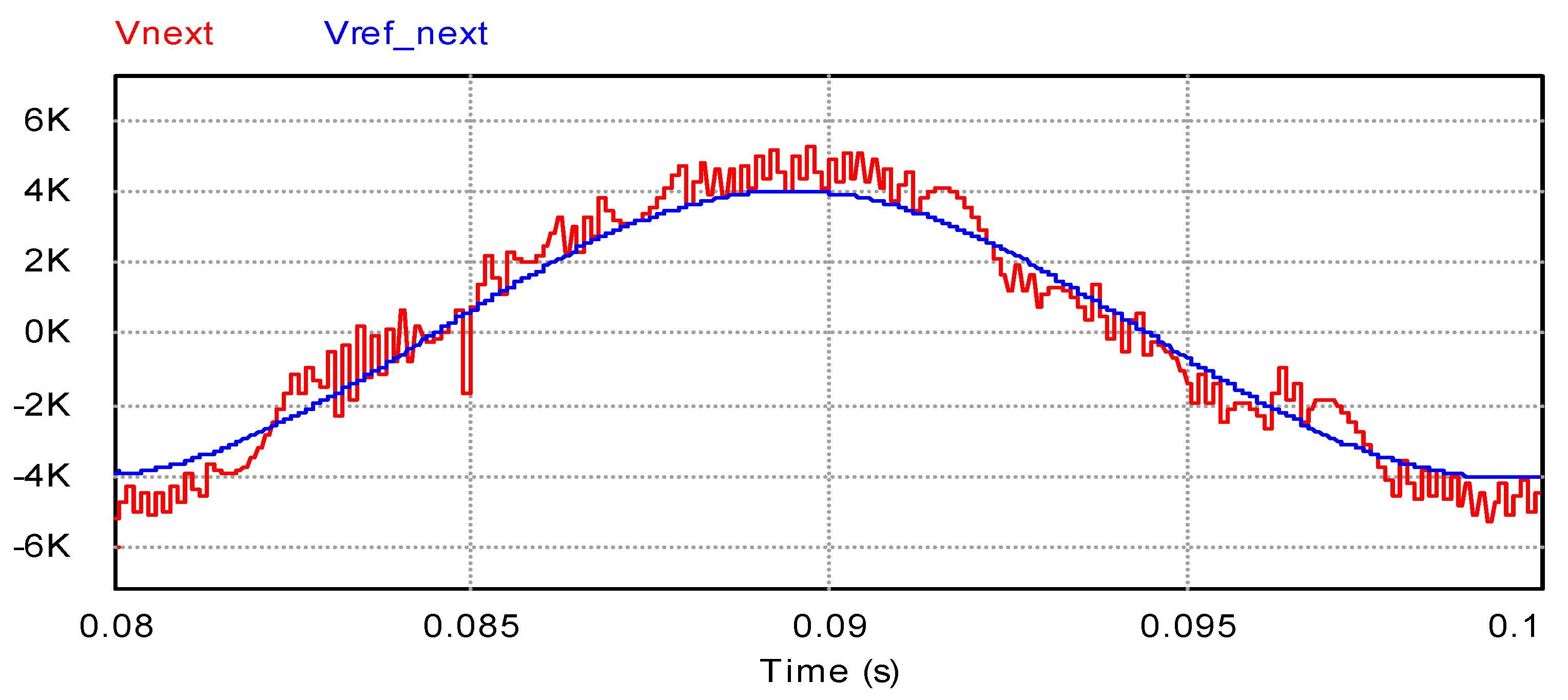

Figure 8.

The waveforms of Vac and Vacref.

Figure 8.

The waveforms of Vac and Vacref.

Figure 9.

The waveforms of Vac and Vacref.

Figure 9.

The waveforms of Vac and Vacref.

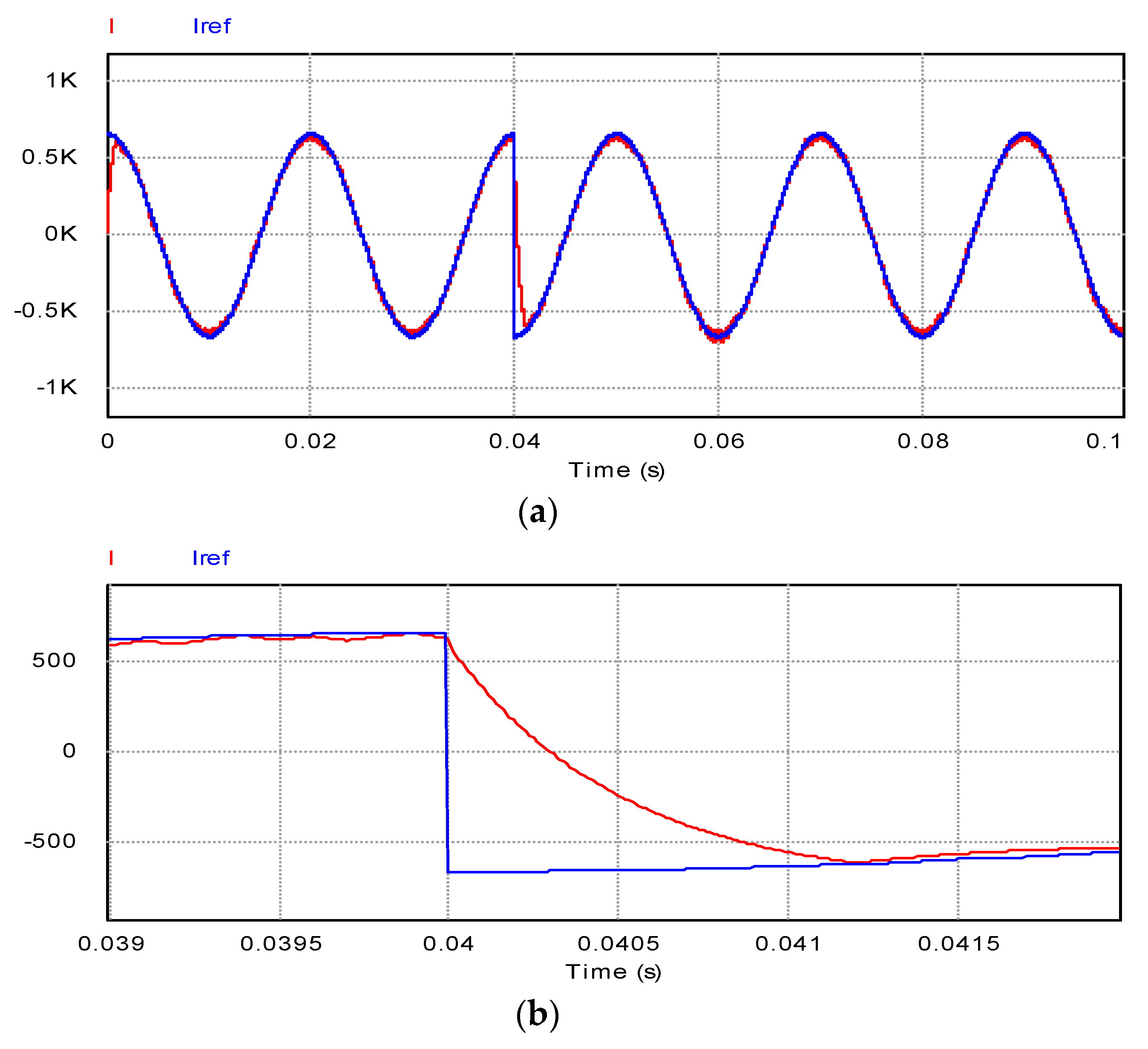

Figure 10.

Load current for a sudden change: (a) reference current and actual load current; (b) Detail of the reference current and actual load current at the instant.

Figure 10.

Load current for a sudden change: (a) reference current and actual load current; (b) Detail of the reference current and actual load current at the instant.

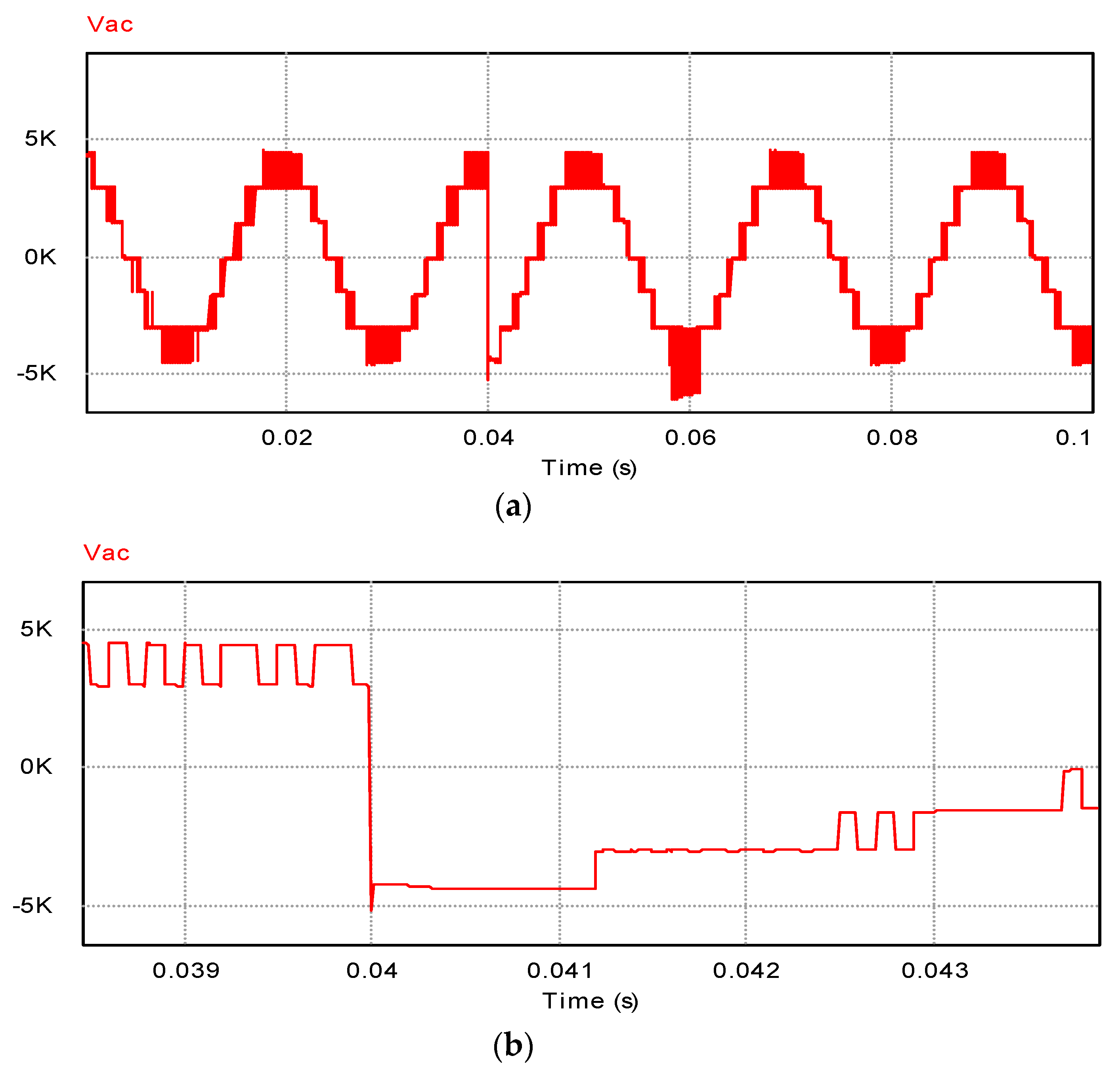

Figure 11.

Output AC voltage waveforms: (a) Output AC voltage ; (b) detail of the output AC voltage at the instant.

Figure 11.

Output AC voltage waveforms: (a) Output AC voltage ; (b) detail of the output AC voltage at the instant.

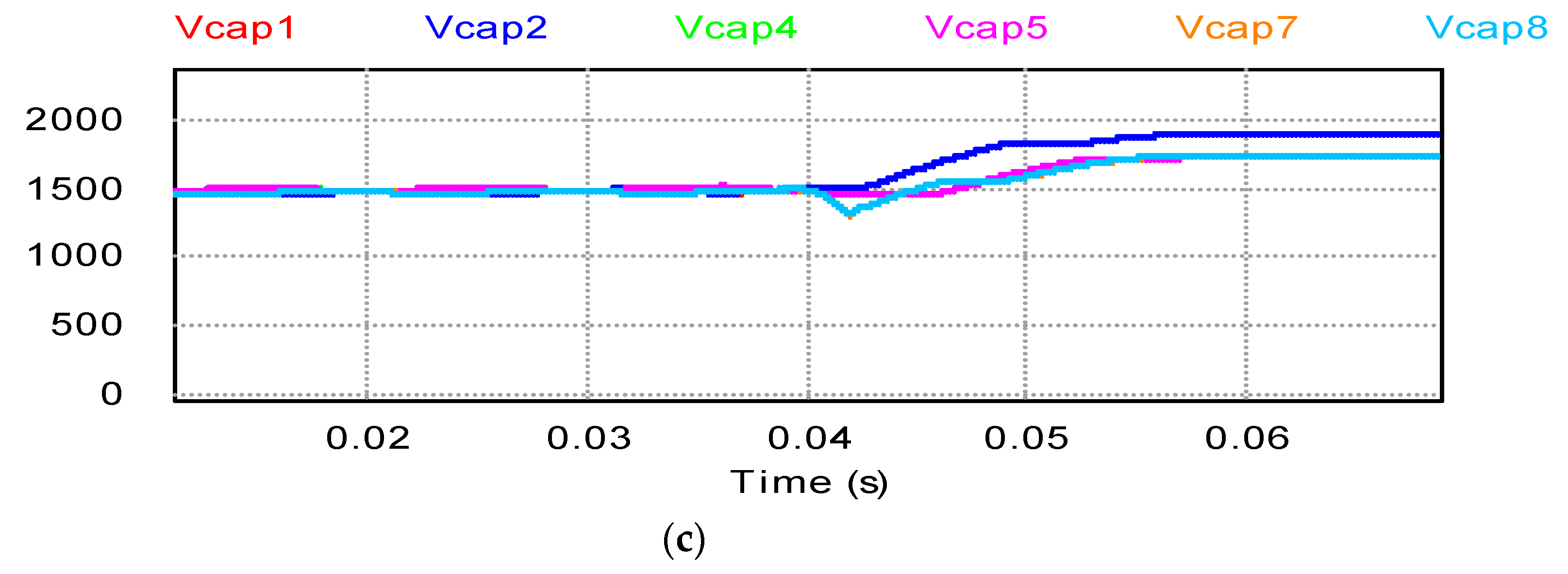

Figure 12.

Capacitor voltages of the sub-module.

Figure 12.

Capacitor voltages of the sub-module.

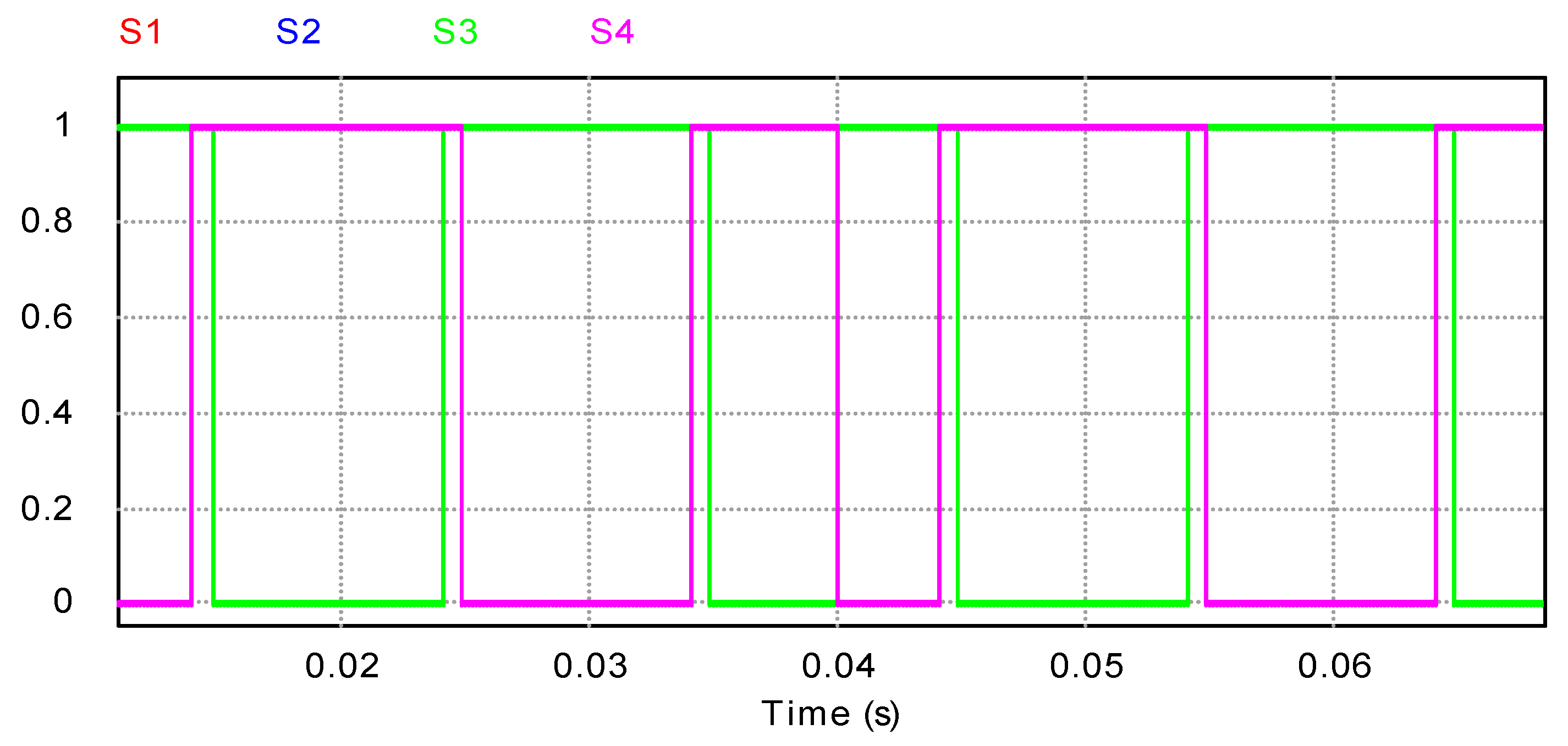

Figure 13.

Control signal of S1–S4.

Figure 13.

Control signal of S1–S4.

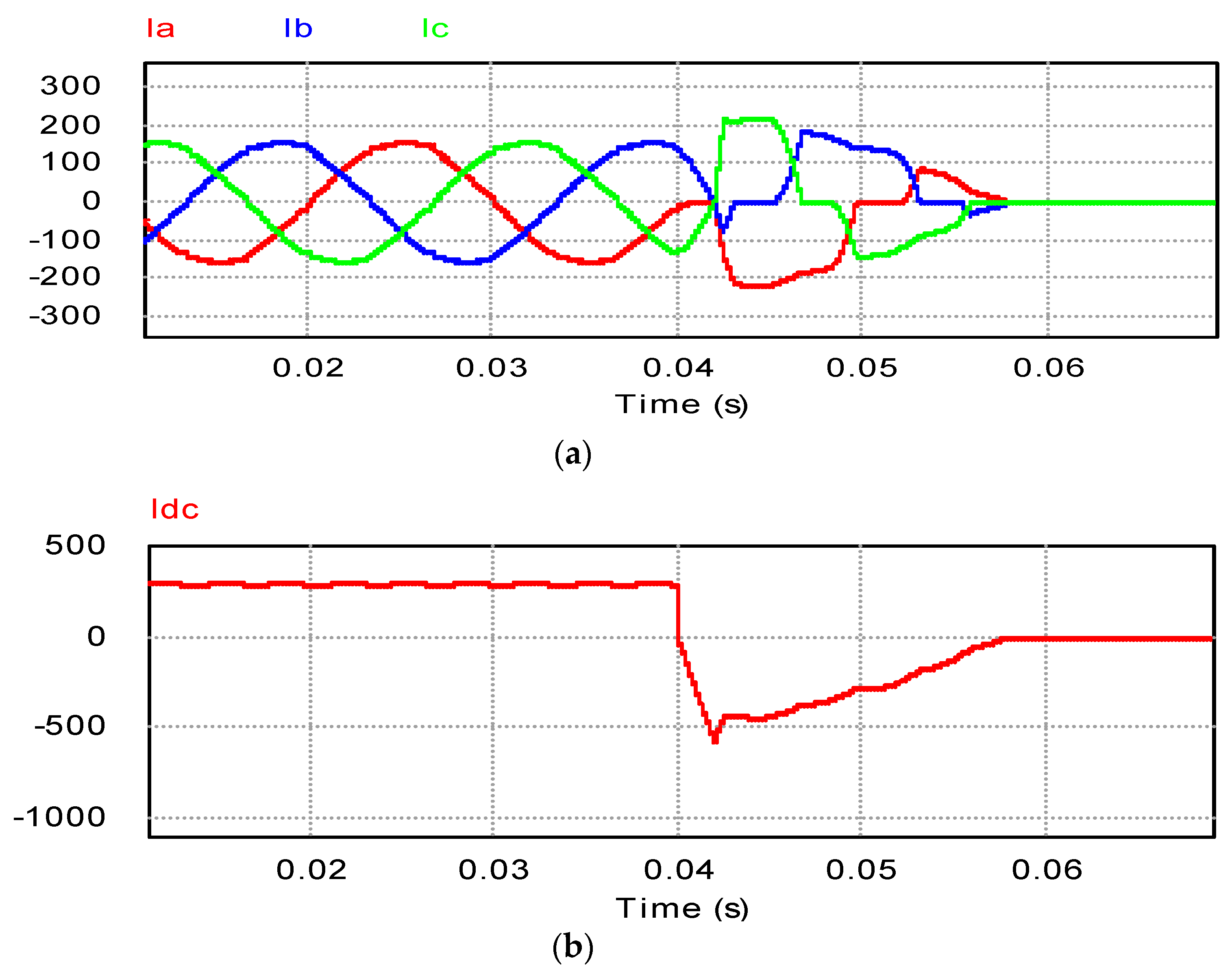

Figure 14.

Current and voltage simulation waveforms of a DC fault: (a) AC current; (b) DC current; (c) capacitor voltages.

Figure 14.

Current and voltage simulation waveforms of a DC fault: (a) AC current; (b) DC current; (c) capacitor voltages.

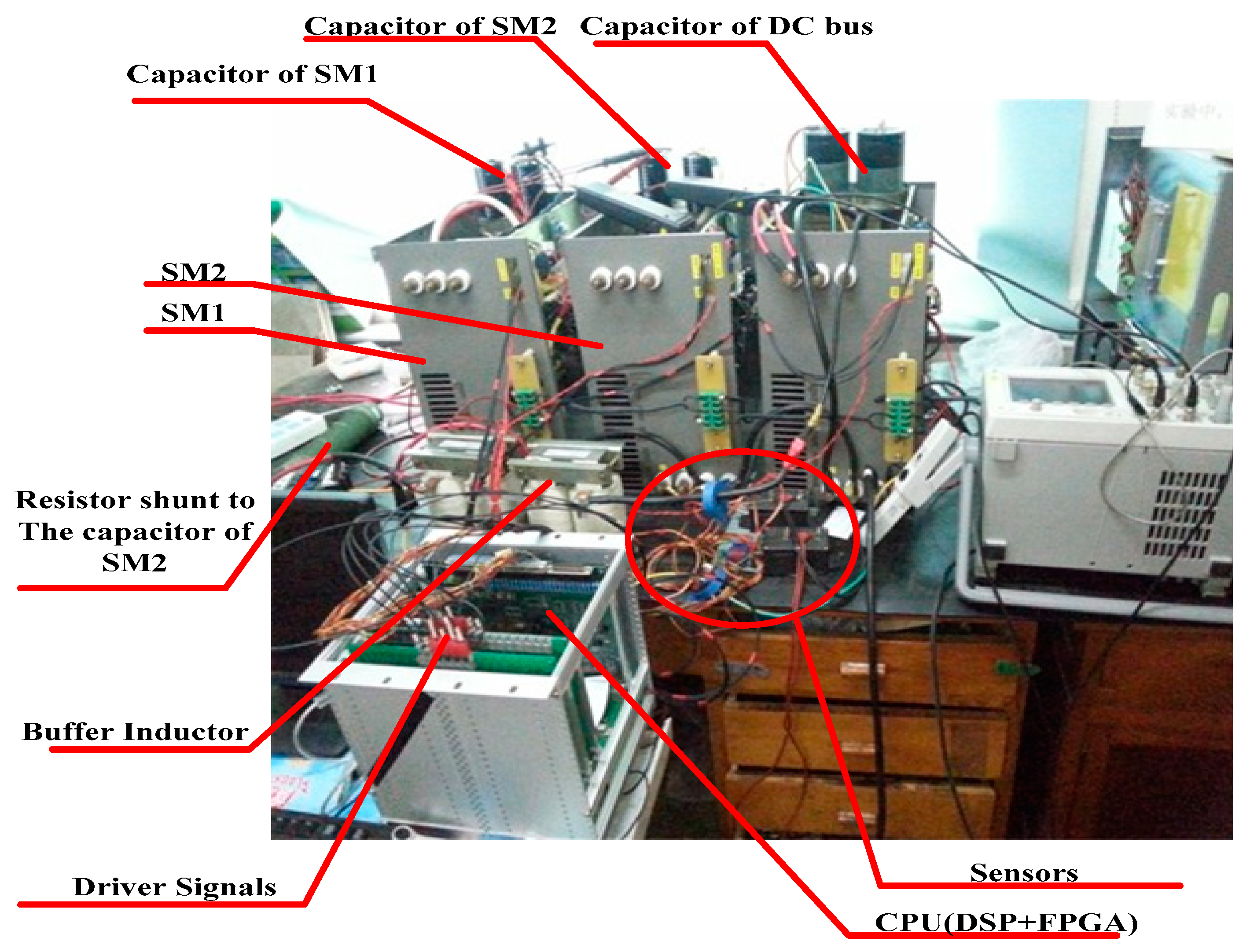

Figure 15.

Photo of the modular multilevel converter (MMC)-based inverter for the experiment.

Figure 15.

Photo of the modular multilevel converter (MMC)-based inverter for the experiment.

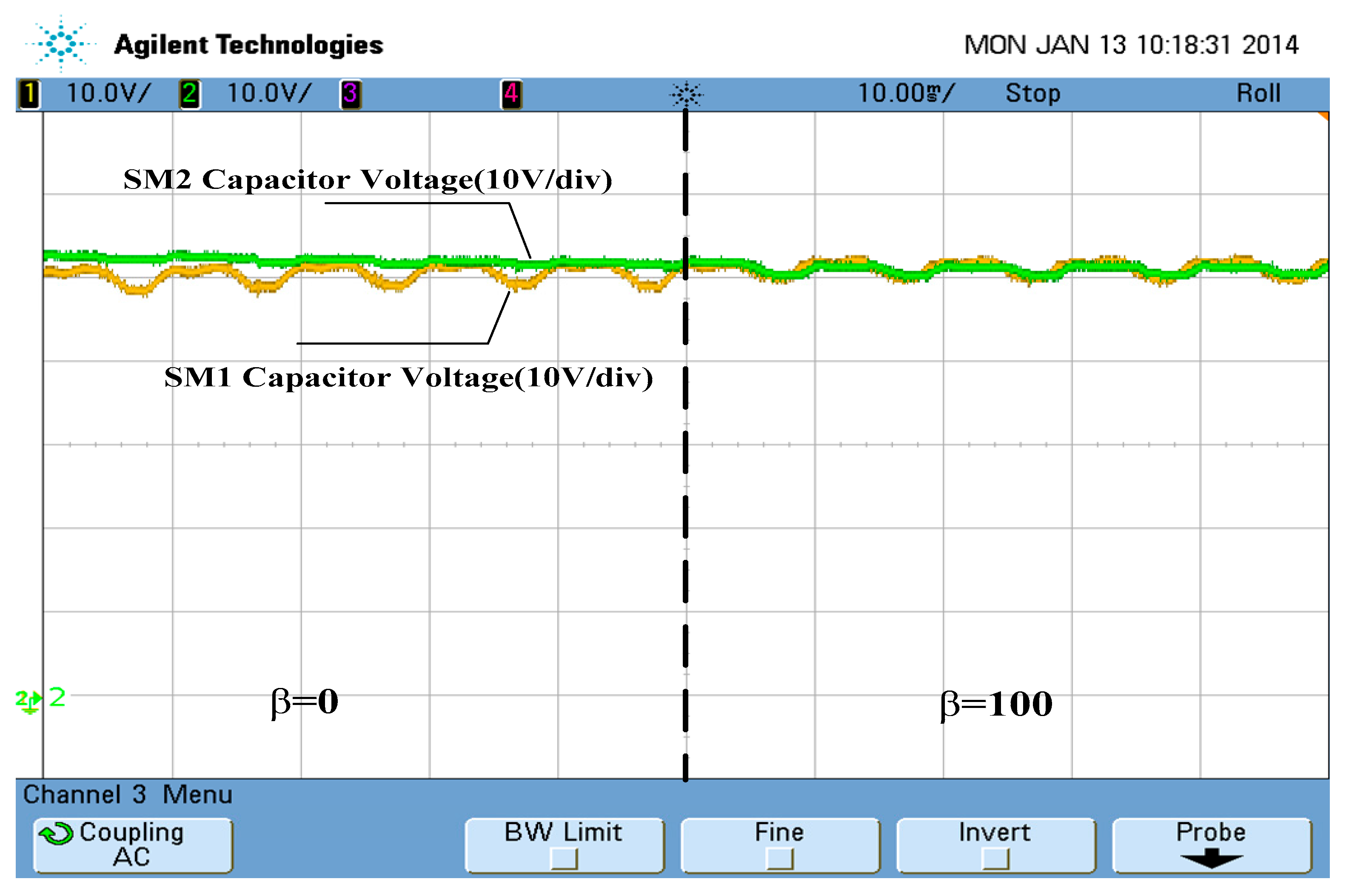

Figure 16.

weighting factor β’s effects on the capacitor voltages.

Figure 16.

weighting factor β’s effects on the capacitor voltages.

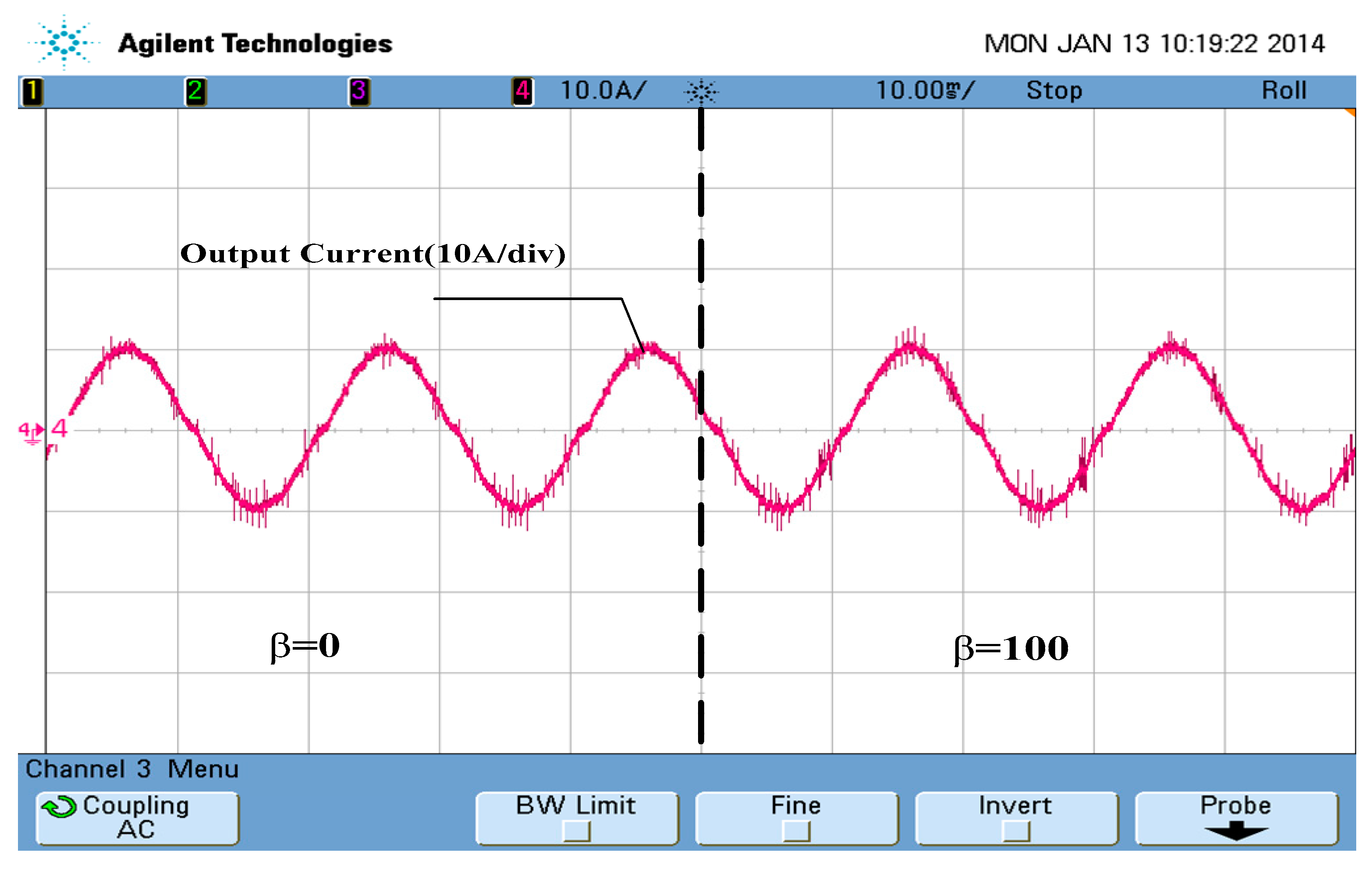

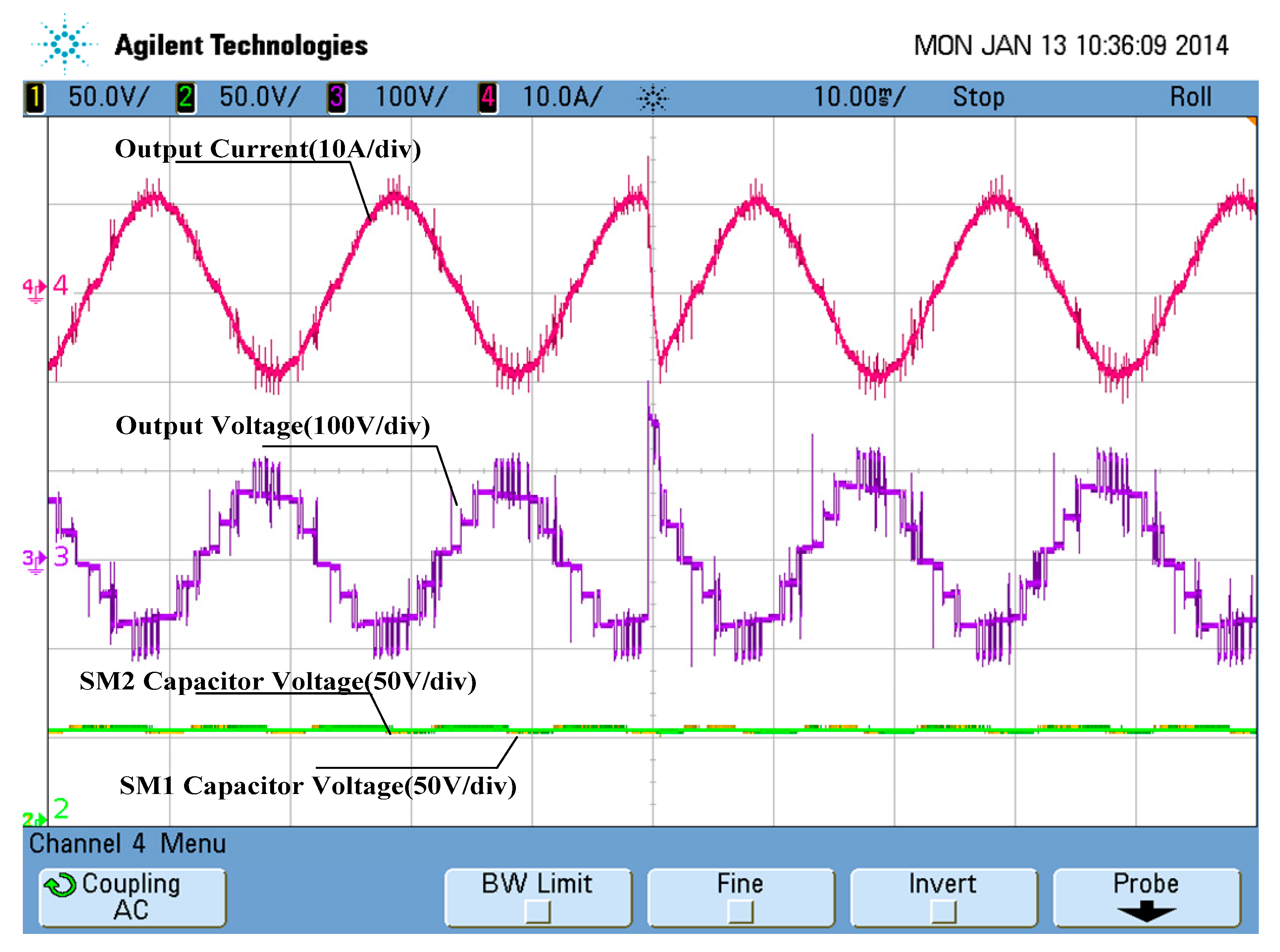

Figure 17.

The waveform of the output current under balanced and unbalanced conditions.

Figure 17.

The waveform of the output current under balanced and unbalanced conditions.

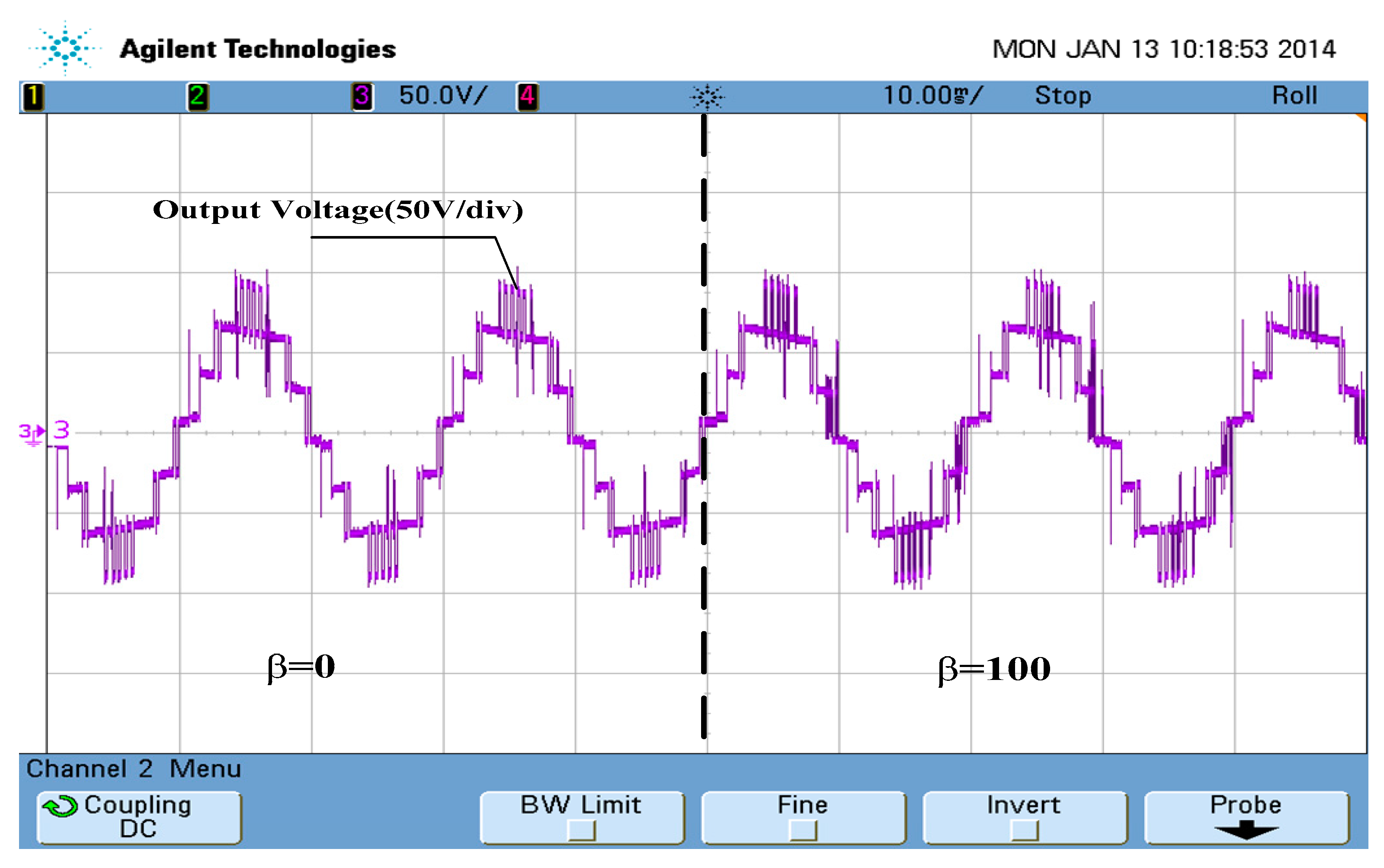

Figure 18.

The waveform of the output voltage under balanced and unbalanced conditions.

Figure 18.

The waveform of the output voltage under balanced and unbalanced conditions.

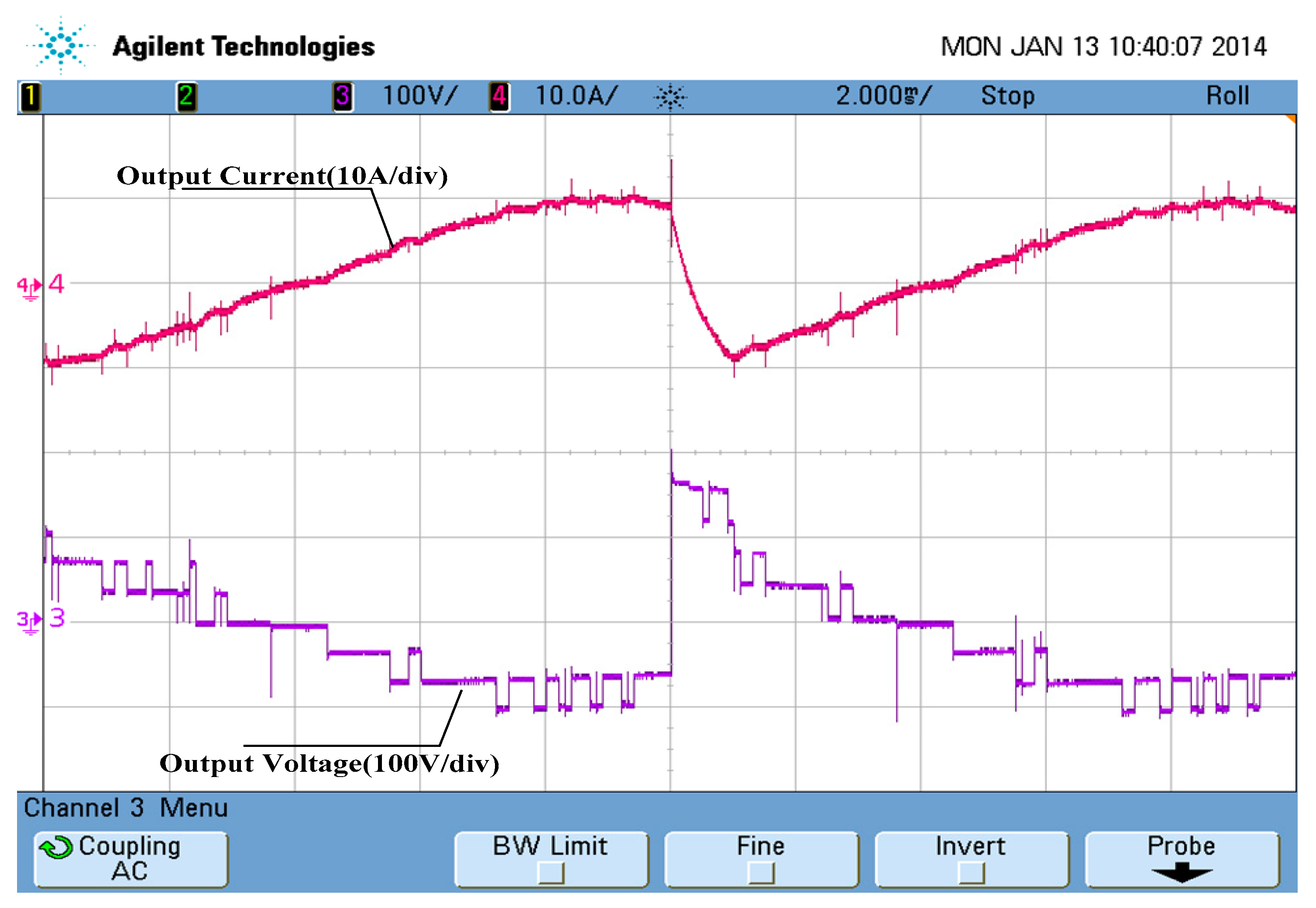

Figure 19.

Waveform of the voltage and current for a step in the angle of the reference current.

Figure 19.

Waveform of the voltage and current for a step in the angle of the reference current.

Figure 20.

Detail of the output voltage and current for a step in the angle of the reference current.

Figure 20.

Detail of the output voltage and current for a step in the angle of the reference current.

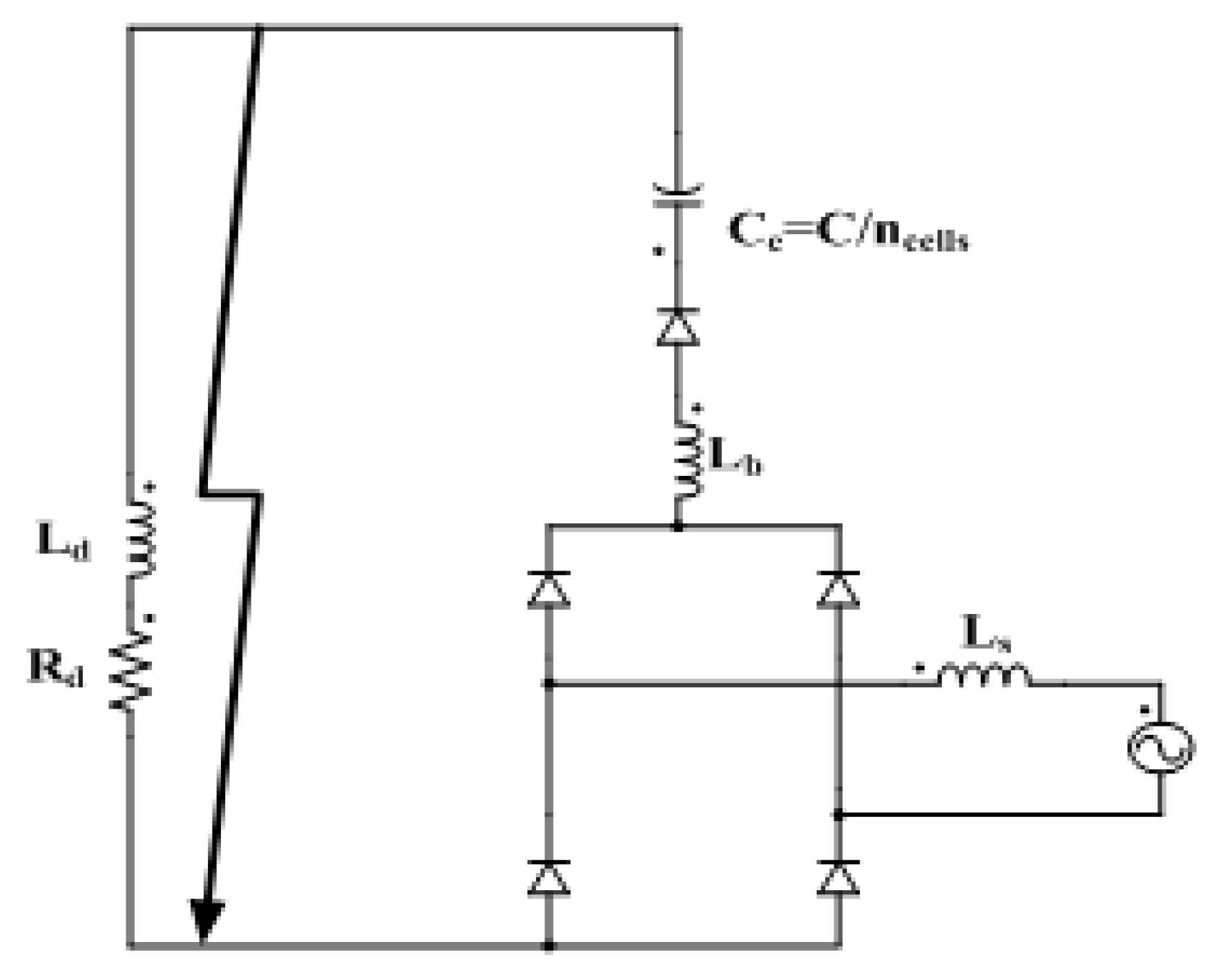

Figure 21.

The equivalent circuit of the insulated-gate bipolar transistors (IGBTs) blocking when a DC fault occurs.

Figure 21.

The equivalent circuit of the insulated-gate bipolar transistors (IGBTs) blocking when a DC fault occurs.

Table 1.

Switching states of director switches.

Table 1.

Switching states of director switches.

| Mode | Sd | S1 | S2 | S3 | S4 | Output Voltage (VAC) |

|---|

| Basic Operating Mode | 1 | ON | OFF | OFF | ON | VMN |

| −1 | OFF | ON | ON | OFF | −VMN |

| Energy Balancing Mode | 0 | ON | ON | ON | ON | 0 |

| 0 | ON | ON | OFF | OFF | 0 |

| 0 | OFF | OFF | ON | ON | 0 |

Table 2.

Parameters of the study system of

Figure 1b.

Table 2.

Parameters of the study system of

Figure 1b.

| DC voltage UDC | 3000 V |

| Submodule capacitor C | 3300 μF |

| Load inductance Ls | 3 mH |

| Buffer inductors Lb | 0.1 mH |

| Load inductance R | 6 |

| Sampling period Ts | 100 μs |

| Nominal frequencies f | 50 Hz |

| No. of cell in the stack of H-bridge cells | 2 |

Table 3.

Experiment parameters.

Table 3.

Experiment parameters.

| DC voltage UDC | 100 V |

| Submodule capacitor C | 3300 μF |

| Load inductance Ls | 3 mH |

| Buffer inductors Lb | 0.1 mH |

| Load inductance R | 6 |

| Sampling period Ts | 100 μs |

| Nominal frequencies f | 50 Hz |

| No. of cell in the stack of H-bridge cells | 2 |

Table 4.

Number of semiconductor devices and sub-module capacitors.

Table 4.

Number of semiconductor devices and sub-module capacitors.

| Topology | Number of Sub-Module Capacitor | Number of IGBTs | Number of Diodes |

|---|

| H-MMC | N | 2 N | 0 |

| F-MMC | N | 4 N | 0 |

| CH-MMC | N | 2.35 N | 0.7 N |

| AAMC | 0.34 N | 1.8 N | 0 |

| FA-MMC | 0.2 N | 1.6 N | 0 |

Table 5.

Losses calculation results

Table 5.

Losses calculation results

| Topology | Switching Losses | Conduction Losses | Total Losses |

|---|

| H-MMC | 0.29% | 0.82% | 1.11% |

| F-MMC | 0.29% | 1.88% | 2.18% |

| CH-MMC | 0.29% | 1.19% | 1.48% |

| AAMC | 0.16% | 0.47% | 0.63% |

| FA-MMC | 0.16% | 0.66% | 0.82% |

Table 6.

Comprehensive comparison with other various topology

Table 6.

Comprehensive comparison with other various topology

| Topology | Economy | Efficiency | Volume | DC Fault Blocking Capacity | Demand for Insulation |

|---|

| H-MMC | +++ | +++ | + | + | + |

| F-MMC | + | + | + | ++ | + |

| CH-MMC | ++ | ++ | + | ++ | + |

| AAMC | ++++ | +++++ | ++ | ++ | ++ |

| FA-MMC | +++++ | ++++ | +++ | ++ | +++ |