Research on the Neutral-Point Voltage Balance for NPC Three-Level Inverters under Non-Ideal Grid Conditions

Abstract

:1. Introduction

2. Mathematical Analysis of the Neutral-Point Voltage under Non-Ideal Grid Conditions

3. Proposed NP Voltage Balance Method under Non-Ideal Grid Conditions

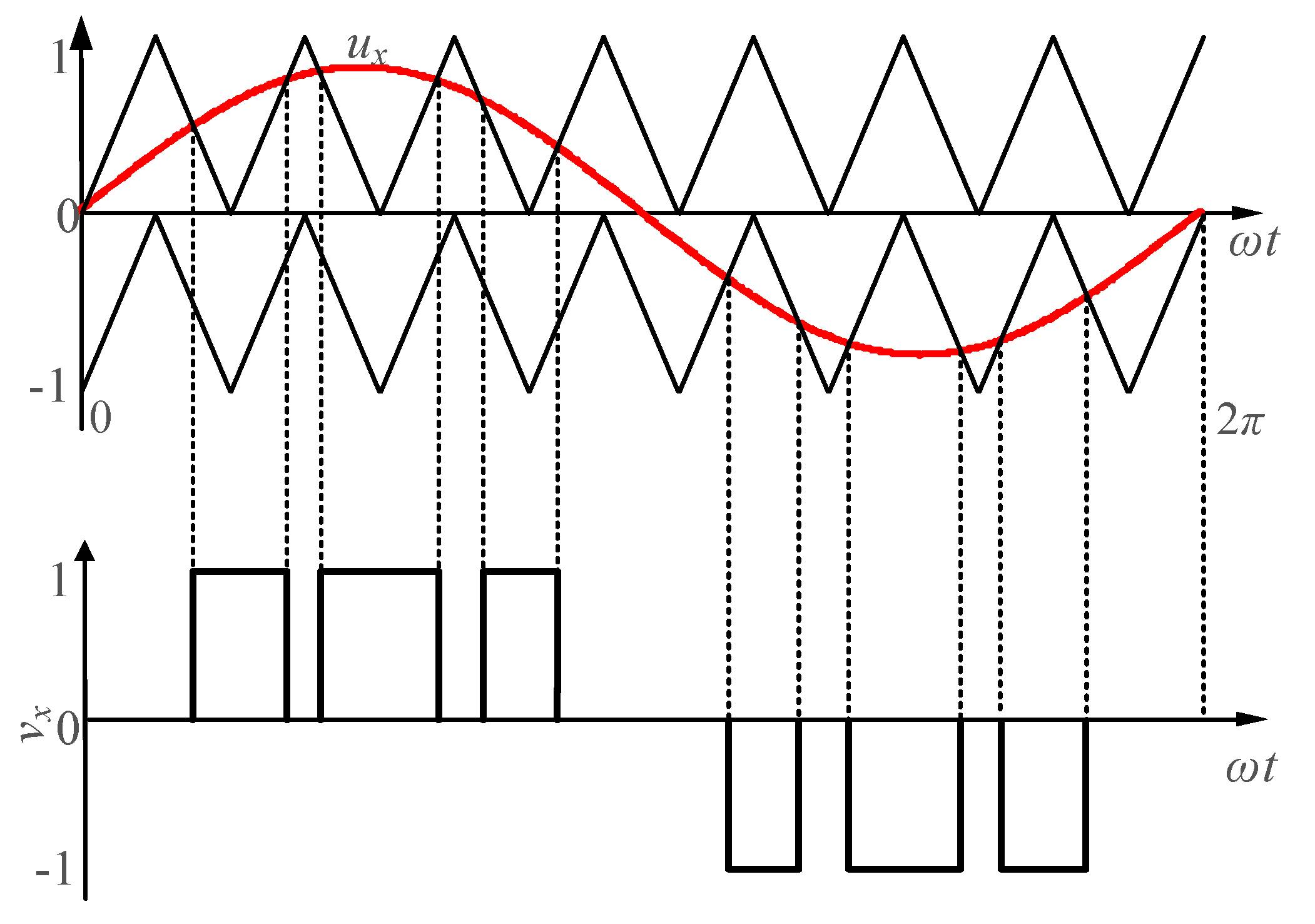

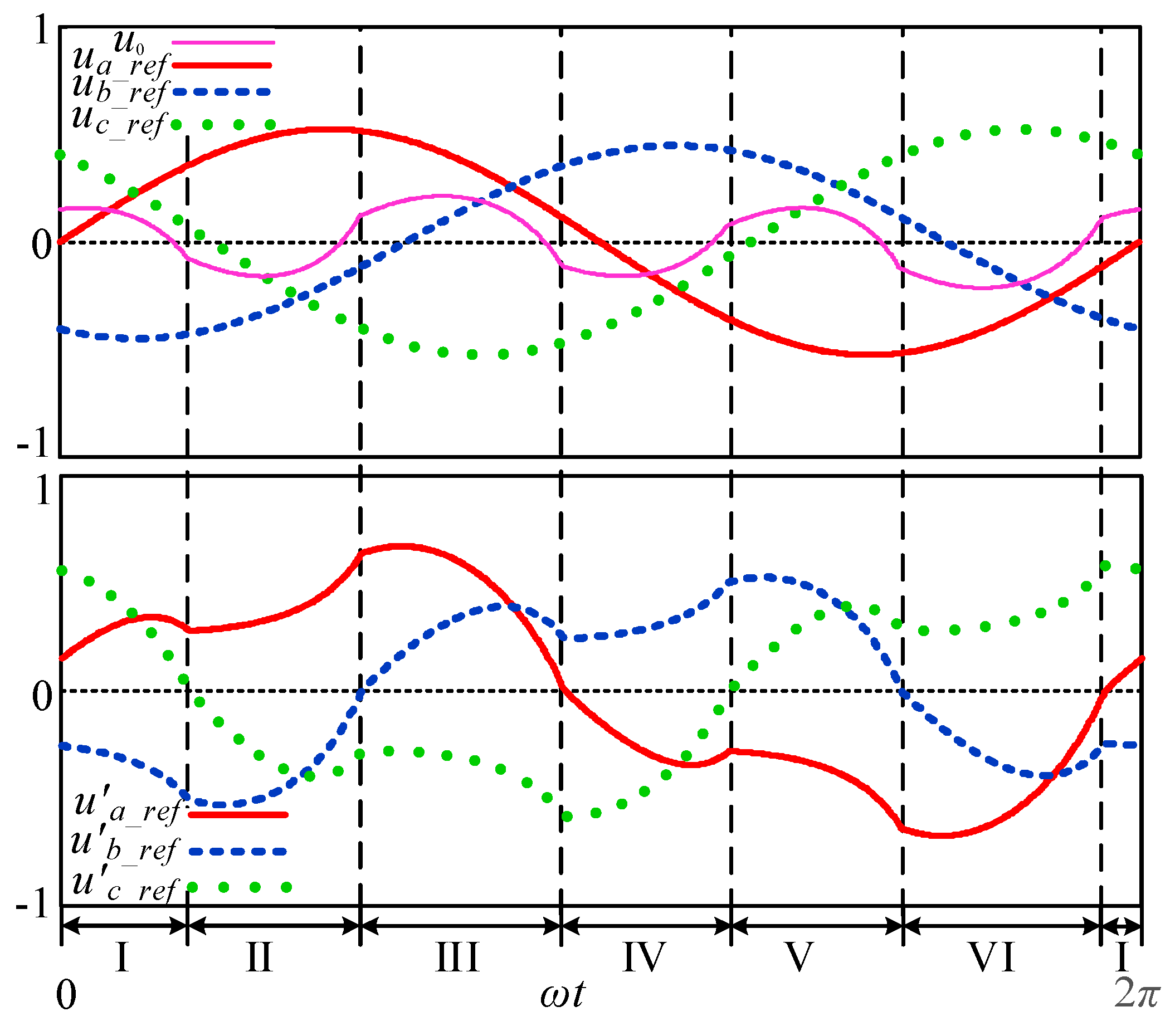

3.1. Analysis of Zero-Sequence Component for Modulation Signals

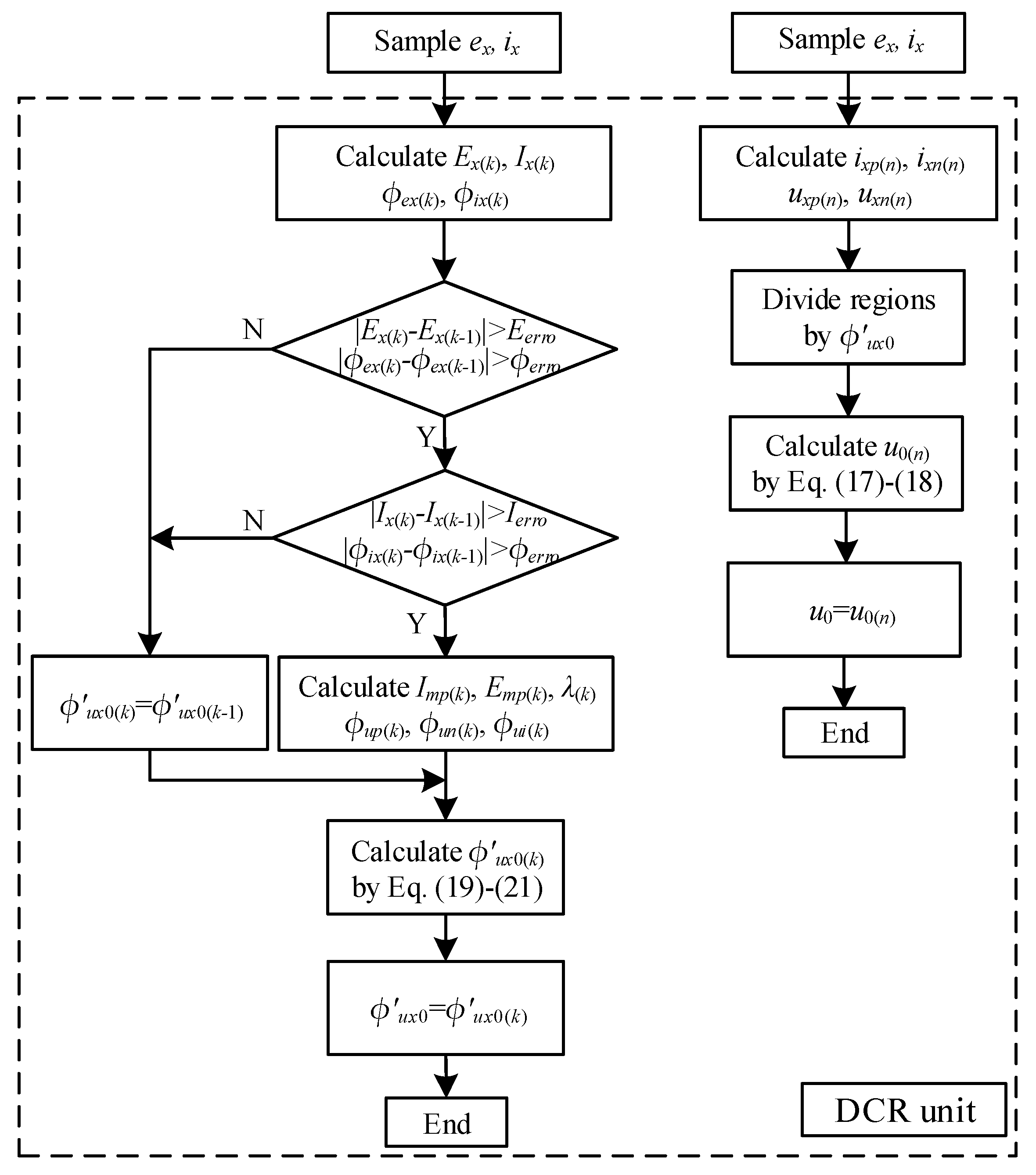

3.2. Design of the NP Voltage Balance Controller

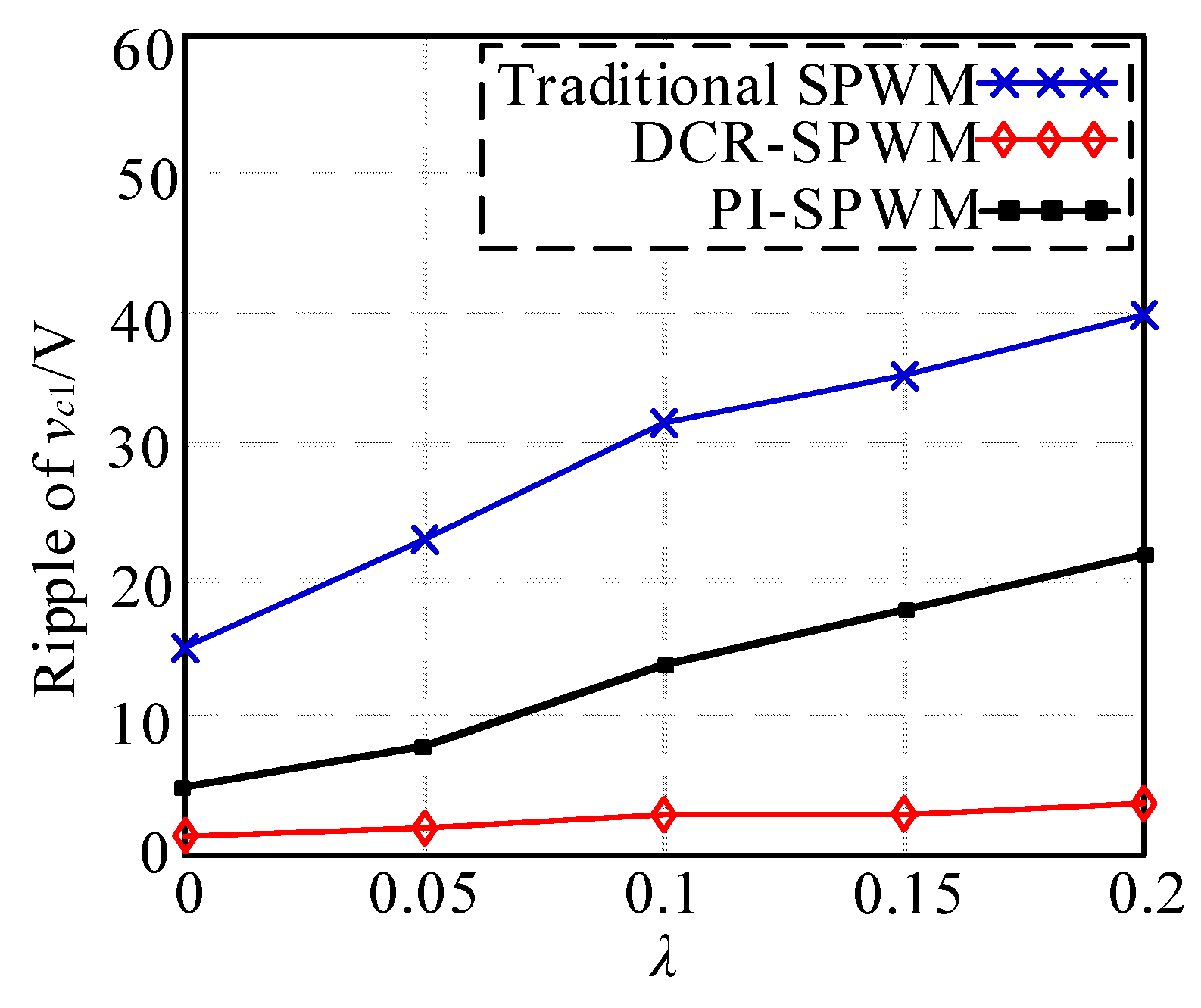

4. Performance Analysis

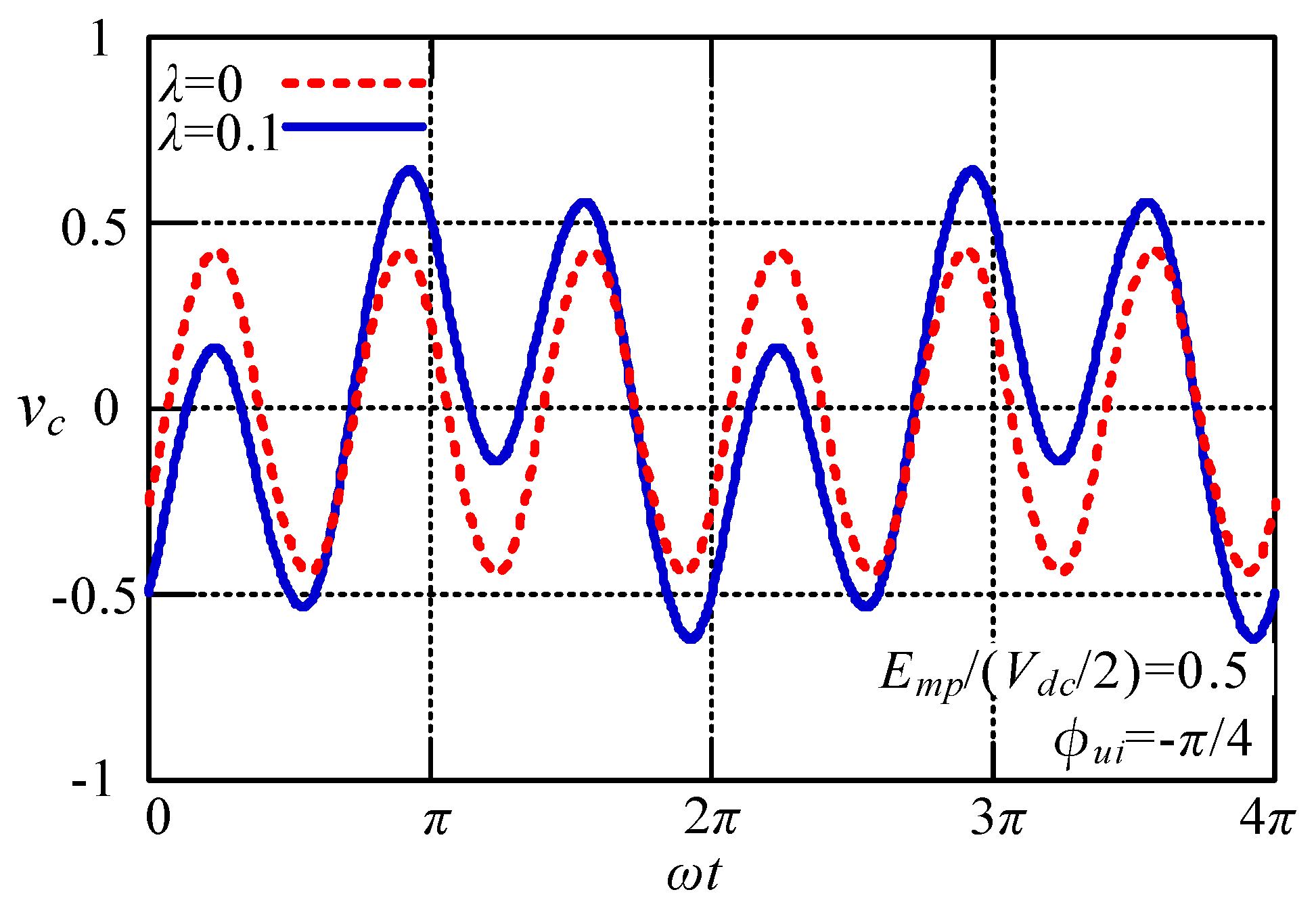

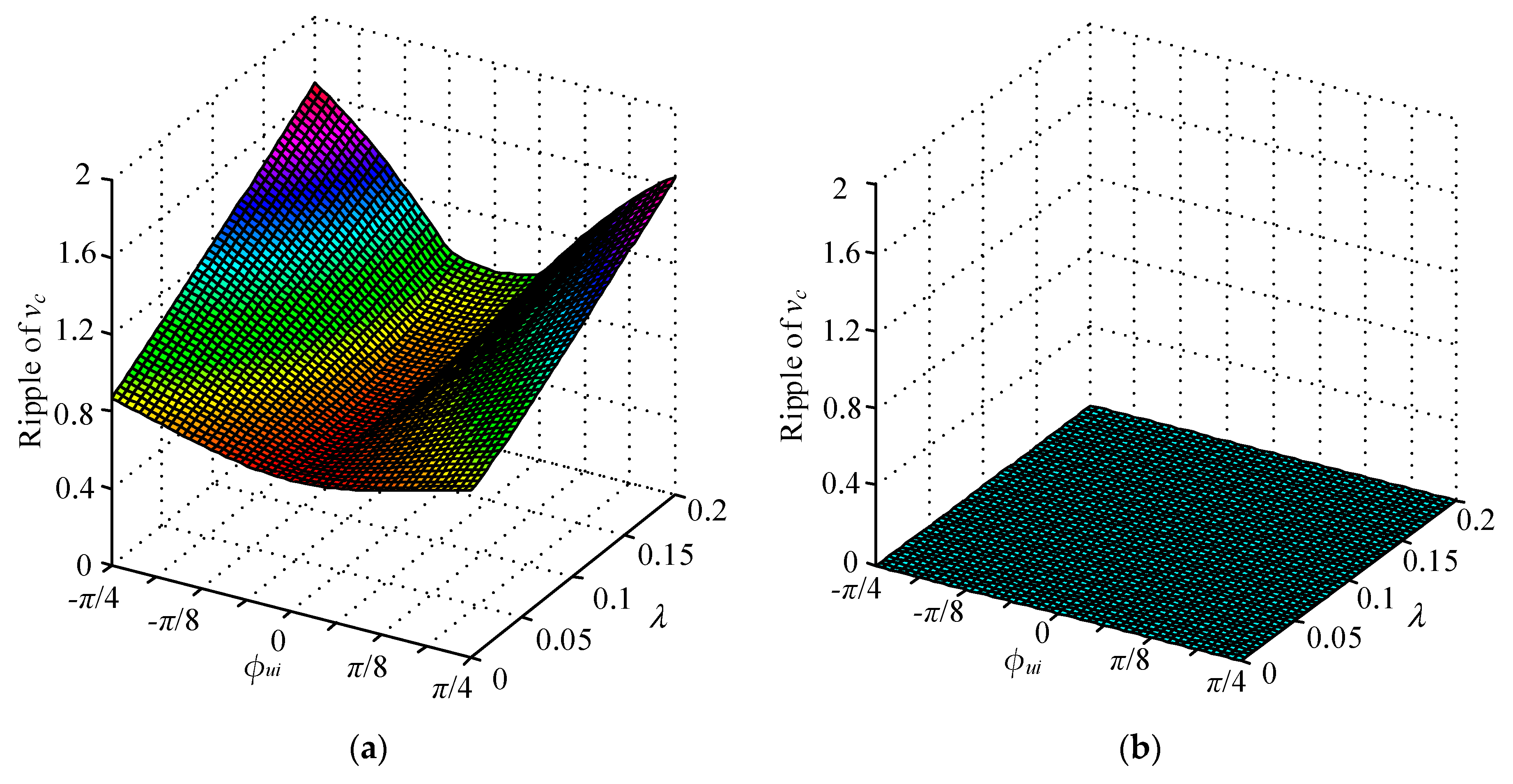

4.1. Analysis of the NP Voltage Fluctuation

4.2. Analysis of the Grid Current Harmonics

5. Simulation and Experimental Verification

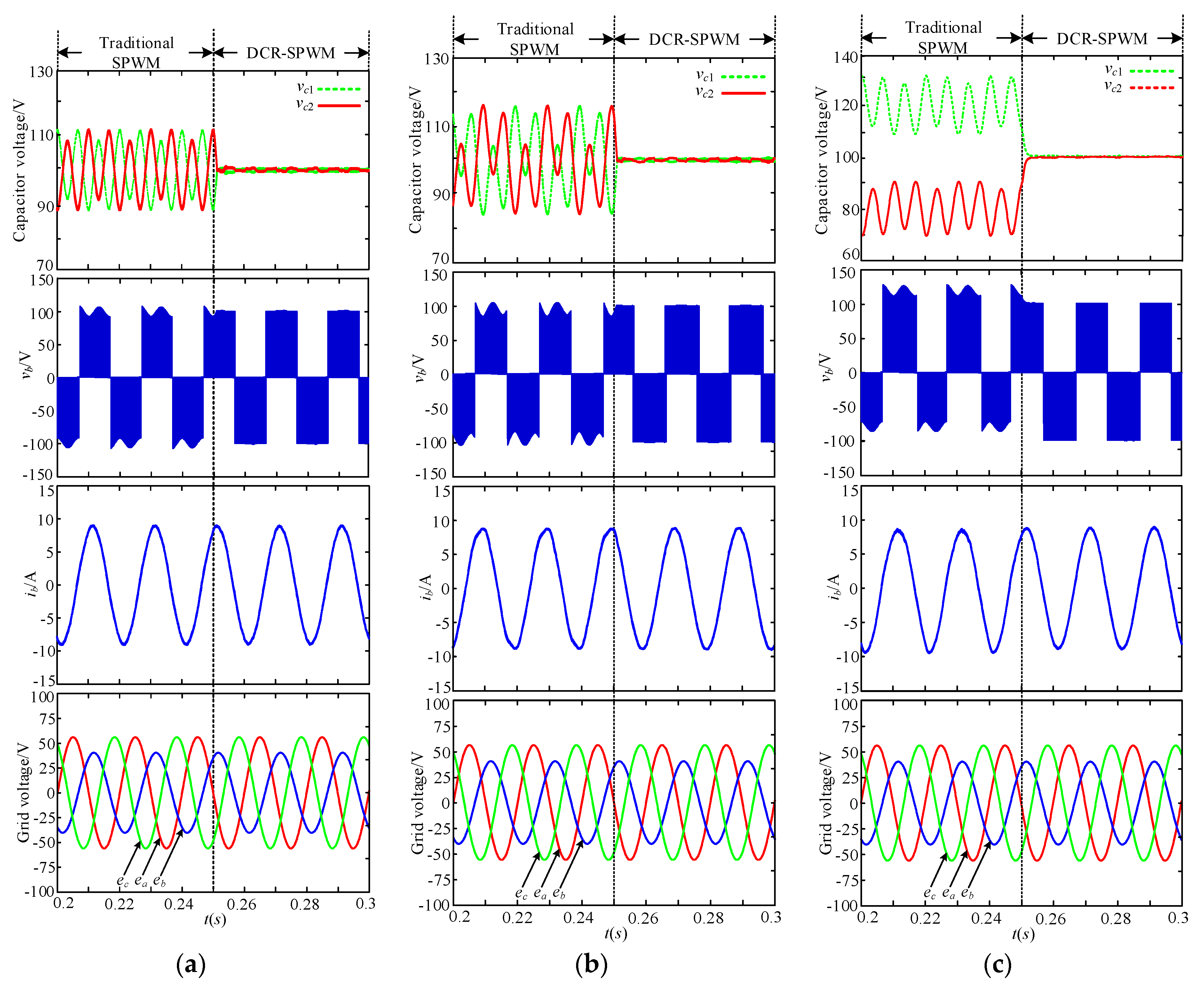

5.1. Simulation Analysis

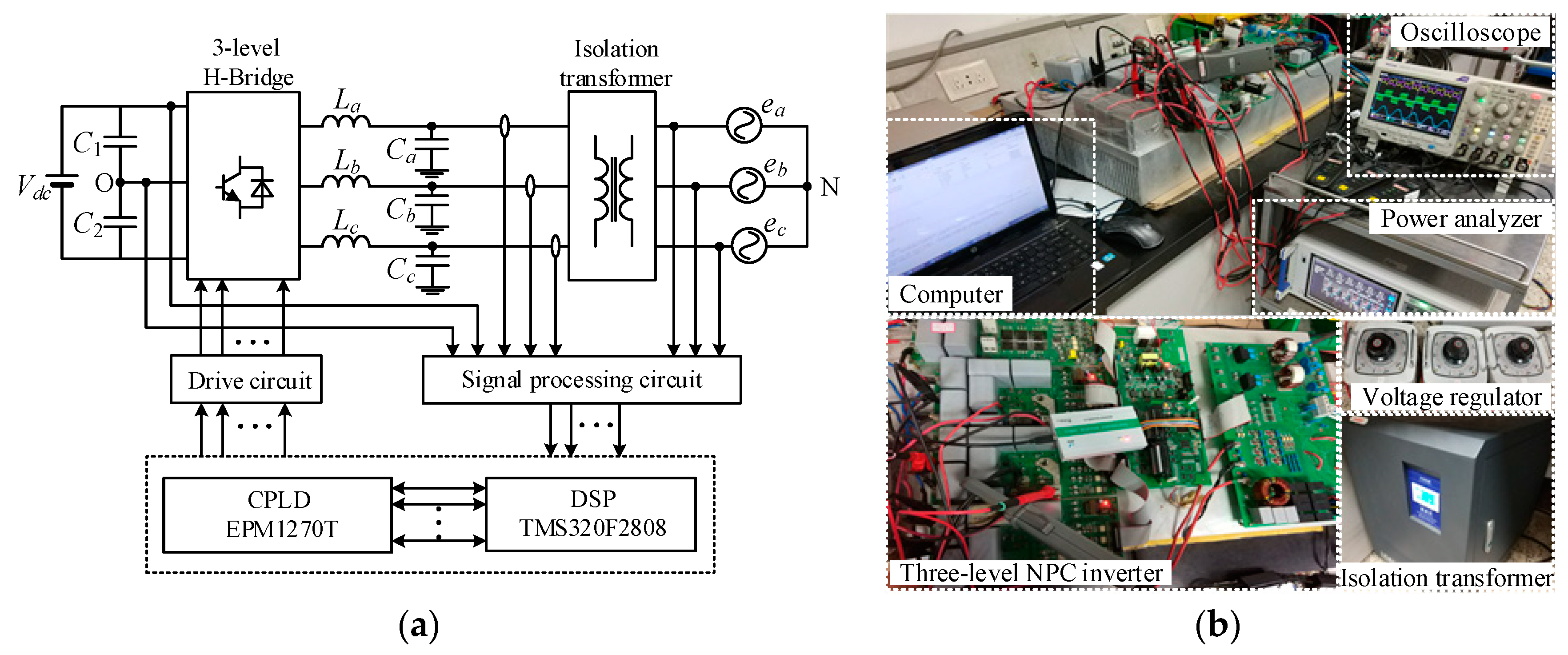

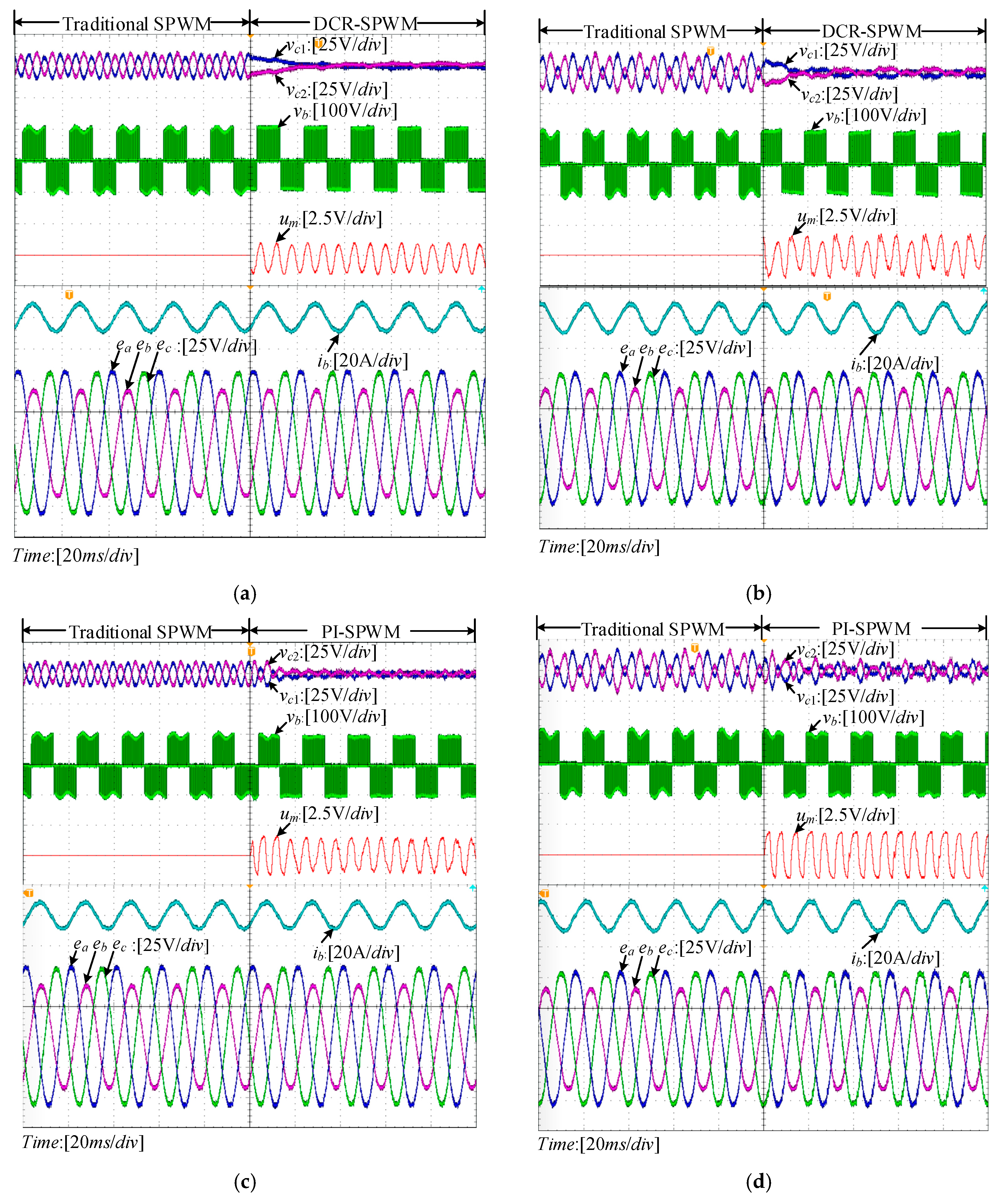

5.2. Experimental Verification

6. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Wang, Y.; Wang, F. Novel Three-Phase Three-Level-Stacked Neutral Point Clamped Grid-Tied Solar Inverter with a Split Phase Controller. IEEE Trans. Power Electron. 2013, 28, 2856–2866. [Google Scholar] [CrossRef]

- Teymour, H.R.; Sutanto, D.; Muttaqi, K.M.; Ciufo, P. Solar PV and Battery Storage Integration Using a New Configuration of a Three-Level NPC Inverter with Advanced Control Strategy. IEEE Trans. Energy Convers. 2014, 29, 354–365. [Google Scholar]

- Zhang, Y.; Li, J.; Li, X.; Cao, Y.; Sumner, M.; Xia, C. A Method for the Suppression of Fluctuations in the Neutral-Point Potential of a Three-Level NPC Inverter with a Capacitor-Voltage Loop. IEEE Trans. Power Electron. 2017, 32, 825–836. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Zaragoza, J.; Pou, J.; Ceballos, S.; Robles, E.; Ibanez, P.; Villate, J.L. A Comprehensive Study of a Hybrid Modulation Technique for the Neutral-Point-Clamped Converter. IEEE Trans. Ind. Electron. 2009, 56, 294–304. [Google Scholar] [CrossRef]

- Choi, U.M.; Lee, H.H.; Lee, K.B. Simple Neutral-Point Voltage Control for Three-Level Inverters Using a Discontinuous Pulse Width Modulation. IEEE Trans. Energy Convers. 2013, 28, 434–443. [Google Scholar] [CrossRef]

- Shen, J.; Schröder, S.; Rösner, R.; El-Barbari, S. A Comprehensive Study of Neutral-Point Self-Balancing Effect in Neutral-Point-Clamped Three-Level Inverters. IEEE Trans. Power Electron. 2011, 26, 3084–3095. [Google Scholar] [CrossRef]

- Choi, U.M.; Lee, J.S.; Lee, K.B. New modulation strategy to balance the neutral-point voltage for three-level neutral-clamped inverter systems. IEEE Trans. Energy Convers. 2014, 29, 91–100. [Google Scholar] [CrossRef]

- Sebaaly, F.; Vahedi, H.; Kanaan, H.Y.; Al-Haddad, K. Novel Current Controller Based on MPC With Fixed Switching Frequency Operation for a Grid-Tied Inverter. IEEE Trans. Ind. Electron. 2018, 65, 6198–6205. [Google Scholar] [CrossRef]

- Sebaaly, F.; Vahedi, H.; Kanaan, H.Y.; Moubayed, N.; Al-Haddad, K. Sliding Mode Fixed Frequency Current Controller Design for Grid-Connected NPC Inverter. IEEE Trans. Power Electron. 2016, 4, 1397–1405. [Google Scholar] [CrossRef]

- López, I.; Ceballos, S.; Pou, J.; Zaragoza, J.; Andreu, J.; Ibarra, E.; Konstantinou, G. Generalized PWM-based method for multiphase neutral-point-clamped converters with capacitor voltage balance capability. IEEE Trans. Power Electron. 2017, 32, 4878–4890. [Google Scholar] [CrossRef]

- Wang, C.; Li, Y. Analysis and calculation of zero-sequence voltage considering neutral-point potential balancing in three-level NPC converters. IEEE Trans. Ind. Electron. 2010, 57, 2262–2271. [Google Scholar] [CrossRef]

- Chaturvedi, P.; Jain, S.; Agarwal, P. Carrier-based neutral point potential regulator with reduced switching losses for three-level diode-clamped inverter. IEEE Trans. Ind. Electron. 2014, 61, 613–624. [Google Scholar] [CrossRef]

- Maheshwari, R.; Munk-Nielsen, S.; Busquets-Monge, S. Design of neutral-point voltage controller of a three-level NPC inverter with small DC-link capacitors. IEEE Trans. Ind. Electron. 2013, 60, 1861–1871. [Google Scholar] [CrossRef]

- Shayestehfard, A.; Mekhilef, S.; Mokhlis, H. IZDPWM-based feedforward controller for grid-connected inverters under unbalanced and distorted conditions. IEEE Trans. Ind. Electron. 2017, 64, 14–21. [Google Scholar] [CrossRef]

- Yan, Q.; Wu, X.; Yuan, X.; Geng, Y. An Improved Grid-Voltage Feedforward Strategy for High-Power Three-Phase Grid-Connected Inverters Based on the Simplified Repetitive Predictor. IEEE Trans. Power Electron. 2016, 31, 3880–3897. [Google Scholar] [CrossRef]

- Teodorescu, R.; Liserre, M.; Rodríguez, P. Grid Converters for Photovoltaic and Wind Power Systems; John Wiley & Sons: Hoboken, NJ, USA, 2011; pp. 171–172. [Google Scholar]

- Ma, K.; Blaabjerg, F. Modulation Methods for Neutral-Point-Clamped Wind Power Converter Achieving Loss and Thermal Redistribution under Low-Voltage Ride-Through. IEEE Trans. Ind. Electron. 2014, 61, 835–845. [Google Scholar] [CrossRef]

- Shao, Z.; Zhang, X.; Wang, F.; Cao, R.; Ni, H. Analysis and Control of Neutral-Point Voltage for Transformerless Three-Level PV Inverter in LVRT Operation. IEEE Trans. Power Electron. 2017, 32, 2347–2359. [Google Scholar] [CrossRef]

- Vahedi, H.; Labbe, P.A.; Al-Haddad, K. Balancing three-level neutral point clamped inverter DC bus using closed-loop space vector modulation: Real-time implementation and investigation. IET Power Electron. 2016, 9, 2076–2084. [Google Scholar] [CrossRef]

- Sebaaly, F.; Vahedi, H.; Kanaan, H.Y.; Moubayed, N.; Al-Haddad, K. Design and Implementation of Space Vector Modulation-Based Sliding Mode Control for Grid-Connected 3L-NPC Inverter. IEEE Trans. Ind. Electron. 2016, 63, 7854–7863. [Google Scholar] [CrossRef]

- Jung, K.; Suh, Y. Compensation of neutral point deviation in 3-level NPC converter under unbalanced grid conditions. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Long Beach, CA, USA, 20–24 March 2016; pp. 17–24. [Google Scholar]

- Jung, K.; Suh, Y. Analysis of neutral point deviation in 3-level NPC converter under unbalanced 3-phase AC grid. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- Von Jouanne, A.; Dai, S.; Zhang, H. A multilevel inverter approach providing DC-link balancing, ride-through enhancement, and common-mode voltage elimination. IEEE Trans. Ind. Electron. 2002, 49, 739–745. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B. Predictive control of a three-level boost converter and an NPC inverter for high-power PMSG-based medium voltage wind energy conversion systems. IEEE Trans. Power Electron. 2014, 29, 5308–5322. [Google Scholar] [CrossRef]

- Zhang, M.; Hang, L.; Yao, W.; Lu, Z.; Tolbert, L.M. A Novel Strategy for Three-Phase/Switch/Level (Vienna) Rectifier under Severe Unbalanced Grids. IEEE Trans. Ind. Electron. 2013, 60, 4243–4252. [Google Scholar] [CrossRef]

- Nejabatkhah, F.; Li, Y.W.; Wu, B. Control Strategies of Three-Phase Distributed Generation Inverters for Grid Unbalanced Voltage Compensation. IEEE Trans. Power Electron. 2016, 31, 5228–5241. [Google Scholar]

- Holmes, D.G.; Lipo, T.A. Pulse width Modulation for Power Converters: Principles and Practice; John Wiley & Sons: Hoboken, NJ, USA, 2003; pp. 473–479. [Google Scholar]

| Coefficient | Expressions |

|---|---|

| Aa | |

| Ba | |

| Ca | |

| Ab | |

| Bb | |

| Cb | |

| Ac | |

| Bc | |

| Cc |

| Specifications of the Prototype | |

|---|---|

| DC bus voltage | Vdc = 200 V |

| DC bus capacitors | C1 = C2 = 150 μF |

| Switching frequency | fs = 16 kHz |

| Apparent power | S = 600 VA |

| The amplitude of grid voltages | Ema = 55 V, Emb = 40 V, Emc = 55 V |

| Output phase filter | L: 1.5 mH, C: 15 μF |

| The Specifications of the Experimental Prototype | |

|---|---|

| DC bus voltage | Vdc = 200 V |

| DC bus capacitors | C1 = C2 = 150 μF |

| Switching frequency | fs = 16 kHz |

| Apparent power | S = 600 VA |

| Digital Process Unit | DSP: TMS320F2808, CPLD: EPM1270T |

| Power switches module | IGBT FZ06NPA070FP |

| Output phase filter | L: 1.5 mH, C: 15 μF |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lyu, J.G.; Wang, J.D.; Hu, W.B.; Wu, Z.F. Research on the Neutral-Point Voltage Balance for NPC Three-Level Inverters under Non-Ideal Grid Conditions. Energies 2018, 11, 1331. https://doi.org/10.3390/en11061331

Lyu JG, Wang JD, Hu WB, Wu ZF. Research on the Neutral-Point Voltage Balance for NPC Three-Level Inverters under Non-Ideal Grid Conditions. Energies. 2018; 11(6):1331. https://doi.org/10.3390/en11061331

Chicago/Turabian StyleLyu, Jian Guo, Ji Dong Wang, Wen Bin Hu, and Zhao Feng Wu. 2018. "Research on the Neutral-Point Voltage Balance for NPC Three-Level Inverters under Non-Ideal Grid Conditions" Energies 11, no. 6: 1331. https://doi.org/10.3390/en11061331

APA StyleLyu, J. G., Wang, J. D., Hu, W. B., & Wu, Z. F. (2018). Research on the Neutral-Point Voltage Balance for NPC Three-Level Inverters under Non-Ideal Grid Conditions. Energies, 11(6), 1331. https://doi.org/10.3390/en11061331