1. Introduction

The term “multilevel” began when Nabae performed the three-level converter in 1981. In this study, a three-level neutral point clamp (NPC) was proposed [

1]. Subsequently, several multilevel converter topologies have been developed [

2,

3,

4,

5]. In recent years, many multilevel converter topologies have been proposed and have gained attention in many applications, especially in the interface for the grid connection of photovoltaic (PV) systems [

3]. The most common multilevel inverter (MLI) topologies can be classified into three types: neutral point MLI, flying capacitor MLI, and cascaded H-bridge (CHB) MLI.

The cascaded H-bridge multilevel inverter (CHB-MLI) is based on the series connection of the H-bridge inverters. It is an alternative topology with fewer switches when compared with other MLI topologies of the same voltage level. Each H-bridge can be used to generate three output voltage levels by a unipolar modulation technique. CHB-MLI has been used for renewable energy sources, especially PV modules, due to its separate Direct Current (DC) source feature. Cascaded H-bridge MLI features have proved to be an attractive solution for many applications, such as standalone systems [

5], volt ampere reactive (VAR) compensations, and grid-connected PV systems as presented in [

6,

7,

8,

9].

Generally, the cascaded H-bridge topologies have received more attention. The cascaded H-bridge inverter has a simple layout, extreme modularity, a simple construction, control, and no voltage balance problems, and compared with the other multilevel topologies, it requires the fewest components for generating the same voltage levels [

10,

11,

12]. However, if more levels are required to improve the current and voltage’s quality, the number of switches can be increased. Increasing the number of switches can lead to an increase in the cost, the conduction, and the switching losses, thus reducing the system efficiency. The reliability will also be reduced when the number of switches is increased, and the control system will be more complex.

Many other cascaded inverter topologies have been proposed to increase the number of voltage levels generated, which will improve the system’s performance and reduce cost [

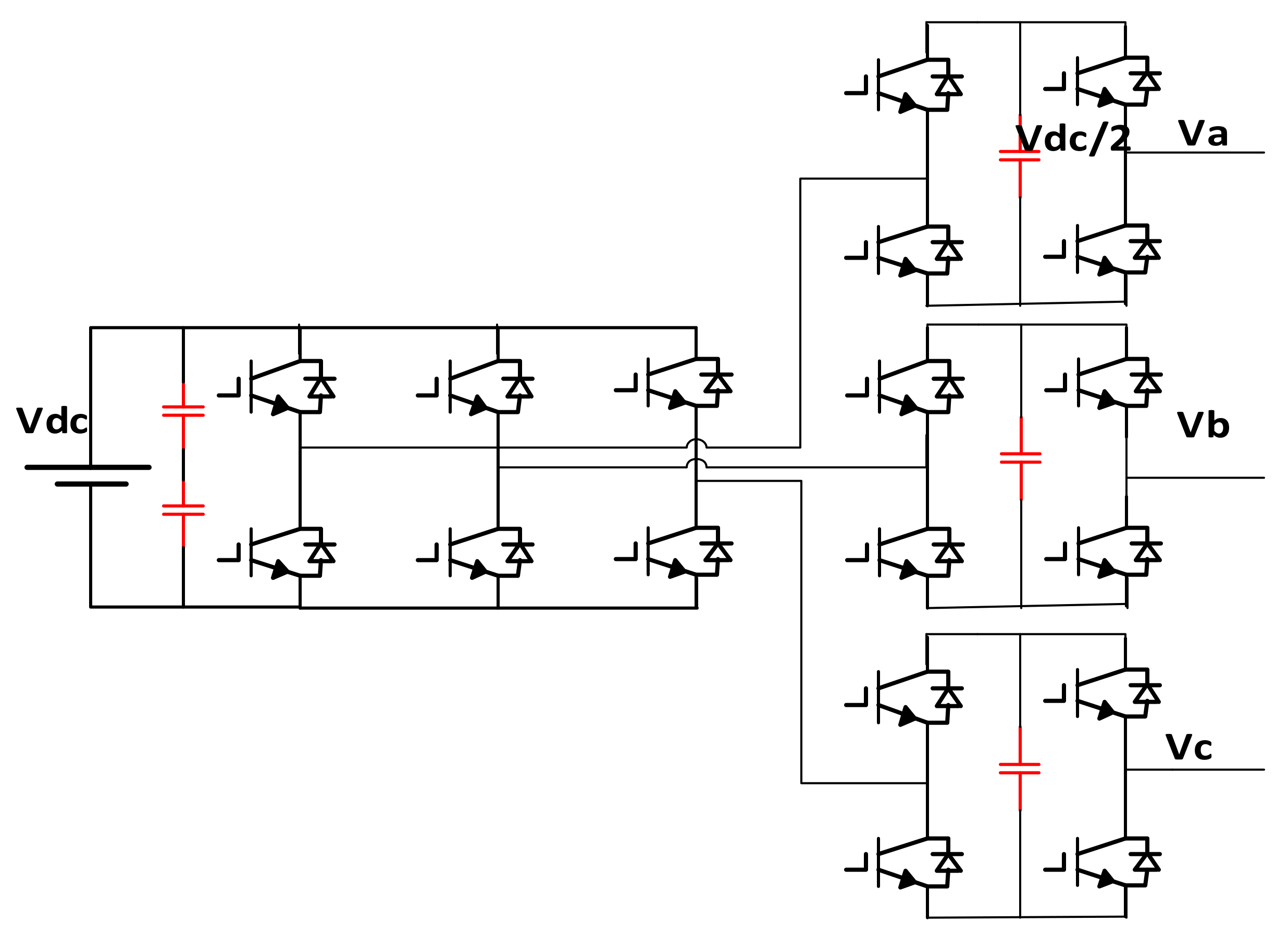

10]. Asymmetrical CHB-MLI topologies have been proposed to increase the number of levels by combining various ranges of voltage DC sources as shown in

Figure 1 [

13,

14,

15]. In these topologies, the number of levels increase, but the stresses on the switches are not equal. The stress on switches connected to the lower DC input voltage will be lower than that on switches connected to the higher DC input voltage. Unequal loss sharing among switches will cause varying temperatures for switches, and some switches may be burnt. In addition, unequal loss sharing means different voltage ratings will be used for switches, which results in a higher cost. On the other hand, unequal loss sharing requires switches with higher voltage ratings.

On the other hand, modified topologies have been proposed based on CHB to improve the output voltage quality [

16,

17], but the advantages of the CHB are lost, such as simplicity, simple construction, simple control, and modularity.

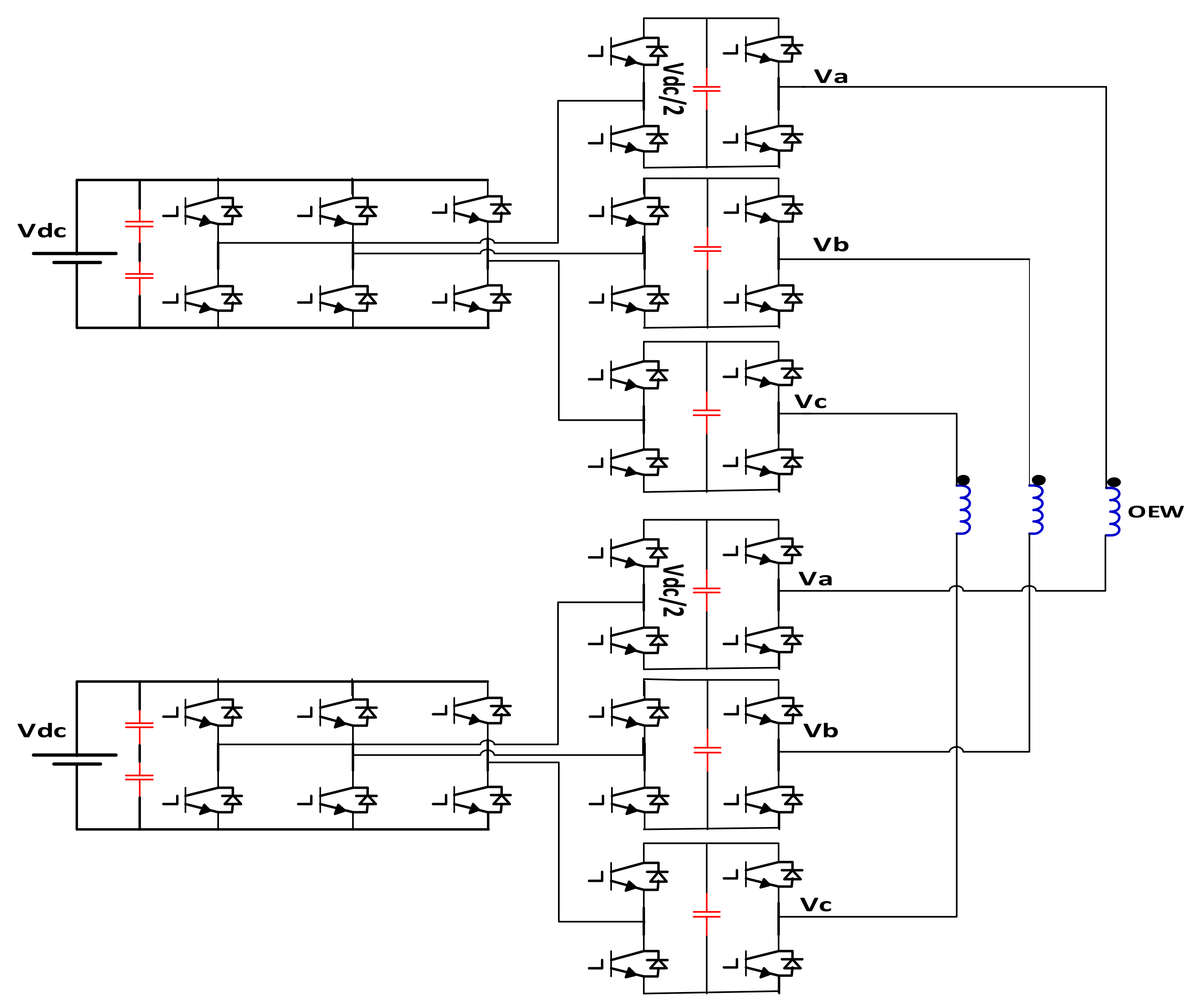

Hybrid multilevel inverter topologies were proposed based on three-leg two-level inverter with CHB [

18,

19,

20,

21,

22]. The hybrid multilevel inverter topology is shown in

Figure 2. The authors in [

18] proposed a five-level inverter topology based on two-level and floating capacitor H-bridge cells. The proposed inverter topology can be operated as a three-level inverter for the full modulation range, in case of any switch failure in the capacitor-fed H-bridge cell. This will increase the system’s reliability. The authors [

22] also proposed a nine-level inverter topology based on a conventional hybrid two-level voltage source inverter (VSI) with CHB-MLI using open-end winding (OEW) transformers as shown in

Figure 3. These topologies are not reliable, however, because they are based on a two-level three-leg inverter. The inverter system will be out of work if this two-level inverter malfunctions, and the power will not be supplied to the grid. In these topologies, the H-bridges are connected to floating capacitors whose voltages should be controlled carefully to be maintained at required asymmetrical values. This adds more complexity to the control algorithm.

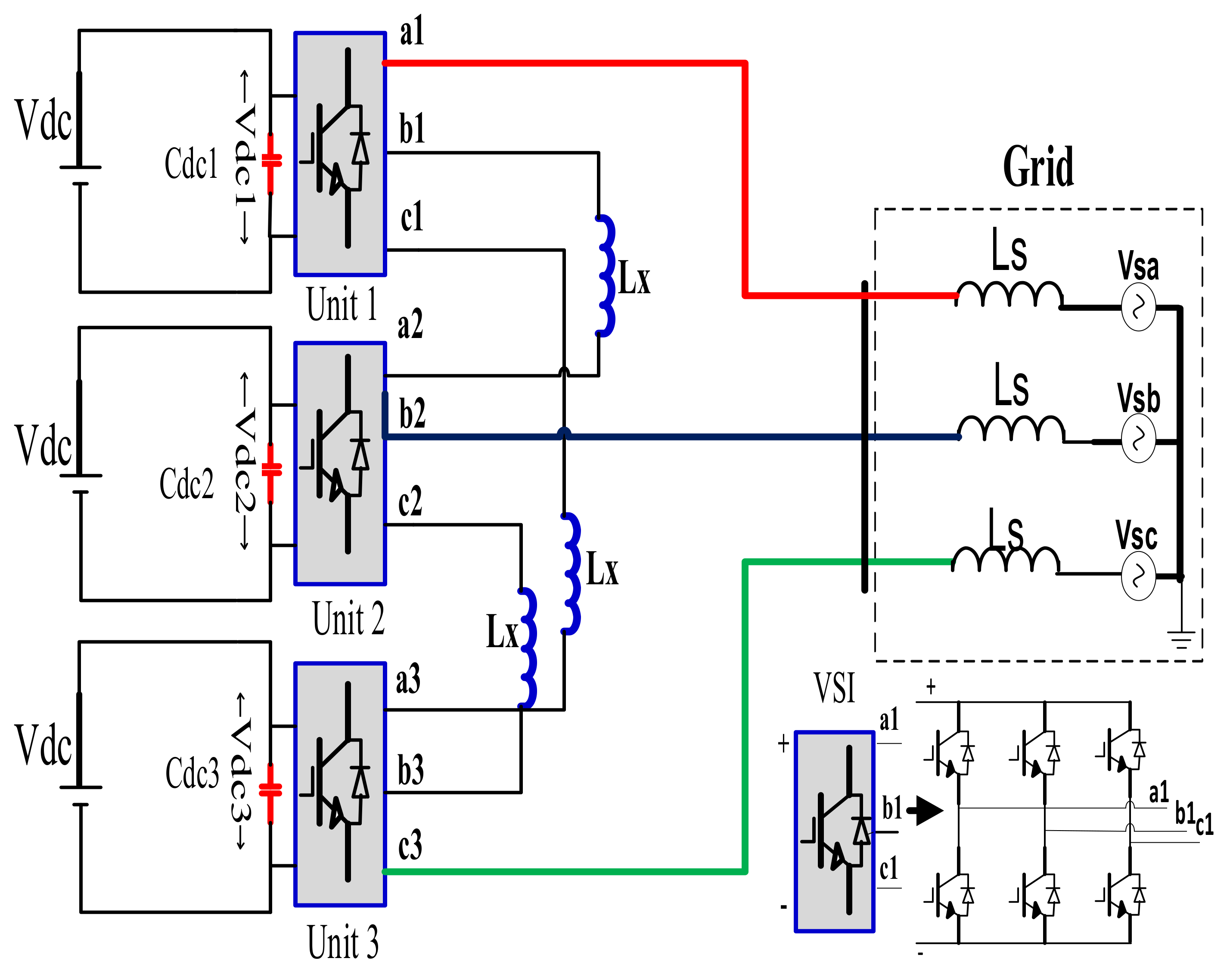

Another type of cascaded MLI topology is based on the conventional two-level voltage source inverter. It has been used in many motor-drive applications as shown in

Figure 4 [

23,

24]. This cascaded MLI can also be used for grid-connected renewable energy applications [

23,

24,

25]. The author in [

23] used this topology to connect the wind farm to the grid, whereas others [

25] used the three-phase cascaded VSI for grid-connected PV applications. However, the three-phase currents in each unit are not balanced, which means the current stresses on each leg are not equal. The authors in [

26] solved the problem of unbalanced three-phase currents in each unit by using inter-mediate transformers instead of inductors as shown in

Figure 5.

However, the inter-mediate transformers are bulky [

27]. On the other hand, in both topologies, the number of voltage levels will be limited due to the limitation in the number of cascaded VSI units.

In this paper, a proposed multilevel inverter configuration introduces a combination of the cascaded H-bridge multilevel inverter and the three-phase cascaded VSI. This combination will increase the number of voltage levels generated from the inverter while using fewer components than the conventional multilevel inverter topologies do for the same voltage levels. The proposed topology is built in the SIMULINK environment (2016a, MathWorks), is simulated under various loads, and is connected to the grid. In

Section 2, the proposed topology is described. In

Section 3, the analysis of the proposed topology is explained. To validate the good performance of the proposed topology, the simulation results are shown in

Section 4. In

Section 5, the experimental setup, and the experimental results are demonstrated.

2. Description of the Proposed Topology

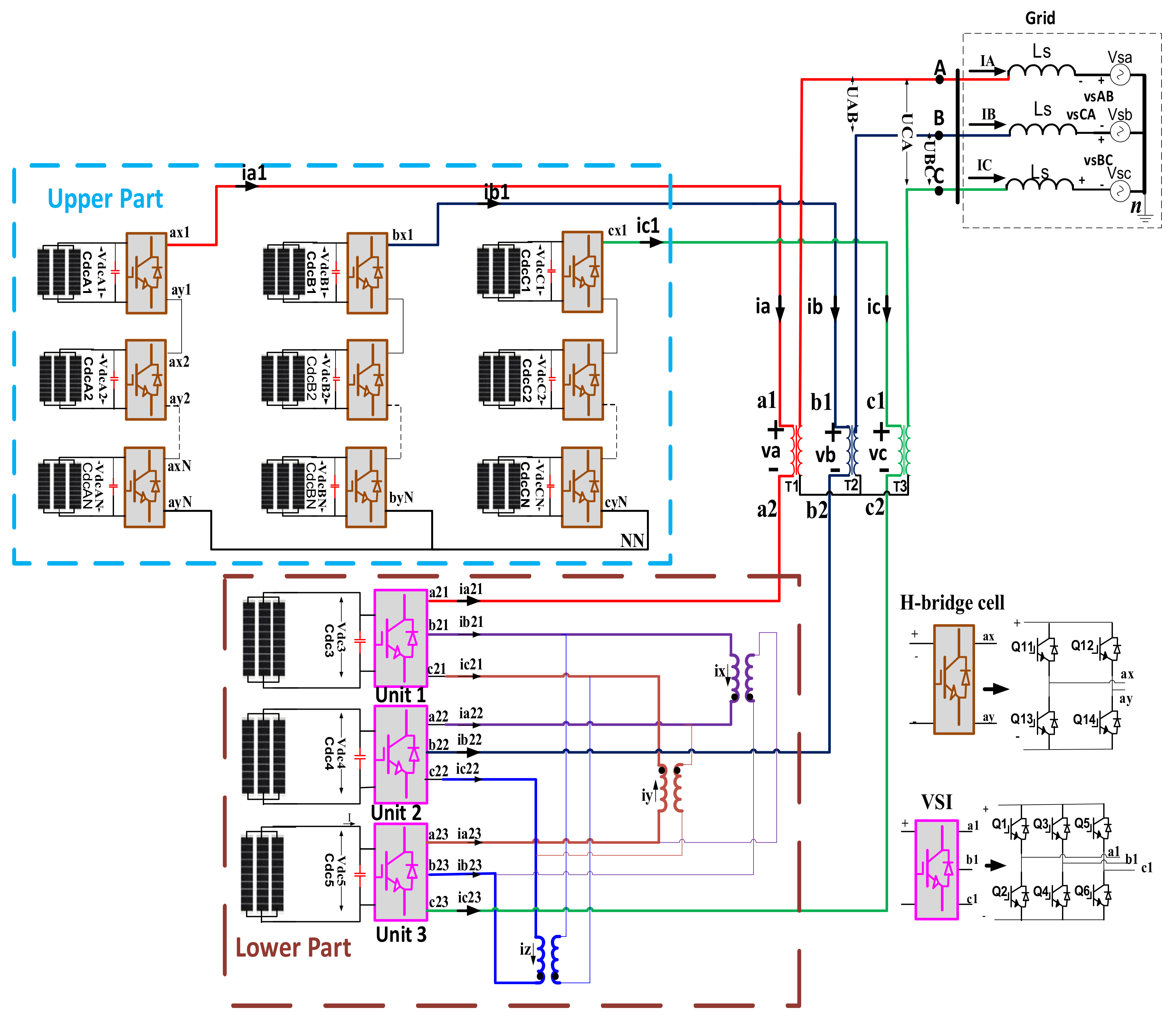

The present topology relates to a three-phase multilevel high-voltage/high-power converter, which is a hybrid configuration that conjoins two conventional multilevel configurations: a cascaded H-bridge MLI and a three-phase cascaded VSI (can also be called three-phase triple VSI (TVSI)).

Figure 6 reveals the proposed cascaded MLI topology. This new topology can be used for numerous grid-connected applications, such as grid-connected PV systems, power factor correction, and static VAR compensation.

The proposed topology can be used to generate any number of voltage levels using fewer components compared with the conventional multilevel inverter topologies. The proposed inverter topology consists of two parts, which are connected together with open-end winding transformers as shown in

Figure 6. To better describe the proposed inverter topology, it has been divided into two parts. The upper part is the cascaded H-bridge MLI, and the lower part is the three-phase triple VSI.

First: Description of the upper part: This part consists of three-phase systems. Each phase consists of N H-bridge cells. These cells are cascaded as shown in the upper part of

Figure 6 such that the

terminal of H-bridge cell 1 in phase a, for example, is connected to the

terminal of the next H-bridge cell. In addition, the

terminal is connected to the

terminal of the last H-bridge cell. The same idea is applied phases b and c. The terminals of

, and

of phases a, b, and c are connected together to one point,

NN.

Second: Description of lower part: The three-phase triple-voltage source inverter consists of three units. Each unit is a three-leg two-level inverter, and the three units are cascaded as shown in the lower part of

Figure 6. Each unit consists of three terminals:

,

where

k is the unit number. The three units are cascaded with one another by using coupled inductors as shown in the lower part of

Figure 6. The coupled inductors are used instead of inter-mediate transformers in the lower part.

Finally: The upper and lower parts are connected in such a way that phase a of the upper configuration is connected to phase a of the lower configuration via open-end winding. Terminal from the upper part is connected to terminal of open-end winding transformer , and terminal of unit 1 in the lower part is connected to terminal of open-end winding transformer . The same idea is applied for open-end winding transformers and . The secondary windings of transformers , and are then connected to the three-phase grid. Three single-phase line frequency transformers presented in the proposed topology are used to connect the upper three-phase cascaded H-bridge inverter with the lower three-phase triple voltage source inverter. The operation of the three single-phase transformers are based on the principles of the open-end transformer. The open-end winding transformer has gained advantages to the MLI topologies: (1) The voltage rating of the power devices is reduced by half; (2) the size of the capacitors is reduced; and (3) the DC bus magnitude that the PV modules provide can be reduced by half compared with if only one part (upper or lower) is used. This topology generates higher voltage levels by reducing the number of required switches compared with the conventional multilevel inverter topologies for the same voltage levels. The reduction in the switches leads to a reduction in complexity and dimensions of the converter. In addition, the topology helps reduce the total harmonic distortion (THD) of the voltages and currents. Another important advantage of the proposed inverter topology is that in case of failure in one part, the other part will work independently, and the power will still be available. In addition, if more levels are needed, the number of H-bridge cells in the upper part can be increased. The concept presented in this paper is validated by means of simulation and experimental results.

The advantages of the invention can be summarized as follows:

More levels can be obtained by using fewer switches compared with the conventional multilevel inverter topologies for the same voltage levels.

Voltage and quality of current can be improved.

A continuous power supply to the grid is assured in the case of failure one configuration. Therefore, the proposed topology is reliable.

The voltage stresses on switches are reduced:

Stresses on the upper switches:

where

V is the root-mean-square (RMS) of the line–line grid voltage, and

N is the number of cascaded H-bridge cells.

Stresses on the lower switches:

Equal Current stresses on switches. The current stress on all switches in the proposed topology is the RMS grid current .

4. Simulation Results

The proposed inverter topology shown in

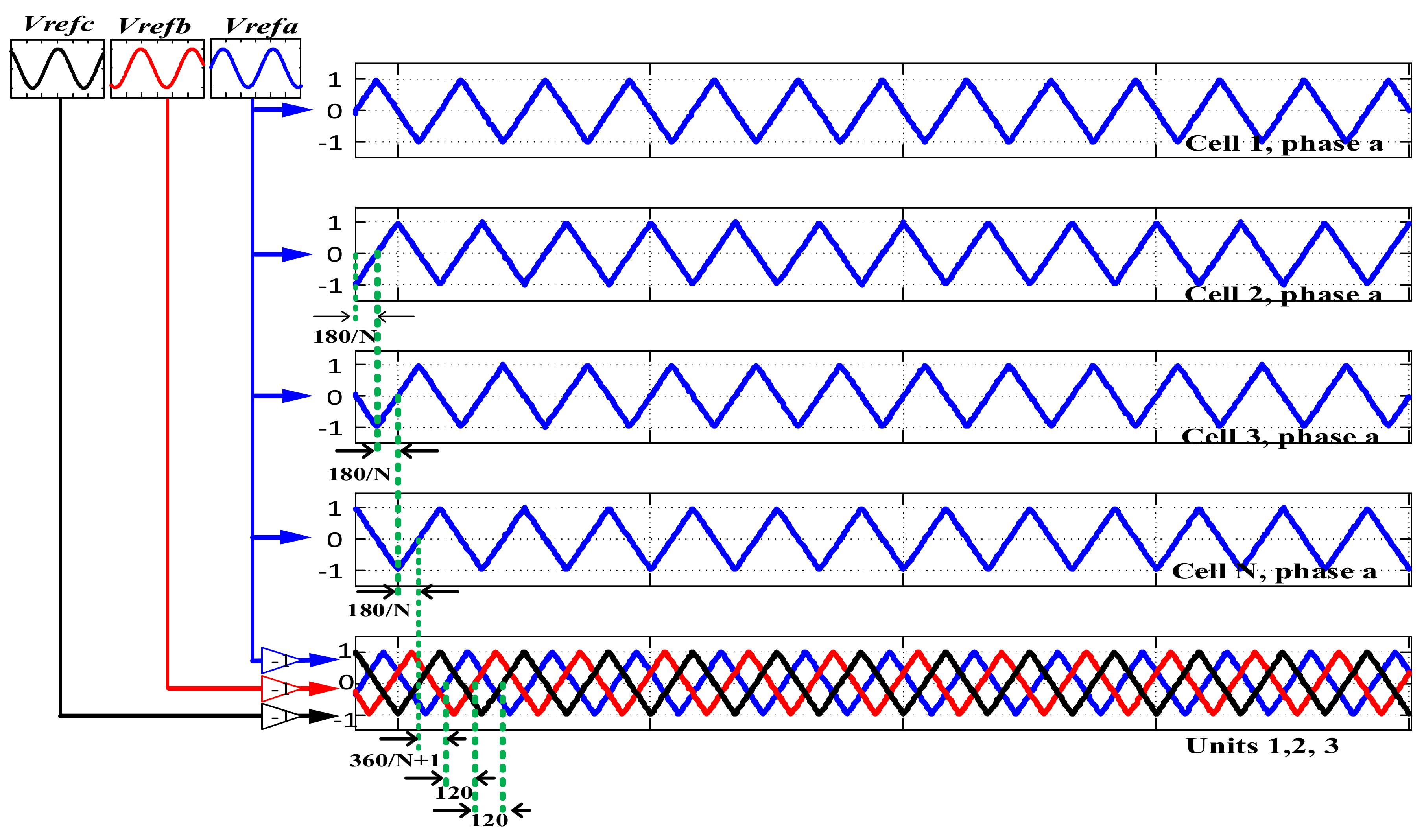

Figure 6 is built in SIMULINK, and the simulation is achieved using the MATLAB/SIMULINK environment (2016a, MathWorks). For simplicity, two cascaded H-bride cells are used in each phase in the upper part of the proposed topology. The magnitude of the DC voltage used for each cell in the upper and lower parts is 30 V. phase-shifted pulse-width modulation (PWM) technique (PSPWM) is used to generate the required pulses of the insulated-gate bipolar transistors (IGBTs). In this technique, the reference signals are used to generate switching pulses to drive the IGBTs of the proposed topology by comparing them with the generated triangular carrier waveforms as shown in

Figure 7. The reference signals are three-phase sine waveforms whose frequencies are 60 Hz. As shown

Figure 7, the phase-shift technique is used to generate the pulses to drive the IGBTs of the cascaded H-bridge part (upper part), as the triangular signal of the next H-bridge cell is shifted from the previous H-bridge by

, where

N is the number of H-bridge cells. Reference voltage signal

is compared with these phase-shifted triangular waveforms, and the resulting pulses are used to drive the IGBTs of the H-bridge cells of phase a.

In addition, reference voltage signals are compared with the phase-shifted triangular waveforms to drive the IGBTs of the H-bridge cells of phases b and c of the upper part respectively.

It should be noted that only the phase-shifted triangular waveforms used to drive the IGBTs of H-bridge cells of phase a (phase a in the upper part) are shown in this figure. In addition, to drive the IGBTs of the three-phase triple VSI (lower part) in the proposed topology, the reference voltage signals of

are compared with the phase-shifted triangular waveforms as shown in

Figure 7. The triangular signal used to generate the PWM pulses of unit 2 is shifted by (

T/3) from that of unit 1, and the triangular signal used to generate PWM pulses of unit 3 is shifted by (

T/3) from that of unit 2. It is noted that the generated triangular waveforms of the lower part are shifted from the triangular signal of H-bridge cell number

N in the upper part by (

T/(

N + 1)), where

N is the number of H-bridge cells in one phase in the upper part of the proposed inverter topology.

The performance of the proposed inverter is tested under variable loads: resistive load, resistive inductive loads connected in a series (RLs), resistive inductive loads connected in parallel (RLp), and a series resistive inductive capacitive (RLCs) load. The parameters used for simulation are shown in

Table 1. In addition, the modulation index is set 1.85, and the sampling time during simulation is 10 µs. The parameters of the transformers are set by the default values of the SIMULINK. The three-phase voltages

,

are measured across the two primary terminals of transformers

,

, and

respectively.

The instantaneous line-line voltages generated from the proposed topology is shown in

Figure 8. As shown in this figure, the total number of voltage levels is 15 level. On the other hand, the total number of voltage levels generated from the proposed topology per phase is 22 levels as revealed in

Figure 9.

To show the performance of the proposed inverter, the harmonic spectrum is measured under various load conditions. The harmonic spectrum of the generated voltage

is seen in

Figure 10. The total harmonic distortion (THD) of

is 10.29%. As depicted in

Figure 10, the first harmonic family appears at five times the fundamental frequency. The fifth, seventh, and 13th harmonic order exists with amplitudes approximately 3%, 2.5%, and 0.9% respectively.

5. Experimental Results

To validate good performance, the proposed topology has been built in the laboratory and experimentally tested under various loads. It is connected to the grid with an open-loop control. In the experimental setup, the PV modules represent the DC voltage sources. For simplicity, two cascaded H-bridge cells are used for each phase in the upper part of the proposed topology. For the three-phase inverter topology, nine PV modules are used since one PV module is connected to each H-bridge cell in the upper part, and one PV module is connected to each unit in the lower part.

The parameters of the PV modules are shown in

Table 1. Data acquisition and the control system are implemented using a DS1202 MicroLabBox system (dSPACE Company, Paderborn, Germany) produced by dSPACE. The required switching pulses are generated inside a SIMUNLINK environment and are sent to the IGBTs via the DS1202 board. During hardware implementation, the phase-shifted PWM technique is used.

The hardware setup of the proposed topology is depicted in

Figure 11. Three single-phase transformers are used for open-end connection. In addition, three coupled inductors, model 810.1201, produced by the Toroid Company (Salisbury, MD, USA), are used in the lower part of the proposed configuration.

The parameter in the experiment is illustrated in

Table 1. The inverter topology is practically tested under the following conditions:

5.1. Various Loads

5.1.1. Resistive load

A three-phase resistive bank is connected to the output terminals of the proposed topology. The three-phase voltages

,

, and

are generated across the primary sides of the transformers

,

, and

, respectively, taken from oscilloscope, is illustrated in

Figure 12a. The THD of the

is 8.41% and its harmonic spectrum, taken from oscilloscope, is depicted in

Figure 12b.

In addition, the three-phase load currents measured via the Hall-effect current sensor, model LTS 25-NP (LEM Company, Milwaukee, WI, USA), are shown in

Figure 12c.

As mentioned in the analysis, the three-phase currents of each unit in the lower configuration are symmetrical and balanced, and they equal the three-phase line currents. Therefore, the current stress on each IGBT in the lower configuration equals the current stress on each IGBT in the upper part. The three-phase currents of unit 1 in the lower configuration are displayed in

Figure 12d. The circulating currents inside the lower configurations is low because the magnetization inductances of the coupled inductors are high. The circulating current inside the lower configuration is low and can be seen in

Figure 12e.

5.1.2. Series Resistive Inductive Capacitive Load

The proposed topology is tested under three-phase RLC series load. The three-phase voltages

,

, and

are generated across the primary sides of the transformers

,

, and

, respectively, taken from oscilloscope, is depicted in

Figure 13a. The THD of the

is 8.53% and its harmonic spectrum, taken from oscilloscope, is depicted in

Figure 13b. In addition, the three-phase load currents are revealed in

Figure 13c.

The total harmonic distortion (THD) of

under all loads described above is practically measured by changing the modulation index (

) and validating the simulation results. The variations of the THD of

with changing

under various loads is seen in

Figure 14. As shown in these figures, the THD is high when

is less than 1, and it decreases with increasing

. The minimum THD occurs at

between 1.5 and 1.85. To reveal the effectiveness and accuracy of the proposed inverter topology, the same conditions of the experiment are applied to the SIMULINK model to validate the practical results by the simulation results. The practical results are validated via the simulation results by changing the modulation index as shown in

Figure 14.

Figure 14a shows the practical variation of the THD of

and the validation via simulation under resistive load. On the other hand, the practical variations of the THD of

under series resistive inductive loads, and their validation via simulation results can be seen in

Figure 14b.

Figure 14c reveals the changing in the THD of the

with changing

under parallel resistive inductive load practically, and this is validated via simulation results. The variations of the THD of the

under series resistive inductive capacitive loads are displayed in

Figure 14d and are validated via the simulation results as shown in the same graph.

The experimental harmonic spectrum of the voltage

under all load variations described above is depicted in

Figure 15. As illustrated in this figure, the higher magnitude of harmonics exists at five times the switching frequency with an amplitude of approximately 4.5%. The magnitude of the harmonic contents higher than fifth becomes lower.

5.2. Grid-Connected Condition

In this experiment, the proposed topology is directly connected to the grid via an interface inductor. The value of the interface inductor is 5 mH. The PV modules represent the DC voltage sources in this experiment. The Chroma grid simulator, model 61830, represents the grid. The three-phase voltages of the grid are measured using three voltage sensors, model LV 25-P, and are used to extract the angular frequency (

) to be used in the phase-locked loop (PLL). The modulation index is 1.5 in this test condition. In addition, the PSPWM technique displayed in

Figure 7 is used to generate the required pulses to drive the IGBTs of the inverter. The generated three-phase voltages

,

, and

taken from oscilloscope, can be seen in

Figure 16a. The THD of the generated voltage

is 6.93% as revealed in the harmonic spectrum of the

in

Figure 16b. As shown in this figure, the highest magnitude is only 2.8% of the fifth harmonic.

Conversely, the proposed inverter topology’s performance is tested by changing the modulation index and measuring the THD of the

as shown in

Figure 17. By increasing the modulation index, the THD of the voltage-generated

is decreased. The minimum THD occurs between modulation indices 1.5 and 1.85 as indicated in the figure. In addition, the harmonic spectrum of

is plotted in

Figure 18. The highest harmonic contents occur at five times the fundamental frequency. The minimum harmonic magnitude occurs at a modulation index of 1.5.