Hardware in the Loop Real-time Simulation for the Associated Discrete Circuit Modeling Optimization Method of Power Converters

Abstract

:1. Introduction

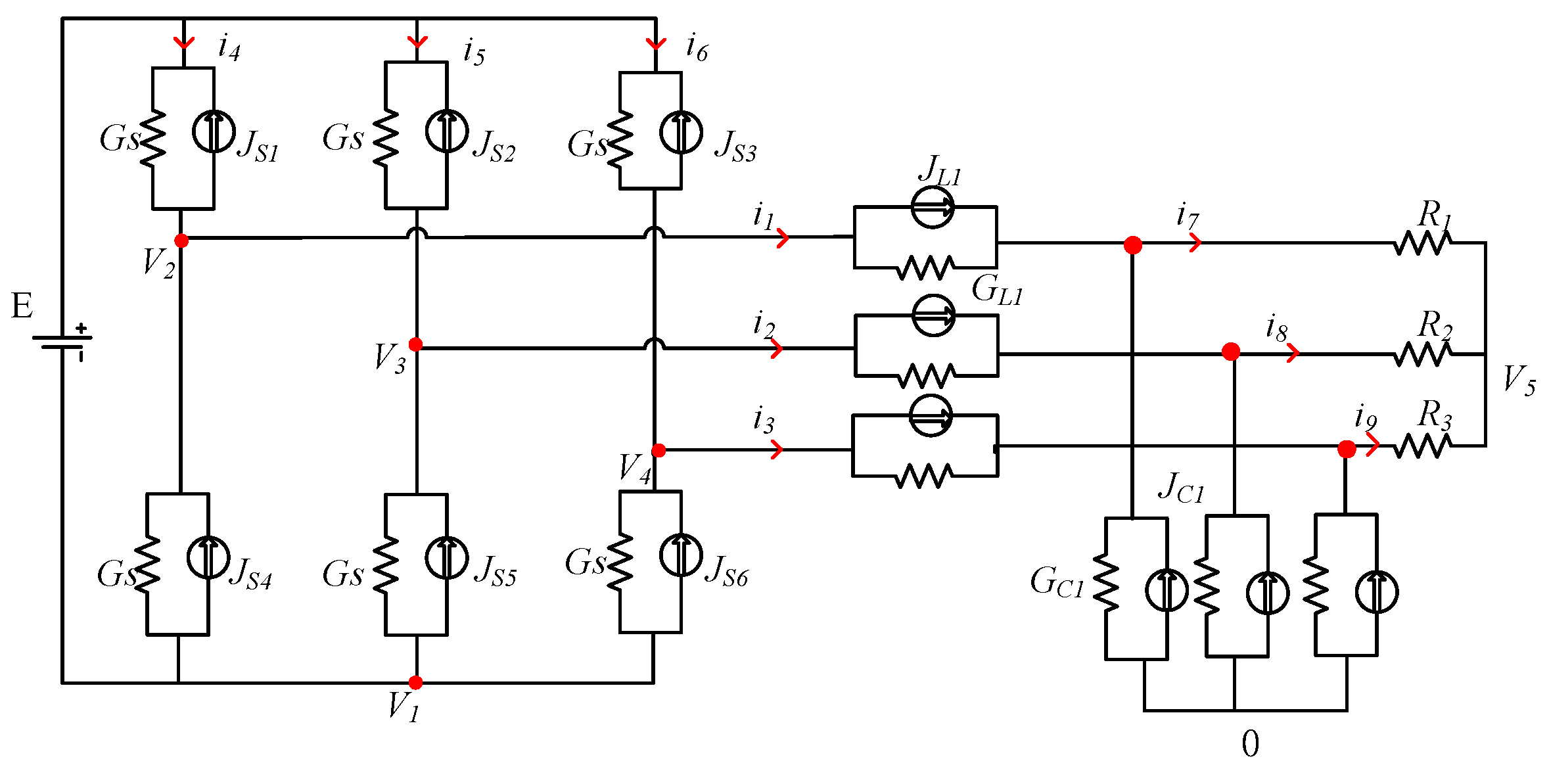

2. Associated Discrete Circuit Modeling Optimization Method

2.1. Associated Discrete Circuit Modeling Method

2.2. The Switch Admittance Parameter Gs Value for Minimum Switching Loss

3. Simulation Verification

4. FPGA Implementation

4.1. FPGA Resource Optimization Method

4.2. Simulation Verification

4.3. Vivado High-Level Synthesis

5. Hardware in the Loop Simulation and Experiment

6. Discussion

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhang, B.; Hu, R.; Tu, S.; Zhang, J.; Jin, X.; Guan, Y.; Zhu, J. Modeling of Power System Simulation Based on FRTDS. Energies 2018, 11, 2749. [Google Scholar] [CrossRef]

- Leng, F.; Mao, C.; Wang, D.; An, R.; Zhang, Y.; Zhao, Y.; Cai, L.; Tian, J. Applications of Digital-Physical Hybrid Real-Time Simulation Platform in Power Systems. Energies 2018, 11, 2682. [Google Scholar] [CrossRef]

- Matar, M.; Iravani, R. FPGA Implementation of the Power Electronic Converter Model for Real-Time Simulation of Electromagnetic Transients. IEEE Trans. Power Deliv. 2010, 25, 852–860. [Google Scholar] [CrossRef]

- Zhang, B.; Wang, Y.; Tu, S.; Jin, Z. FPGA-Based Real-Time Digital Solver for Electro-Mechanical Transient Simulation. Energies 2018, 11, 2650. [Google Scholar] [CrossRef]

- Li, J.; Li, X.; Du, L.; Cao, M.; Qian, G. An Intelligent Sensor for the Ultra-High-Frequency Partial Discharge Online Monitoring of Power Transformers. Energies 2016, 9, 383. [Google Scholar] [CrossRef]

- Zhang, B.; Wu, Y.; Jin, Z.; Wang, Y. A Real-Time Digital Solver for Smart Substation Based on Orders. Energies 2017, 10, 1795. [Google Scholar] [CrossRef]

- Zhang, B.; Nie, S.; Jin, Z. Electromagnetic Transient-Transient Stability Analysis Hybrid Real-Time Simulation Method of Variable Area of Interest. Energies 2018, 11, 2620. [Google Scholar] [CrossRef]

- Stifter, M.; Cordova, J.; Kazmi, J.; Arghandeh, R. Real-Time Simulation and Hardware-in-the-Loop Testbed for Distribution Synchrophasor Applications. Energies 2018, 11, 876. [Google Scholar] [CrossRef]

- Benhalima, S.; Miloud, R.; Chandra, A. Real-Time Implementation of Robust Control Strategies Based on Sliding Mode Control for Standalone Microgrids Supplying Non-Linear Loads. Energies 2018, 11, 2590. [Google Scholar] [CrossRef]

- Garcia, J.; Garcia, P.; Capponi, F.G.; Donato, G.D. Analysis, Modeling, and Control of Half-Bridge Current-Source Converter for Energy Management of Supercapacitor Modules in Traction Applications. Energies 2018, 11, 2239. [Google Scholar] [CrossRef]

- Priyadarshi, N.; Padmanaban, S.; Lonel, D.M.; Mihet-Popa, L.; Azam, F. Hybrid PV-Wind, Micro-Grid Development Using Quasi-Z-Source Inverter Modeling and Control—Experimental Investigation. Energies 2018, 11, 2277. [Google Scholar]

- Sudha, S.A.; Chandrasekaran, A.; Rajagopalan, V. New approach to switch modelling in the analysis of power electronic systems. IEE Proc. B Electr. Power Appl. 1993, 140, 115–123. [Google Scholar] [CrossRef]

- Wedepohl, L.M.; Jackson, L. Modified nodal analysis: An essential addition to electrical circuit theory and analysis. Eng. Sci. Educ. J. 2002, 11, 84–92. [Google Scholar] [CrossRef]

- Blij, N.H.V.D.; Ramirez-Elizondo, L.M.; Spaan, M.; Bauer, P. A State-Space Approach to Modelling DC Distribution Systems. IEEE Trans. Power Syst. 2018, 33, 943–950. [Google Scholar] [CrossRef] [Green Version]

- Kiffe, A.; Geng, S.; Schulte, T. Automated generation of a FPGA-based oversampling model of power electronic circuits. In Proceedings of the 15th International Power Electronics and Motion Control Conference (EPE/PEMC), Novi Sad, Serbia, 4–6 September 2012. [Google Scholar]

- Hui, S.Y.R.; Christopoulos, C. A discrete approach to the modeling of power electronic switching networks. IEEE Trans. Power Electron. 1990, 5, 398–403. [Google Scholar] [CrossRef]

- Dufour, C.; Cense, S.; Ould-Bachir, T.; Gregoire, L. General-purpose reconfigurable low-latency electric circuit and motor drive solver on FPGA. In Proceedings of the 38th Annual Conference on IEEE Industrial Electronics Society (IECON), Montréal, QC, Canada, 25–28 October 2012; pp. 3073–3081. [Google Scholar]

- Maguire, T.; Giesbrecht, J. Small time-step (< 2usec) VSC model for the real time digital simulator. In Proceedings of the International Conference on Power Systems Transients (IPST’05), Montreal, QC, Canada, 20–23 June 2005. [Google Scholar]

- Matar, M.; Iravani, R. An FPGA-based real-time digital simulator for power electronic systems. In Proceedings of the International Conference on Power Systems Transients (IPST’07), Lyon, France, 4–7 June 2007. [Google Scholar]

- Miceli, R.; Schettino, G.; Viola, F. A Novel Computational Approach for Harmonic Mitigation in PV Systems with Single-Phase Five-Level CHBMI. Energies 2018, 11, 2100. [Google Scholar] [CrossRef]

- Nicolas-Apruzzese, J.; Lupon, E.; Busquets-Monge, S.; Conesa, A.; Bordonau, J.; García-Rojas, G. FPGA-Based Controller for a Permanent-Magnet Synchronous Motor Drive Based on a Four-Level Active-Clamped DC-AC Converter. Energies 2018, 11, 2639. [Google Scholar] [CrossRef]

- Baptista, D.; Mostafa, S.S.; Pereira, L.; Sousa, L.; Morgado-Dias, F. Implementation Strategy of Convolution Neural Networks on Field Programmable Gate Arrays for Appliance Classification Using the Voltage and Current (V-I) Trajectory. Energies 2018, 11, 2460. [Google Scholar] [CrossRef]

- Ricco, M.; Mathe, L.; Monmasson, E.; Teodorescu, R. FPGA-Based Implementation of MMC Control Based on Sorting Networks. Energies 2018, 11, 2394. [Google Scholar] [CrossRef]

- Nguyen-Van, T.; Abe, R.; Tanaka, K. Digital Adaptive Hysteresis Current Control for Multi-Functional Inverters. Energies 2018, 11, 2422. [Google Scholar] [CrossRef]

- Schlecker, W.; Beuschel, C.; Pfleiderer, H.J. Analytical consideration of the quantization error in basic arithmetic operations of digital signal processing. Adv. Radio Sci. 2005, 3, 343–347. [Google Scholar] [CrossRef]

- Schlecker, W. Quantization Effects in Digital Signal Processing; The University of Ulm: Ulm, Germany, 2006. [Google Scholar]

- Li, Y.; Zhu, T.; Cao, Z. Analysis of Influence of Time Step on Numerical Simulation of Finite Volume Method. Comput. Simul. 2009, 26, 117–120. [Google Scholar]

- Kim, Y.M.; Shin, D.G.; Kim, C.G. Optimization of Design Pressure Ratio of Positive Displacement Expander for Vehicle Engine Waste Heat Recovery. Energies 2014, 7, 6105–6117. [Google Scholar] [CrossRef] [Green Version]

- Dang, H.S.; Wang, L.; Wang, X.Q. Development and application of FPGA based on Vivado HLS. J. Shaanxi Univ. Sci. Technol. 2015, 33, 341–361. [Google Scholar]

- Lei, J.; Li, Y.; Zhao, D.; Xie, J.; Chang, C.; Wu, L.; Li, X.; Zhang, J.; Li, W. A Deep Pipelined Implementation of Hyperspectral Target Detection Algorithm on FPGA Using HLS. Remote Sens. 2018, 10, 516. [Google Scholar] [CrossRef]

- Huang, H.; Zhai, L.; Wang, Z. A Power Coupling System for Electric Tracked Vehicles during High-Speed Steering with Optimization-Based Torque Distribution Control. Energies 2018, 11, 1538. [Google Scholar] [CrossRef]

- Guillo-Sansano, E.; Syed, M.H.; Roscoe, A.J.; Burt, G.M. Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study. Energies 2018, 11, 1087. [Google Scholar] [CrossRef]

- Rodič, M.; Milanovič, M.; Truntič, M. Digital Control of an Interleaving Operated Buck-Boost Synchronous Converter Used in a Low-Cost Testing System for an Automotive Powertrain. Energies 2018, 11, 2290. [Google Scholar] [CrossRef]

| Parameters | Unit | Value |

|---|---|---|

| DC voltage | V | 300 |

| Switching frequency | kHz | 10 |

| Fundamental modulation frequency | Hz | 50 |

| Inductance L | H | 1.2 × |

| Capacitance C | F | 2 × |

| Load resistance R | Ω | 4 |

| Admittance parameter Gs | mH | 0.0872 |

| Duty circle | - | 0.9 |

| FPGA Resource | 25 | 28 | 31 | Available |

|---|---|---|---|---|

| Slice | 4910 | 5560 | 5821 | 50,950 |

| LUTs | 13,439 | 16,207 | 16,653 | 203,800 |

| DSPs | 337 | 468 | 474 | 840 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Guo, X.; Yuan, J.; Tang, Y.; You, X. Hardware in the Loop Real-time Simulation for the Associated Discrete Circuit Modeling Optimization Method of Power Converters. Energies 2018, 11, 3237. https://doi.org/10.3390/en11113237

Guo X, Yuan J, Tang Y, You X. Hardware in the Loop Real-time Simulation for the Associated Discrete Circuit Modeling Optimization Method of Power Converters. Energies. 2018; 11(11):3237. https://doi.org/10.3390/en11113237

Chicago/Turabian StyleGuo, Xizheng, Jiaqi Yuan, Yiguo Tang, and Xiaojie You. 2018. "Hardware in the Loop Real-time Simulation for the Associated Discrete Circuit Modeling Optimization Method of Power Converters" Energies 11, no. 11: 3237. https://doi.org/10.3390/en11113237