Novel Three-Phase Nine-Level Inverter and Its Control Strategies

Abstract

1. Introduction

2. Methods

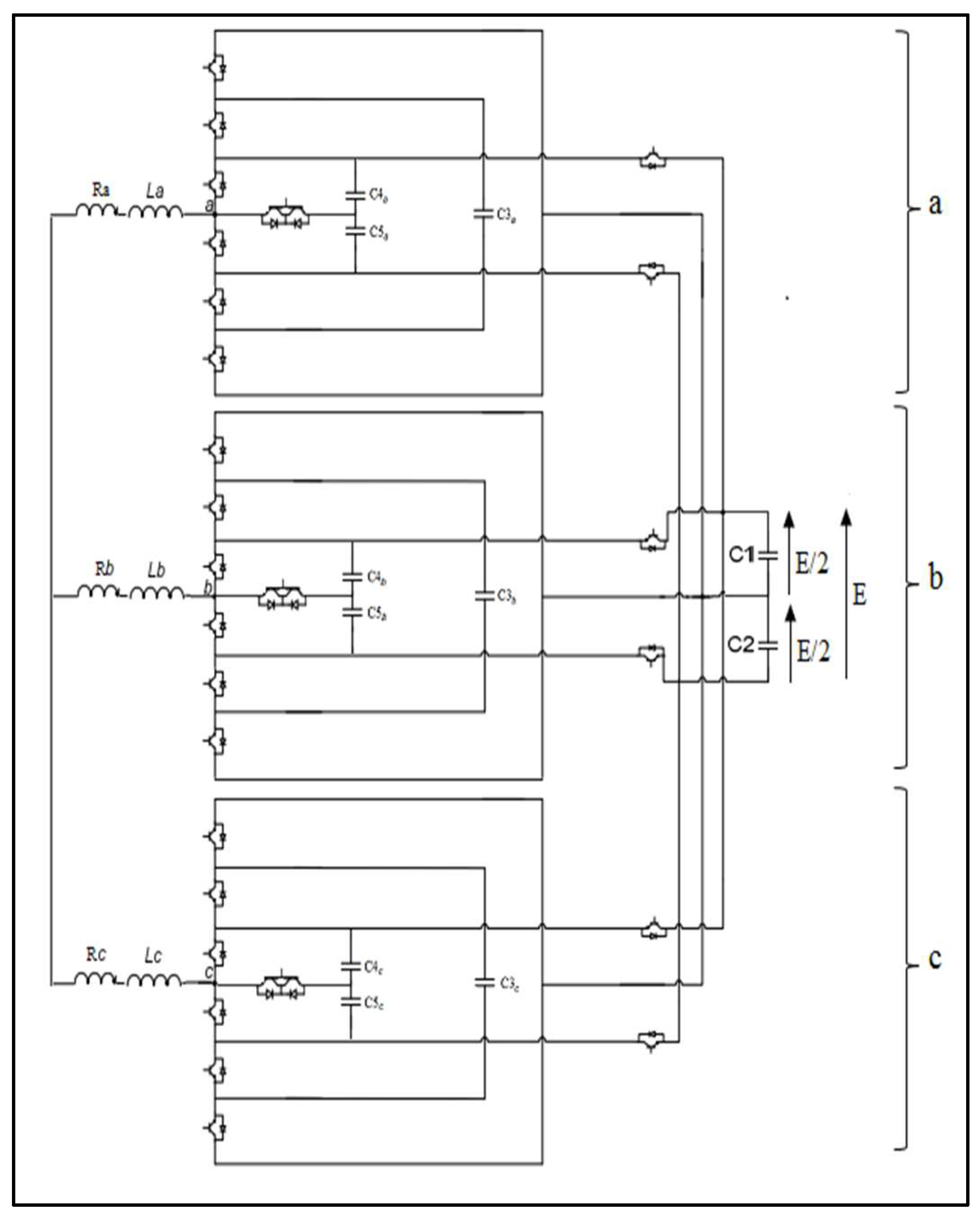

2.1. Presentation the Proposed Three-Phase Inverter Topology and Switching States

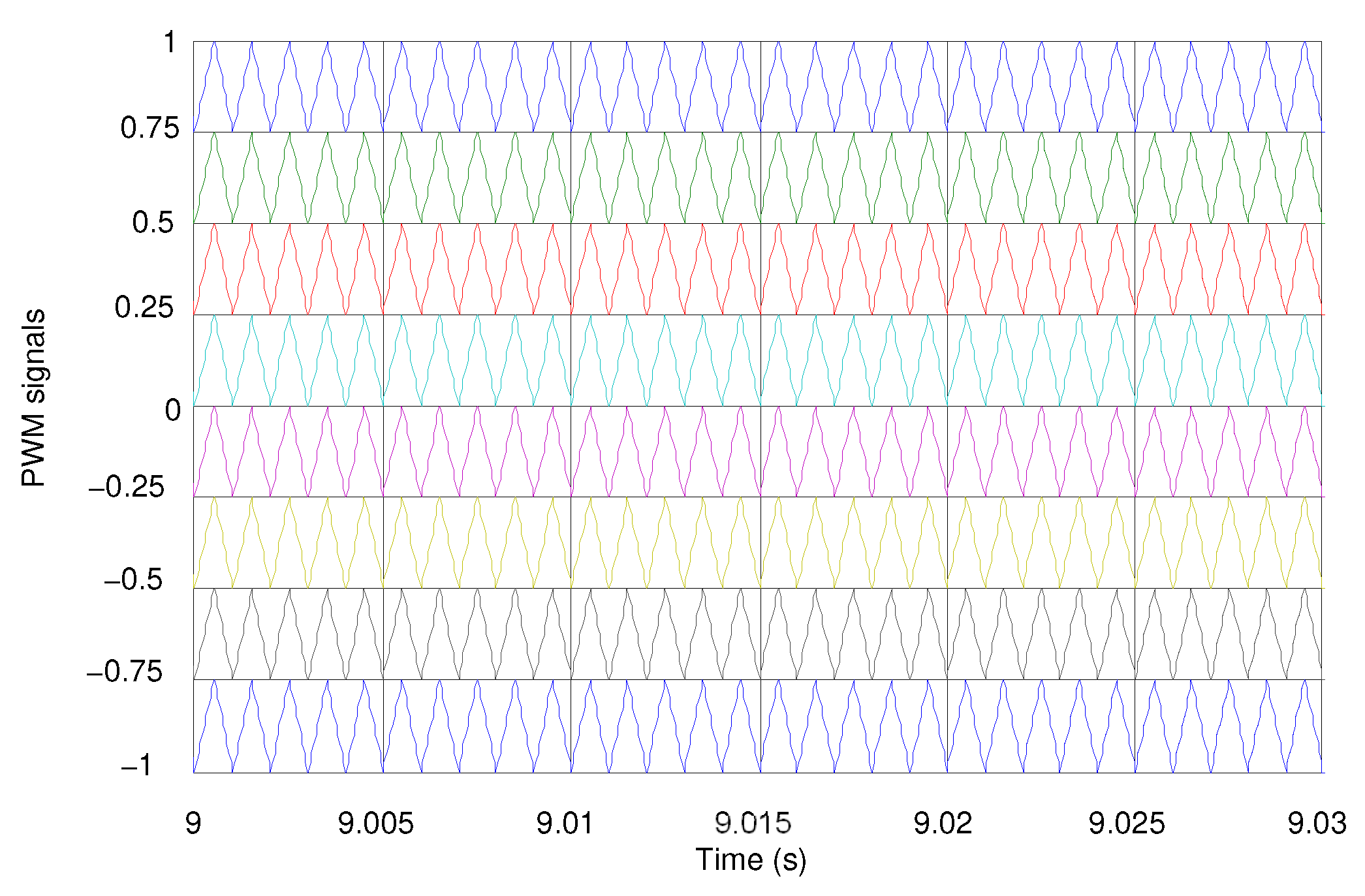

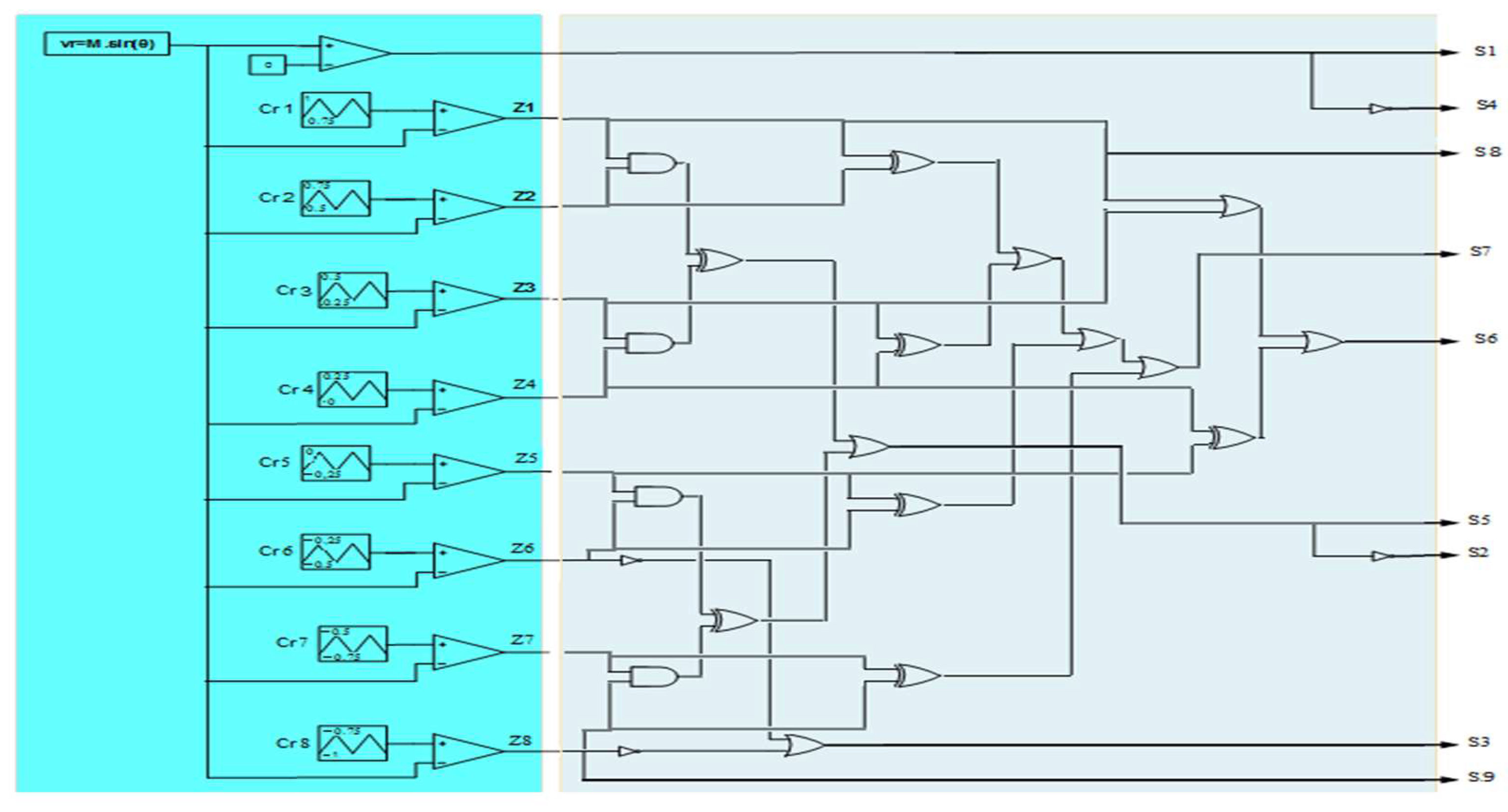

2.2. Proposed Nine-Level Inverter Using PWM Technique

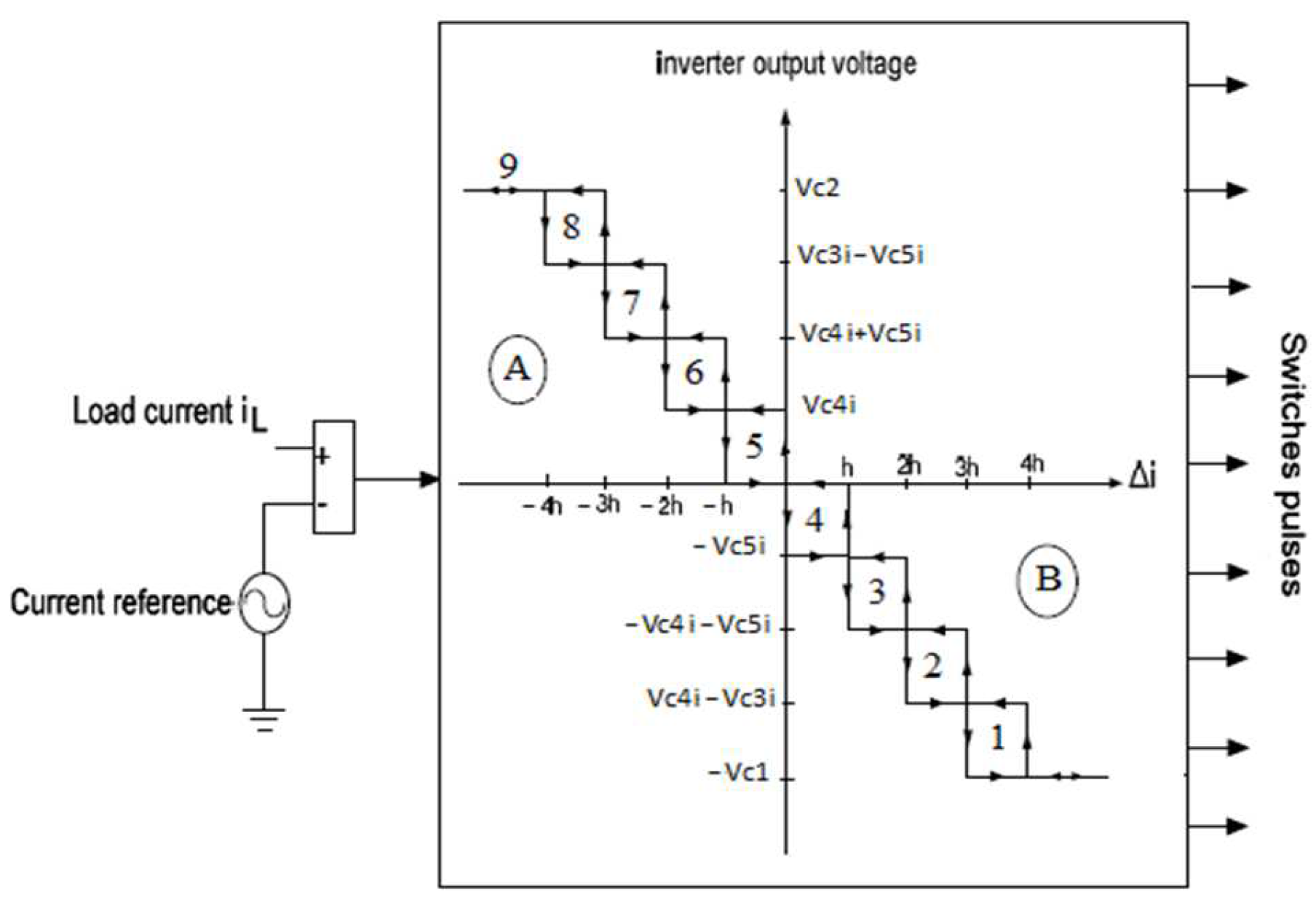

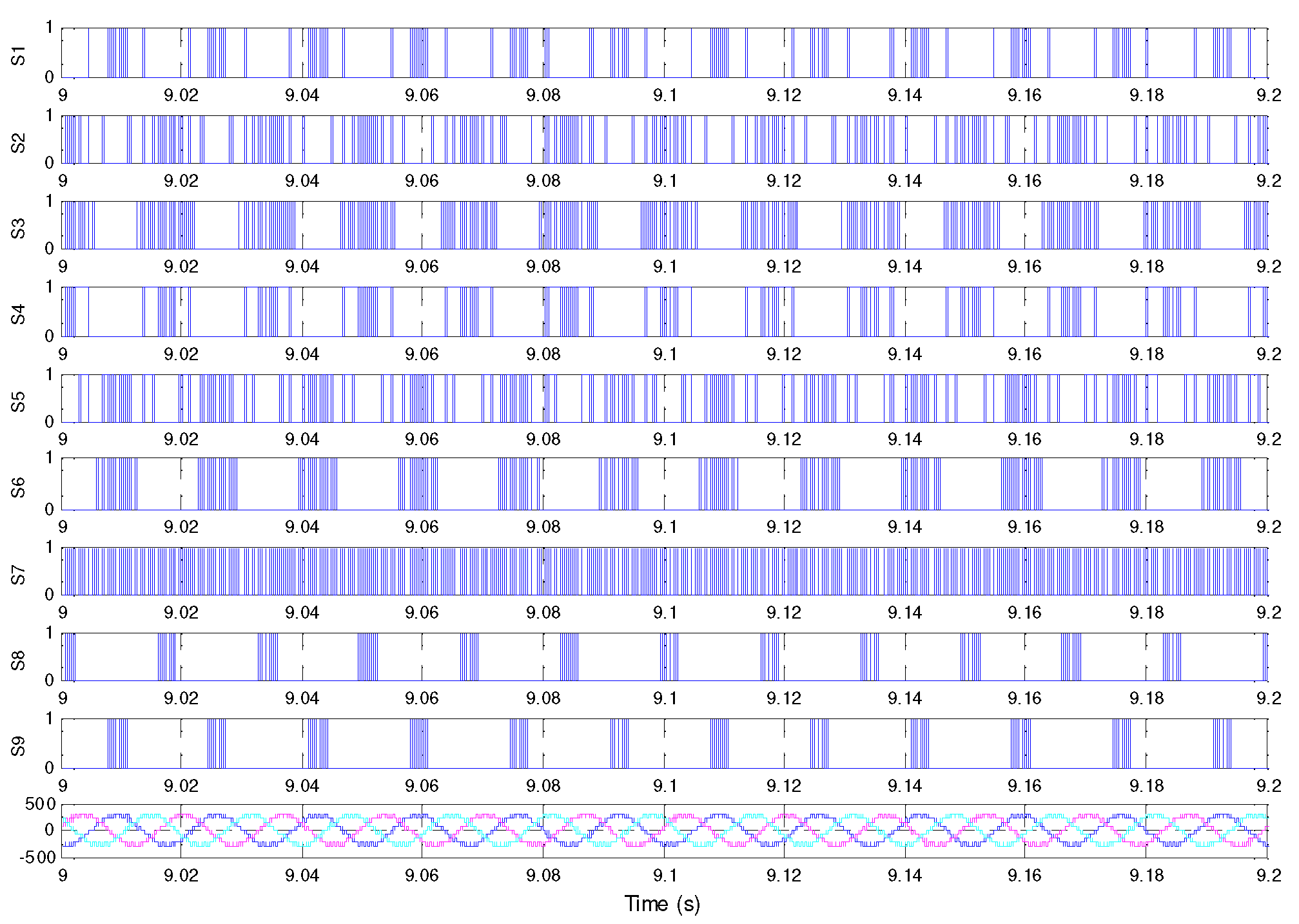

2.3. Proposed Nine-Level Inverter Using Hysteresis Control

3. Results

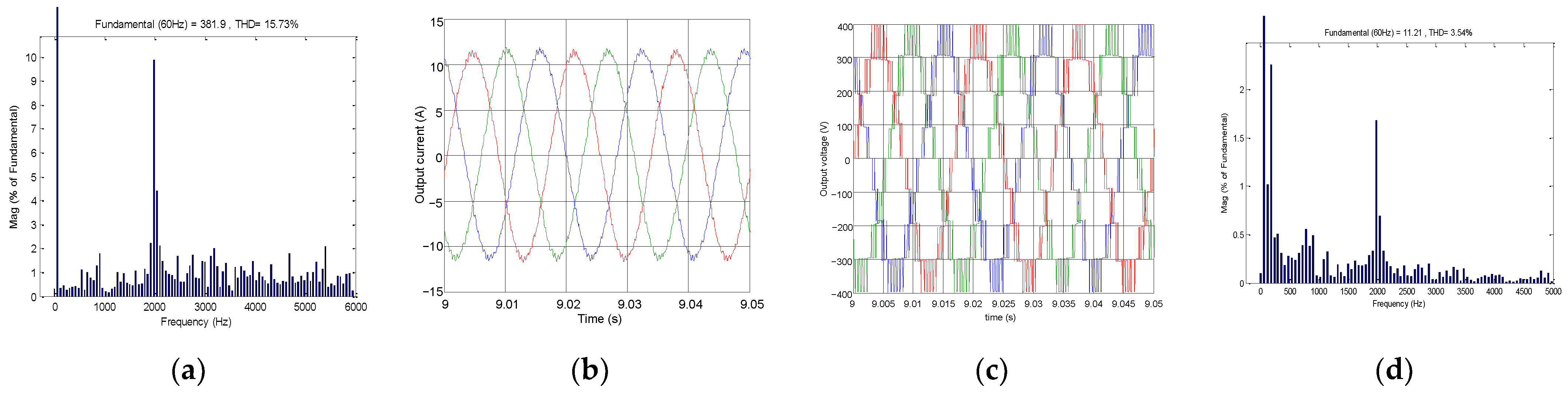

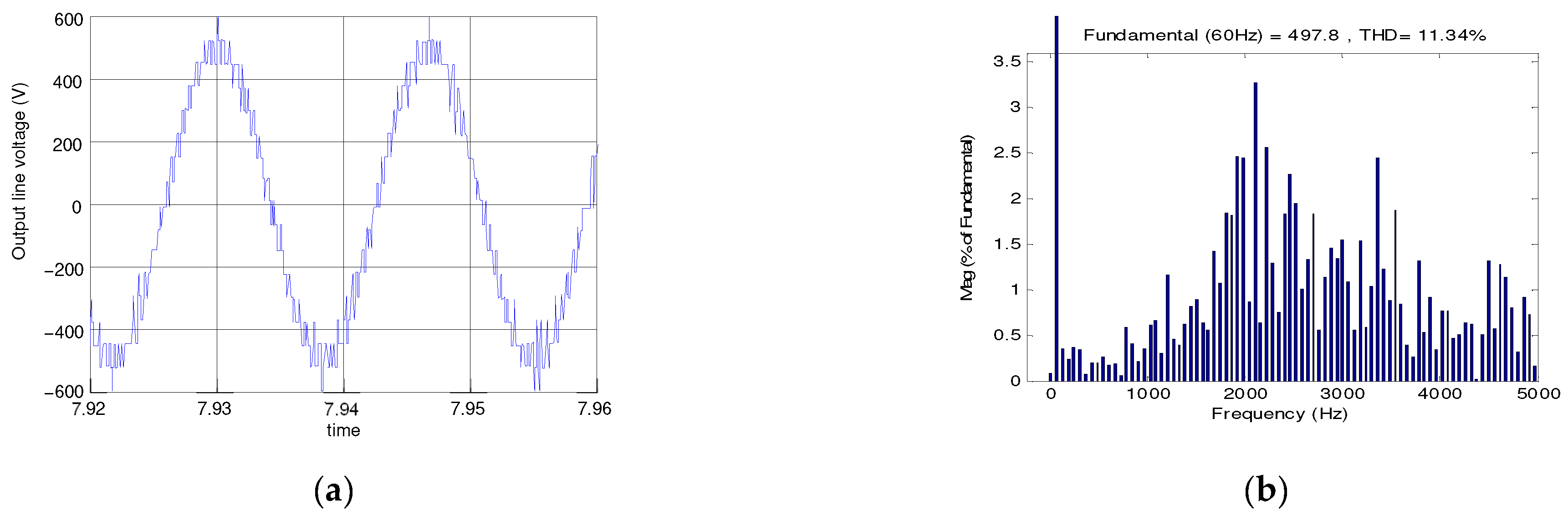

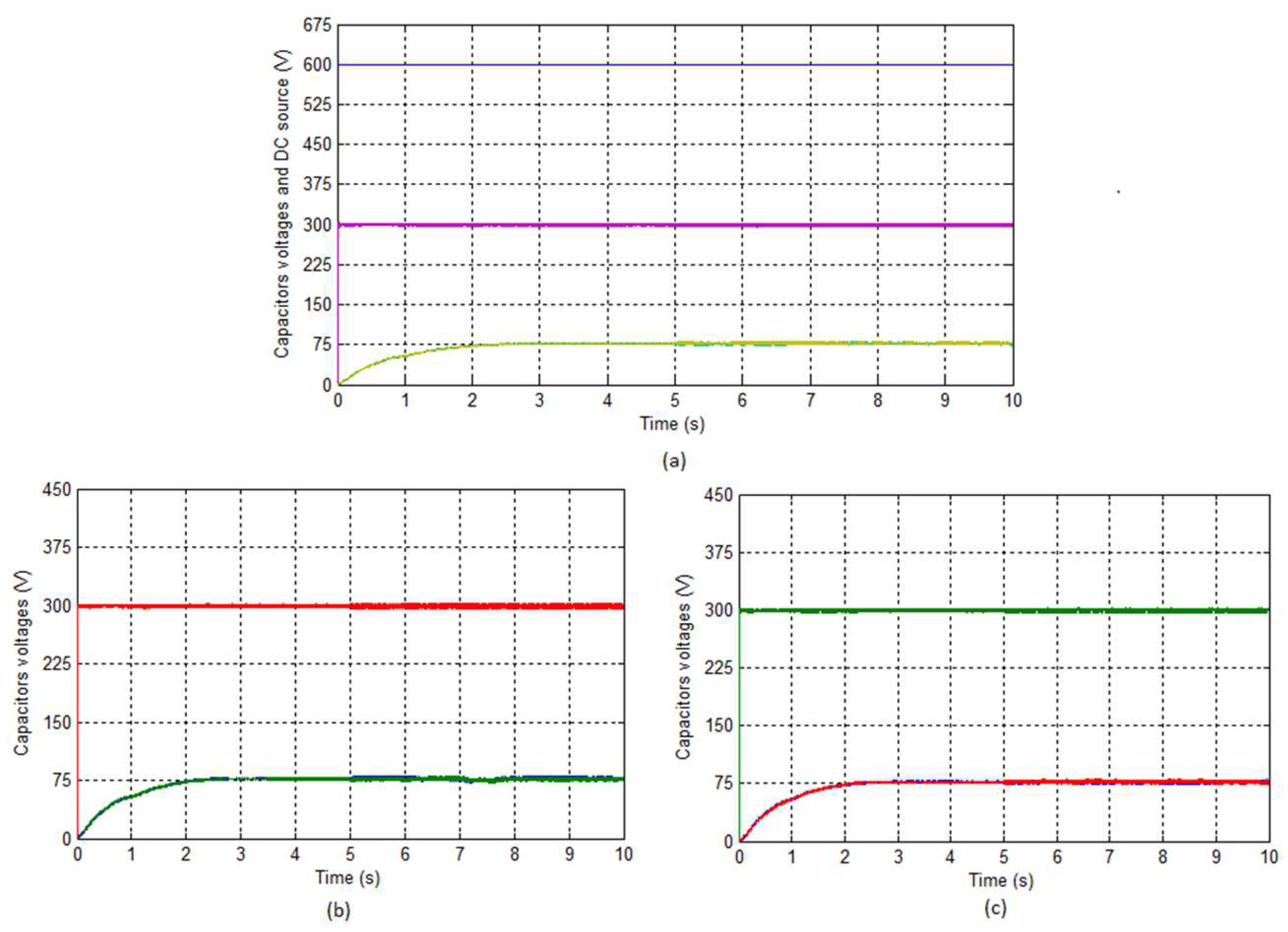

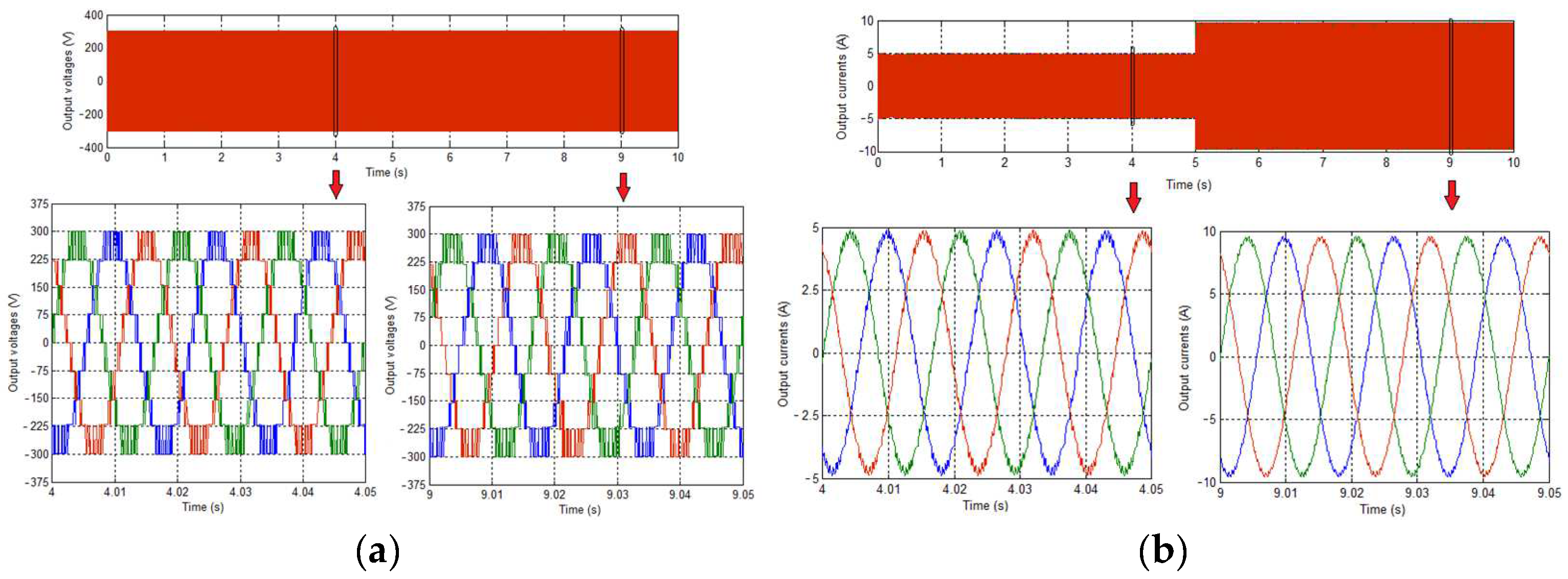

3.1. Using PWM Technique

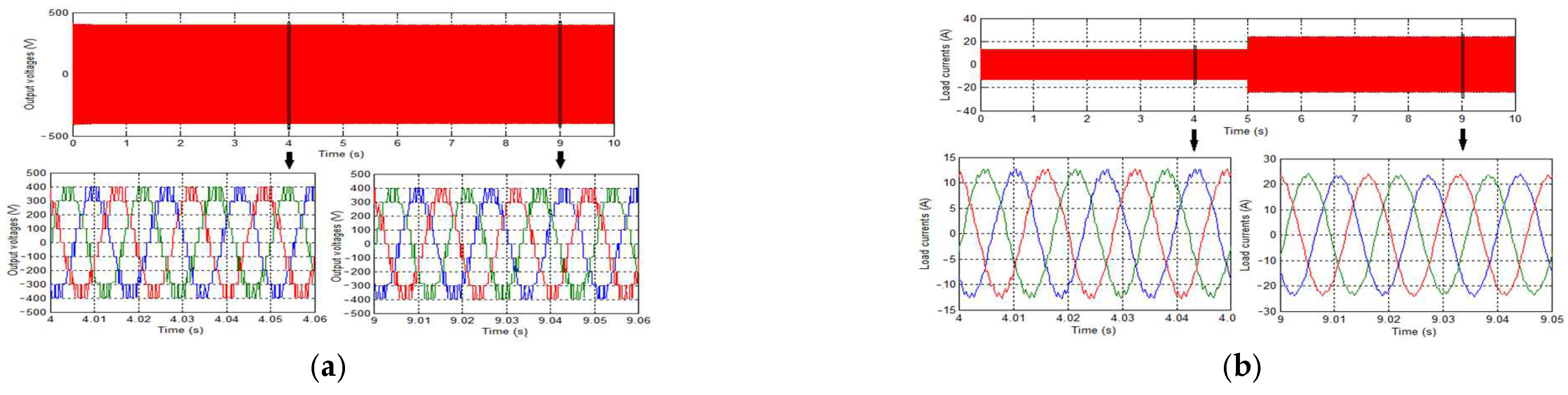

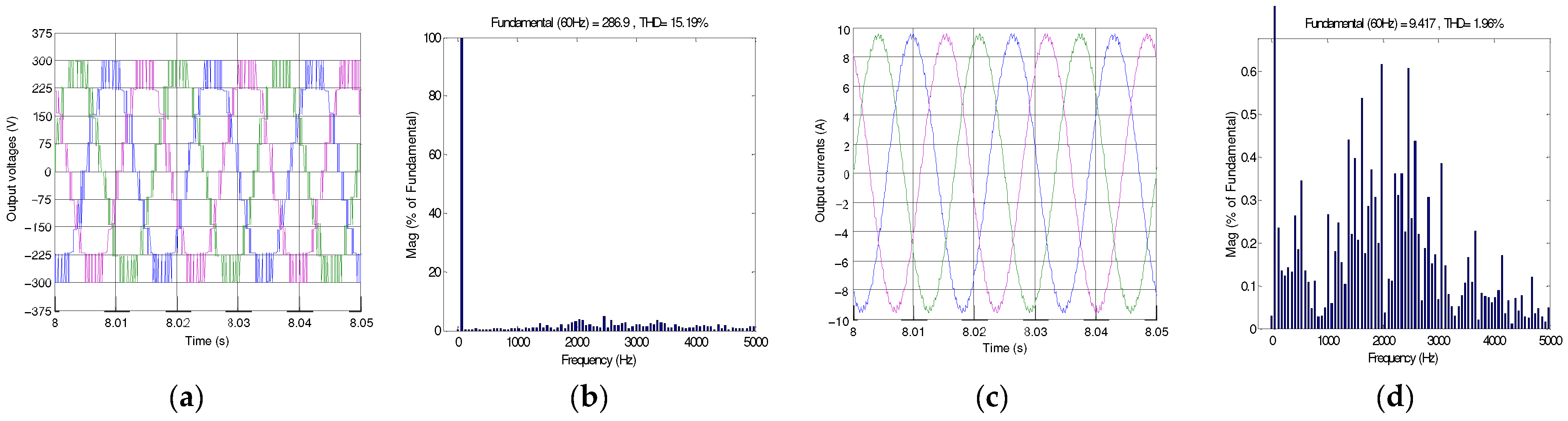

3.2. Using Hysteresis Control

4. Comparative Study

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Peng, F.Z.; Lai, J.-S.; McKeever, J.W.; VanCoevering, J. A multilevel voltage-source inverter with separate DC sources for static VAr generation. IEEE Trans. Ind. Appl. 1996, 32, 1130–1138. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-level conversion: High voltage choppers and voltage-source inverters. In Proceedings of the PESC’92 Record, 23rd Annual IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992; pp. 397–403. [Google Scholar] [CrossRef]

- El Gadari, A.; el Ouardi, H.; Alibou, S.; Ounejjar, Y.; Bejjit, L.; Sharifzadeh, M.; Al-Haddad, K. New Nine-Level SPUC Inverter Using Single DC Source. In Proceedings of the IECON 2019—45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K. New Nine-Level Inverter with Self Balancing of Capacitors Voltages. In Proceedings of the IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; Volume 1, pp. 4467–4472. [Google Scholar] [CrossRef]

- Ounejjar, Y.; El Gadari, A.; Abarzadeh, M.; Al-Haddad, K. PWM Sensor-less Balancing Technique for the Fifteen-Level PUC Converter. In Proceedings of the 2018 IEEE Electrical Power and Energy Conference (EPEC), Toronto, ON, Canada, 10–11 October 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Al-Haddad, K. Packed E-Cell (PEC) Converter Topology Operation and Experimental Validation. IEEE Access 2019, 7, 93049–93061. [Google Scholar] [CrossRef]

- Saha, D.; Roy, T.; Debata, S. Closed Loop Control of a Novel Three Phase Switched Capacitor Multilevel Inverter using Model Predictive Control Technique. In Proceedings of the 2018 National Power Engineering Conference (NPEC), Madurai, India, 9–10 March 2018. [Google Scholar] [CrossRef]

- Chen, R.; Niu, J.; Gui, H.; Zhang, Z.; Wang, F.; Tolbert, L.M.; Costinett, D.J.; Blalock, B.J.; Choi, B.B. Modeling, Analysis, and Reduction of Harmonics in Paralleled and Interleaved Three-Level Neutral Point Clamped Inverters with Space Vector Modulation. IEEE Trans. Power Electron. 2019, 35, 4411–4425. [Google Scholar] [CrossRef]

- Babadi, A.N.; Salari, O.; Mojibian, M.J.; Bina, M.T. Modified Multilevel Inverters with Reduced Structures Based on PackedU-Cell. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 6, 874–887. [Google Scholar] [CrossRef]

- Lopez, I.; Ceballos, S.; Pou, J.; Zaragoza, J.; Andreu, J.; Kortabarria, I.; Agelidis, V.G. Modulation Strategy for Multiphase Neutral-Point-Clamped Converters. IEEE Trans. Power Electron. 2015, 31, 928–941. [Google Scholar] [CrossRef]

- Xiang, C.-Q.; Shu, C.; Han, D.; Mao, B.-K.; Wu, X.; Yu, T.-J. Improved Virtual Space Vector Modulation for Three-Level Neutral-Point-Clamped Converter with Feedback of Neutral-Point Voltage. IEEE Trans. Power Electron. 2017, 33, 5452–5464. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K. Multiband hysteresis controller of the novel three phase seven-level PUC-NPC converter. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar] [CrossRef]

- Ali, M.; Tariq, M.; Upadhyay, D.; Khan, S.A.; Satpathi, K.; Alamri, B.; Alahmadi, A.A. Genetic Algorithm Based PI Control with 12-Band Hysteresis Current Control of an Asymmetrical 13-Level Inverter. Energies 2021, 14, 6663. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Dessaint, L.A. A Novel Six-Band Hysteresis Control for the Packed U Cells Seven-Level Converter: Experimental Validation. IEEE Trans. Ind. Electron. 2011, 59, 3808–3816. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L.; Li, Y. Neutral-Point Voltage Balancing Method for Five-Level NPC Inverters Based on Carrier-Overlapped PWM. IEEE Trans. Power Electron. 2020, 36, 1428–1440. [Google Scholar] [CrossRef]

- Wang, J.; Yuan, X.; Jin, B. Carrier-based Closed-loop DC-link Voltage Balancing Algorithm for Four Level NPC Converters Based on Redundant Level Modulation. IEEE Trans. Ind. Electron. 2020, 68, 11707–11718. [Google Scholar] [CrossRef]

- Nami, A.; Zare, F.; Ghosh, A.; Blaabjerg, F. A Hybrid Cascade Converter Topology with Series-Connected Symmetrical and Asymmetrical Diode-Clamped H-Bridge Cells. IEEE Trans. Power Electron. 2009, 26, 51–65. [Google Scholar] [CrossRef]

- Zhang, X.; Yue, W. Neutral point potential balance algorithm for three-level NPC inverter based on SHEPWM. Electron. Lett. 2017, 53, 1542–1544. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Gregoire, L.-A. Novel three phase seven level PWM converter. In Proceedings of the 2009 IEEE Electrical Power & Energy Conference (EPEC), Montreal, QC, Canada, 22–23 October 2009. [Google Scholar] [CrossRef]

- Vijaykrishna, G.; Shekhar, O.C. A Three Phase 7-Level and 9-Level Reversing Voltage Multilevel Inverter. Indian J. Sci. Technol. 2015, 8, 1–10. [Google Scholar] [CrossRef][Green Version]

- Ravi, Y.; Bansal, P.; Saxena, A.R. A three-phase 9-level inverter with reduced switching devices for different PWM techniques. In Proceedings of the 2014 6th IEEE Power India International Conference (PIICON), Delhi, India, 5–7 December 2014. [Google Scholar]

- Kumar, M. Analysis, Comparison & Simulation of Three Phase 9 Level Cascaded Multilevel Inverter with Advanced Modulation Control Techniques using Less Switches. In Proceedings of the 2018 Second International Conference on Advances in Electronics, Computers and Communications (ICAECC), Bangalore, India, 9–10 February 2018. [Google Scholar] [CrossRef]

- Bandaru, U.; Rayudu, S.D. Harmonic Orientation of Pulse Width Modulation Technique in Multilevel Inverters. Adv. Electr. Electron. Eng. 2011, 9, 29–34. [Google Scholar] [CrossRef]

- Irusapparajan, G.; Periyaazhagar, D. Asymmetric Three-Phase Cascading Trinary-DC Source Multilevel Inverter Topologies for Variable Frequency PWM. Circuits Syst. 2016, 7, 506–519. [Google Scholar] [CrossRef][Green Version]

| State | Interconnection | Voltage(V) | S1i | S2i | S3i | S4i | S5i | S6i | S7i | S8i | S9i |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 9 | Vc2 | 400 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 9′ | Vc3i | 400 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| 8 | Vc3i − Vc5i | 300 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 7 | Vc3i − (Vc4i + Vc5i) | 200 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 7′ | Vc4i + Vc5i | 200 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 6 | Vc4i | 100 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 5 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 5′ | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| 4 | −Vc5i | −100 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 3 | −Vc4i − Vc5i | −200 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 3′ | (Vc4i + Vc5i) − Vc3i | −200 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 2 | Vc4i − Vc3i | −300 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 1′ | −Vc3i | −400 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | −Vc1 | −400 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| Parameter | Value |

|---|---|

| Switching frequency | 1000 Hz |

| E (DC source voltage) | 800 V |

| Load resistor | 30 Ω |

| Load inductance | 15 mH |

| Auxiliary DC bus capacitor | 4000 µF |

| Amplitude modulation index | m = 0.75 |

| Parameters | Value |

|---|---|

| Hysteresis bandwidth | 0.25 |

| E (DC source voltage) | 600 V |

| Load resistor | 30 Ω |

| Load inductance | 15 mH |

| Auxiliary DC bus capacitor | 4000 µF |

| Amplitude Modulation Index | Inverters | THD Level % | ||

|---|---|---|---|---|

| 1000 Hz | 2000 Hz | 5000 Hz | ||

| m = 1.15 | Proposed Inverter | 14.05 | 13.32 | 13.27 |

| m = 1 | Proposed Inverter | 14.27 | 13.51 | 13.4 |

| 9-Level, Three-Phase Reversing Voltage [21] | N.C | N.C | 16.30 | |

| Three-Phase, 9-Level Inverter with Reduced Switching Devices [22] | 14.35 | N.C | N.C | |

| Three-Phase, 9-level Cascaded MLI with less switches [23] | N.C | N.C | 13.72 | |

| m = 0.9 | Proposed Inverter | 15.12 | 14.02 | 13.8 |

| 3-Phase, Nine-Level Diode Clamped Inverter [24] | 14.32 | 14.09 | N.C | |

| Asymmetric Three-Phase Cascading Trinary-DC Source [25] | N.C | 16.06 | N.C | |

| Three-Phase, 9-Level Inverter with Reduced Switching Devices | 15.27 | N.C | N.C | |

| m = 0.85 | Proposed Inverter | 15.41 | 14.60 | 14.22 |

| Asymmetric Three-Phase Cascading Trinary-DC Source | N.C | 17.39 | N.C | |

| m = 0.75 | Proposed Inverter | 16.36 | 15.73 | 15.17 |

| Inverters | Switches | Clamping Diodes | Capacitors | DC Source |

|---|---|---|---|---|

| Diode clamped | 48 | 168 | NA | 8 |

| Flying capacitor | 48 | NA | 84 | 8 |

| H-Bridge | 48 | NA | NA | 12 |

| PUC | 24 | NA | 6 | 3 |

| Proposed inverter | 27 | NA | 11 | 1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

El Gadari, A.; El Ouardi, H.; Ounejjar, Y.; Al-haddad, K. Novel Three-Phase Nine-Level Inverter and Its Control Strategies. Electronics 2022, 11, 3348. https://doi.org/10.3390/electronics11203348

El Gadari A, El Ouardi H, Ounejjar Y, Al-haddad K. Novel Three-Phase Nine-Level Inverter and Its Control Strategies. Electronics. 2022; 11(20):3348. https://doi.org/10.3390/electronics11203348

Chicago/Turabian StyleEl Gadari, Ayoub, Hind El Ouardi, Youssef Ounejjar, and Kamal Al-haddad. 2022. "Novel Three-Phase Nine-Level Inverter and Its Control Strategies" Electronics 11, no. 20: 3348. https://doi.org/10.3390/electronics11203348

APA StyleEl Gadari, A., El Ouardi, H., Ounejjar, Y., & Al-haddad, K. (2022). Novel Three-Phase Nine-Level Inverter and Its Control Strategies. Electronics, 11(20), 3348. https://doi.org/10.3390/electronics11203348