2W HBT Power Amplifier Module with Dual Second Harmonic Suppression Technique

Abstract

1. Introduction

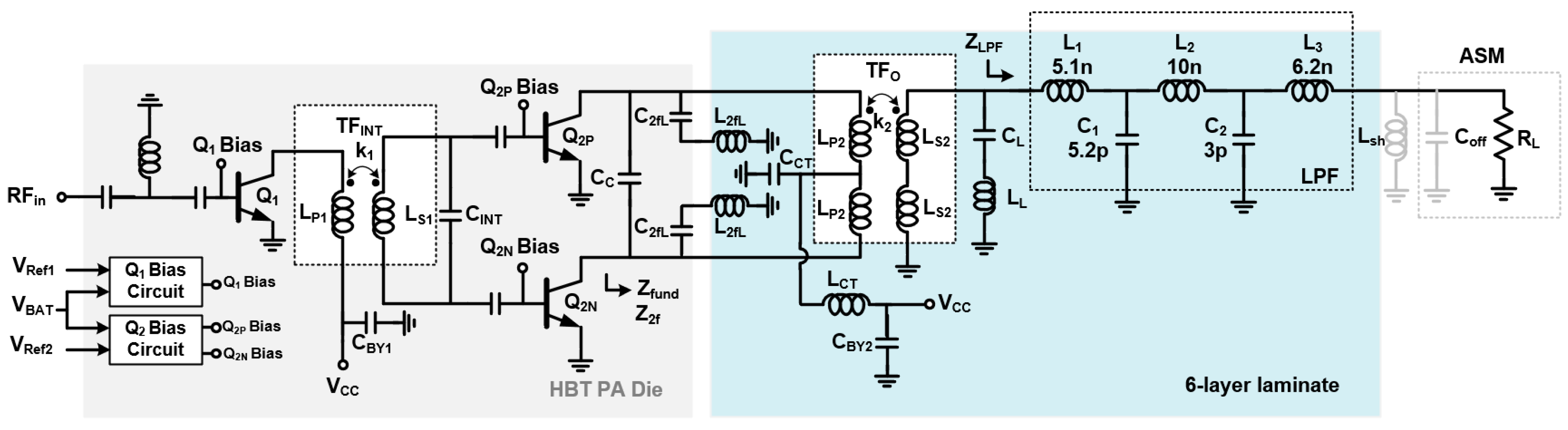

2. HBT PA Module Design

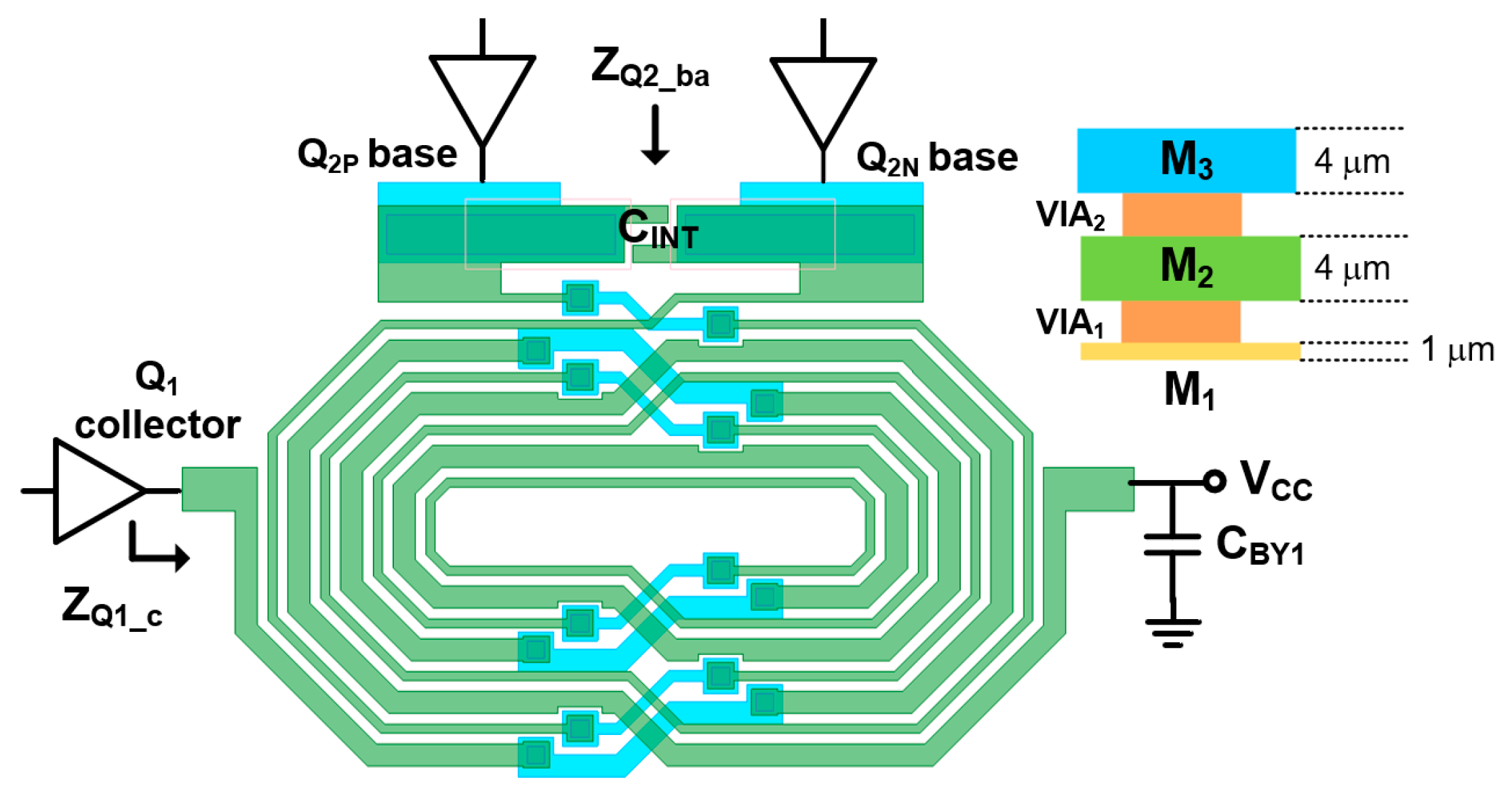

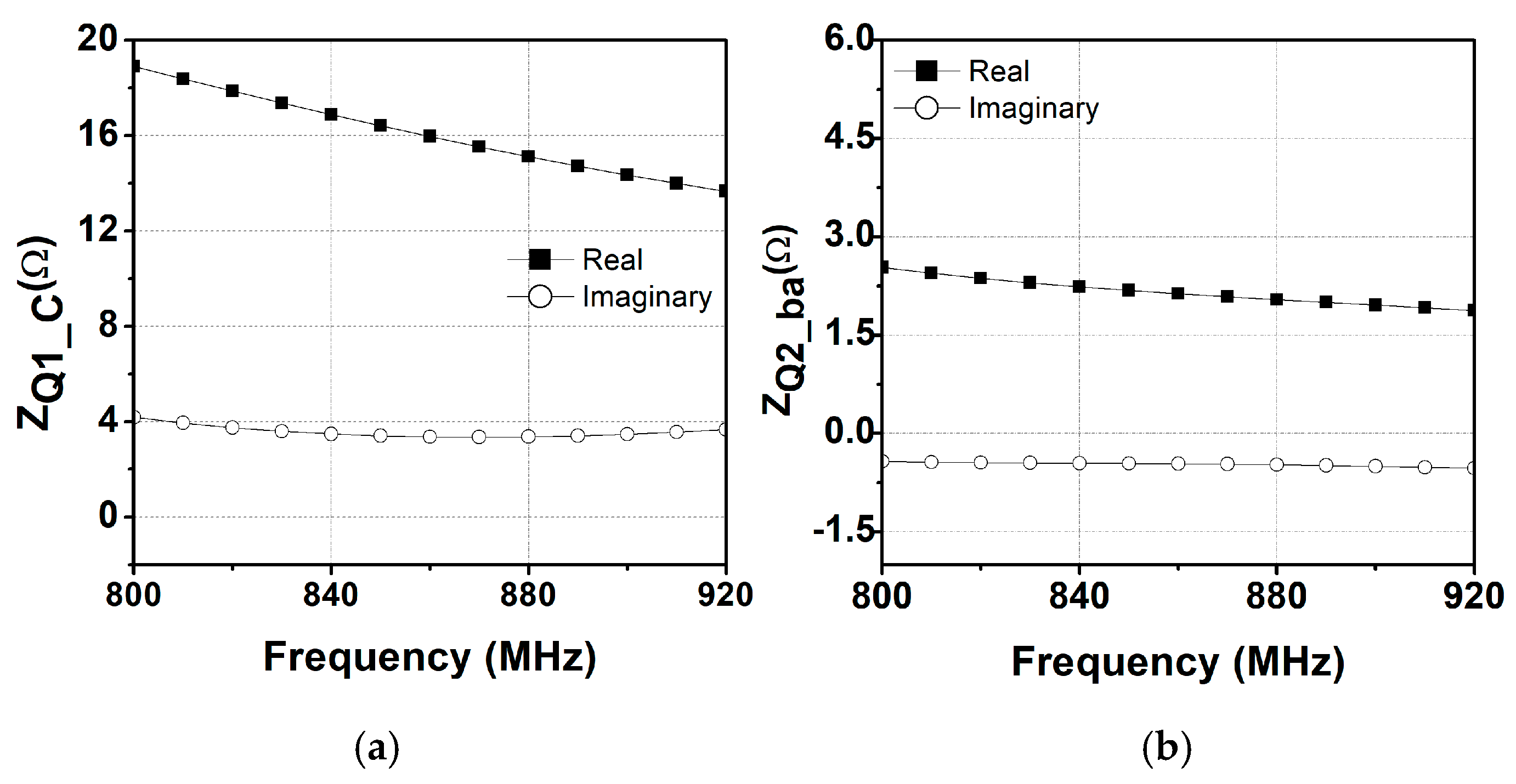

2.1. HBT PA Design

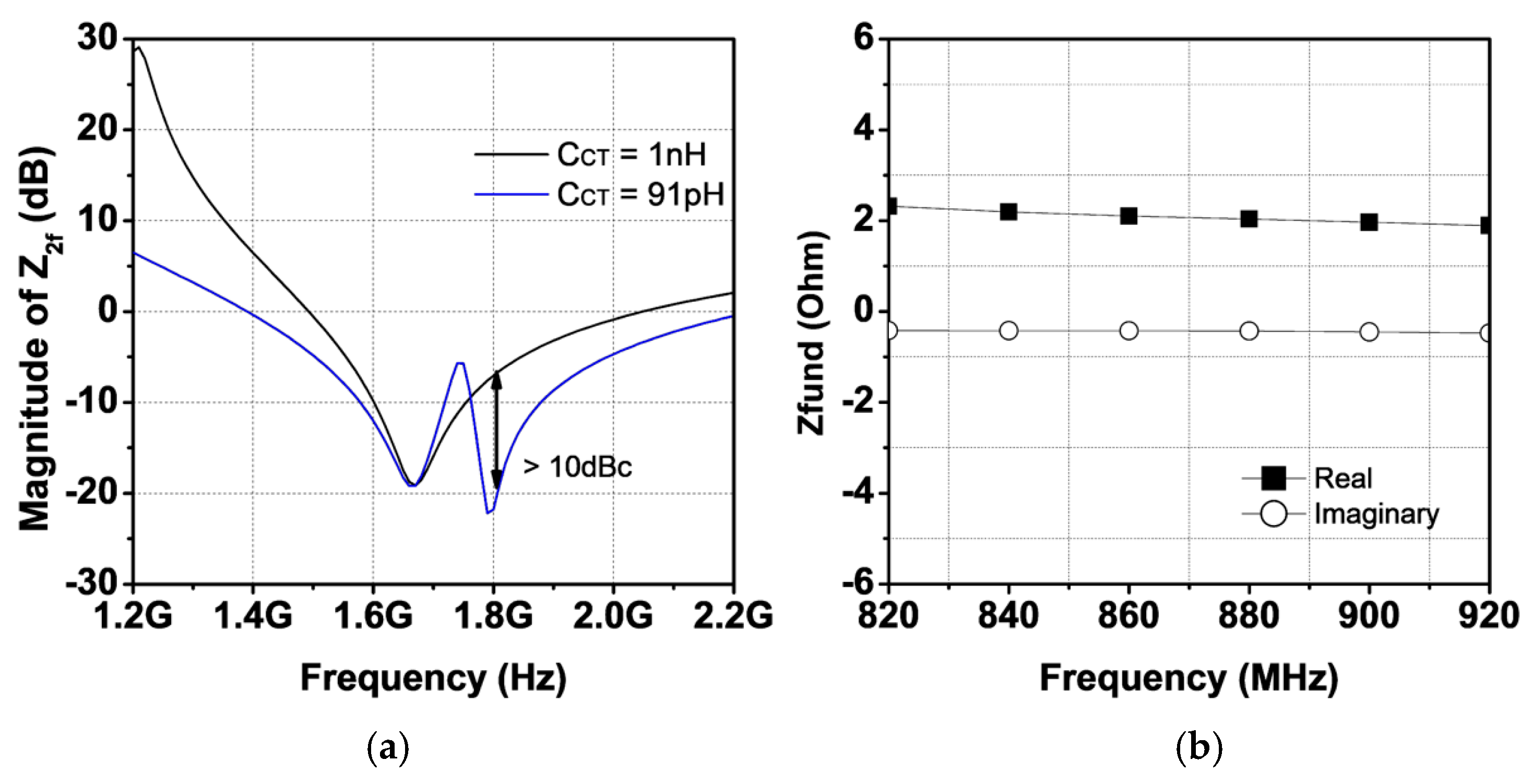

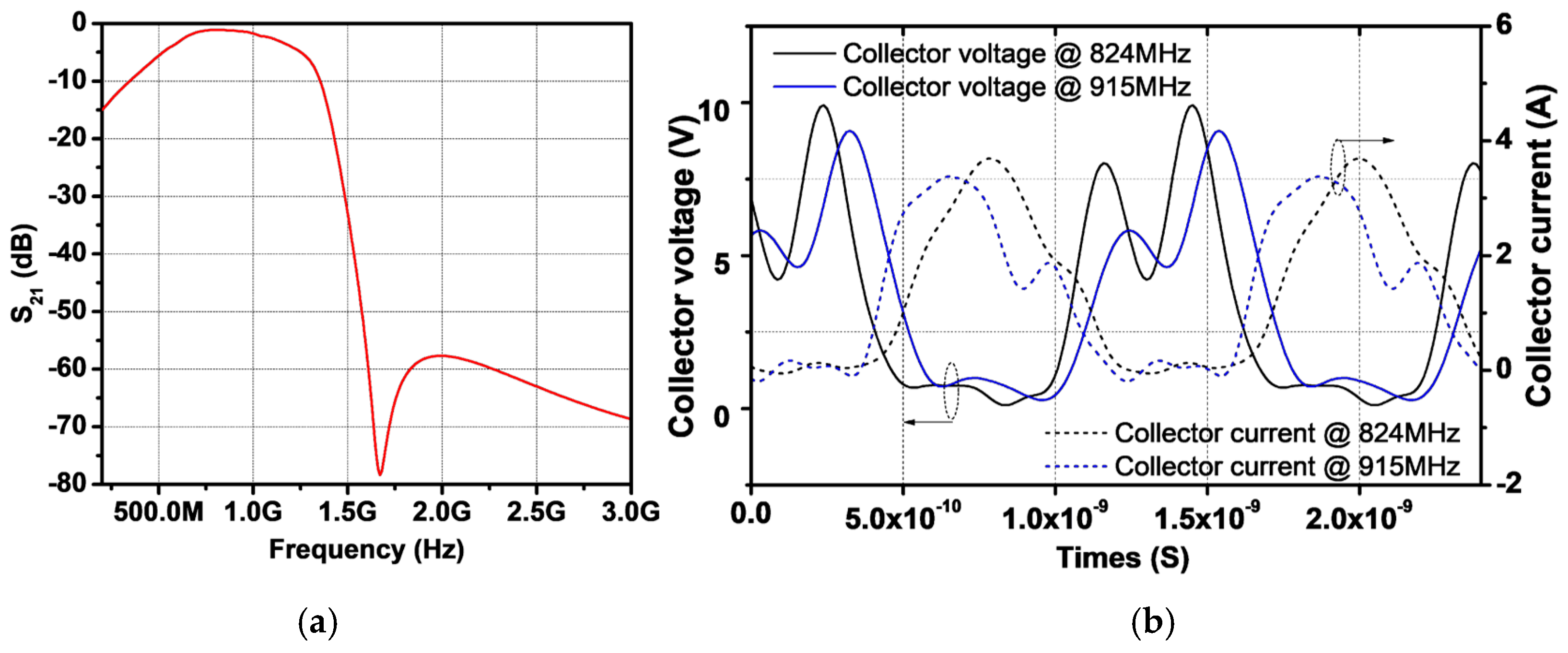

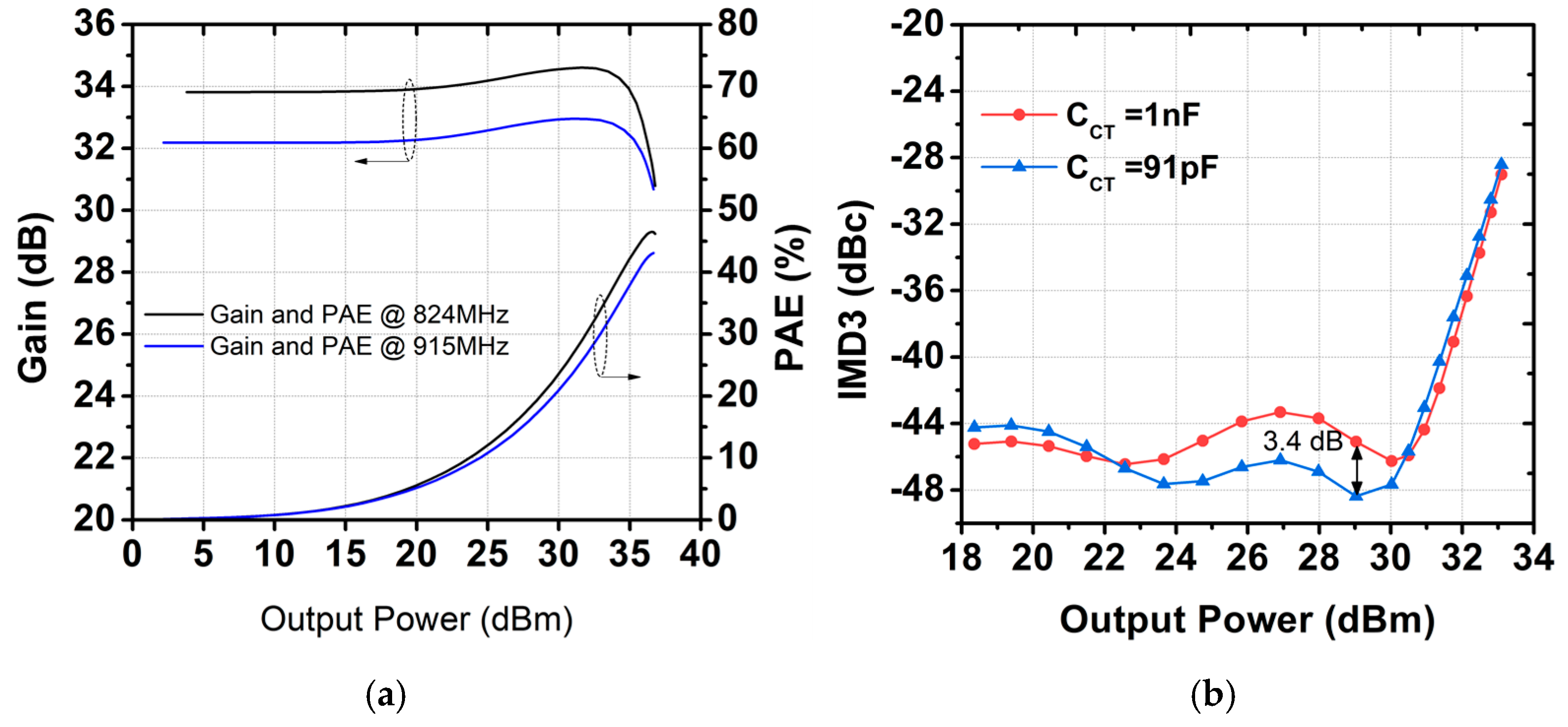

2.2. Second Harmonic-Tuned Output Matching

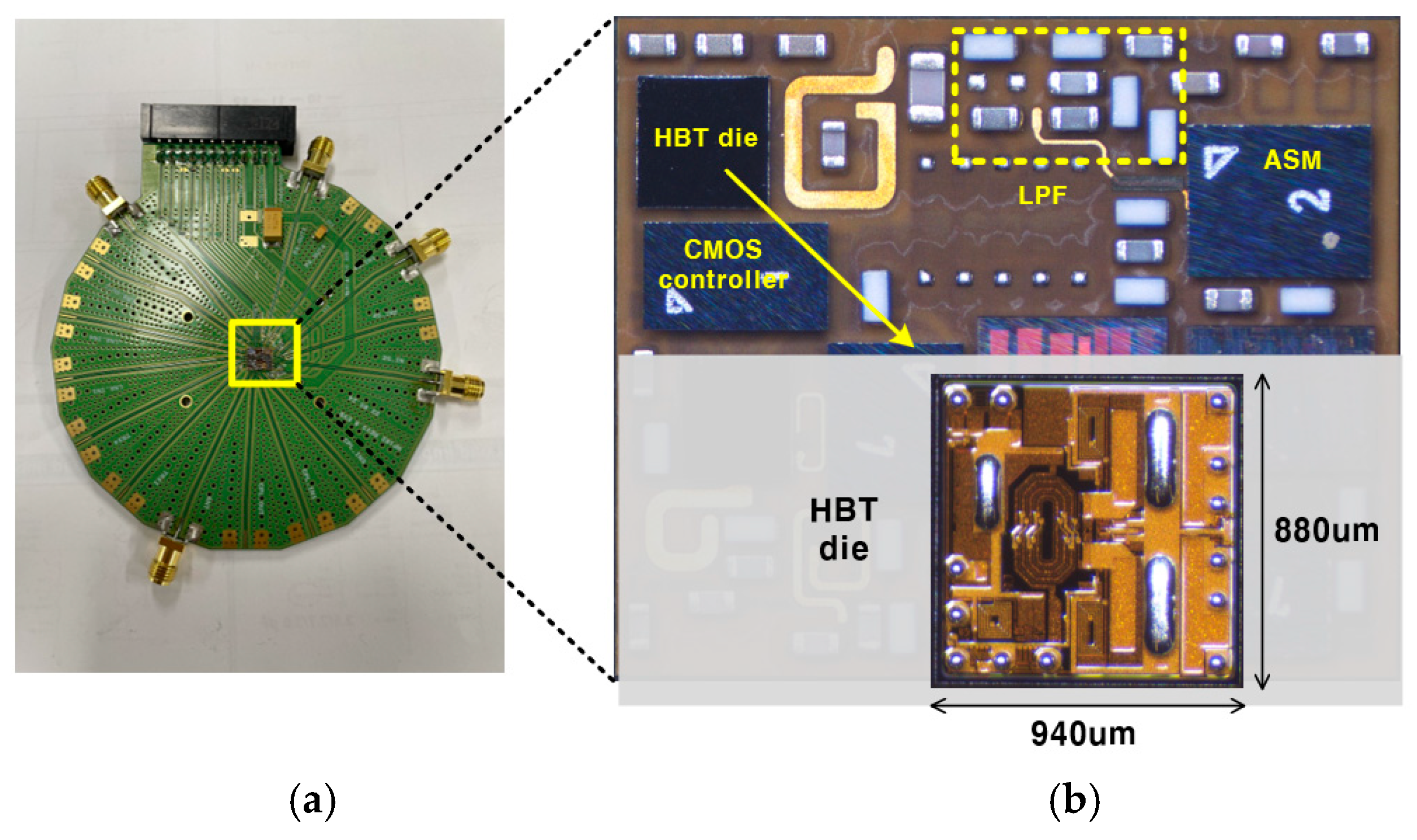

2.3. Implementation of HBT PA Module

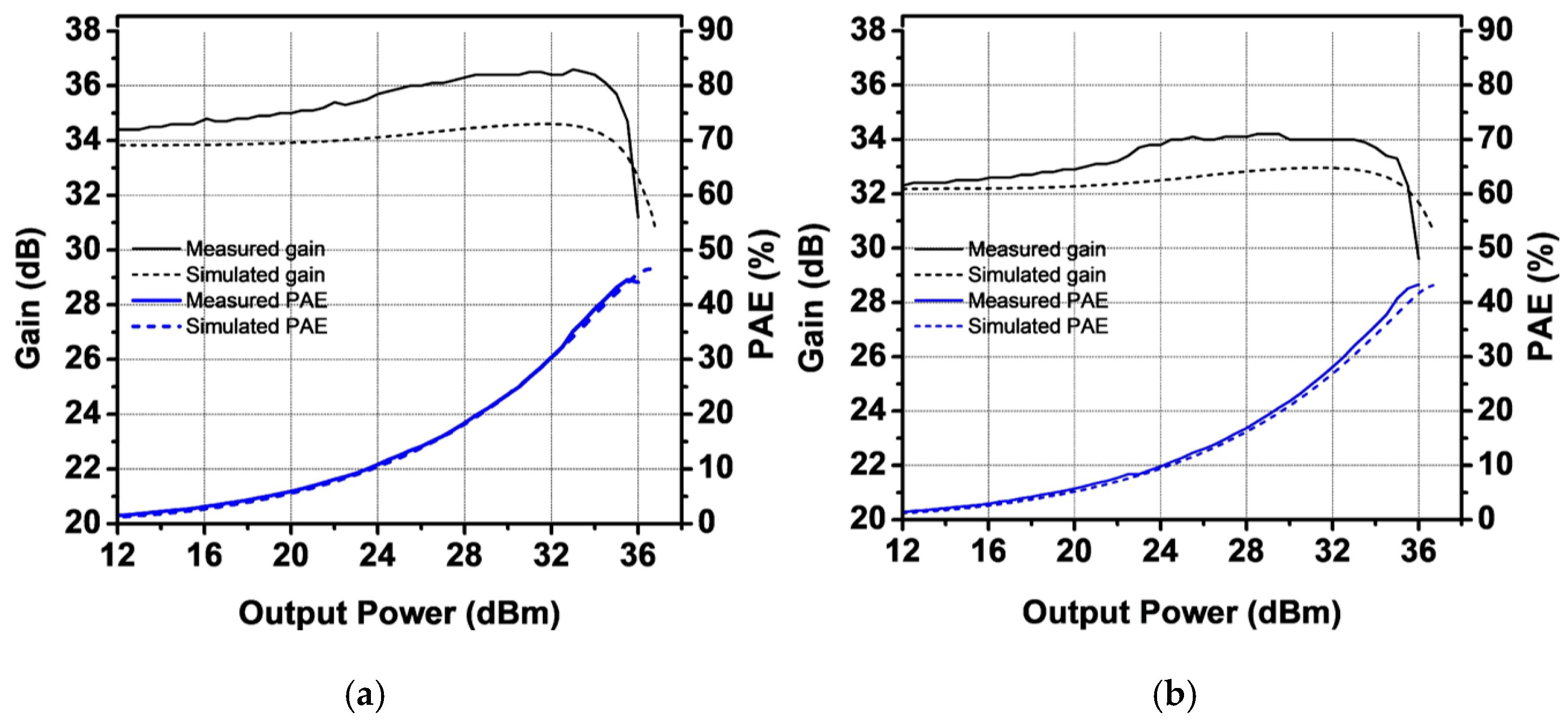

3. Measured Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Balteanu, F.; Modi, H.; Choi, Y.; Lee, J.; Drogi, S.; Khesbak, S. 5G RF front-end module architectures for mobile application. In Proceedings of the 2019 49th European Microwave Conference, Paris, France, 1–3 October 2019; pp. 252–255. [Google Scholar]

- Aoki, I.; Kee, S.; Magoon, R.; Aparicio, R.; Bohn, F.; Zachan, J.; Hatcher, G.; McClymont, D.; Hajimiri, A. A fully-integrated quad-band GSM/GPRS CMOS power amplifier. IEEE J. Solid State Circuits 2008, 43, 2747–2758. [Google Scholar] [CrossRef]

- Kim, W.; Yang, K.S.; Han, J.; Chang, J.J.; Lee, C.-H. An EDGE/GSM quad-Band CMOS power amplifier. IEEE J. Solid State Circuits 2014, 49, 2141–2149. [Google Scholar] [CrossRef]

- Tsai, M.D.; Lin, C.C.; Chen, P.Y.; Chang, T.Y.; Tseng, C.W.; Lin, L.C.; Beale, C.; Tseng, B.; Tenbroek, B.; Chiu, C.-S.; et al. A fully integrated multimode front-end module for GSM/EDGE/TD-SCDMA/TD-LTE applications using a Class-F CMOS power amplifier. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 5–9 February 2017; pp. 216–218. [Google Scholar]

- Ju, I.; Gong, Y.; Cressler, J.D. Highly linear high-power 802.11ac/ax WLAN SiGe HBT power amplifiers with a compact 2nd-harmonic-shorted four-way transformer and a thermally compensating dynamic bias circuit. IEEE J. Solid State Circuits 2020, 55, 2356–2370. [Google Scholar] [CrossRef]

- Hwang, S.; Jeon, J.; Bae, S.; Yoon, B.; Kang, S.; Kim, J. Switchless dual-power-mode fully differential HBT power amplifier for mobile applications. IEEE Trans. Microw. Theory Tech. 2023, 71, 2934–2945. [Google Scholar] [CrossRef]

- Li, J.; Zhang, Z.; Zhang, G. A 5.15–6.425 GHZ stagger-tuning neutralized power amplifier using a continuous-mode harmonically tuned network. IEEE Microw. Wirel. Technol. 2022, 33, 173–176. [Google Scholar] [CrossRef]

- Oka, T.; Hasegawa, M.; Hirata, M.; Amano, Y.; Ishimaru, Y.; Kawamura, H.; Sakuno, K. A high-power low-distortion GaAs HBT power amplifier for mobile terminals used in broadband wireless applications. IEEE J. Solid State Circuits 2007, 42, 2123–2129. [Google Scholar] [CrossRef]

- Spirito, M.; de Vreede, L.; Nanver, L.; Weber, S.; Burghartz, J. Power amplifier PAE and ruggedness optimization by second-harmonic control. IEEE J. Solid State Circuits 2003, 38, 1575–1583. [Google Scholar] [CrossRef]

- Refai, W.Y.; Davis, W.A. A highly efficient linear multimode multiband Class-J power amplifier utilizing GaAs HBT for handset modules. IEEE Trans. Microw. Theory Tech. 2020, 68, 3519–3531. [Google Scholar] [CrossRef]

- Skyworks Inc. SKY77336. Available online: https://www.skyworksinc.com/Products/Amplifiers/SKY77336 (accessed on 16 February 2025).

- Qorvo. TQM7M9023. Available online: https://www.qorvo.com/products/p/TQM7M9023 (accessed on 16 February 2025).

| Parameters | Value | Parameters | Value |

|---|---|---|---|

| 3.3 nH | 0.82 | ||

| 2.6 nH | 91 pF | ||

| 0.75 | 0.4 nH | ||

| 0.85 nH | 8.8 pF | ||

| 2.9 nH | 0.35 nH |

| Ref. | [3] | [4] | [10] | [11] | [12] | This work | ||

| Process | 180 nm CMOS | 153 nm CMOS | GaAs HBT | GaAs HBT | GaAs HBT | GaAs HBT | ||

| Harmonic filter | No | Yes | No | No | Yes | Yes | ||

| Antenna switch | No | Yes | No | No | Yes | Yes | ||

| Frequency (MHz) | 800/850 | 850 | 814–915 | 824–915 | 824–915 | 824–915 | ||

| VDD (V) | 3.5 | 3.5 | 3.5 | 3.5 | 3.5 | 3.5 | ||

| Reference output | PA output | Mod. output | PA output | PA output | PA output | PA output 1 | Mod. output | |

| GMSK GSM /EGSM | Psat (dBm) | 34.5 | 34 | 34.3 | 35 | 35 | 37.15 | 36 |

| PAE (%) | 55 | 36.8 | 57.5–62.2 | 55 | 55 | 54.5–57 | 41.8–43.7 | |

| Harmonic, 2fo (dBm) | - | <−30 | - | −10 | −10 | - | <−50 | |

| Harmonic, 3fo (dBm) | - | <−30 | - | −15 | −15 | - | <−43 | |

| Rx band noise (dBm/100 kHz) @20 MHz offset | −86 | −84 | - | −87 | −87 | - | −88 | |

| EDGE GSM /EGSM | Pout (dBm) | 28.5 | 28 | 29 | 29 | 29 | 29.65 | 28.5 |

| PAE (%) | 22 | - | 33–35 | 28 | 28 | 27.3 | 21 | |

| ACPR (dBc) @400 kHz | −57 | −61 | −52.8 | - | −60 | - | <−61 | |

| ACPR (dBc) @600 kHz | −75 | - | - | - | −70 | - | <−70 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Byeon, C.-W.; Kim, J.-H. 2W HBT Power Amplifier Module with Dual Second Harmonic Suppression Technique. Sensors 2025, 25, 1231. https://doi.org/10.3390/s25041231

Byeon C-W, Kim J-H. 2W HBT Power Amplifier Module with Dual Second Harmonic Suppression Technique. Sensors. 2025; 25(4):1231. https://doi.org/10.3390/s25041231

Chicago/Turabian StyleByeon, Chul-Woo, and Joon-Hyung Kim. 2025. "2W HBT Power Amplifier Module with Dual Second Harmonic Suppression Technique" Sensors 25, no. 4: 1231. https://doi.org/10.3390/s25041231

APA StyleByeon, C.-W., & Kim, J.-H. (2025). 2W HBT Power Amplifier Module with Dual Second Harmonic Suppression Technique. Sensors, 25(4), 1231. https://doi.org/10.3390/s25041231