A CMOS Optoelectronic Transceiver with Concurrent Automatic Power Control for Short-Range LiDAR Sensors

Abstract

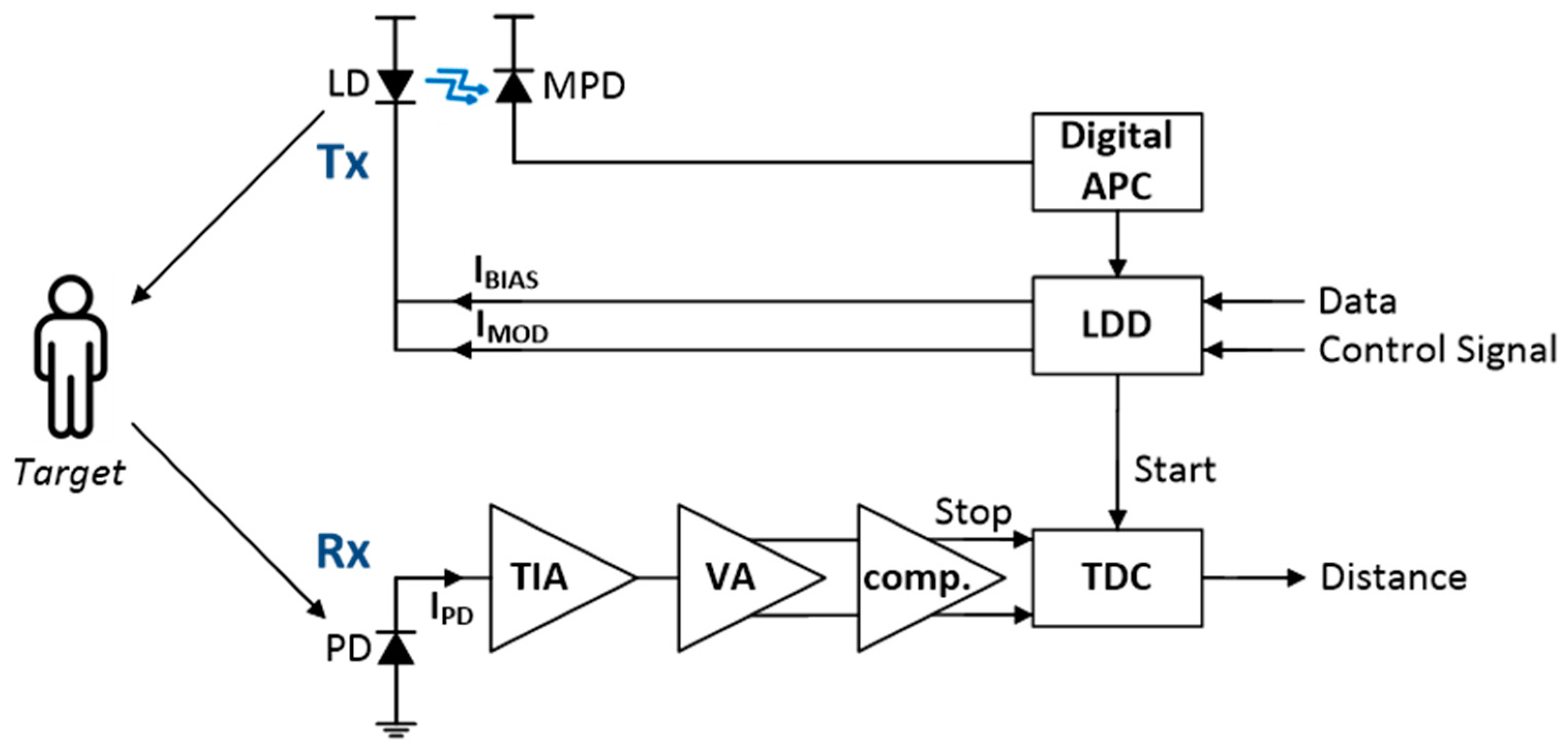

1. Introduction

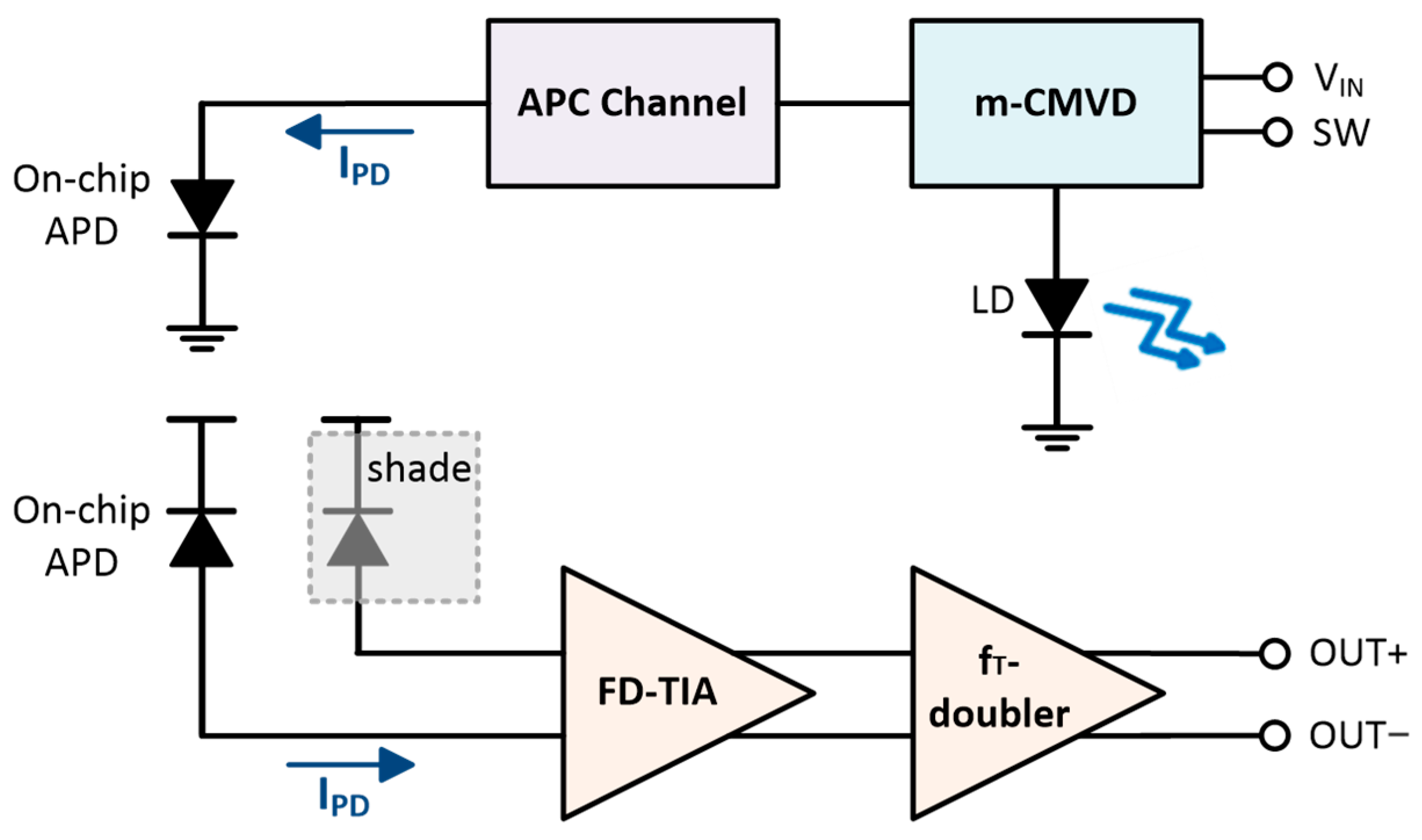

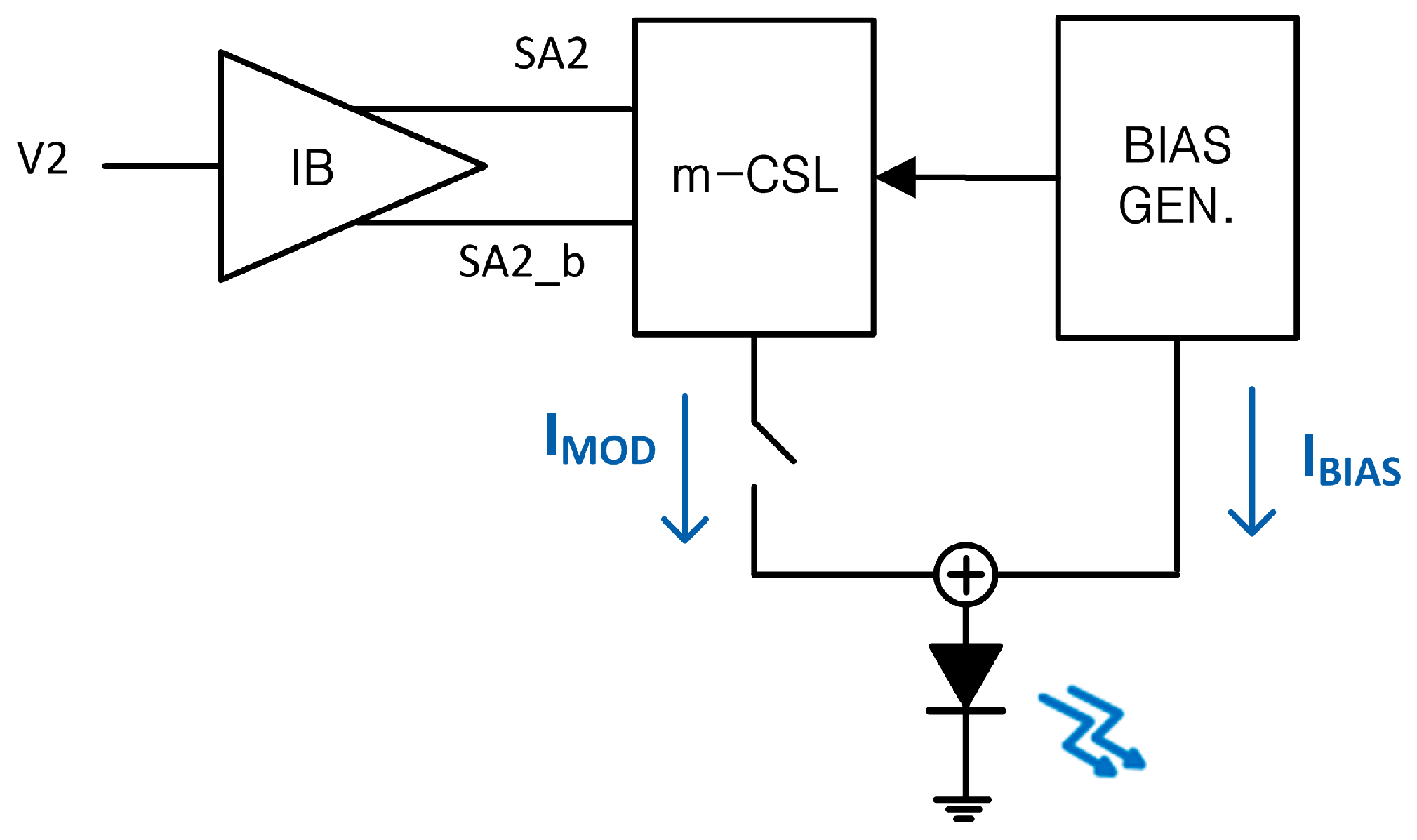

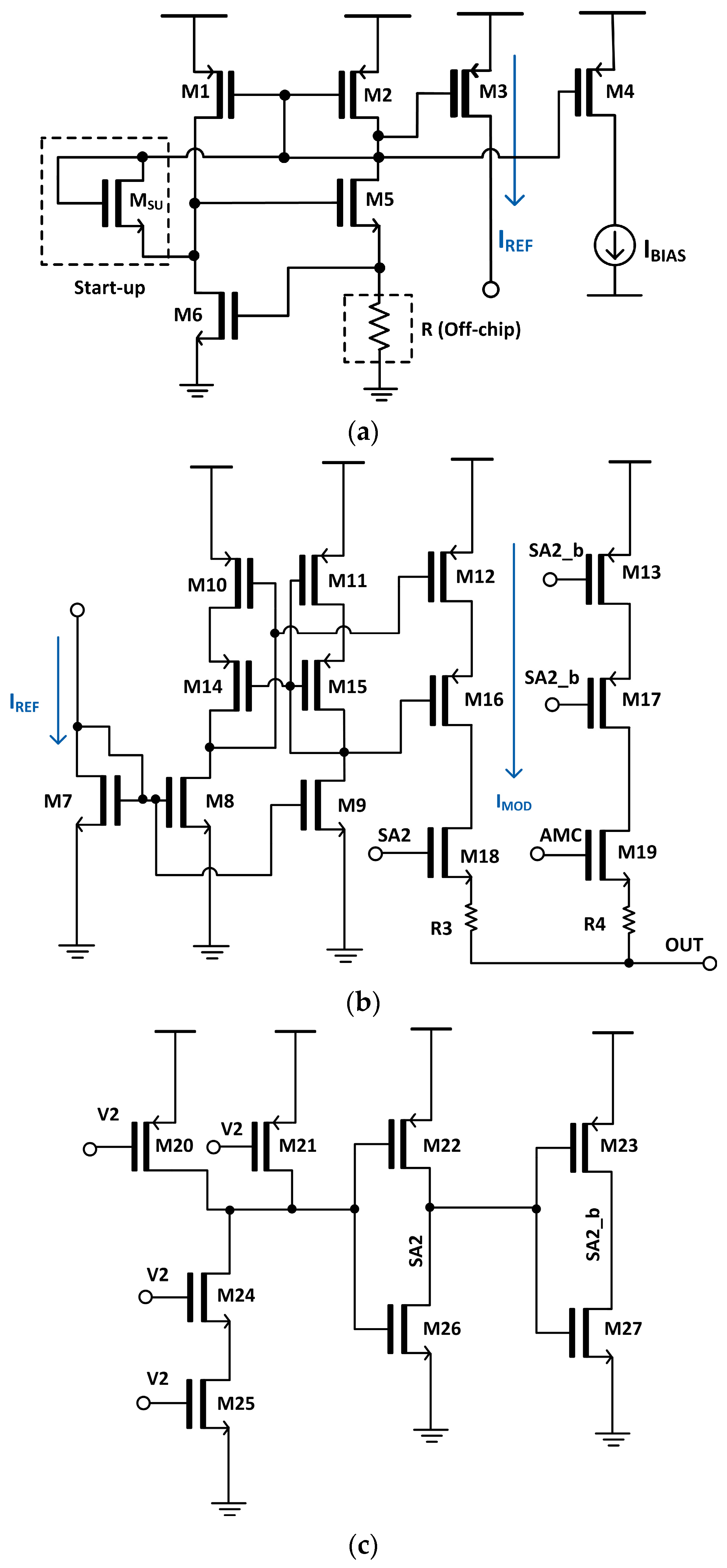

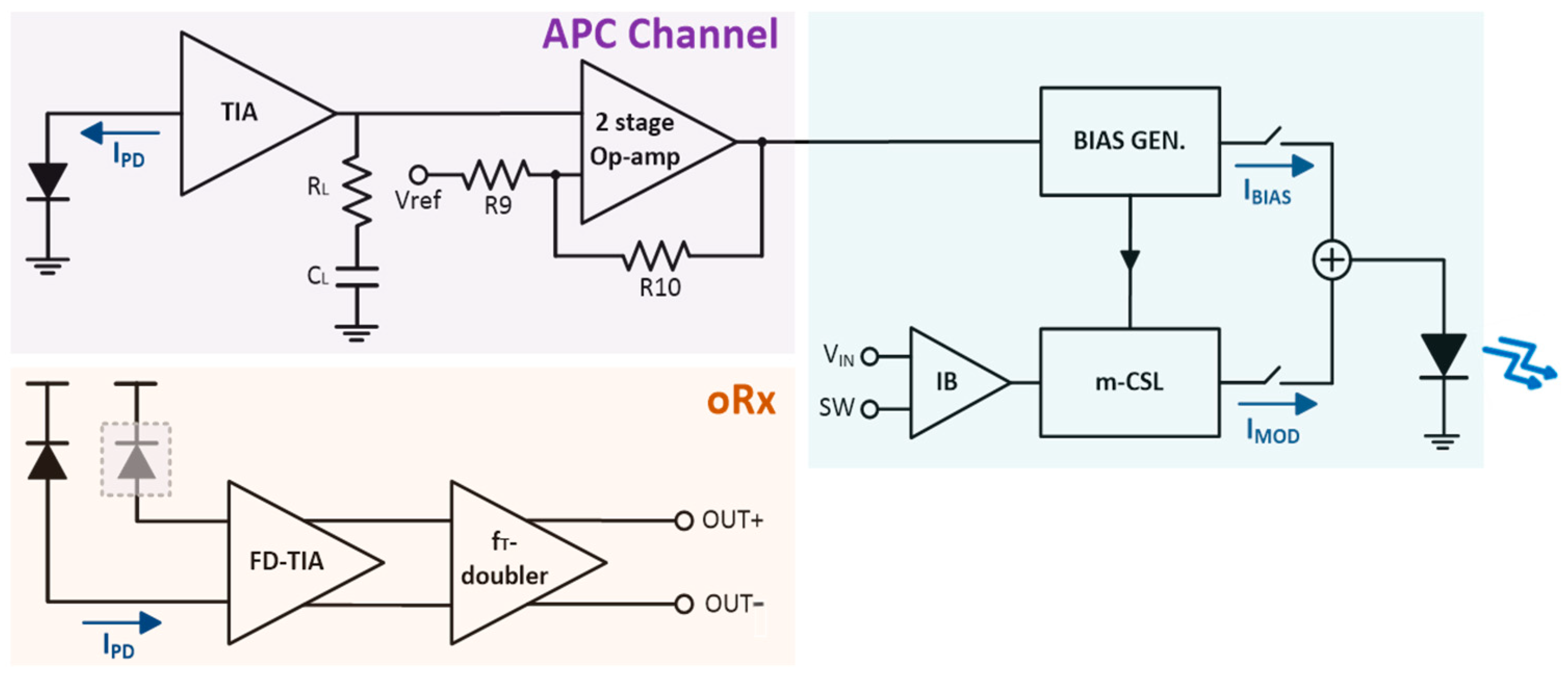

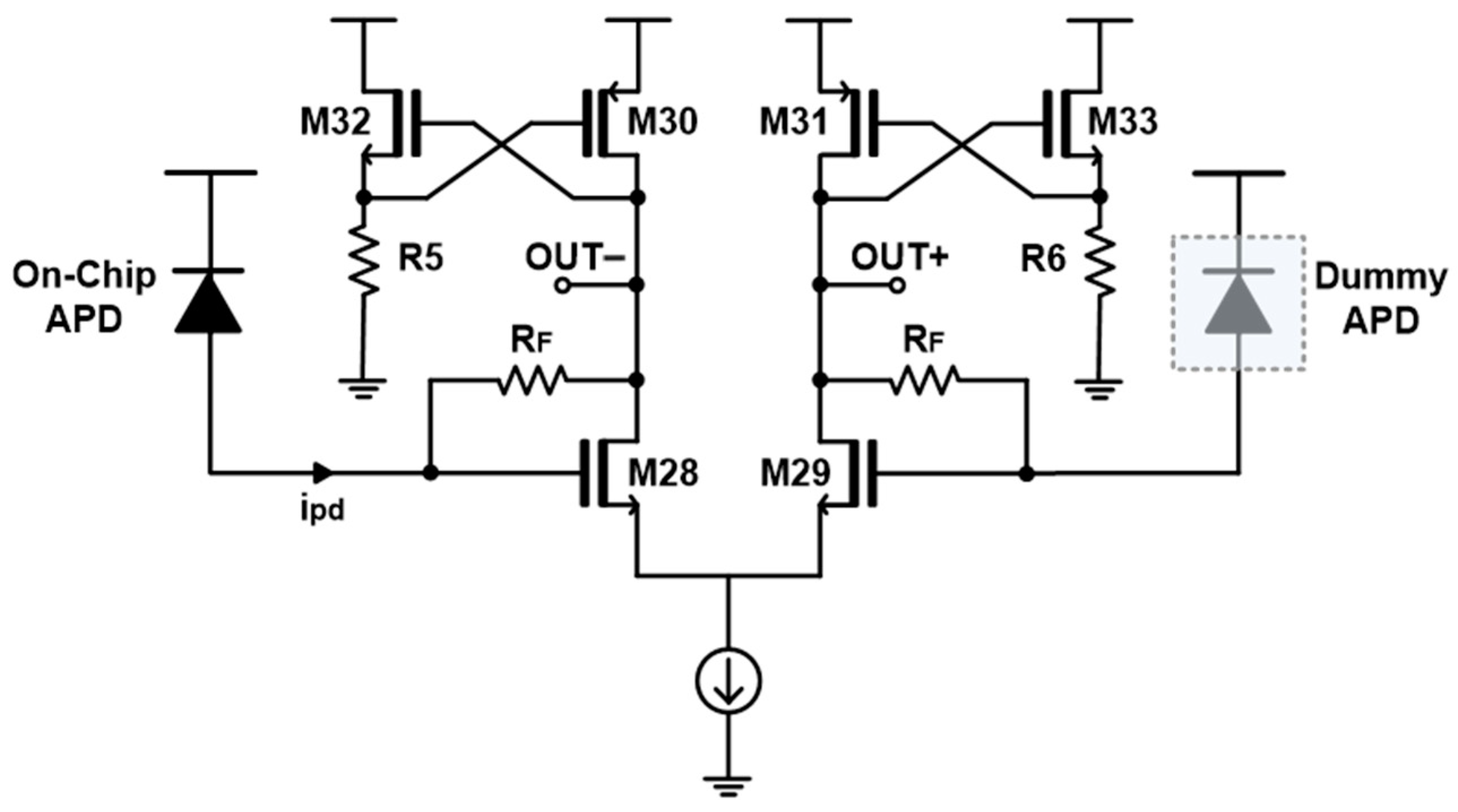

2. Circuit Description

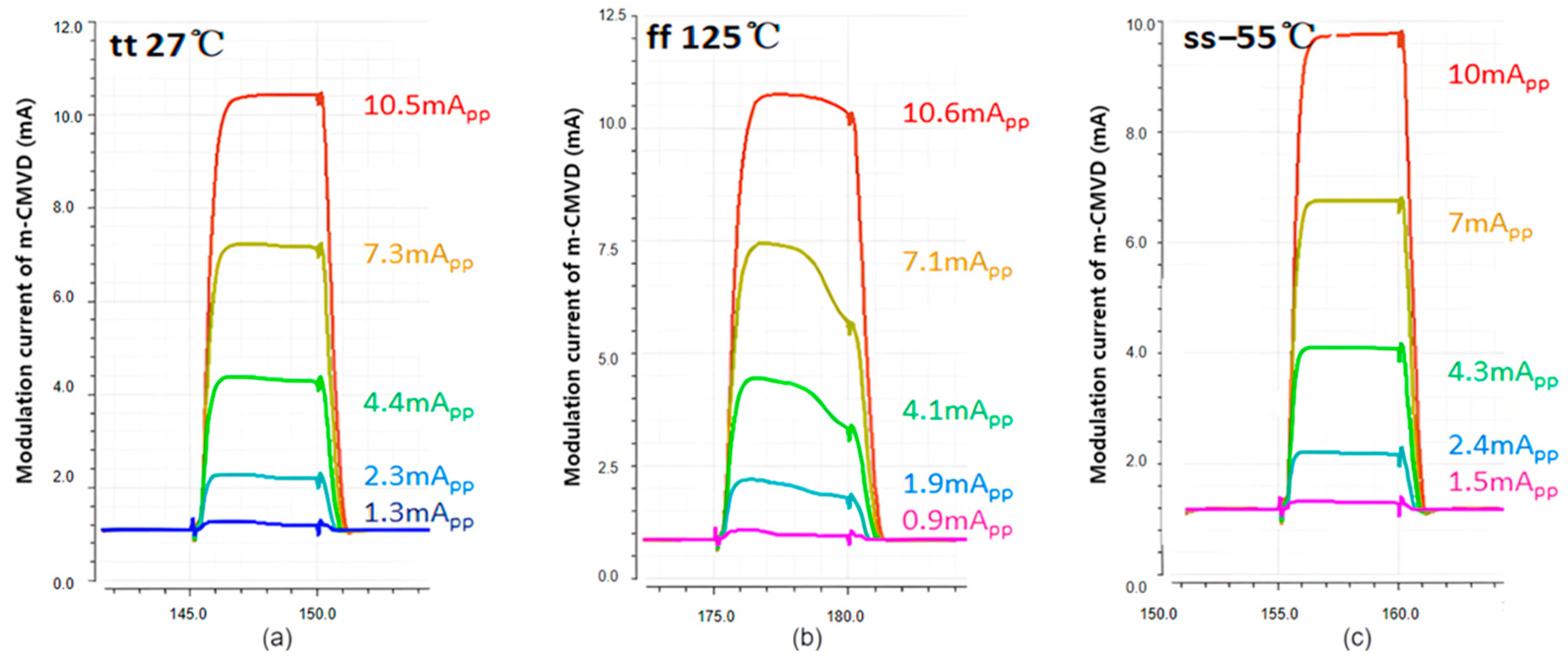

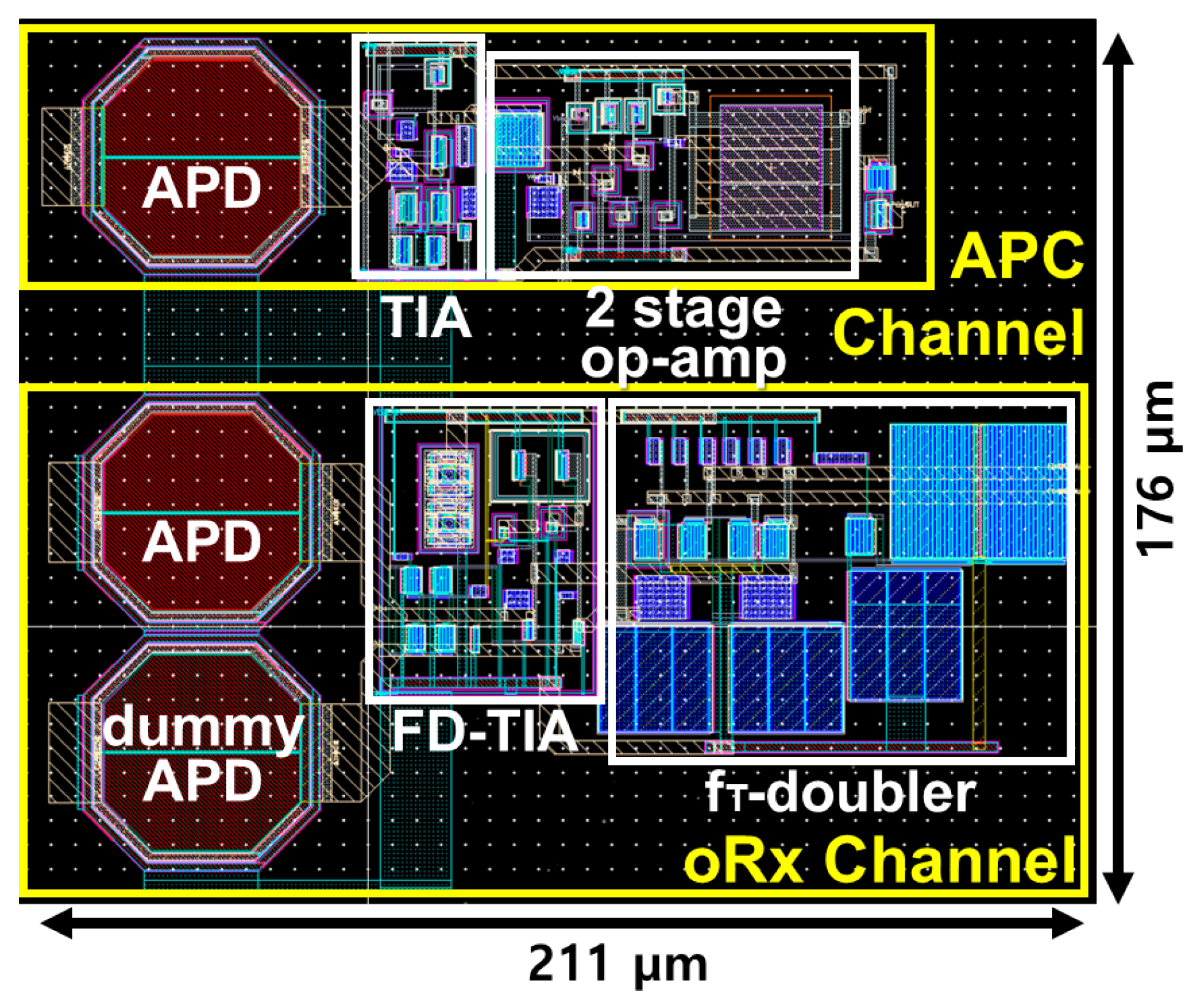

3. Layout and Simulation Results

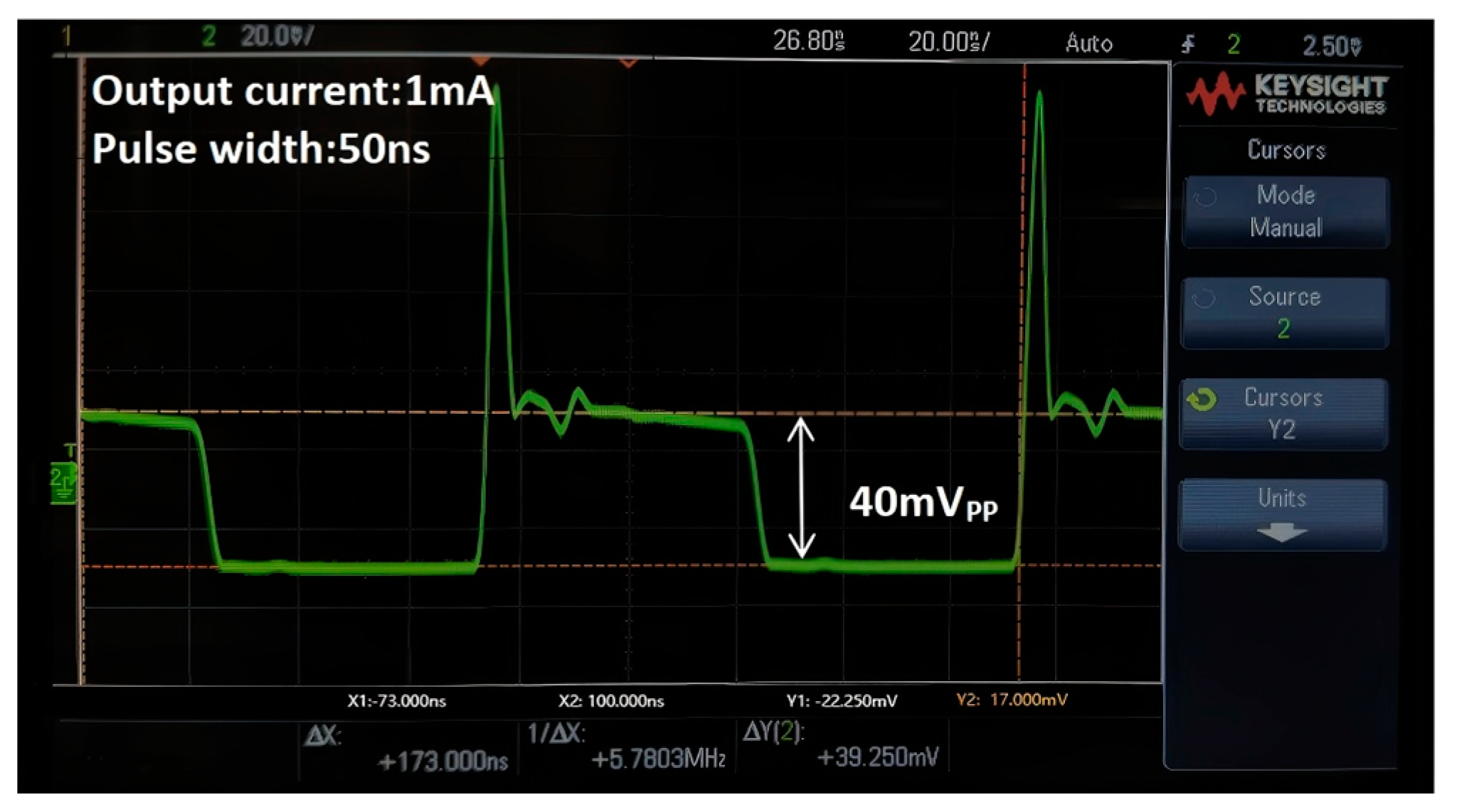

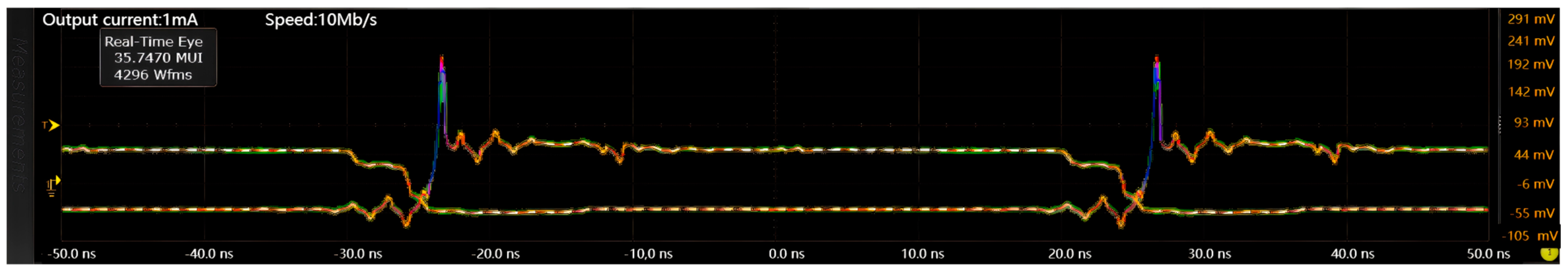

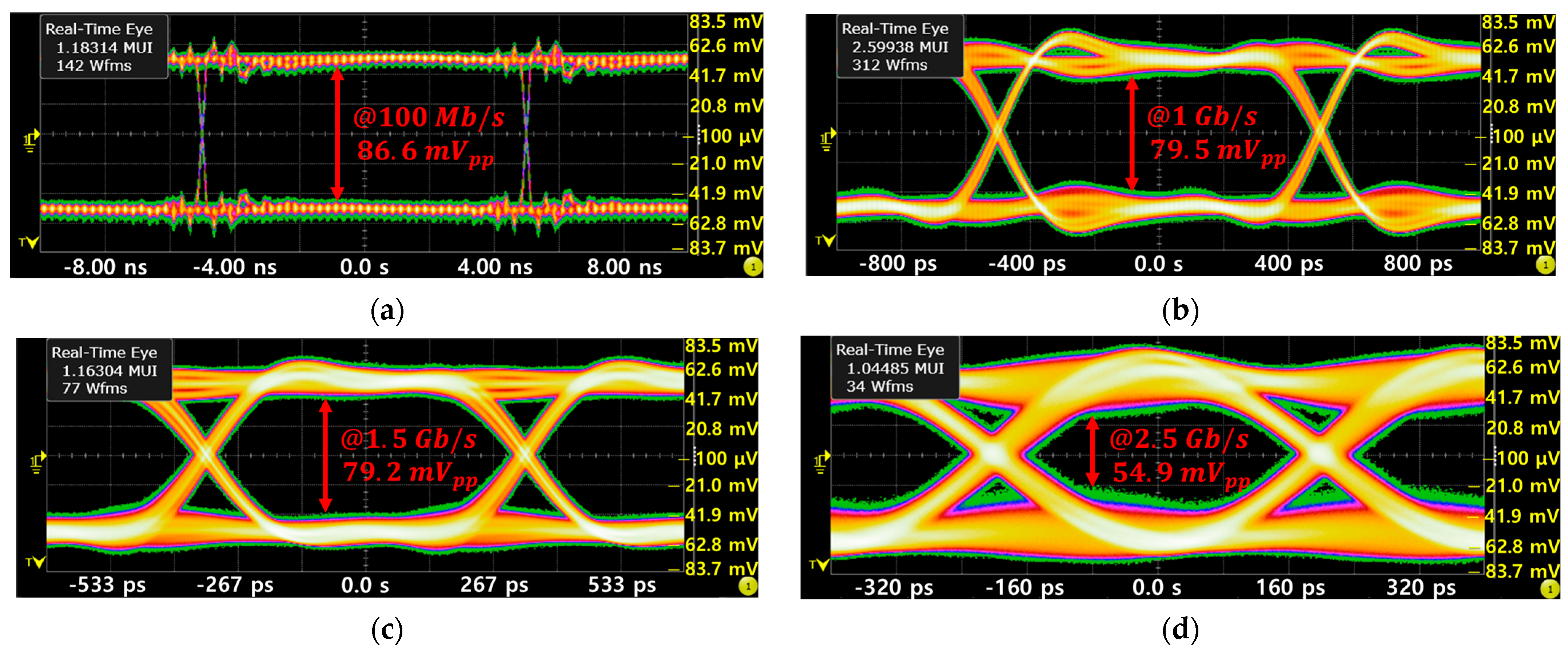

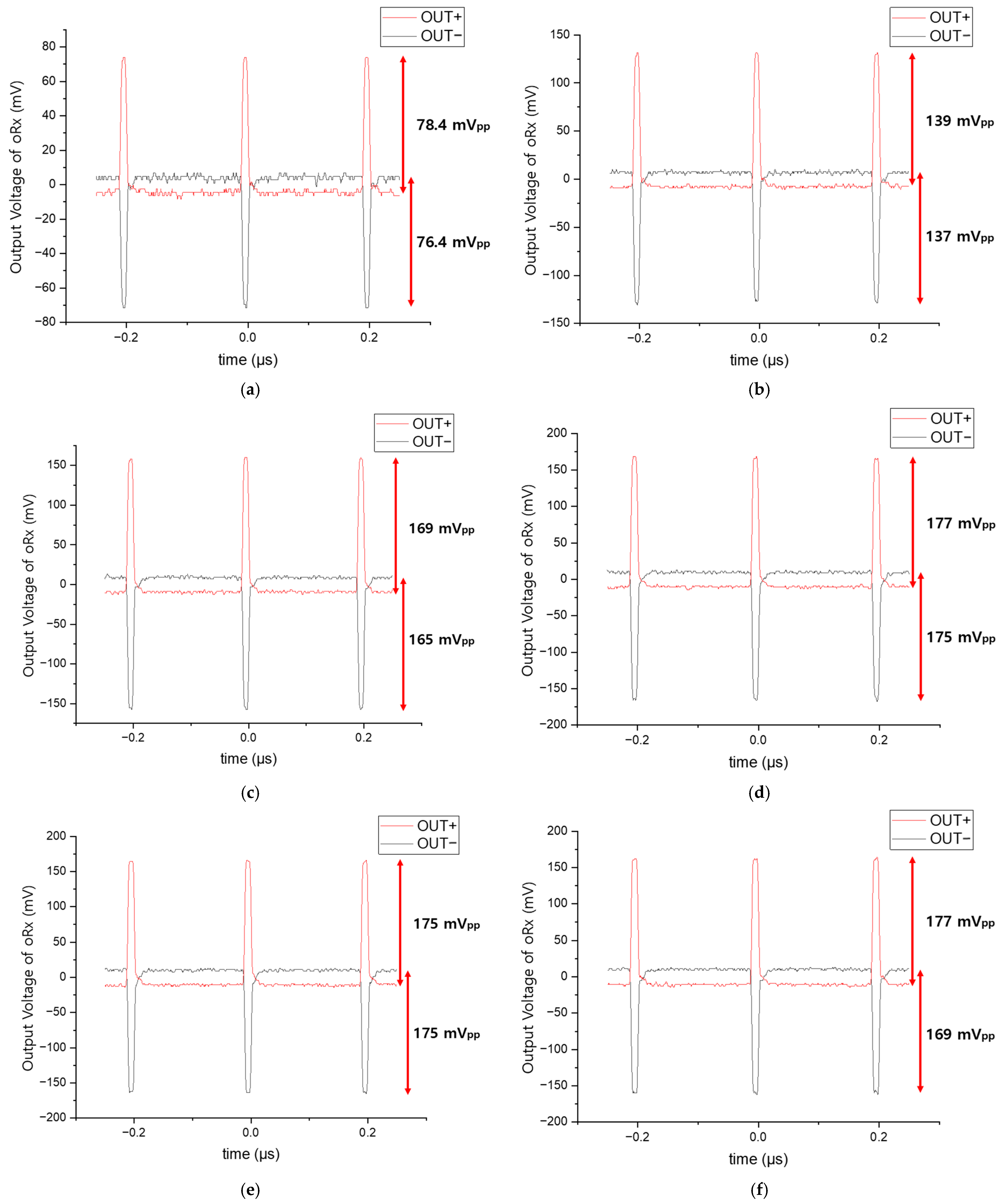

4. Measured Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zamanakos, G.; Tsochatzidis, L.; Amanatiadis, A.; Pratikakis, I. A comprehensive survey of LIDAR-based 3D object detection methods with deep learning for autonomous driving. Comput. Graph. 2021, 99, 153–181. [Google Scholar] [CrossRef]

- Usmani, S.; Saboor, A.; Haris, M.; Khan, M.A.; Park, H. Latest Research Trends in Fall Detection and Prevention Using Machine Learning: A Systematic Review. Sensors 2021, 21, 5134. [Google Scholar] [CrossRef] [PubMed]

- Ohno, M.; Ukyo, R.; Amano, T.; Rizk, H.; Yamaguchi, H. Privacy-preserving Pedestrian Tracking using Distributed 3D LiDARs. In Proceedings of the IEEE International Conference on Pervasive Computing and Communications (PerCom), Atlanta, GA, USA, 13–17 March 2023. [Google Scholar]

- Shi, Y.; Zhang, W.; Yao, Z.; Li, M.; Liang, Z.; Cao, Z.; Zhang, H.; Huang, Q. Design of a Hybrid Indoor Location System Based on Multi-Sensor Fusion for Robot Navigation. Sensors 2018, 18, 3581. [Google Scholar] [CrossRef] [PubMed]

- Roriz, R.; Cabral, J.; Gomes, T. Automotive LiDAR Technology: A Survey. IEEE Trans. Intell. Transp. Syst. 2022, 23, 6282–6297. [Google Scholar] [CrossRef]

- Li, J. Design of Burst-Mode Laser Driver Based on Digital APC. Master’s Thesis, Xidian University, Xi’an, China, 2013. [Google Scholar]

- Nissinen, J.; Nissinen, I.; Kostamovaara, J. Integrated Receiver Including Both Receiver Channel and TDC for a Pulsed Time-of-Flight Laser Rangefinder with cm-Level Accuracy. IEEE J. Solid-State Circuits 2009, 44, 1486–1497. [Google Scholar] [CrossRef]

- TIDA-01573 Reference Design: High-Speed, High-Power Laser Driver for LIDAR Applications. Available online: https://www.ti.com/tool/TIDA-01573 (accessed on 16 January 2025).

- Nissinen, J.; Kostamovaara, J. A high repetition rate CMOS driver for high-energy sub-ns laser pulse generation in SPAD-based time-of-flight range finding. IEEE Sens. J. 2016, 16, 1628–1633. [Google Scholar] [CrossRef]

- Development Trends of Automotive Lidar Laser Technology from an Industry Perspective. Available online: https://www.mems.me/mems/overview_202409/13033.html (accessed on 16 January 2025).

- Oh, W.-S.; Park, K.-Y.; Im, Y.-M.; Kim, H.-K. A 12.5-Gb/s Optical Transmitter Using an Auto-power and -modulation Control. J. Opt. Soc. Korea 2009, 13, 434–438. [Google Scholar] [CrossRef]

- Li, J.; Chon, Y.; Choi, S.; Park, S.-M. A Modified Current-Mode VCSEL Driver for Short-Range LiDAR Sensor Applications in 180 nm CMOS. Photonics 2024, 11, 868. [Google Scholar] [CrossRef]

- Joo, J.-E.; Lee, M.-J.; Park, S.-M. A CMOS Optoelectronic Receiver IC with an On-Chip Avalanche Photodiode for Home-Monitoring LiDAR Sensors. Sensors 2021, 21, 4364. [Google Scholar] [CrossRef] [PubMed]

- Yu, H.; Joo, J.-E.; Zhang, X.; Chon, Y.; Choi, S.; Lee, M.-J.; Park, S.-M. A Current-Mode Optoelectronic Receiver IC for Short-Range LiDAR Sensors in 180 nm CMOS. Photonics 2023, 10, 746. [Google Scholar] [CrossRef]

- Lee, M.-J.; Choi, W.-Y. Effects of Parasitic Resistance on the Performance of Silicon APDs in Standard CMOS Technology. IEEE Electron Device Lett. 2016, 37, 60–63. [Google Scholar] [CrossRef]

- Han, J.; Seo, M.; Lee, D.; Eo, Y. A 20-Gb/s Transformer-Based Current-Mode Optical Receiver in 0.13-μm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 348–352. [Google Scholar]

- Taol, C.; Lei, L.; Chen, Z.; Hong, Z.; Huang, Y. A 50MHz Bandwidth TIA Based on Two Stage Pseudo-Differential OTA with Cascode Negative Resistance and R-C Compensation Technique. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Hiroshima, Japan, 7–10 August 2022. [Google Scholar]

- Häberle, M.; Djekic, D.; Fantner, G.E.; Lips, K.; Ortmanns, M.; Anders, J. An Integrator-Differentiator TIA Using a Multi Element Pseudo-Resistor in its DC Servo Loop for Enhanced Noise Performance. In Proceedings of the IEEE ESSCIRC, Dresden, Germany, 3–6 September 2018. [Google Scholar]

- Royo, G.; Sánchez-Azqueta, C.; Aldea, C.; Celma, S.; Gimeno, C. CMOS transimpedance amplifier with controllable gain for RF overlay. In Proceedings of the 12th Conference on Ph.D. Research in Microelectronics and Electronics, Porto, Portugal, 30 June 2016. [Google Scholar]

- Awny, A.; Nagulapalli, R.; Kroh, M.; Hoffmann, J.; Runge, P.; Micusik, D.; Fischer, G.; Ulusoy, A.C.; Ko, M.; Kissinger, D. A Linear Differential Transimpedance Amplifier for 100-Gb/s Integrated Coherent Optical Fiber Receivers. IEEE Trans. Microw. Theory Tech. 2018, 66, 973–986. [Google Scholar] [CrossRef]

- Tang, W.; Plant, D.V. 3.125Gbit/s Low Power Truly-Differential Parallel Optical Receiver Module in 0.13 μm CMOS. In Proceedings of the 48th Midwest Symposium on Circuits and Systems, Covington, KY, USA, 7–10 August 2005. [Google Scholar]

- Yang, C.; Kee, K.; Lee, S.; Jung, H. Implementation of 10 Gb/s 4-Channel VCSELs Driver Chip for Output Stabilization Based on Time Division Sensing Method. J. Korean Inst. Commun. Inf. Sci. 2015, 40, 1347–1353. [Google Scholar]

- Cho, S.; Oh, J.; Lee, K.-W.; Moon, H. A 4-Channel Multi-Rate VCSEL Driver with Automatic Power, Magnitude Calibration using High-Speed Time-Interleaved Flash-SAR ADC in 0.13 μm CMOS. J. Semicond. Technol. Sci. 2016, 16, 274–286. [Google Scholar] [CrossRef]

- Huang, X.; Gong, D.; Guo, D.; Hou, S.; Huang, G.; Kulis, S.; Liu, C.; Liu, T.; Moreira, P.; Rodríguez, A.S.; et al. A Novel Quad-Channel 10 Gbps CMOS VCSEL Array Driver with Integrated Charge Pumps. J. Instrum. 2020, 15, T12004. [Google Scholar] [CrossRef]

| Parameters | [22] | [23] | [24] | This Work |

|---|---|---|---|---|

| CMOS Process (nm) | 130 | 130 | 65 | 180 |

| Optical Device | VCSEL | VCSEL | VCSEL | VCSEL |

| Architecture | current-mode | current-mode | current-mode | current-mode |

| Signaling Configuration | single-ended | differential | single-ended | single-ended |

| Driver Type | common-cathode | common-anode | common-cathode | common-cathode |

| Supply Voltage (V) | 3.3 | 1.2/3.3 | 3.3 | 3.3 |

| Bias Current (mA) | 5–20 | 5–20 | - | 1 |

| Maximum Modulation Current (mA) | 5–20 | 5–20 | 14 | 10 |

| Max. Power Consumption (mW) | 371 | 471.36 | 376 | 11 |

| APC Implementation | Digital APC with Time Division Sensing | Digital APC with Flash-SAR ADC | Charge Pump with feedback loop | Analog APC with APD feedback |

| APC Range(mA) | 5–20 | 5–20 | - | 0.93–1.42 |

| Chip Area(mm2) | 4.823 | 4.2 | 3 | 0.131 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, Y.; Li, J.; Jung, D.; Choi, S.; Park, S.-M. A CMOS Optoelectronic Transceiver with Concurrent Automatic Power Control for Short-Range LiDAR Sensors. Sensors 2025, 25, 753. https://doi.org/10.3390/s25030753

Choi Y, Li J, Jung D, Choi S, Park S-M. A CMOS Optoelectronic Transceiver with Concurrent Automatic Power Control for Short-Range LiDAR Sensors. Sensors. 2025; 25(3):753. https://doi.org/10.3390/s25030753

Chicago/Turabian StyleChoi, Yejin, Juntong Li, Dukyoo Jung, Seonhan Choi, and Sung-Min Park. 2025. "A CMOS Optoelectronic Transceiver with Concurrent Automatic Power Control for Short-Range LiDAR Sensors" Sensors 25, no. 3: 753. https://doi.org/10.3390/s25030753

APA StyleChoi, Y., Li, J., Jung, D., Choi, S., & Park, S.-M. (2025). A CMOS Optoelectronic Transceiver with Concurrent Automatic Power Control for Short-Range LiDAR Sensors. Sensors, 25(3), 753. https://doi.org/10.3390/s25030753