1. Introduction

Nondestructive Testing (NDT) techniques have become an essential tool widely utilized for structural health monitoring across various critical sectors such as aerospace, railway infrastructure, and energy engineering. Despite numerous existing studies exploring various NDT methodologies, the development of high-voltage power supplies specifically tailored for ultrasonic NDT systems remains relatively limited. Given their critical role in reliably driving piezoelectric transducers, advancements in high-voltage power supply technologies promise significant enhancements in detection sensitivity and operational efficiency [

1]. Consequently, the research to optimize these power supplies is widely recognized as highly valuable and broadly applicable.

Currently, the existing literature addressing push–pull power supply topologies, although numerous, predominantly focuses on traditional analog-based control methods with significant reliance on auxiliary circuits. For instance, previous studies have emphasized improvements in efficiency and output stability through conventional push–pull methods [

2]. However, these systems frequently encounter diverse challenges such as structural complexity, voltage instability, and inefficient asynchronous switching, ultimately restricting their practical deployment in precision-driven NDT contexts. In addition, the reliance on analog control strategies and auxiliary circuits continues to present notable drawbacks, including difficulties in debugging, limited adaptability under dynamic loads, and insufficient real-time monitoring capabilities [

3,

4]. Recent advances in digital power electronics have targeted these issues: Ghalebani et al. (2022) improved push–pull current regulation via digital peak control but lacked multi-channel sensing for NDT’s variable transducer loads [

3]; Pidaparthy et al. (2015) achieved 92% efficiency at 20 kHz with digital push–pull control for LLC converters, yet failed NDT’s < 10 mV ultrasonic noise requirement [

5]; Vivas et al. (2024) optimized high-voltage push–pull modeling but retained analog feedback, slowing response to NDT’s dynamic loads [

6]. Additionally, Cvetanovic et al. (2023) proposed a median-based feedback filtering strategy to suppress switching noise and achieve very high control bandwidths in multi-sampled pulse-width modulated (MS-PWM) systems [

7]. To address these limitations, it is necessary to extend prior research by incorporating digital control techniques to simplify the circuit complexity, enhance the operational stability, and provide much flexibility in handling the diverse load conditions.

In summary, a clear research gap remains in achieving a fully digital, multi-channel push–pull topology with integrated soft-start and protection for NDT. This work fills the gap by introducing a digital PWM-based design that simplifies circuitry, improves adaptability, and ensures reliable high-voltage operation. Therefore, this paper proposes a novel digitally controlled push–pull power supply topology to specifically design for the ultrasonic nondestructive testing applications. The proposed approach employs digital pulse-width modulation (PWM) to control multi-stage metal-oxide-semiconductor field-effect transistors (MOSFETs), integrating adjustable duty-cycle control, real-time multi-channel current feedback, and robust fault protection mechanisms. Experimental validation confirms that this digital approach significantly improves operational stability, reduces noise, and enhances multi-channel coordination, making it particularly suitable for advanced industrial scenarios requiring precise and reliable high-voltage power supplies.

2. Working Phase and Analysis of Current

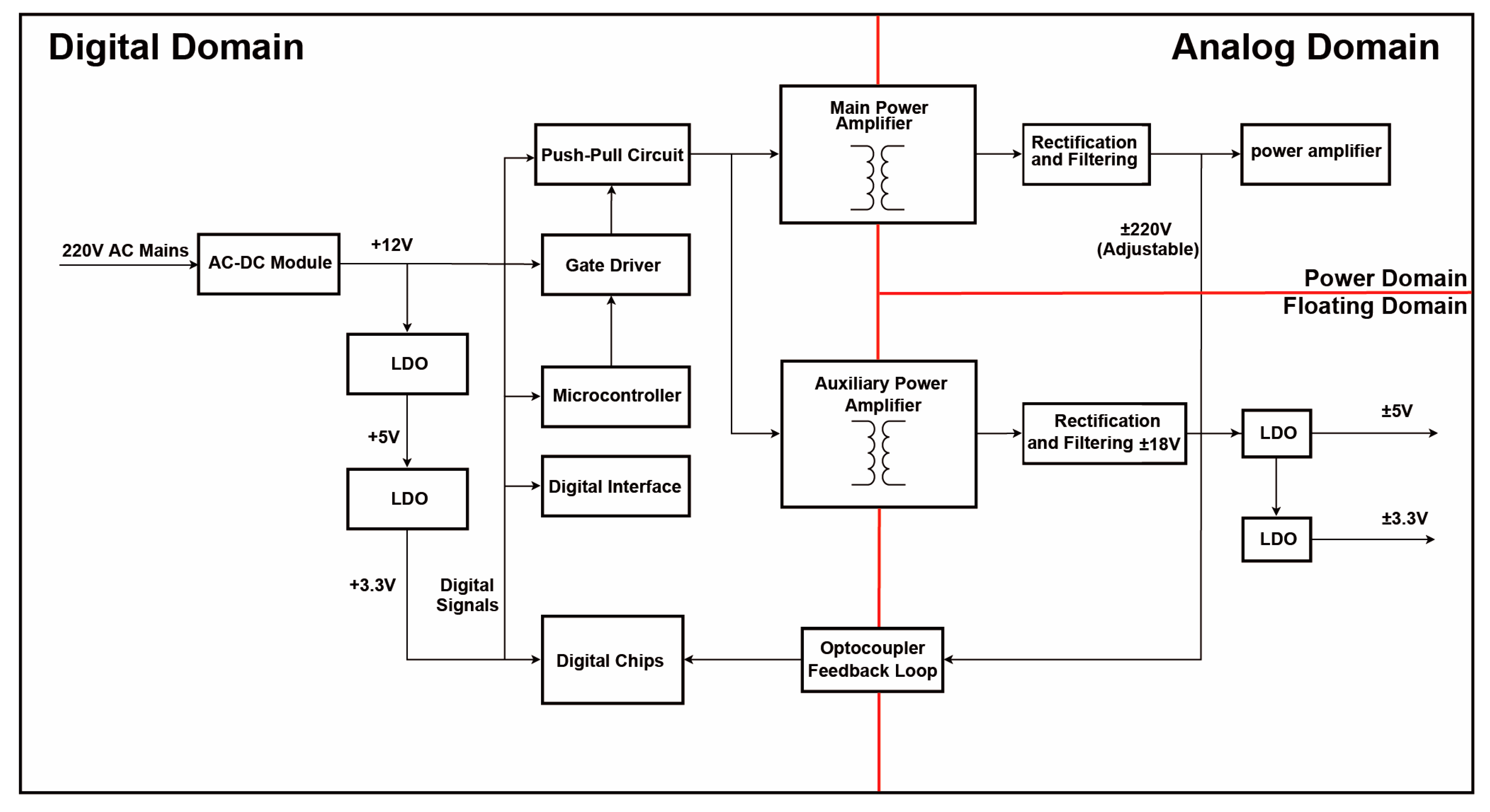

The power supply system is critical in NDT and similar instruments, serving as the energy source for the entire system. As shown in

Figure 1, this study details a power supply system designed for the push–pull drive circuit. The system uses a transformer for electrical isolation, dividing the design into two domains: the digital domain and the analog domain, with the analog domain further split into the power domain and floating domain. The digital domain handles control, signal processing, and data conversion, with a microcontroller generating PWM control signals to regulate system performance. A commercial AC-DC converter transforms the 220 V AC supply to 12 V DC, which powers the PWM signal and is stepped down to 3.3 V via low-dropout (LDO) regulators to supply the microcontroller and digital circuits [

6,

7,

8]. The push–pull drive generates complementary PWM signals to control the transformer and regulate primary power output. The analog domain manages high-precision and real-time tasks like power conversion, filtering, and feedback control. It includes amplification, voltage/current sampling, and feedback circuits, ensuring fast response and low noise. The domain outputs ±220 V and ±18 V to supply the power amplifier and external devices, while isolated ±5 V and ±3.3 V supplies are used within the floating domain to reduce interference between digital and analog components.

The proposed design improves the conventional push–pull power supply topology by integrating the soft-start, push–pull, sampling, and protection circuits via multiple digital control ports [

9,

10,

11]. This allows precise control of the soft-start time, output voltage regulation, and real-time monitoring of current and voltage. Deviations trigger dynamic adjustments or shutdowns, ensuring system stability and safety. The topology, shown in

Figure 2, generates a dual power outputs: a main power supply for high-power components and an auxiliary supply for analog system components [

12,

13]. The transformer’s input terminal is a critical node with high

. For instance, when the upper MOSFET Q2 transitions from ON to OFF while the lower MOSFET Q6 remains OFF, Q2’s drain voltage changes from 0 V to

, and Q6’s drain voltage drops from

to 0 V [

14]. Without a capacitor

between these nodes, the voltage slope

is determined by

, where

is the transformer’s magnetizing current, and

is the parasitic capacitance, including MOSFET and PCB trace capacitances. In step-up transformers, the secondary

amplifies proportionally to the turns ratio (

), significantly increasing noise.

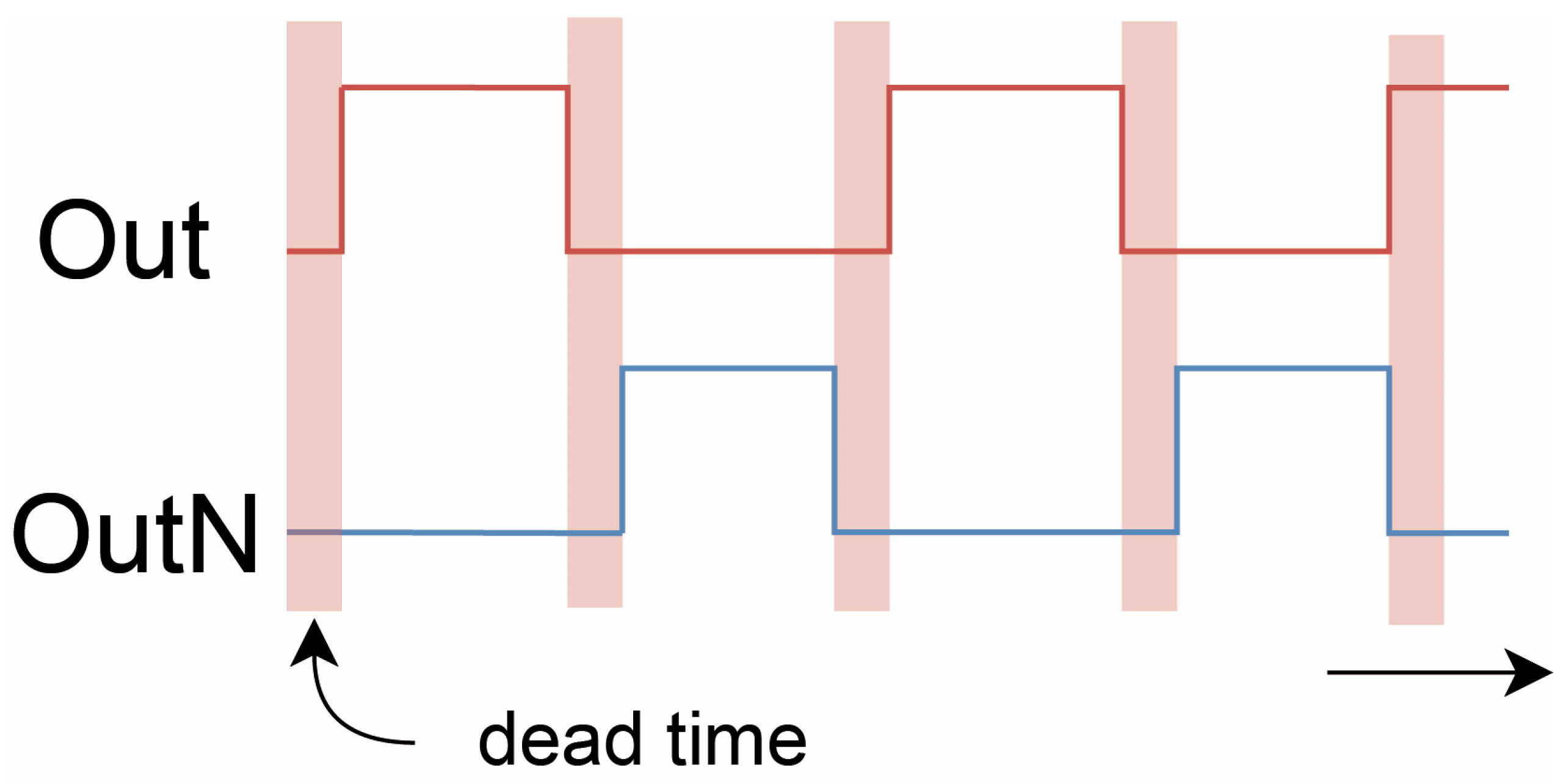

To mitigate this, a capacitor is added between the MOSFET drains to increase node capacitance, replacing the parasitic capacitance and reducing

. The added capacitance slows the voltage transition, lowering noise. During this transition, both MOSFETs remain OFF simultaneously, introducing a necessary dead time, as illustrated in

Figure 3. This approach effectively minimizes the high-frequency noise and stabilizes the circuit. By adjusting the duty cycle D, different output analog voltages can be obtained.

From the perspective of electromagnetic interference (EMI), reducing the slope and carefully controlling dead time are also beneficial for electromagnetic compatibility (EMC). In conventional push–pull circuits, steep voltage transitions often generate high-frequency harmonics that couple into adjacent circuits and degrade the signal-to-noise ratio. The added drain–drain capacitance, combined with digital dead-time adjustment, effectively suppresses these harmonics and minimizes EMI emissions, which is particularly important for nondestructive testing applications requiring low-noise, high-stability operation.

The duty cycle is defined as the ratio of the high-level time

to the total period

The calculation formula is as follows [

15,

16]:

The duty cycle D is influenced by controlling the duration of the dead time in the PWM signal. The relationship between the output voltage

and the duty cycle is as follows [

17]:

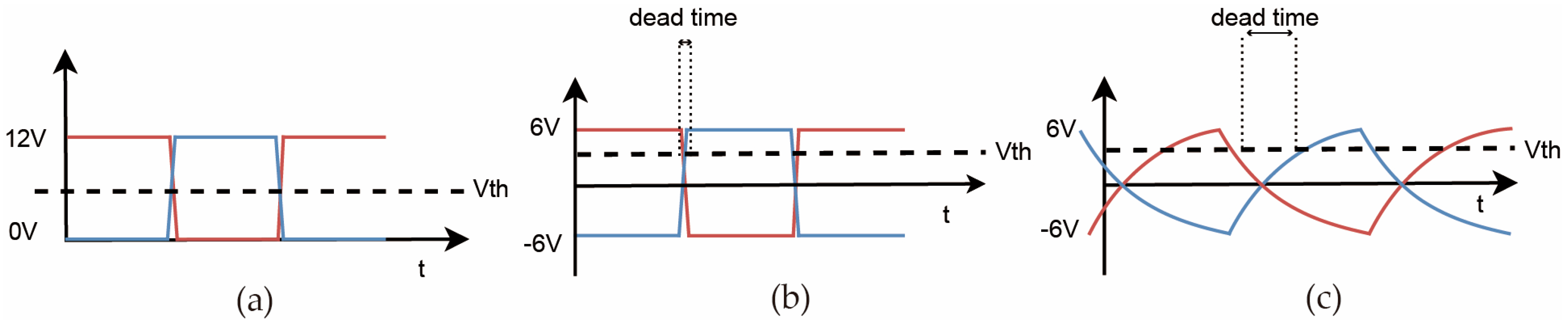

The input voltage , the primary winding turns , and the secondary winding turns define the voltage transformation in the circuit. The gate drive signal originates from the PWM output of a microcontroller configured at 20 kHz with a 5 V high level, 0 V low level, and an adjustable duty cycle from 0% to 50%.

This signal is fed into an integrated gate driver, which amplifies the drive capability, inverts the signal, and converts it to 0 V–12 V, as shown in

Figure 4a. The drive signals are then passed through CR high-pass filters to shift the range to +6 V to −6 V, as shown in

Figure 4b. The inverted signals ensure that when one MOSFET conducts, the other is off, preventing short circuits in the transformer’s primary winding. Low-pass RC filters are then used to increase dead time when the duty cycle approaches 50%, as shown in

Figure 4c, ensuring safe operation. To reduce noise and electromagnetic interference, the design minimizes the

at electrical nodes. High

slopes introduce high-frequency components that can propagate through the system, causing electromagnetic radiation and circuit interference. By optimizing the circuit design, these effects are mitigated, ensuring stable operation.

In the design of the push–pull driver circuit described in this paper, a soft-start circuit based on a PTC (Positive Temperature Coefficient) thermistor is introduced into the power supply system to prevent surge currents during startup, which could cause damage to circuit components or instability in performance. The soft-start circuit effectively limits the startup current by exploiting the temperature-dependent resistance characteristic of the PTC thermistor. As the temperature increases, the resistance rises sharply in the high-temperature range [

18,

19,

20].

The resistance

of the PTC thermistor typically follows the relation:

where

is the base resistance,

is the temperature coefficient, and

is the reference temperature. Near the Curie temperature, the resistance increases sharply and can be described using the following empirical formula:

where

is the Curie temperature, and

is a material constant. During the initial startup phase, the PTC thermistor has a low resistance, and the current is relatively high. The current

varies with time, following Ohm’s law:

where

increases with temperature. Once the circuit reaches a stable state, the current stabilizes, and the PTC thermistor reaches its maximum resistance

:

At this point,

can be expressed as [

21,

22,

23]:

In the push–pull driver circuit design described in this paper, the PTC thermistor is connected in series between MOSFETs Q2 and Q5, and the soft-start circuit is activated by a digital signal to limit the surge current of the high-voltage power amplifier. When the power supply is turned on, the initial resistance of the thermistor is low, resulting in a high current. As the circuit operates, the resistance of the thermistor gradually increases, limiting the current rise [

24,

25,

26]. This design effectively improves system stability and ensures smooth operation of the high-voltage power amplifier in nondestructive testing scenarios.

3. Circuit Design of Digital Push–Pull Drive Power Topology

Figure 2 illustrates the overall topology of the optimized digital-driven push–pull power supply, integrating a soft-start circuit, push–pull circuit, sampling circuit, and protection circuit. This design enhances the classic push–pull switching power supply by addressing voltage instability, noise interference, and dynamic load challenges.

As described in Equation (2), the precise output voltage regulation is achieved by adjusting the PWM duty cycle and the push–pull driver’s switching state. During load variations or changing output demands, the system dynamically adjusts the duty cycle based on real-time current and voltage feedback, maintaining stable output voltage.

Digital control improves duty cycle and dead-time regulation, addressing inefficiencies in traditional push–pull designs. Excessively short dead times can cause transistor overlap and short circuits, while long dead times reduce efficiency. Furthermore, high-frequency switching in conventional circuits increases noise, destabilizing the power supply and interfering with surrounding circuits. To mitigate these issues, real-time sampling and protection mechanisms are implemented, improving dynamic response and overall stability.

The proposed topology features seven MOSFETs, with alternating conduction of Q2 and Q5 enabling efficient voltage conversion. A soft-start circuit (Q3, Q6, Q7) limits inrush current for smooth startup, while a protection circuit (Q1, Q4) rapidly responds to anomalies, enhancing reliability.

Table 1 summarizes the key control circuits and their respective MOSFET states. This design demonstrates superior adaptability, stability, and performance under dynamic industrial conditions.

3.1. Soft-Start Circuit Design

The soft-start circuit is designed to mitigate large current surges during power supply startup. By controlling the duration of the gate voltage applied to MOSFET Q7, the circuit reduces inrush current, thereby protecting the components in the power supply.

Figure 5a shows the implementation of the soft-start circuit. The three curves in

Figure 5a represent the current states at points (1), (2), and (3) in the power supply structure when the gate of MOSFET Q7 receives the soft-start signal. When the gate of Q7 is driven, Q7 turns on, and current flows from VCC to GND as indicated by the current direction (1). At this point, MOSFETs Q3 and Q6 remain off. Due to the push–pull signals, the gates of Q2 and Q5 are activated, causing Q2 and Q5 to conduct. The primary current then flows through the soft-start circuit in current directions (2) and (3), entering the signal sampling module and ultimately flowing to GND to complete the loop.

3.2. Push–Pull Circuit Design

As shown in

Figure 5b, the push–pull circuit employs two PWM square wave signals Push–pull Signal 1 and Push–pull Signal 2—with a phase difference of 180°. By dynamically controlling the duty cycle of these signals, the circuit rapidly alternates the conduction and cutoff times of switching transistors Q2 and Q5, generating an alternating magnetic field that induces the required stable output voltage in the secondary winding.

When the Soft-Start Signal is deactivated, the push–pull circuit begins to generate two complementary square wave signals, with the direction of the current flow illustrated in

Figure 5b. VCC applies a driving voltage to the gates of the field-effect transistors Q3 and Q6 through resistors R7 and R8, causing Q3 and Q6 to conduct. This action shorts the soft-start circuit, rendering it inactive. Subsequently, the signals driven by Push–pull Signal 1 and Push–pull Signal 2 are applied to the gates of Q2 and Q5, causing Q2 and Q5 to conduct. At this point, the current flows in the direction indicated by the arrows in

Figure 5b into the signal sampling module and ultimately to GND, completing the circuit loop.

3.3. Sampling Circuit Design

As shown in

Figure 5c, the sampling circuit is utilized to monitor the primary current and secondary output voltage in real time. By detecting the magnitude of the primary current, the system can determine whether the input current to the transformer is within normal operating ranges. Sampling the secondary output voltage serves a dual purpose: it not only assesses the operational status of the power supply system but also provides feedback to the preceding stage by comparing the actual output voltage with the target voltage. This feedback mechanism enables the control of the push–pull circuit to ensure that the output voltage meets the desired specifications and maintains dynamic stability.

In

Figure 5c, arrows labeled (1) and (2) indicate the directions of the sampled currents during the normal operation of the power supply. When the power supply is activated, the primary current flows into the signal sampling module in the direction indicated by arrow (1). Simultaneously, the secondary voltage passes through the voltage reduction circuit and enters the signal sampling module in the direction shown by arrow (2). The sampling module then feeds this data back to the push–pull circuit and protection circuit to ensure the safety of the primary-side components and verify the normality of the current output.

3.4. Protection Circuit Design

As shown in

Figure 5d, the protection circuit is designed to immediately shut down the power supply when an abnormal condition occurs, ensuring the safety of circuit components and users. In practical applications, when an abnormal output voltage is detected—such as a sudden increase in output voltage due to a short circuit in the backend circuit or a rapid rise in primary input current caused by damage to primary-side components—the signal sampling module feeds this abnormal information back to the preceding stage, triggering the protection signal. Specifically, as illustrated in

Figure 5d, the arrows labeled (1) and (2) indicate the directions of current flow when the protection signal is activated. Upon activation of the protection signal, voltage is applied to the gates of Q1 and Q4, causing them to conduct. Push–pull Signal 1 and Push–pull Signal 2 pass through Schottky diodes D1 and D2, and then through Q1 and Q4 into GND. This action rapidly turns off the MOSFETs Q2 and Q5, cutting off power to the downstream circuit and thereby ensuring the safety of the power supply system.

4. Simulation Results

In order to evaluate the performance of the push–pull driver circuit, computer simulations of the current waveforms generated by the different circuit methods were performed in the LTSPICE (Version 24.1.10) circuit simulation software. The simulation parameters were set as follows: a switching frequency of 20 kHz, an input voltage of 12 V, a desired output voltage of 220 V, a desired output current of 1A, and a transformer primary-to-secondary winding ratio of 0.05:1. The parameters used in the simulation experiments are consistent with those in the actual experiments.

The first set of simulations tested the variation in the PWM duty cycle from 10% to 40% and the corresponding output voltage at a 40% duty cycle. By adjusting the duty cycle, the output voltage can be precisely controlled. The PWM waveforms at duty cycles of 10%, 20%, 30%, and 40% are shown in

Figure 6.

At a duty cycle of 40%, the simulated waveforms of the dual-output voltage are shown in

Figure 7a. The simulation results demonstrate stable output voltages of ±220 V, confirming the circuit’s effectiveness in meeting design specifications. The simulation of the soft-start circuit validated its ability to gradually increase the output voltage during startup and protect the system from inrush current impacts. As shown in

Figure 7b, the simulation results indicate a slow voltage rise, confirming the effectiveness of the soft-start mechanism.

As shown in

Figure 7c, the simulation results of the protection circuit signal control highlight its ability to respond promptly under abnormal conditions, such as output overvoltage or overcurrent. Upon activation of the protection signal, the power system rapidly shuts down, effectively safeguarding the system and its components, thereby demonstrating the robustness and reliability of the protection mechanism.

The simulations clearly demonstrate that duty cycle adjustment enables precise voltage regulation, as shown in

Figure 6. The circuit maintains a stable ±220 V output at maximum duty cycle, as illustrated in

Figure 7a. The soft-start mechanism achieves controlled startup without inrush current, as shown in

Figure 7b. The protection circuit rapidly shuts down abnormal outputs to ensure system safety, as demonstrated in

Figure 7c. These results confirm both stable voltage control and reliable fault protection.

By adjusting the PWM duty cycle, the circuit achieves precise voltage control. The soft-start mechanism ensures safe power-on operation, while the protection circuit provides rapid response under abnormal conditions. These features demonstrate that the proposed topology can effectively, flexibly, and reliably meet the demands for high-voltage, highly stable power supplies in nondestructive testing and other industrial applications.

5. Experimental Result

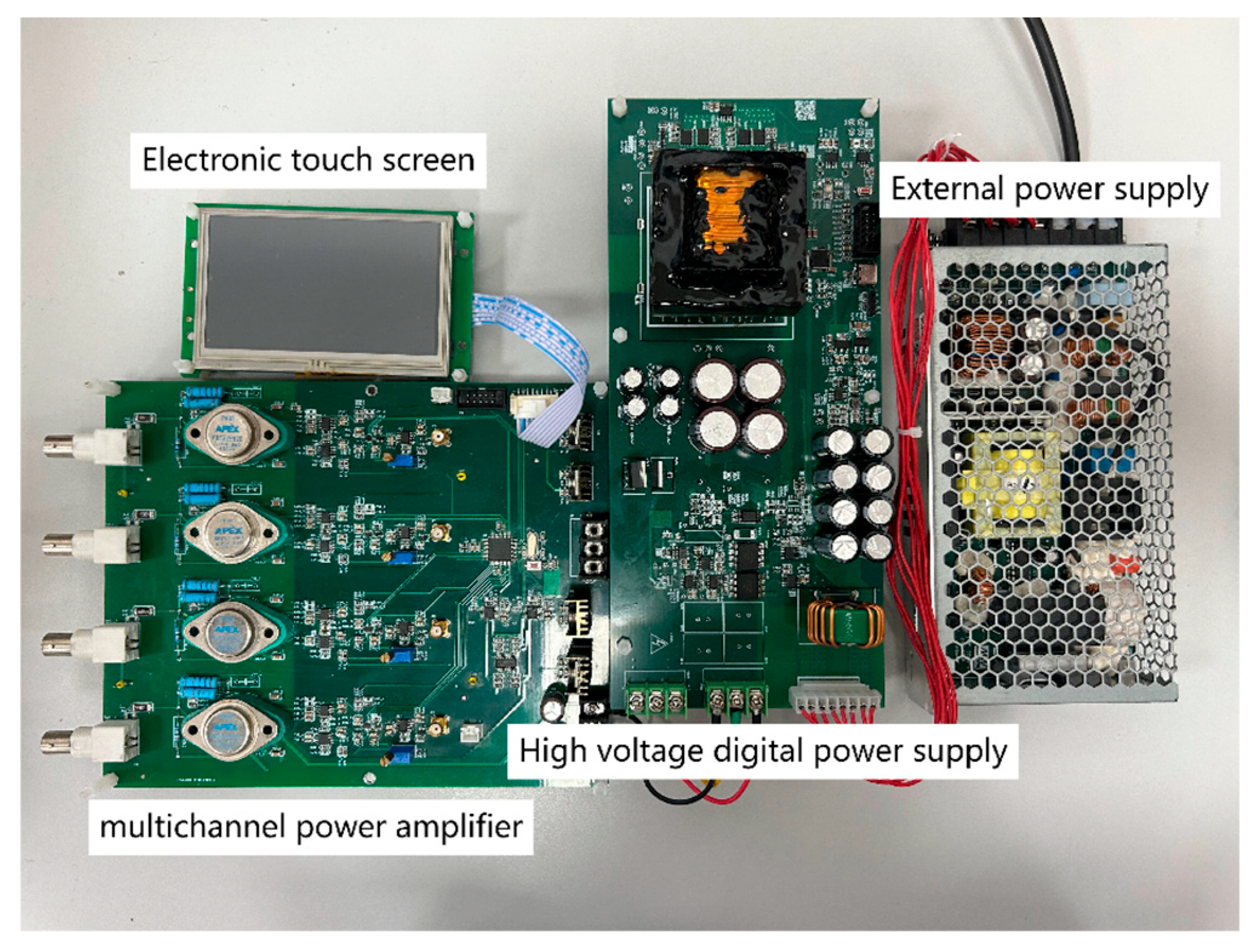

The experiment is carried out to validate the feasibility of the push–pull power circuit topology in practical applications by using a power supply system based on the proposed drive circuit design. The experimental parameters are configured as follows: a switching frequency of 20 kHz, an input voltage of 12 V, a target output voltage of 220 V, a target output current of 1 A, a transformer primary-to-secondary winding ratio of 0.05:1, and a duty cycle range of 0% to 45%. As shown in

Figure 8, the power supply system is designed based on the proposed topology.

The experiment initially evaluated the output waveform of the power system under both no-load and full-load conditions. As shown in

Figure 9a, the output voltage waveform under no-load conditions demonstrates that the power supply maintains a stable output with no significant interference. Further measurements reveal that the no-load noise, as depicted in

Figure 9c, is 5.346 mV, indicating good stability and low noise characteristics under no-load conditions. Under full-load conditions, the output voltage waveform is presented in

Figure 9b. The experimental results indicate that the power supply successfully achieves the target voltage and current outputs while maintaining stable operation. Although the noise level during the experiment was influenced by environmental interference, the results validate the power system’s ability to maintain a stable output. These findings highlight the significance of the experimental validation, confirming that the proposed design not only meets performance specifications but also provides low-noise, stable operation suitable for high-precision applications. With future optimization of power supply design and control strategies, it is expected that the noise amplitude will be further reduced, thereby enhancing the system’s performance and reliability.

Next, using the laboratory’s ultrasonic piezoelectric transducer and aluminum test sample, as shown in

Figure 10a, and the board, as shown in

Figure 10b, the experiment tests whether the power amplifier powered by the push–pull drive circuit designed in this paper can successfully excite the piezoelectric transducer and collect the echo signal via the upper-level computer. A 4 Vpp five-peak waveform was output from the ultrasonic emission test board and amplified by the power amplifier powered by the push–pull drive circuit designed in this study. The result was a 100 Vpp Hanning-windowed signal used for excitation. The amplified excitation signal was applied to the test sample, with the frequency increased from 100 kHz to 500 kHz in separate experiments. Signals were collected at the receiving end using a data acquisition system.

The host computer, designed using LabVIEW software, provides functions including hardware connection control, parameter adjustment, and echo signal acquisition and display. The echo signal images at different frequencies, collected by the host computer, are shown in

Figure 10.

The acquired echo images clearly demonstrate that the system successfully captures distinct five-peak waveforms across the frequency range of 100 kHz to 500 kHz. This indicates that the high-voltage amplifier, designed based on the Digital Push–pull Driver Power Topology, can effectively excite ultrasonic piezoelectric transducers and enable distortion-free echo signal acquisition throughout the entire operational bandwidth. The clarity and consistency of these signals emphasize the quality of the experimental validation, confirming that the proposed topology enables high-fidelity echo acquisition essential for reliable nondestructive testing. These results validate the feasibility and performance stability of the proposed topology. With further optimization of its design parameters and system integration, the Digital Push–pull Driver Power Supply Topology holds great potential for broader applications in radar sensing scenarios, such as short-range penetration detection and target identification, offering significant engineering value and practical applicability.

6. Conclusions

This paper presents a novel digital push–pull driver power supply topology to enhance the efficiency, stability, and adaptability of NDT systems. Traditional push–pull topologies, despite their efficiency, face challenges such as structural complexity, voltage instability under load variations, and limited protection mechanisms, restricting their application in high-precision testing. To address these issues, the proposed design incorporates digitally controlled multi-stage MOSFETs, PWM-driven adjustable duty cycles, real-time current detection, and fault protection for precise voltage regulation and improved reliability.

The topology includes a soft-start circuit to limit inrush currents, a push–pull driver for efficient power conversion, a sampling circuit for real-time monitoring, and a protection circuit for rapid anomaly response. Digital signal control enables flexible voltage adjustment, reduced noise, minimized electromagnetic interference, and enhanced stability under load fluctuations. Simulations and experiments validate its performance, demonstrating a stable ±220 V output at 20 kHz switching frequency, precise duty cycle control, and effective mitigation of abnormal conditions. Practical tests with ultrasonic transducers confirm its capability to drive high-voltage amplifiers for NDT applications across a frequency range of 100 kHz to 500 kHz.

With superior efficiency, adaptability, and reliability compared to conventional designs, the proposed topology is ideal for industrial testing requiring multi-channel operation, stringent power supply for dual-rail amplifiers, and high-precision signal amplification. Future enhancements may extend its applications to radar sensing, power system testing, aerospace security, and advanced manufacturing.