A Star Network of Bipolar Memristive Devices Enables Sensing and Temporal Computing

Abstract

1. Introduction

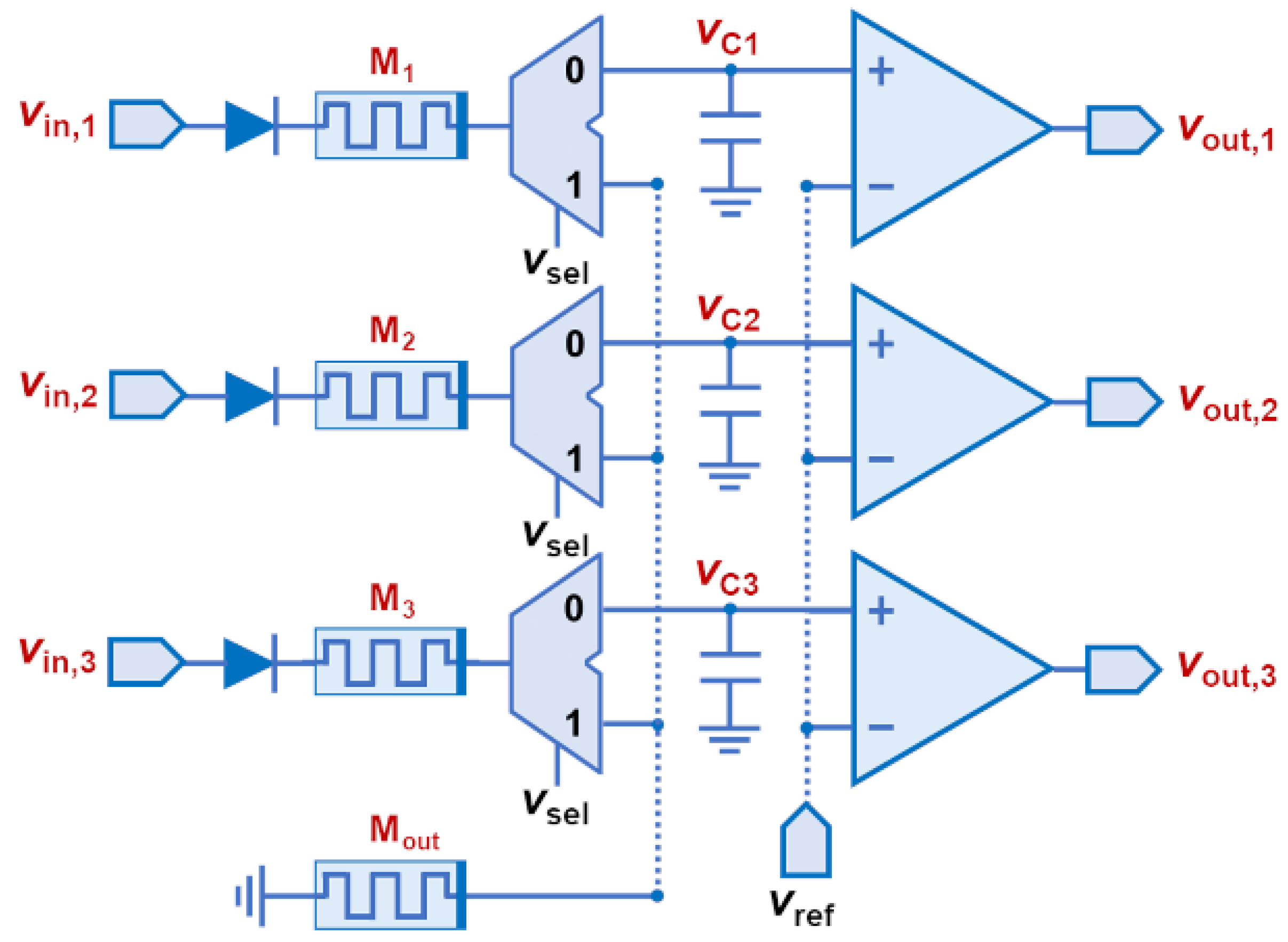

2. The Memristive Star Network Topology

3. Application-Specific Requirements for Memristive Devices

- abrupt SET: The arrival of the first wavefront will cause the conditional activation of the “fuse”. In the extreme case that many wavefronts arrive simultaneously, then the respective input memristive devices will all experience a SET process in parallel. Under these circumstances, the circuit can label the input channel(s) where the wavefront(s) arrived first, with the LRS of the respective memristive devices.

- gradual SET: The arrival of every successive wavefront will initiate a SET process in the corresponding input memristive device. If only one wavefront arrives, its SET process will eventually trigger the “fuse”. However, if more wavefronts arrive at close moments, several input memristive devices can be subjected to a SET process in parallel, before the “fuse” is activated. Under these circumstances, the circuit can capture the recent history of the arriving wavefronts and store such temporal information in the resistance of the input memristive devices using a “rank order” encoding scheme. Different resistive states will be achieved, proportional to the time that elapsed from the moment of arrival of the wavefront until the RESET of Mout. The earlier a wavefront arrives, the lower the resistance of the corresponding memristive device(s).

4. Simulation Results

4.1. The Dynamic Memristive Voltage Divider

4.2. The Memristive Star Network

4.3. A Circuit for Capture and Reproduction of Signal Edges

4.4. Effects of Memristive Device Variability in the Overall Circuit Performance

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lanza, M.; Sebastian, A.; Lu, W.D.; Le Gallo, M.; Chang, M.F.; Akinwande, D.; Puglisi, F.M.; Alshareef, H.N.; Liu, M.; Roldan, J.B. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. Science 2022, 376, eabj9979. [Google Scholar] [CrossRef] [PubMed]

- Chang, T.-C.; Chang, K.C.; Tsai, T.M.; Chu, T.J.; Sze, S.M. Resistance random access memory. Mater. Today 2016, 19, 254–264. [Google Scholar] [CrossRef]

- Pantazi, A.; Woźniak, S.; Tuma, T.; Eleftheriou, E. All-memristive neuromorphic computing with level-tuned neurons. Nanotechnology 2016, 27, 355205. [Google Scholar] [CrossRef] [PubMed]

- Pedretti, G.; Ielmini, D. In-Memory Computing with Resistive Memory Circuits: Status and Outlook. Electronics 2021, 10, 1063. [Google Scholar] [CrossRef]

- Fernandez, C.; Cirera, A.; Vourkas, I. Design Exploration of Threshold Logic in Memory and Experimental Implementation using Knowm Memristors. Int. J. Unconv. Comput. 2023, 18, 249–267. [Google Scholar]

- Lee, S.-J.; Yoo, H.-J. Race Logic Architecture (RALA): A Novel Logic Concept Using the Race Scheme of Input Variables. IEEE J. Solid-State Circuits 2002, 37, 191–201. [Google Scholar]

- Madhavan, A.; Sherwood, T.; Strukov, D. Race Logic: Abusing Hardware Race Conditions to Perform Useful Computation. IEEE Micro 2015, 35, 48–57. [Google Scholar] [CrossRef]

- Smith, J.E. Space-Time Algebra: A Model for Neocortical Computation. In Proceedings of the 2018 ACM/IEEE 45th Annual International Symposium on Computer Architecture (ISCA), Los Angeles, CA, USA, 1–6 June 2018. [Google Scholar]

- Madhavan, A.; Daniels, M.W.; Stiles, M.D. Temporal State Machines: Using Temporal Memory to Stitch Time-based Graph Computations. J. Emerg. Technol. Comput. Syst. 2021, 17, 28. [Google Scholar] [CrossRef] [PubMed]

- Tzimpragos, G.; Volk, J.; Vasudevan, D.; Tsiskaridze, N.; Michelogiannakis, G.; Madhavan, A.; Shalf, J.; Sherwood, T. Temporal Computing with Superconductors. IEEE Micro 2021, 41, 71–79. [Google Scholar] [CrossRef]

- Vakili, H.; Sakib, M.N.; Ganguly, S.; Stan, M.; Daniels, M.W.; Madhavan, A.; Stiles, M.D.; Ghosh, A.W. Temporal Memory with Magnetic Racetracks. IEEE J. Explor. Solid State Comput. Devices Circuits 2020, 6, 107–115. [Google Scholar] [CrossRef]

- Slipko, V.; Pershin, Y. Metastable memristive lines for signal transmission and information processing applications. Phys. Rev. E 2017, 95, 042213. [Google Scholar] [CrossRef] [PubMed]

- Vourkas, I.; Escudero, M.; Sirakoulis, G.C.; Rubio, A. Ubiquitous Memristors In Multi-Level Memory, In-Memory Computing, Data Converters, Clock Generation and Signal Transmission. In Metal Oxides for Non-Volatile Memory, Materials, Technology and Applications; Dimitrakis, P., Valov, I., Tappertzhofen, S., Eds.; Elsevier: Amsterdam, The Netherlands, 2022; pp. 445–463. [Google Scholar]

- Madhavan, A.; Stiles, M.D. Storing and Retrieving Wavefronts with Resistive Temporal Memory. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020. [Google Scholar]

- Vourkas, I.; Sirakoulis, G.C. Networks of Memristors and Memristive Components. In Memristor-Based Nanoelectronic Computing Circuits and Architectures, 1st ed.; Springer International Publishing: Cham, Switzerland, 2016; pp. 173–198. [Google Scholar]

- Pershin, Y.V.; Di Ventra, M. Self-organization and solution of shortest-path optimization problems with memristive networks. Phys. Rev. E 2013, 88, 013305. [Google Scholar] [CrossRef] [PubMed]

- Ju, D.; Ahn, J.; Ho, J.; Kim, S.; Chung, D. Implementation of Physical Reservoir Computing in a TaOx/FTO-Based Memristor Device. Mathematics 2023, 11, 4325. [Google Scholar] [CrossRef]

- Mizrahi, A.; Marsh, T.; Hoskins, B.; Stiles, M.D. Scalable Method to Find the Shortest Path in a Graph with Circuits of Memristors. Phys. Rev. Appl. 2018, 10, 064035. [Google Scholar] [CrossRef]

- Vourkas, I.; Sirakoulis, G.C. Nano-Crossbar Memories Comprising Parallel/Serial Complementary Memristive Switches. BioNanoSci. 2014, 4, 166–179. [Google Scholar] [CrossRef]

- Linn, E.; Rosezin, R.; Kügeler, C.; Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 2010, 9, 403–406. [Google Scholar] [CrossRef] [PubMed]

- Serb, A.; Khiat, A.; Prodromakis, T. Practical demonstration of a RRAM memory fuse. Int. J. Circ. Theor. Appl. 2021, 49, 2363–2372. [Google Scholar] [CrossRef]

- Stathis, D.; Vourkas, I.; Sirakoulis, G.C. Shortest Path Computing Using Memristor-Based Circuits and Cellular Automata. In Cellular Automata: ACRI 2014. Lecture Notes in Computer Science; Wąs, J., Sirakoulis, G.C., Bandini, S., Eds.; Springer: Cham, Switzerland, 2014; Volume 8751, pp. 398–407. [Google Scholar]

- Vourkas, I.; Sirakoulis, G.C. On the Generalization of Composite Memristive Network Structures for Computational Analog/Digital Circuits and Systems. Microelectron. J. 2014, 45, 1380–1391. [Google Scholar] [CrossRef]

- Pershin, Y.; Di Ventra, M. SPICE model of memristive devices with threshold. Radioeng. 2013, 22, 485–489. [Google Scholar]

- Roldán, J.B.; Miranda, E.; Maldonado, D.; Mikhaylov, A.N.; Agudov, N.V.; Dubkov, A.A.; Koryazhkina, M.N.; González, M.B.; Villena, M.A.; Poblador, S.; et al. Variability in Resistive Memories. Adv. Intell. Syst. 2023, 5, 2200338. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Riquelme, J.; Vourkas, I. A Star Network of Bipolar Memristive Devices Enables Sensing and Temporal Computing. Sensors 2024, 24, 512. https://doi.org/10.3390/s24020512

Riquelme J, Vourkas I. A Star Network of Bipolar Memristive Devices Enables Sensing and Temporal Computing. Sensors. 2024; 24(2):512. https://doi.org/10.3390/s24020512

Chicago/Turabian StyleRiquelme, Juan, and Ioannis Vourkas. 2024. "A Star Network of Bipolar Memristive Devices Enables Sensing and Temporal Computing" Sensors 24, no. 2: 512. https://doi.org/10.3390/s24020512

APA StyleRiquelme, J., & Vourkas, I. (2024). A Star Network of Bipolar Memristive Devices Enables Sensing and Temporal Computing. Sensors, 24(2), 512. https://doi.org/10.3390/s24020512