Abstract

Modern applications of Internet of Things (IoT) devices require cheap and effective methods of measurement of physical quantities. Cheap IoT devices with sensor functionalities can detect a lack or excess of substances in everyday life or industry processes. One possible use of tension sensors in IoT applications is the automated replenishment process of fast moving consumer goods (FMCG) on shop shelves or home retail automation that allows for quick ordering of FMCG, where the IoT system is a part of smart packaging. For those reasons, a growing demand for cheap and tiny tension sensors has arisen. In this article, we propose a solution of a small flexible tension sensor fabricated in an amorphous InGaZnO (a-IGZO) thin-film process that can be integrated with other devices, e.g., near-field communications (NFC) or a barcode radio frequency identification (RFID) tag. The sensor was designed to magnify the slight internal changes in material properties caused by mechanical stress. These changes affect the dynamic electrical properties of specially designed inverters for a pair of ring oscillators, in which the frequencies become stress-dependent. In the article, we discuss and explain the approach to the optimum design of a ring oscillator that manifests the highest sensitivity to mechanical stress.

1. Introduction

Existing methods for measuring strain in integrated circuits (ICs) commonly use silicon piezoresistors as sensing elements, thereby, giving rise to a variety of microelectromechanical system (MEMS) solutions [1]. A different, possibly more sensitive method of measuring strain using regular complementary metal oxide semiconductor (CMOS) technology is based on measuring gate-induced drain leakage as a function of strain (denoted as ); however, this method sacrifices linearity while possibly requiring mechanical stress bias, which might be difficult to achieve under a standard technological process [2].

Despite the low cost and relative popularity of the a-IGZO fabrication process, there is limited literature concerning mechanical strain sensors using this technology, whereas most authors investigating a-IGZO properties have focused on the mechanical stress impact on the durability and electrical characteristics [3,4,5,6]. Furthermore, many other methods utilized for sensor manufacturing commonly make use of non-standard materials, such as pressure-sensitive rubber [7], polydimethylsiloxane (PDMS) film [8] or polyvinylidene fluoride-trifluoroethylene (P(VDF-TrFE)) [9], driving up the manufacturing cost.

A similar issue arises when considering nanomaterial-based sensors [10], as these would require significant changes to the fabrication process to integrate them with standard semiconductor technology. A possible alternative could be to use a metal strain gauge, incorporating it as a part of an RFID inlay and bonding it with the IC—this poses separate issues related to miniaturization [11]. The aspect of converting the sensor’s output to a quantity usable in a digital circuit is also usually omitted.

While the strain-dependent resistance or capacitance is easy to measure in a laboratory setting, it requires additional mixed-signal circuitry to incorporate into a larger digital system. An interesting solution to this problem can be found in [12], where the variable mobility of charge carriers affects propagation delay within ring oscillators. This provides a frequency output, which can then be measured using a simple digital counter.

There are several articles in which the authors reported mechanical stress-induced changes of a-IGZO material, though these are presented in terms of changes in the electrical performance of flexible displays, rather than sensors applications. The authors in [13] reported the electrical performance and stability of a-IGZO TFTs on a polyimide substrate for various degrees of mechanical stress. In the article, the authors created variable mechanical stress by changing the bending radius of a device under test. The experiments showed that the mechanical strain increased the sub-gap Density of States (DoS), which, in turn, caused the parameter deterioration of a-IGZO devices [13,14]. Geng et al. in [9] built an a-IGZO piezoelectric sensor; however, their solution required integration with a P(VDF-TrFE)/PZT composite piezo-capacitor. In that solution, the pressure caused by external force changed the top-gate potential, leading to a change in the transistor threshold voltage.

In this article, we propose a practical use of a-IGZO stress-induced parameter deterioration in a stress (tension) sensor. For this purpose, we use a process described in [15] to manufacture a sensor consisting of a pair of specially designed ring oscillators, with each of the oscillators exposed to a different mechanical strain due to the physical construction of the sensor. The chosen process, uses patterned layers of N-type metal-oxide thin-film transistors (TFT) and resistors deposited on a polyimide substrate. The transistors in such a technology manifest a very low leakage current; therefore, they are suitable for low-power applications, such as RFID or memory designs [16].

The technology offers flexible polyimide wafers with four routable metal layers. The other advantages of the process are as follows: the use of conventional processing equipment (adapted to produce flexible polyimide substrate electronics), low mask and wafer production costs in high-volume production. Moreover, the process offers a minimum channel length of and thickness of the whole wafer, whereas the minimum supply voltage is only [15].

The advantages of the flexible IGZO process result in faster design and higher customization capabilities, allowing fitting ICs to exact products and needs. Lower chip thickness and elasticity are also beneficial in the later stages of integration. They give the chip more durability while incorporating it into the inlay and the final product, raising the final production yields.

The rest of the article is organized as follows: Section 2 covers all the issues related to the characterization of mechanical stress influence on electrical parameters, the design of the sensor, and its optimization. In Section 2.1, we describe various test structures used to estimate the stress-induced variability of electrical parameters. Based on these findings, we approximate to what extent the strain affects particular operating regions of N-type metal oxide amorphous semiconductor field effect transistor devices available in the process and propose the strain-sensitive ring oscillator structures in Section 2.2. Section 2.3 covers the electrical macromodel optimization of the proposed sensor, whereas Section 3 shows the circuit frequency measurement results for various strains. The same section explains the difference between the expected and measured circuit sensitivity to strain.

2. Materials and Methods

The implementation of the flexible tension sensor that can be designed in the same process as the microcontroller or an RFID tag requires a suitable flexible substrate TFT-based technology [15,17,18]. Despite the obvious advantages of flexible technologies, such as their low overall production cost [5,19], rapid tapeouts, and flexibility, the flexible substrate TFT-based processes have some major drawbacks that limit their functionality, i.e., a limited number of metallization and interconnection layers, limited carrier mobility, and relatively wide parameter tolerances when compared to standard CMOS monocrystalline processes.

The flexible TFT a-IGZO process that was chosen for the target implementation provides only three fundamental circuit elements, i.e., an N-type metal oxide amorphous semiconductor field effect transistor (NMOS), a resistor, and a metal oxide semiconductor capacitor. Therefore, the design of the discussed sensor was demanding and highly process-dependent. However, the basic underlying assumption was that the sensor should be as simple as possible. It should be implemented with the use of standard cells (logic gates used for other designs in this technology), immune to local process variation, and the output tension-dependent quantity should be easily processed by a logical sequential device (e.g., a microprocessor). For the above reasons, a ring oscillator with a stress-dependent frequency output was chosen as the target design.

2.1. Influence of Mechanical Stress on Electrical Parameters

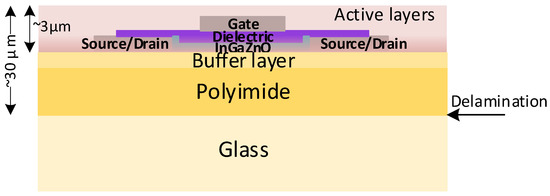

The example cross-section of active layers and a polyimide substrate in the process chosen for a target design is shown in Figure 1.

Figure 1.

Schematic diagram of the IGZO structure stack [13,19,20].

The wafers are manufactured on a glass substrate and delaminated after production. After the delamination, the thickness of the active layers forming the electronic devices is still very small (less than ) in comparison to the thickness of the whole flexible wafer () [15]. In order to investigate the electrical changes, induced by the mechanical stress to the basic parts, such as NMOS transistors, thin-film metal-oxide resistors, and MOS capacitors, we designed and implemented test series for each component type. These results were used to investigate and approximate the stress-induced changes in basic component model parameters.

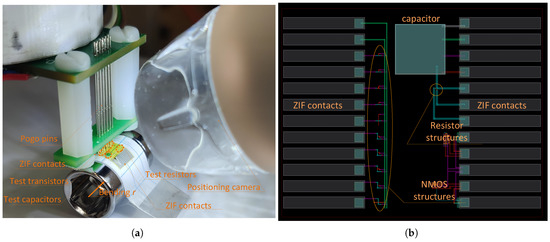

The test structures with basic components were subjected to the mechanical stress (compression) caused by bending on a jig of a particular radius, whereas the electrical connections to the bent wafers were made with the use of either a 12 contact pitch zero insertion force (ZIF) connector or pogo pin contacts as shown in Figure 2a. The layout of the test structure that allowed us to evaluate stress-caused changes in the transfer characteristics of an NMOS, in resistance, and in-MOS capacitance is shown in Figure 2b. It was extremely important to verify the impact of the width- (W) to-length (L) ratio () on the transfer characteristics of mechanically stressed devices.

Figure 2.

Test structure attached to a bending jig (a) and layout of the test structures (top view) (b).

The impact of mechanical stress on the transfer characteristics of NMOS transistors with various ratios can be further used to maximize the whole sensor circuit sensitivity. Therefore, transistors with the following ratios were implemented: (smallest permitted dimensions), , , , and (corresponding sizes given in ) and their transfer characteristics, i.e., were measured both on a flat surface and on the bending jig (cylinder of a certain radius) leading to a compressive strain . Resistance and capacitance measurements were also performed with , resistive tracks and capacitor structures, respectively.

In order to measure NMOS transfer (I–U) characteristics, we used an Agilent 33600A (Agilent Technologies, Santa Clara, CA, USA ) function generator acting as a programmable gate-source voltage source (), whilst the Keysight DSOS604A oscilloscope (Keysight, Santa Rosa, CA, USA) registered the voltage drop on a reference drain resistors, corresponding to the drain current of a flat device and current of the same transistor subjected to a compressive strain .

During the measurements of transfer characteristics (both and ), the voltage varied in the 0– range, whereas the indirectly measured current ranged from for to for at the operating point of , and maximum . Therefore, during all of the measurements, the transistors operated in the saturation region, and the measurements of the transfer characteristics are approximated by Equation (1):

where , is the estimated average carrier (electron) mobility; is the estimated dielectric capacitance (see Figure 1) per unit area of unstressed NMOS transistors (pristine conditions after detaching form the carrier glass); corresponds to a threshold voltage, at which a significant increase of drain ( or ) current is observed; and ranges from 2 to [13,21]. However, in the case of our experiments, the square law, i.e., was functional.

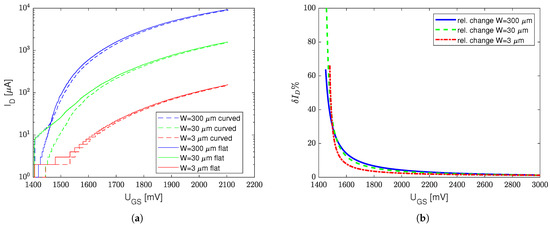

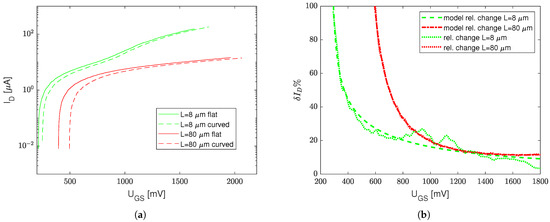

The measurement results approximated with Equation (1) are presented for both mechanically stressed (bent on a diameter cylinder resulting in compressive strain ) and unstressed (flat) transistors with the minimum possible channel length, i.e., , , (see Figure 3a), and the minimum possible channel width, i.e., , (see Figure 4a).

Figure 3.

Transistor transfer characteristics for unstressed and stressed conditions (compressive strain ). Transistors with the minimum channel length (a) and a relative difference of and transfer characteristics (with and without compressive strain) at various (b).

Figure 4.

Transfer characteristics of stressed (compressive strain ) and unstressed transistors with minimum channel width (a) and their relative difference (b) at various .

In order to better understand the stress impact on transfer curves, a relative drain current difference for is shown in Figure 3b and Figure 4b. Two extreme cases were taken into the consideration, i.e., the strain impact for the minimum available transistor length (Figure 3b) and the minimum transistor channel width (Figure 4b).

Due to the local process variation (that randomly affects ) and different ranges of magnitudes of (and ) for high and low ratios, the measurement results of the transfer characteristics are separated between the devices with minimum L (Figure 3a) and minimum W (Figure 4a). However, one can see that mechanical stress affects the transfer characteristics primarily for relatively low voltages.

This results from the different influence of two parameters in Equation (1), i.e., the threshold voltage and (which is mobility dependent) on (and ). The strongest influence on the mechanical stress (compression) is visible when the voltage is close to ; hence, slight variations of (resulting from the mechanical stress) can cause huge fluctuations of . However, when , the mechanical-stress-induced increase is masked at high transconductances, i.e., when .

This phenomenon results from a relatively low linear influence of the drop on the current, opposite to the increase, which, in turn, heavily affects the second order term in Equation (1) when . Table 1 presents and values obtained with various transistor sizes for both the stressed (bent on a 3 mm cylinder) and unstressed conditions.

Table 1.

and threshold voltages of transistors in the pristine state (unstressed) and subjected to mechanical stress (compressive) strain ).

The impact of the stress-induced increase on () is highest for relatively low quiescent points. Regarding the operation of a ring oscillator, acting as a tension sensor, in which the frequency should strongly depend on mechanical stress, the above considerations enforce the operation of transistors slightly above . Moreover, the switching time of a transistor in an oscillator should be at its maximum near the low operating region.

According to Table 1, one can see that, in the case of either low L or low W transistors, is not a linear function of the ratio—this phenomenon is not further analyzed in this paper. Nevertheless, from the sensor design point of view, the most important thing is that the highest stress impact on was observed for high devices. In the case of a stressed transistor of , the relative current drop for was , whereas, in the case of the transistor, this relative current drop reached up to , which was close to the transistor with a drop.

We also investigated the behavior of resistors and capacitors subjected to compressive strain, as investigated previously with transistors. In the case of resistors (see Figure 2b), we observed a relative resistance increase caused by the piezoresistive effect of for a , for a strain and for a strain (). The resistance vs. stress dependence appears to be quite linear; therefore, we exclude any defective effects, such as contact resistance degradation at higher strains.

In the case of the capacitors with a thin dielectric used as the plate separator, we expected low capacitance stress-induced changes resulting only from the material deformation. While bending the capacitor changes its geometric shape, neither the metallization area nor the dielectric width (i.e., the parameters determining the capacitance) change significantly, which leads to the conclusion that the stress-induced capacitance changes cannot be large. For the applied mechanical stresses, the observed effect was predictably small, similar to the change in the dimensions of the structure resulting from the , i.e., the maximum relative decrease of capacitance was , for .

According to the above considerations, one can see that the mechanical compression of the flexible wafer caused the NMOS drain current to drop and the resistance to rise, whereas the capacitors maintained almost constant parameters. Based on these results, we made adjustments to the Cadence SPECTRE environment models of the NMOS, resistor, and capacitor components. In this way, we obtained an appropriate model version with adjusted parameters for the mechanically-stressed devices. Therefore, we were able to optimize the electrical behavior of more sophisticated circuits in two extreme conditions—stressed and unstressed.

2.2. Design of a Ring-Oscillator-Based Sensor

Mechanical compressive stress shifts the voltage towards higher values and slightly decreases due to a slight decrease in the mobility . Similar results were reported in [22], where the authors explained the shift by changes in the Fermi function. In contrast, a change in the electron-lattice interaction explained the mobility changes due to variations in the interatomic distance [22]. Moreover, the authors in [5,6] reported that, under tensile strain, an opposite shift of and the increase in mobility can be observed, which are caused by the rise of the midgap DoS and donor-like and acceptor-like states [23].

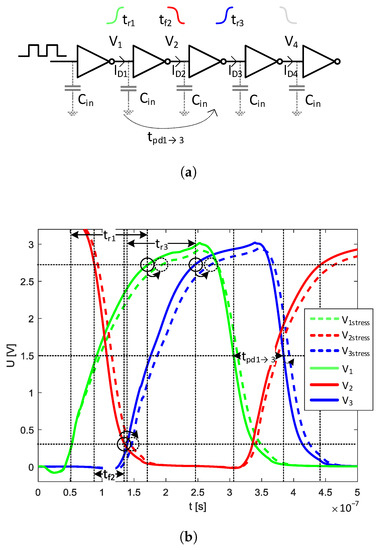

The voltage, drain current, and drain resistance define the static voltage characteristics () and output current characteristics () of logic gates implemented in either pseudo-CMOS or MOS resistor–transistor logic (RTL) [24,25]. Considering the capacitive character of the logical gate input, a change of the drain current or the drain resistance influences the gate’s output slew rate, i.e., in the case of a cascade connection (see Figure 5a).

Figure 5.

Explanation of the mechanical stress influence on and the frequency performance of logical gates: (a) example circuit consisting of a five-stage cascade of inverters and (b) output waveforms at the corresponding inverter stages (appropriate 10%, 50%, and 90% levels are marked on the waveforms, and the example propagation delay between a pair of inverters).

This means that caused by mechanical stress affects the dynamic performance of a logic circuit, changing its output rise and fall times ( and , respectively, as denoted in Figure 5b). These times, in turn, influence the overall propagation delay () of logical gates (or inverters), thereby, affecting the maximum frequency of operation (see Figure 5b). Moreover, the observed stress-induced shift delays the gate turn-on time, leading to even higher .

This phenomena can be used for mechanical stress measurements, where the stress-induced and changes affect the of inverters connected in a ring, leading to a stress-variable frequency of oscillation. Figure 5b also shows an example of the propagation delay () increase between the first and third stage of a cascade formed of inverters with a stress-dependent and .

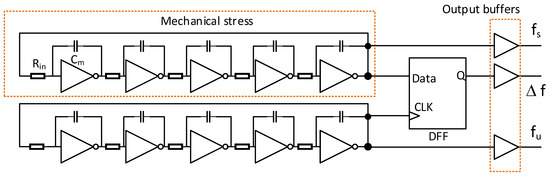

Based on the previous considerations and measurements of electronic circuit elements, we propose a sensor circuit utilizing a pair of identical ring oscillators consisting of logical gates (i.e., inverters) and a frequency mixer built of a D flip-flop (DFF). The block diagram of the device is shown in Figure 6. In the proposed circuit, only one of the ring oscillators is subjected to significant mechanical stress (its frequency is denoted as ), whereas the other oscillator (operating at the frequency) is located on a structure in such a way that the material deformation in its neighborhood can be neglected.

Figure 6.

Block diagram of the sensor circuit.

In this way, the difference (deviation) of generator (ring oscillators) frequencies resulting from stress-induced electrical parameter changes can be observed. In order to obtain a differential frequency at the sensor output, a simple master-slave DFF was implemented, in which a non-zero differential frequency of the ring oscillators causes a time shift between the active (rising) slopes at the data and CLK inputs. This, in turn, leads to periodic changes of the signal at the DFF output. In this way, the DFF acts as a frequency mixer.

The inverters and DFF were implemented in the pseudo-CMOS logic and RTL, which resulted from the lack of PMOS devices in the a-IGZO process [26]. Therefore, the DFF presented in Figure 7a consists of two jamb-latch stages (master and slave) [27] built with low-power RTL inverters. The data transmission between the master and slave stages of the DFF is differential, and both the and output lines are used to reduce the sustain and hold times of the DFF and to keep the energy consumption as low as possible. The DFF output is buffered with a push–pull transistor pair, i.e., and .

Figure 7.

Internal schematics of sensor subcircuits: (a) schematic diagram of the D flip-flop used as a frequency mixer and (b) schematic diagram of the inverters used in the ring oscillator.

Ring oscillator inverters (whose schematic diagram is shown in Figure 7b) were designed to allow adjustment of their small-signal gain (the slope of the transfer characteristics) and their output resistance independently. An additional resistance connected in series with the inverters increases the input charge/discharge time constant, which is -dependent. The proper choice of , and allowed us to maximize the frequency sensitivity (which is the inverse function of ) of the ring-oscillator sensor to the mechanical stress.

The inverters are internally coupled using , in order to obtain the bootstrap effect maximizing the output voltage swing [24]. The external capacitor provides the additional Miller effect. Due to the negative value, the Miller effect occurs, and the capacitance is multiplied at the inverter input. The use of , together with , increases the rise and fall times as well as the overall propagation delay , which, in turn, determines the frequency of the ring oscillators, i.e., , where n corresponds to the odd number of inverters in Figure 6.

The Miller effect is mostly visible when the small signal gain of the transfer characteristics reaches its maximum, i.e., when all the transistors in Figure 7b operate in the pentode region. Therefore, the Miller effect significantly reduces and and, hence, the internal power dissipated by the inverters resulting from charge flow in the internal gate-source , gate-drain , and parasitic capacitances. In this particular design, the number of inverters was , which corresponded to .

2.3. Circuit Analysis and Optimization

In the proposed design, the Miller effect was used not only to reduce the frequency and energy requirements but also to increase the sensor sensitivity to stress-induced parameter changes. The increase of affects , due to its sensitivity to (see Figure 7b) and, on the other hand, decreases the transconductance of . These two factors mainly affect the internal small signal gain of the first stage of inverter (formed of and ), and therefore the gain of the whole inverter becomes strain dependent.

One can see that acts as a voltage follower (whose gain is <1) with a dynamic load formed of ; therefore, their impact on is negligible in the pentode region, giving . The relative stress-induced changes varied from 2% to 100%, whereas can vary up to for a constant (see previous subsection). Therefore, a small signal sensitivity of , i.e., depends mainly on the parameters of ; hence, properly adjusted and with a transistor in a proper region of operation causes the stress-induced changes to dominate over the changes. Summarizing, the dimensions L and W, are crucial for the circuit sensitivity to mechanical stress.

The variable gain also magnifies at the inverter input depending on the strain. The Miller multiplied capacitance, together with , influences the of the inverter. Moreover, the internal output resistance of the inverter, formed by the parallel connection of drain-source (channel) resistances of and , varies with the strain. The higher the compressive strain, the higher the channel resistances (lower transconductances) of and [13], leading to an additional increase in and as well as the resultant propagation delay () of the inverter.

One can see that the total strain impact on the of the inverter is extremely difficult for symbolic analysis. In order to perform an in-depth analysis, it is necessary to obtain the solution to inverter output voltage over the time t for a step pulse at the input. Afterward, an inverse function must be calculated for a given , i.e, , which allows for finding out the relationship for different design variables .

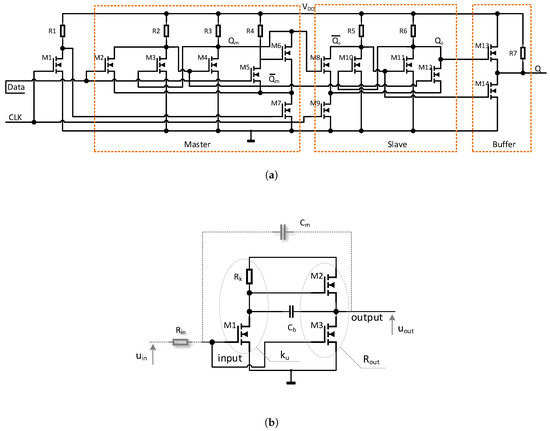

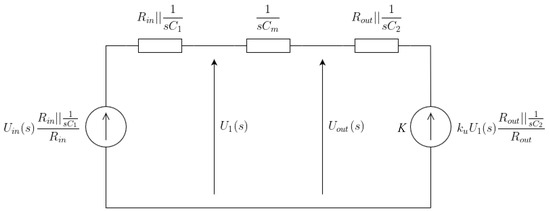

One can see that the dimensions of the inverter design parameter space are too high for a reasonable and intuitive analysis. For this purpose, we conceived a simplified macromodel presented in Figure 8, which corresponds to the inverter in Figure 7b with the reduced parameter space. The voltage-controlled source K and resistance are nonlinear, and both the macromodel circuit parameters and depend on at least three different design variables (, and ) and three different operating regions of (cut-off, triode, and pentode).

Figure 8.

Nonlinear inverter macromodel.

Moreover, the presence of , (corresponding to the physical capacitances of the inverter) and requires describing the circuit with a set of nonlinear differential equations; hence, a simple symbolic solution explaining the influence of over is impossible. Therefore, we performed two methods of analysis in order to determine the optimum parameter set for the maximum sensitivity to the strain. In the first one, we used the Laplace transform of a small signal macromodel appropriate for the pentode region of the circuit presented in Figure 8.

In the second approach, we used the Cadence SPECTRE simulator, which allowed us to obtain nonlinear inverter transfer characteristics (and ), and output characteristics for various . Afterward, we used spline approximations of for K and of the circuit in Figure 8 to build precise look-up tables (LUTs) for both stressed () and unstressed conditions and different values of , and . Such an approach allowed us to reduce the dimensions of the design parameter space in which the analysis and optimization was performed. Therefore, we significantly improved the speed of analysis.

In order to perform the analysis of the circuit in Figure 8 with the Laplace transform, we linearized the circuit and transformed it to a less complex form. This led us to the circuit shown in Figure 9, in which corresponds to a Laplace transform of a Heaviside step function applied at the input, is an auxiliary variable controlling the linearized K source in Figure 8, and is the Laplace transform of the inverter’s step response. For our convenience, the circuit analysis of the input and output response with the Laplace transform was scaled down to up to 1 V, whereas the results obtained with the inverse transform were scaled back to a quite typical voltage response, i.e, 0– V. The above circuit allowed us to derive a Laplace transform of the circuit transmittance (Equation (2)).

Figure 9.

Linearized version of the inverter.

An inverse transform of Equation (2) is troublesome for a direct analysis; however, the complete equation describing step response is available in the Appendix A.1. With the use of , we analyzed and according to the relative parameter changes obtained in Section 2.1. In this way, we were able to perform data screening for various and solve the optimization problem, i.e., , in order to choose the design parameter set, thereby, ensuring the highest inverter sensitivity to the mechanical stress.

The initial (unstressed) parameters taken as the starting points in the macromodel simulation (with the MATLAB Simulink environment) were , , , , and . The small signal gain was within the limits.

The , , and resulted from the physical parameters extracted with Cadence SPECTRE and Mentor Calibre PEX environments for an inverter with typical and sizes of and (see Figure 7b). The and ratios were chosen to obtain gains within the range. The initial value of the capacitor was , which corresponded to a square structure with a thin ZnO dielectric inside.

The initial ensured a previously assumed relatively low operating frequency of the ring oscillators (i.e., ), which allowed for easy measurements of the frequencies with an embedded counter/divider or a spectrum analyzer. In order to maximize the stress-induced influence on transconductance, according to the results presented in Section 2.1, we used the lowest possible ratio (along with a matching ) that still ensured proper switching (noise margins) of the inverter.

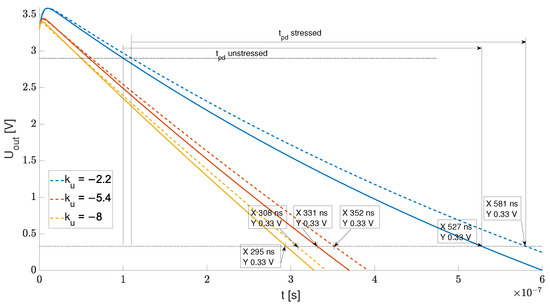

The example results obtained for the set were calculated with both the linear system from Equation (2) and SPECTRE for nominal and stressed sets of parameters (). The results obtained with Equation (2) are shown in Figure 10. Both the nonlinear and linear analysis showed a significant increase of for an inverter with the lowest in comparison to and for and , respectively. One can see that, according to Figure 10, an additional low time constant reduces the slope of for low , which additionally increases the stress impact on . Based on these initial findings, we performed a constrained optimization task, i.e., for both the linear and nonlinear macromodels of the inverter.

Figure 10.

Example step responses and the influence of on for stressed and unstressed devices.

For the purpose of the numerical optimization, we used a MATLAB fmincon function with the interior point algorithm [28]. The macromodel variables subjected to optimization were reduced to a vector of independent design parameters . We assumed that the parameter is constant and solely depends on the dimensions of and , which are set to the minimum allowed process dimensions; therefore, it was eliminated from .

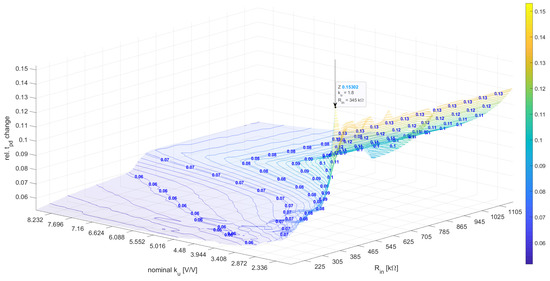

The obtained optimum set for the linear model was , with the value reaching the optimization constraint —, which led to an infeasible solution in which the inverter did not reach the logical zero at the output due to improper noise margins. Figure 11 shows the dependence for the variables and as well as the constant .

Figure 11.

The relative influence for various and for a linear model.

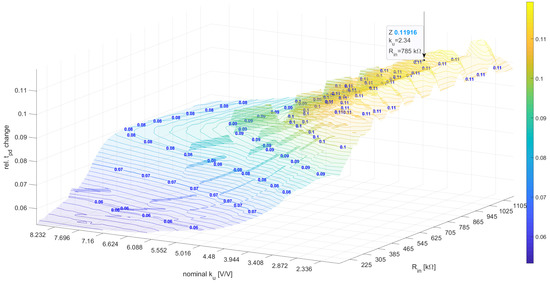

The optimization of for the nonlinear macromodel brought slightly different results, i.e., . In this case, the algorithm did not reach any of the constraints; however, the optimum small signal gain was also low, i.e., . The resistance was more than twice as high compared to the linear macromodel optimization results; however, the objective function had a very small derivative for and the range (see Figure 12).

Figure 12.

The relative influence for various and for a nonlinear model.

The optimization results indicated a nontrivial solution in which the Miller capacitance, together with a low , flatten the step response of the circuit, thereby, leading to a increase. Moreover, a low value near the level enhances the inverter sensitivity to stress-induced fluctuations of and .

According to these outcomes, we fabricated a frequency response sensor with the design parameters corresponding to the results obtained above according to the block diagram in Figure 6. The optimum set of macromodel parameters corresponded to a physical design parameter set, i.e., m, m, m, m, m, m, and m}. We used the maximum that allowed us to obtain the given . In this way, according to results presented in Figure 4b, the highest stress-induced sensitivity is observed.

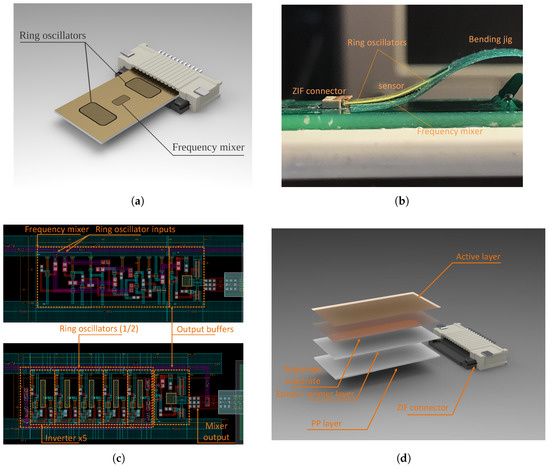

The bottom and side views of the sensor with the corresponding layouts of the DFF and ring oscillators with the optimum physical parameter set (see Figure 13c) are shown in Figure 13a–c. The topology of both ring oscillators is identical; therefore, only a single layout is shown. The output signals of ring oscillators and DFF are buffered by two stages of inverters and attached to the ZIF connector, together with the power supply rails.

Figure 13.

Mechanical assembly mode —SolidWorks bottom view (a), its physical implementation (side view) during tension measurements (b), internal sensor structure layouts (c), and (d) the complete sensor layer stack (bottom view).

The whole sensor structure is long and wide and ends with a Molex 12-contact pitch ZIF connector soldered to a PCB [29], which acts as sensor housing. In order to increase the sensor sensitivity to the bending radius and to ensure a tight fit to the ZIF connector, we added a thick polypropylene (PP) layer, a thick adhesive primer, and an epoxy layer. The whole layer stack of the sensor is shown in Figure 13d. One can see that the active layer is placed at the bottom of the sensor, whereas its buffer layer is stuck to the polypropylene. The ring oscillators are intentionally placed in locations subjected to different strains to ensure a frequency difference resulting from the stress-induced fluctuations.

3. Results

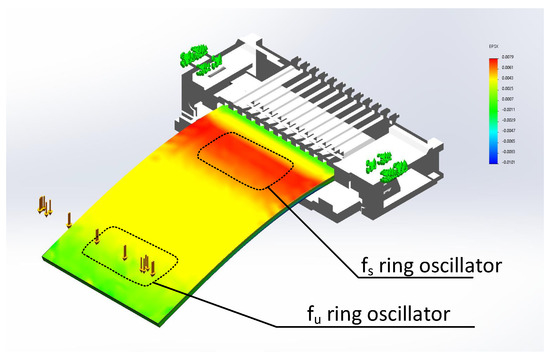

The physical experiment results that are described in this section required applying load forces (F) to the sensor, which resulted in the sensor bending with radii (r), and this varied along the sensor’s length. In this way, an dependence was obtained in the physical proximity of both ( and ) frequency oscillators. For this purpose, we simulated a deflection of the whole multi-layer sensor structure in the SolidWorks 2022 environment. We assumed that the sensor acts as a beam with a single end fixed support, in which a perpendicular point load (F) is applied to the other end. In this way, we were able to obtain the local strain distribution in the sensor.

The distribution of in the sensor is responsible for differences of the inverters’ values of the ring oscillators (see Figure 13a) as previously described in Section 2.1 and Section 2.2. In Figure 14, an example calculated bottom-side strain distribution is shown, in the case of a load applied at the sensor’s end. The example shows that the strain away from the fixing point (ZIF connector) at the active a-IGZO surface of the ring oscillator was , whereas the strain near the other sensor end (where the second ring oscillator is located) was only (over an order of magnitude lower).

The results clearly show that should primarily affect the material properties near the oscillator, whereas the vicinity of the oscillator should remain almost unchanged. The mechanical stress near the oscillator should result in a slight offset in the atomic distance and changes in the energy level splitting of the binding orbitals between the atoms of the semiconductor layer [22].

These changes affect the Fermi function, leading to a transistor shift, which, in turn, changes the transconductances () and, eventually, the inverters’ small signal gain (i.e., ; see the previous section). As discussed in Section 2.3, the small signal gain affects the performance (understood as the propagation delay ) of inverters due to the presence of the Miller effect.

Concerning an obvious relationship describing the ring oscillator frequency of oscillation, i.e., (where the length of the inverter ring in the proposed solution is ), one can see that is a stress-dependent variable. Moreover, the stress-induced variations of interatomic distances influence the electron-lattice interaction and lead to changes in the mobility . Therefore, the compressive strain decreases the electron mobility (as shown in Section 2.1), whereas the tensile strain causes the opposite behavior.

One can see that, according to Equation (1), the drain current is a mobility-dependent variable. Therefore, the final slew rate of each inverter (and , which heavily depends on ; see Figure 5b), rises in cases of tensile stress and decreases for compressive stress. In this way, the depends on (and ). In contrast, remains almost constant since it comes from a circuit that is an order of magnitude less affected by (and therefore almost constant ) leading to a high non-zero as expected.

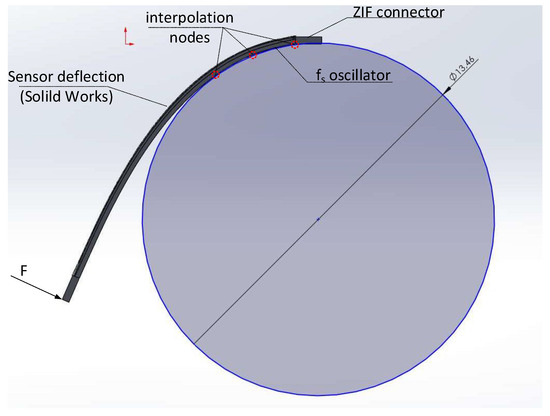

As the strain near the oscillator can be regarded as negligible, and the strain near the oscillator correlates with the and local radius r of curvature near the connector, in the following section of the paper, we focus solely on the local curvature radius near the connector. The example SolidWorks-based simulation and local approximation (with a circle of a matching diameter) of a sensor deflection is depicted in Figure 15.

Figure 15.

Local sensor deflection approximation near the oscillator obtained with finite element analysis.

The use of an additional PP layer increased the strain obtained for the corresponding bending radii r. Therefore, the measurements of the relationship obtained with a physical structure can be more accurate, i.e, higher bending radii were necessary to obtain corresponding to higher . For the purpose of sensor characterization, we applied a bending force at the end of the sensor structures and measured the obtained radii r and . The tensile force caused the bottom layers (i.e., the active layer) to expand; therefore, the decrease in and the increase of was observed.

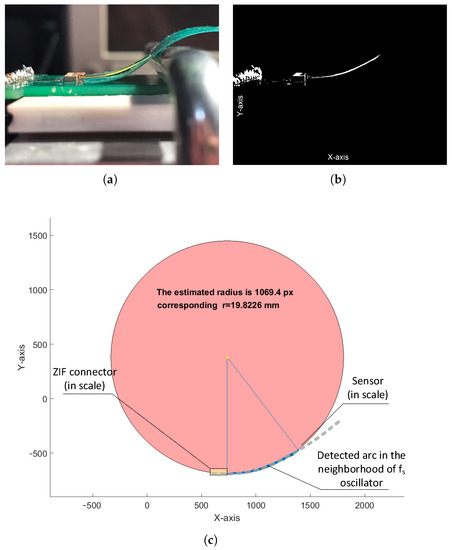

The manufactured physical sensors structures were supplied from a stabilized voltage supply by the ZIF connector, and the average power consumption was . The ring oscillators generated square waves (with and frequencies), which were applied to the DFF mixer. In this way, a periodic signal of frequency(deviation) was measured at the output of the sensor’s mixer circuit. For this purpose, we used a Tektronix MDO3024 oscilloscope with the Fast Fourier Transform (FFT) analysis. In order to provide quick, accurate, and automated r measurements of the sensor arc near the ZIF connector, we used a picture analysis (edge detection) algorithm of the sensor test bench (Figure 16a shows the test bench).

Figure 16.

Arc detection algorithm (image processing) used in the radius estimation: test bench (a), picture after the edge detection (b), and (c) automated circle approximation (the sensor and ZIF connector are also marked in scale for greater readability).

Therefore, during each measurement, we captured the shape of the bent sensor (arc) in proximity of the ZIF connector with a camera (Figure 16b shows the results of the edge-detection algorithm) instead of bending the sensor with cylinders of a reference radii, which was troublesome due to the ZIF connector housing. This approach increased both the accuracy and speed of the measurements. In order to calculate the arc radius, we used the least squares algorithm that approximated the detected arc of a bent sensor with a circle (Figure 16c shows the example results of automated circle fitting in the MATLAB environment). In the automated arc approximation algorithm, we used the arc shape placed closer to the ZIF connector, since the curvature of the bent sensor changes with the distance from the fixing point.

We measured r and for 10 sensor structures that came from the same wafer. First, we tested the sensors for six different bending radii, i.e, 7.5, 13, 16, 20, 23, and 29 mm . Second, we estimated their maximum strains with the SolidWorks environment for corresponding r, from the ZIF connector where the ring oscillator is located. The maximum calculated strains for corresponding were 0.0086, 0.0055, 0.004, 0.0033, 0.0029, 0.0021 . To validate the results obtained with the image processing algorithm, we also propped up the circuit with a dynamometer gauge arm to measure the mechanical force exerted perpendicularly to the circuit surface.

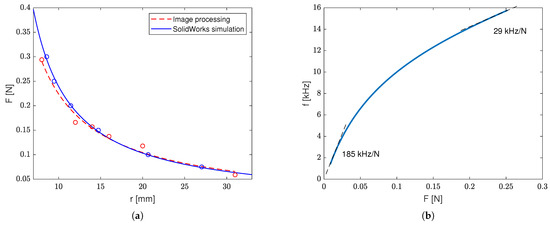

Figure 17a shows the relationship between the applied force and the resulting radii obtained via image processing compared with the same relationship taken from the SolidWorks simulation. After running a static simulation study for each force, the local radius of curvature near the oscillator was obtained by finding a circle passing through three points near the connector in each of the deflected Finite Element Analysis (FEA) meshes (see Figure 15).

Figure 17.

Sensor characterization results: (a) comparison of relationships obtained with SolidWorks and the physical measurements and (b) the output characteristic function of the sensor.

One can see that the image-processing-based estimation gave results that are close to these obtained with SolidWorks. With the use of empirical relationships of (presented in Figure 18a) and (based on both numerical estimates and physical measurements), we were able to estimate the sensor output characteristic function, i.e., , which is shown in Figure 17b. This function allowed us later to estimate such crucial sensor parameters as sensitivity, the limit of detection (LoD), and the limit of quantification (LoQ).

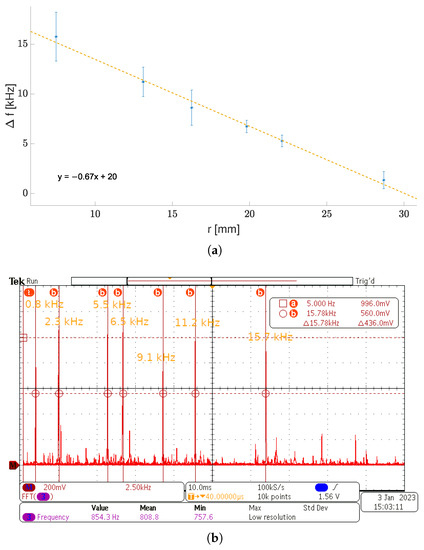

Figure 18.

Frequency measurements of a physical sensor structure, output frequency vs. bending radius (a) and (b) the frequency–domain response of the sensor for variable radius.

The frequency measurement results are presented in Figure 18a, in which each point corresponds to an average value coming from multiple measurements of various sensor specimens. The values were obtained with the spectrum analysis based on the FFT of the differential signal at the frequency mixer (DFF) output. Figure 18b shows an overlay of some of the measured oscillation peaks in the frequency domain (spectrum analysis of the signal from the DFF mixer) with their frequencies rising along with a decreasing r.

It is worth mentioning that the maximum and minimum frequencies (before mixing) were 91 and , respectively, whereas remained almost unchanged (). The and difference (), when no mechanical stress was applied, resulted from the local circuit mismatch. However, during measurements, this difference did not exceed . The uncertainty bounds in the picture show the minimum and maximum values obtained for each sensor specimen and its bending r. The linear approximation of dependence yielded an average sensitivity coefficient; however, a saturation was observable at low r.

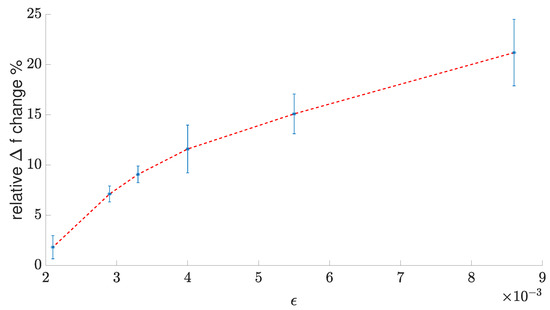

The saturation effect at low r (high ) is clearly visible on the relative frequency deviation plot, i.e., , which is shown in Figure 19.

Figure 19.

Relative frequency deviation vs. strain.

One can see that the initial sensitivity of the relative frequency deviation at low is almost three-times higher than for . The frequency deviation for relatively low is mainly caused by the and fluctuations near its nominal values for the unstressed material. The deviation saturation for higher likely results from the maximum available mobility of the material for a certain interface trap density, which, in turn, depends highly on the mechanical strain [13].

In the proposed structure, the strain resulting from the applied force F causes the opposite parameter change to the one described in Section 2.1. In the setup discussed in Section 2 we investigated the transistor parameter fluctuation resulting from the material compression, whereas, in this case, the tensile forced was applied to resistors and transistors forming the ring oscillators. The saturation of electron mobility for higher strains decreased the strain-induced impact of , thereby, decreasing the sensor’s sensitivity for high . Therefore, the sensor characteristic curve, i.e., , is a nonlinear function of force F, and thus the sensor manifests different sensitivities in different ranges of operation.

The higher strains, i.e., sometimes caused permanent degradation effects on a few sensors. Such effects resulted in a sudden and permanent frequency drop or output signal deterioration, e.g., aperiodic responses of the ring oscillators. This behavior may result from contact resistance degradation by the local delamination or the increase in the access resistance resulting from the defect formation. An additional explanation for this phenomenon may result from the formation of cracks in the material [30]. Strain applied in parallel to the source-drain current path (i.e., the channel of the NMOS transistors) may cause severe degradation when .

The degradation occurs as cracks in the transistor channel cause a bottleneck effect on the flow of electrical current [30]. Therefore, for high strains, damage formation limits the current leading to saturation of the stress-induced (and ) increase. Moreover, hysteresis effects may appear for , as not all the cracks will disappear after re-flattening the sensor (i.e., applying ). For this reason, we assumed that the maximum acceptable and repeatable that does not affect the material degradation is less than , which, in the case of our sensor, corresponds to and a 7.5 mm bending radius. The occurrence of this effect defined an obvious bound for the measurement range of our sensor.

Based on the measurements of the bending radii (r), force (F), and SolidWorks strain estimates (presented in Figure 17a, Figure 18a, and Figure 19), we were able to obtain the output characteristic curve of the sensor (presented in Figure 17b) and performance measures, such as the accuracy (), precision (), sensitivity (), resolution (), limit of detection (), and limit of quantification (). Accuracy measurements were based on the inverse function of the sensor characteristic curve, the physical bending force measurements, and corresponding frequencies. In this way, the differences between the physically applied force F and its estimates were found. The estimated accuracy was , whereas the precision (based on the scatter of measured values) was .

The proposed sensor, despite its digital design, utilizes fully analog phenomena. The sensor’s output quantity (frequency deviation ) is a result of a relative position of rising slopes of square wave signals from the and ring oscillators. Therefore, is a continuous variable, and the sensor can be considered an analog sensor. For this reason, in order to estimate the sensor resolution, it was necessary to estimate the sensor noise, resulting from the momentary fluctuations and measurement range.

Considering the measured standard deviation, i.e., , and the sensor measurement range, i.e., , the resultant resolution was . The sensor characteristic transfer curve is nonlinear; therefore, its sensitivity varies with the slope. The minimum sensitivity was , whereas the maximum sensitivity was . Both the limit of detection and quantification were estimated by using the calibration curve S method. In this method, based on the standard deviation of the output quantity, i.e., , the y-axis intercept points at the calibration curve were found for (in the case of ) and (in the case of ) as well as their corresponding measured quantity values (i.e., F). Based on this method, the estimated and were and , respectively, allowing us to estimate the minimum of the proposed sensor’s range.

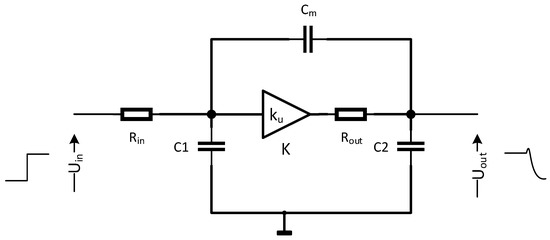

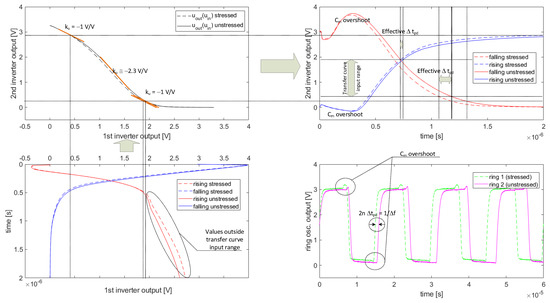

The other important observation during the measurements was that, despite the relatively high sensitivity of the device to mechanical stress, the initial relative frequency deviation for low strains, i.e., , was below expectation (≈2%) when compared to values of the optimization criterion denoted in Section 2.3 as . Due to the voltage shift of the inverter transfer curve towards low input voltages, the inverters were immune to excessively long rising slopes and more vulnerable to falling ones. The diagram presented in Figure 20 explains the mechanism of so-called flattening for edges of a certain type in subsequent inverters of a ring.

Figure 20.

masking mechanism.

The edges of the first inverter output waveforms (intentionally rotated clockwise at the bottom-left part of Figure 20) are passed to the transfer curve of the second inverter (see Figure 6). One can see that the highest differences between the stressed and unstressed cases are visible for the rising slope. These differences are mostly visible for low voltages of the M2 voltage follower (see Figure 7b), which manifests low transconductance in this region of operation. The higher sensitivity to for low transconductances was previously discussed in Section 2.1.

Moreover, low transconductance (resulting in high of M2) reduces the speed of charging, which additionally decreases the output slew rate (see both rising slopes in the bottom-left waveform of Figure 20). Unfortunately, the majority of this low region, where a high sensitivity to stress is observed, is masked by a low (see the top-left transfer curve of the diagram in Figure 20) because this particular region is mainly situated outside the active input range of the transfer curve.

Nevertheless, despite the described flattening effect, one can see that the resultant response of the second inverter manifests high . Unfortunately, in the case of the falling edge at the first inverter output, a high transconductance (caused by its high ) masks the stress impact on the falling edge.

This falling edge passed to the transfer curve of the consecutive inverter turns into the rising edge, which manifests a slight sensitivity—mainly due to the transfer curve shift caused by the stress-induced shift (see the top-left side of the diagram in Figure 20). One can see that, despite the high influence of stress on falling/rising slopes near the asymptotic values (0 and ), the effective (within nonzero bounds) is smaller.

We also experimentally verified the influence of small signal gain and the Miller effect on the sensitivity of the sensor. For this purpose, we fabricated six different sensor versions with/without the Miller capacitor and three combinations of small signal gains . We measured the relative frequency deviation for (), which is one of the measurement points depicted in Figure 18a and Figure 19. The relative frequency deviations for various design parameter combinations are listed in Table 2.

Table 2.

Comparison of relative frequency deviations for optimum and non-optimum sets of inverter parameters both with and without the Miller capacitor for ().

One can see that physical measurements listed in Table 2 confirm the results obtained with macromodels, and the Miller effect improves the circuit performance, whereas the circuit with yields the highest sensitivity.

4. Discussion and Conclusions

In the paper, we discussed the design and optimization of the a-IGZO stress sensor. For optimization purposes, we derived linear and nonlinear macromodels of inverters comprising the crucial part of the sensor. Both macromodels yielded similar results, showing that circuits with low gain and additional Miller effect bring the best sensitivity to electrical changes induced by mechanical stress. Over the whole measured range, i.e., for an unstressed sensor up to strain (corresponding to a 7.5 mm bending radius), the physical sensor structure exhibited a frequency deviation (i.e., ) in the output signal.

For the sensor characterization, we used an image processing algorithm that automatically calculated the arc radius of the device under test. The sensor is of a differential structure, which makes it immune to power supply and temperature variations. Its digital output facilitates further integration with digital blocks contained within the same system. Moreover, it does not require sophisticated analog subcircuits for signal conditioning, whereas the measured quantity (strain or force) corresponds to a digital signal frequency.

One of the disadvantages of the proposed design is the initial differential offset frequency for a sensor with no mechanical stress applied. This nonzero offset results from the local mismatches and, during measurements, did not exceed , thus, corresponding to a error of the average output frequency for a non-stressed device. Such an inconvenience can be easily removed by an offset reset applied by a microcontroller device during circuit warm-up. The other drawback may result from the flexible nature itself, i.e., elasticity in smart packaging, where the whole product and its packaging are susceptible to deformation. In such a case, the packaging would likely have to be designed from the ground up with the sensor in mind.

However, flexible packaging constitutes a tiny part of the smart packaging market. There might be another niche for goods that are sensitive to deformation while at the same time being infeasible to store in rigid containers. The main advantages of the proposed sensor are its high sensitivity () and resolution () resulting from the nonlinear strain vs. material mobility relationship, with a low power consumption of maintained during a measurement.

Some hysteresis is to be expected for due to the formation of cracks in the material; however, it proved difficult to quantify using our measurement methods for within the sensor’s measurement range. Moreover, the stand-alone sensor (without the ZIF connector) can be considered as a 5 × 0.2 mm stripe, which, in a volume production, can cost less than half of a cent in USD. However, only about of this sensor area would be used by the sensor layout. Considering the sensor as a part of a larger device (C, RFID tag, etc.), the sensor footprint itself would cost around 3/100th of a cent.

Author Contributions

Conceptualization, electrical designs, final measurements, writing, draft preparation: P.Z.W.; software, data analysis, writing: K.S.; layout, optimization and production: K.G.; preliminary measurements, mechanical stress measurements: M.R.; production arrangements: M.P. All authors have read and agreed to the published verion of the manuscript.

Funding

This research was funded by the National Center for Research and Development grant number POIR.01.01.01-00-0908/19, Warsaw University of Technology Institute of Electronic Systems, and Talkin’ Things.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The data that support the findings of this study are available from the corresponding author, upon a reasonable request. Some data, concerning the technical details of the semiconductor technology used, may be subject to intellectual property restrictions..

Conflicts of Interest

The authors declare no conflict of interest.

Appendix A

Appendix A.1. Step Response of the Inverter

References

- Barlian, A.A.; Park, W.T.; Mallon, J.R.; Rastegar, A.J.; Pruitt, B.L. Review: Semiconductor Piezoresistance for Microsystems. Proc. IEEE 2009, 97, 513–552. [Google Scholar] [CrossRef] [PubMed]

- Lau, W.; Yang, P.; Siah, S.; Chan, L. The role of a tensile stress bias for a sensitive silicon mechanical stress sensor based on a change in gate-induced-drain leakage current. Microelectron. Reliab. 2012, 52, 2847–2850. [Google Scholar] [CrossRef]

- Song, J.; Huang, X.; Han, C.; Yu, Y.; Su, Y.; Lai, P. Recent Developments of Flexible InGaZnO Thin-Film Transistors. Phys. Status Solidi A 2021, 218, 2000527. [Google Scholar] [CrossRef]

- Seo, Y.; Jeong, H.S.; Jeong, H.Y.; Park, S.; Jang, J.T.; Choi, S.; Kim, D.M.; Choi, S.J.; Jin, X.; Kwon, H.I.; et al. Effect of Simultaneous Mechanical and Electrical Stress on the Electrical Performance of Flexible In-Ga-Zn-O Thin-Film Transistors. Materials 2019, 12, 3248. [Google Scholar] [CrossRef] [PubMed]

- Billah, M.M.; Hasan, M.M.; Jang, J. Millisecond Stretched Exponential Recovery of Threshold Voltage for Mechanically Stressed Flexible a-IGZO Thin-Film Transistors. IEEE Electron Device Lett. 2018, 39, 699–702. [Google Scholar] [CrossRef]

- Billah, M.M.; Hasan, M.M.; Jang, J. Effect of Tensile and Compressive Bending Stress on Electrical Performance of Flexible a-IGZO TFTs. IEEE Electron Device Lett. 2017, 38, 890–893. [Google Scholar] [CrossRef]

- Park, I.J.; Jeong, C.Y.; Cho, I.T.; Lee, J.H.; Cho, E.S.; Kwon, S.J.; Kim, B.; Cheong, W.S.; Song, S.H.; Kwon, H.I. Fabrication of amorphous InGaZnO thin-film transistor-driven flexible thermal and pressure sensors. Semicond. Sci. Technol. 2012, 27, 105019. [Google Scholar] [CrossRef]

- Xin, C.; Chen, L.; Li, T.; Zhang, Z.; Zhao, T.; Li, X.; Zhang, J. Highly Sensitive Flexible Pressure Sensor by the Integration of Microstructured PDMS Film With a-IGZO TFTs. IEEE Electron Device Lett. 2018, 39, 1073–1076. [Google Scholar] [CrossRef]

- Geng, D.; Han, S.; Seo, H.; Mativenga, M.; Jang, J. Piezoelectric Pressure Sensing Device Using Top-Gate Effect of Dual-Gate a-IGZO TFT. IEEE Sens. J. 2017, 17, 585–586. [Google Scholar] [CrossRef]

- Qiu, A.; Li, P.; Yang, Z.; Yao, Y.; Lee, I.; Ma, J. A Path Beyond Metal and Silicon:Polymer/Nanomaterial Composites for Stretchable Strain Sensors. Adv. Funct. Mater. 2019, 29, 1806306. [Google Scholar] [CrossRef]

- Zhang, J.X.J.; Hoshino, K. Mechanical transducers: Cantilevers, acoustic wave sensors, and thermal sensors. Mol. Sensors Nanodevices 2019, 311–412. [Google Scholar] [CrossRef]

- Schörner, R.; Poppinger, M.; Eibl, J. Silicon pressure sensor with frequency output. Sens. Actuators A Phys. 1990, 21, 73–78. [Google Scholar] [CrossRef]

- Jeong, H.J.; Han, K.L.; Ok, K.C.; Lee, H.M.; Oh, S.; Park, J.S. Effect of mechanical stress on the stability of flexible InGaZnO thin-film transistors. J. Inf. Disp. 2017, 18, 87–91. [Google Scholar] [CrossRef]

- Hsieh, H.H.; Kamiya, T.; Nomura, K.; Hosono, H.; Wu, C.C. P-29: Modeling of Amorphous Oxide Semiconductor Thin Film Transistors and Subgap Density of States. SID Symp. Dig. Tech. Pap. 2008, 39, 1277. [Google Scholar] [CrossRef]

- Biggs, J.; Myers, J.; Kufel, J.; Ozer, E.; Craske, S.; Sou, A.; Ramsdale, C.; Williamson, K.; Price, R.; White, S. A natively flexible 32-bit Arm microprocessor. Nature 2021, 595, 532–536. [Google Scholar] [CrossRef]

- Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 2018, 1, 30–39. [Google Scholar] [CrossRef]

- Dembo, H.; Kurokawa, Y.; Ikeda, T.; Iwata, S.; Ohshima, K.; Ishii, J.; Tsurume, T.; Sugiyama, E.; Yamada, D.; Isobe, A.; et al. RFCPUs on glass and plastic substrates fabricated by TFT transfer technology. In Proceedings of the IEEE InternationalElectron Devices Meeting, 2005—IEDM Technical Digest, Washington, DC, USA, 5 December 2005; IEEE: New York, NY, USA, 2005. [Google Scholar] [CrossRef]

- Takayama, T.; Ohno, Y.; Goto, Y.; Machida, A.; Fujita, M.; Maruyama, J.; Kato, K.; Koyama, J.; Yamazaki, S. A CPU on a plastic film substrate. In Digest of Technical Papers, Proceedings of the 2004 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2004; IEEE: New York, NY, USA, 2005. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef]

- Zhang, L.; Yu, H.; Xiao, W.; Liu, C.; Chen, J.; Guo, M.; Gao, H.; Liu, B.; Wu, W. Strategies for Applications of Oxide-Based Thin Film Transistors. Electronics 2022, 11, 960. [Google Scholar] [CrossRef]

- Nathan, A.; Kumar, A.; Sakariya, K.; Servati, P.; Sambandan, S.; Striakhilev, D. Amorphous silicon thin film transistor circuit integration for organic LED displays on glass and plastic. IEEE J. Solid-State Circuits 2004, 39, 1477–1486. [Google Scholar] [CrossRef]

- Münzenrieder, N.S.; Cherenack, K.H.; Tröster, G. Testing of flexible InGaZnO-based thin-film transistors under mechanical strain. Eur. Phys. J. Appl. Phys. 2011, 55, 23904. [Google Scholar] [CrossRef]

- Jin, J.W.; Nathan, A.; Barquinha, P.; Pereira, L.; Fortunato, E.; Martins, R.; Cobb, B. Interpreting anomalies observed in oxide semiconductor TFTs under negative and positive bias stress. AIP Adv. 2016, 6, 085321. [Google Scholar] [CrossRef]

- Chen, Y.; Geng, D.; Lin, T.; Mativenga, M.; Jang, J. Full-Swing Clock Generating Circuits on Plastic Using a-IGZO Dual-Gate TFTs With Pseudo-CMOS and Bootstrapping. IEEE Electron Device Lett. 2016, 37, 882–885. [Google Scholar] [CrossRef]

- Tiwari, B.; Martins, J.; Kalla, S.; Kaushik, S.; Santa, A.; Bahubalindruni, P.G.; Tavares, V.G.; Barquinha, P. A High Speed Programmable Ring Oscillator Using InGaZnO Thin-Film Transistors. In Proceedings of the 2018 International Flexible Electronics Technology Conference (IFETC), Ottawa, ON, USA, 7–9 August 2018; IEEE: New York, NY, USA, 2018. [Google Scholar] [CrossRef]

- Hwang, T.H.; Yang, I.S.; Kwon, O.K.; Ryu, M.K.; Byun, C.W.; Hwang, C.S.; Park, S.H.K. Inverters Using Only N-Type Indium Gallium Zinc Oxide Thin Film Transistors for Flat Panel Display Applications. Jpn. J. Appl. Phys. 2011, 50, 03CB06. [Google Scholar] [CrossRef]

- Zhou, J.; Kinniment, D.; Russell, G.; Yakovlev, A. A robust synchronizer. In Proceedings of the IEEE Computer Society Annual Symposium on Emerging VLSI Technologies and Architectures (ISVLSI’06), Karlsruhe, Germany, 2–3 March 2006; IEEE: New York, NY, USA, 2006. [Google Scholar] [CrossRef]

- Villaverde, A.F.; Fröhlich, F.; Weindl, D.; Hasenauer, J.; Banga, J.R. Benchmarking optimization methods for parameter estimation in large kinetic models. Bioinformatics 2019, 35, 830–838. [Google Scholar] [CrossRef] [PubMed]

- Jasanuma. Easy-On FFC/FPC Connector, 0.50 mm Pitch, FD19 Series, Right-Angle, Bottom Contact, 1.90 mm Height, 12 Circuits, 150 °C Operating Temperature, Gold over Nickel Plating; Technical report; MOLEX: Lisle, IL, USA, 2019. [Google Scholar]

- Lee, S.M.; Shin, D.; Yun, I. Degradation Mechanisms of Amorphous InGaZnO Thin-Film Transistors Used in Foldable Displays by Dynamic Mechanical Stress. IEEE Trans. Electron Devices 2017, 64, 170–175. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).