High-Power-Efficiency Readout Circuit Employing Average Capacitance-to-Voltage Converter for Micro-Electro-Mechanical System Capacitive Accelerometers

Abstract

:1. Introduction

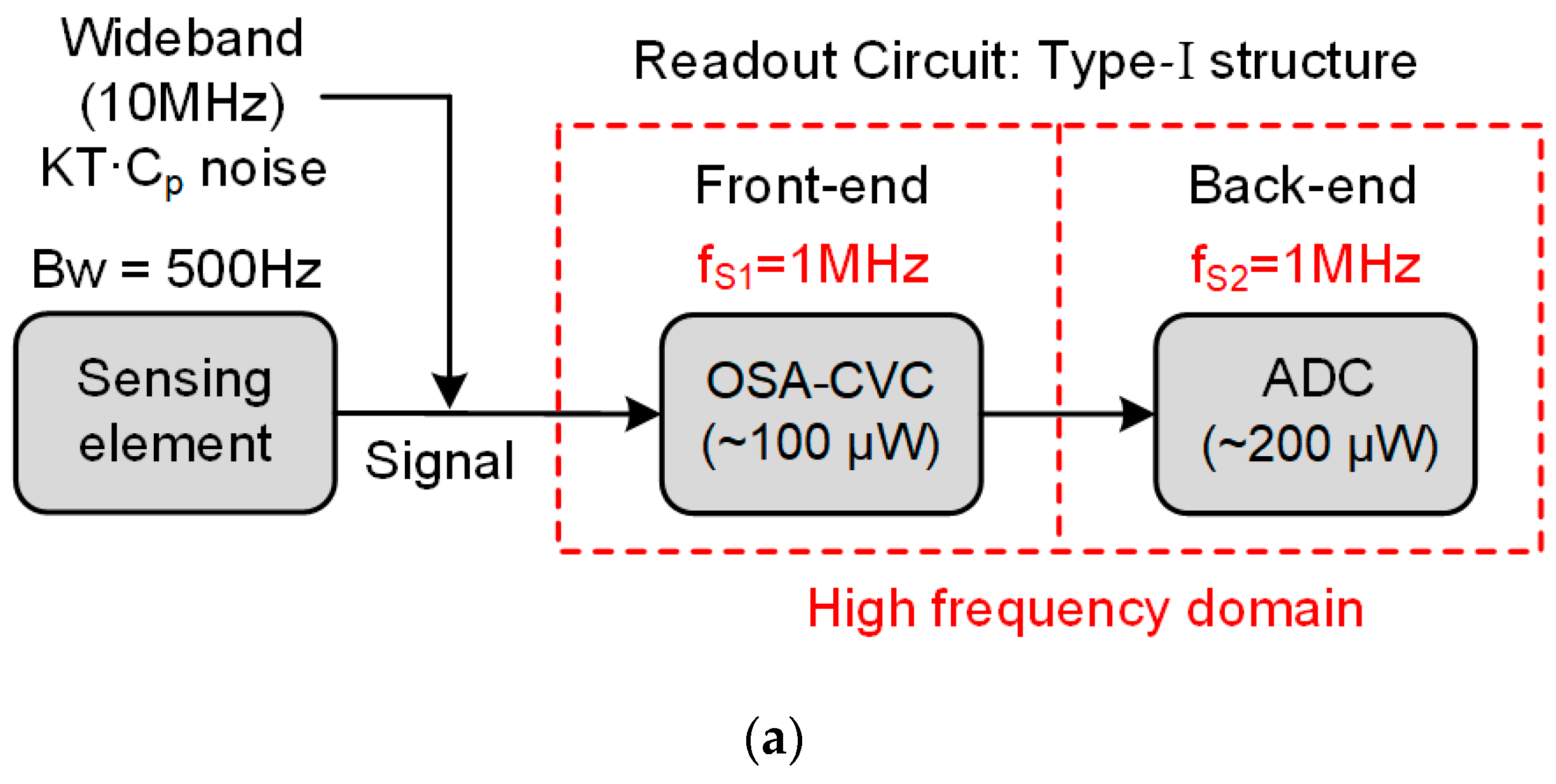

2. Traditional Readout System of MEMS Capacitive Accelerometer

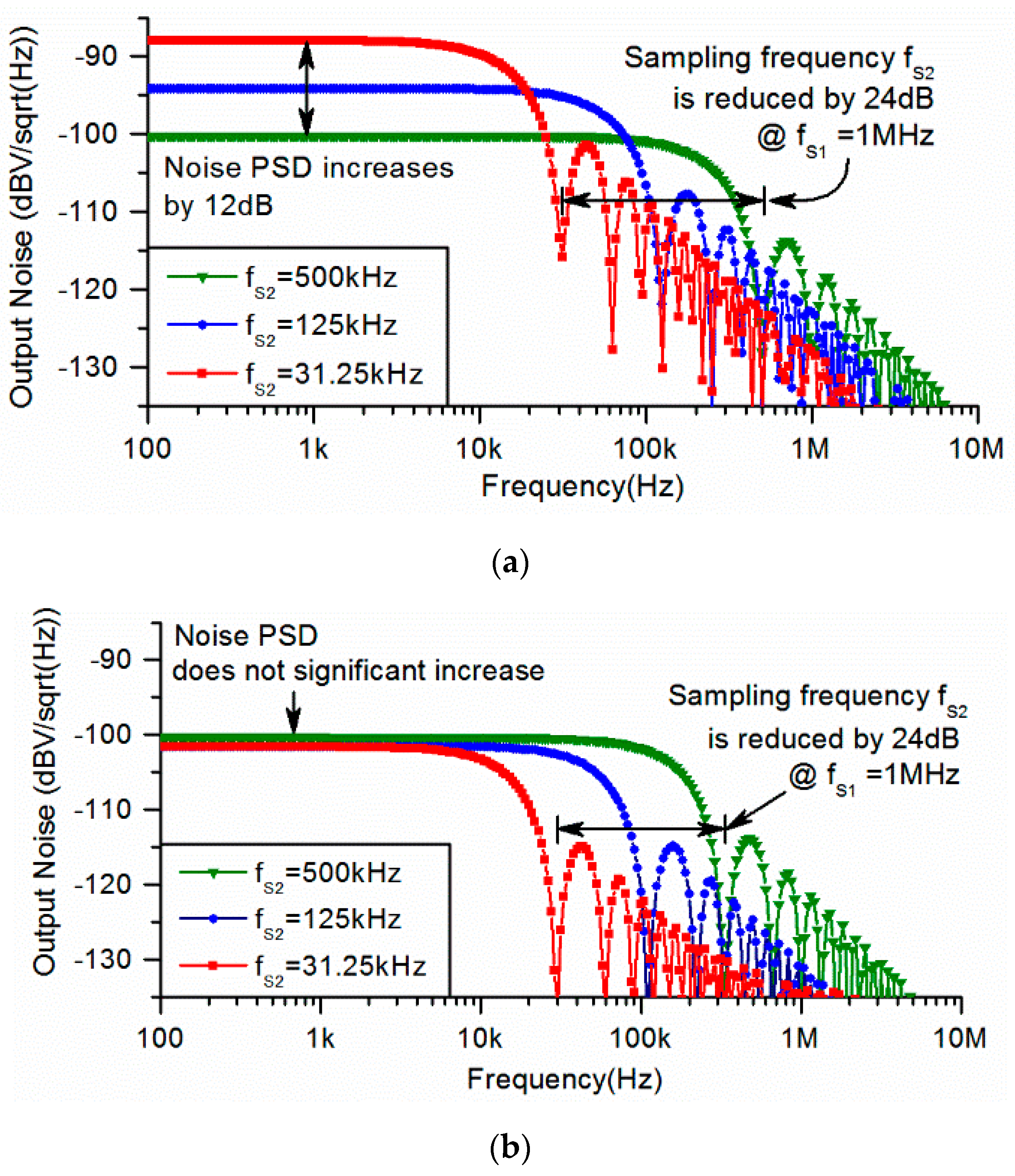

2.1. Sensor Structure

2.2. Traditional Readout Circuit for MEMS Capacitive Accelerometer

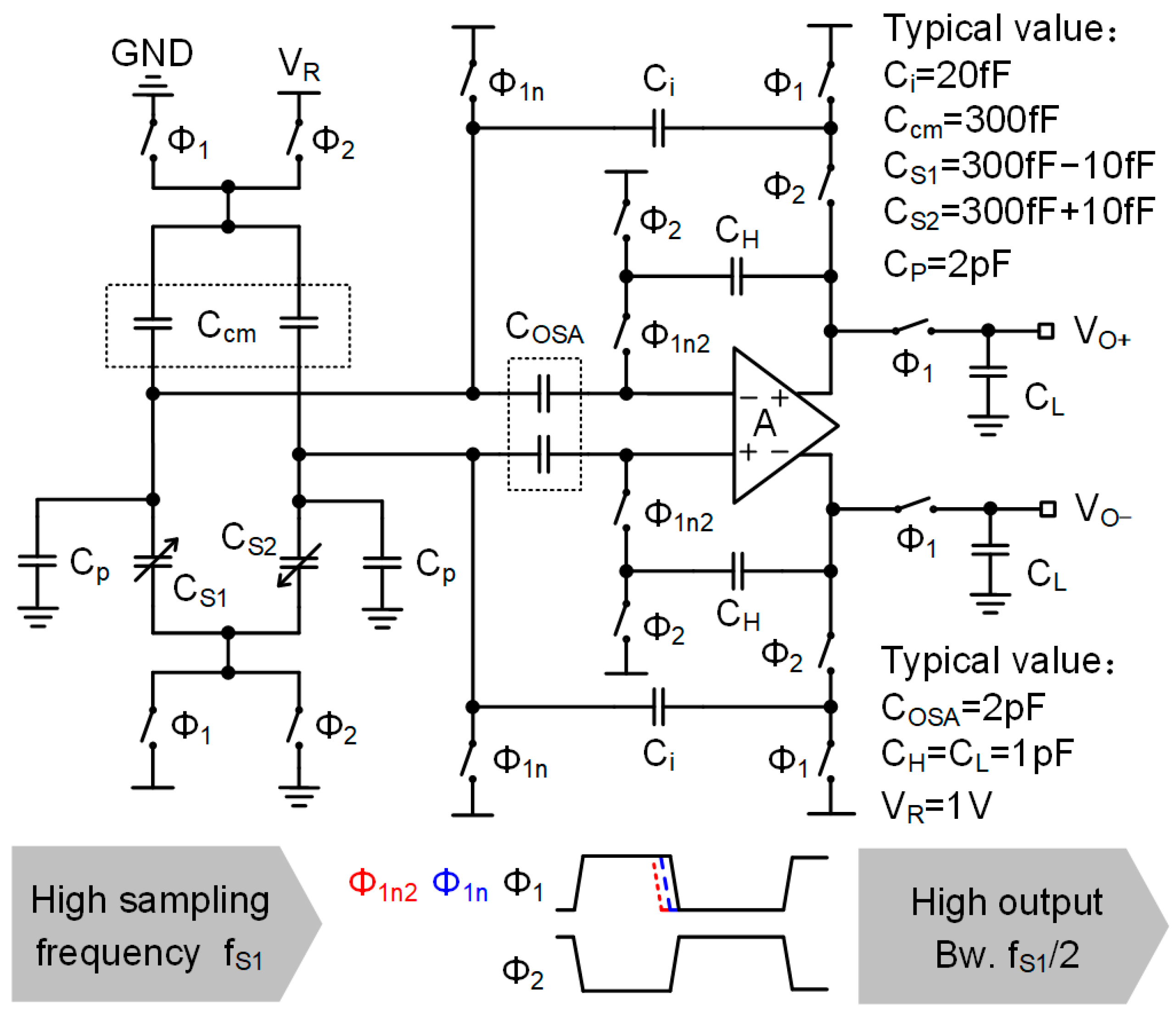

2.3. Capacitance to Voltage Converter

3. Proposed Average CVC

4. Simulation Result

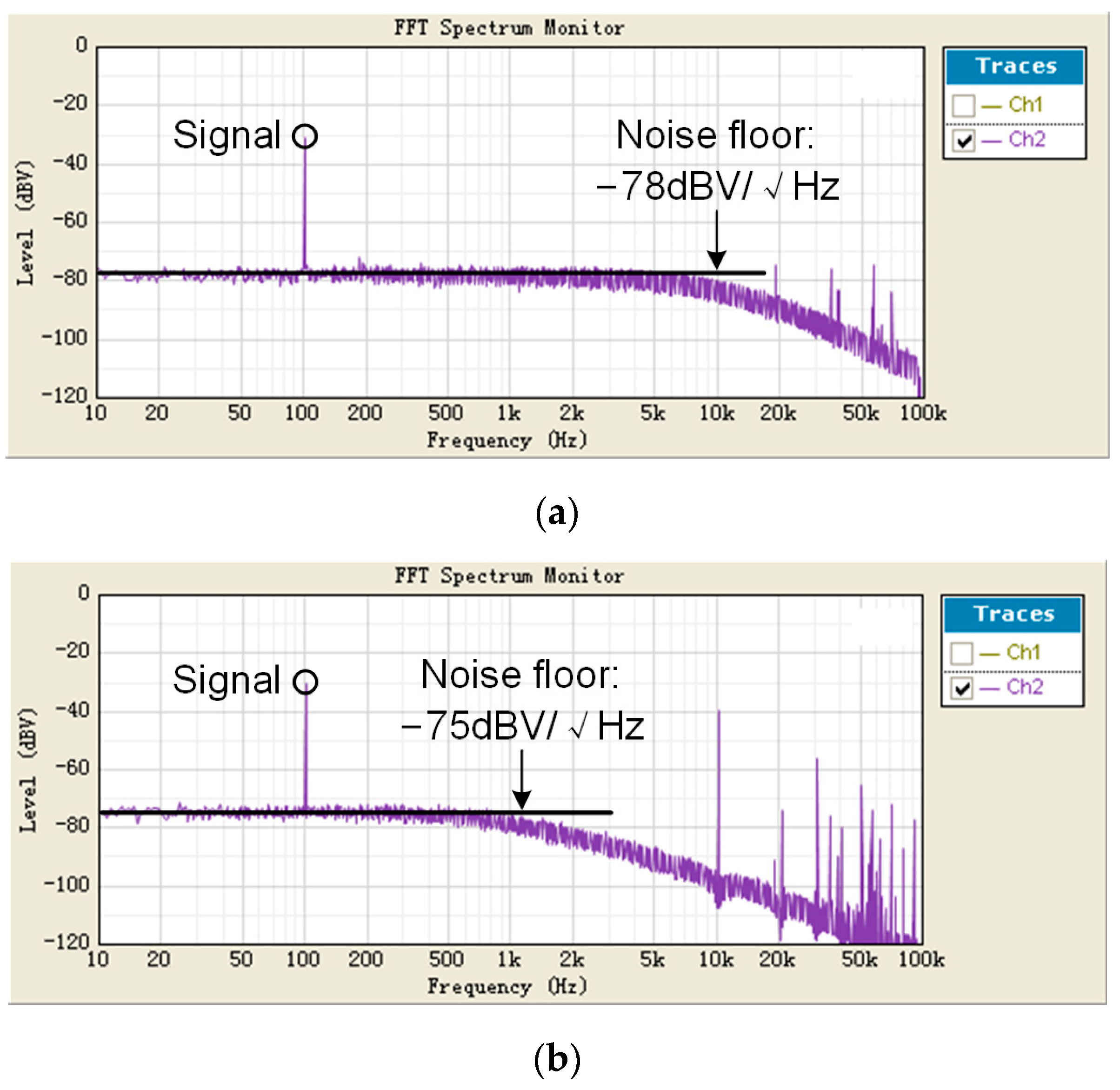

5. Experimental Result

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Shi, S.; Geng, W.; Bi, K.; Shi, Y.; Li, F.; He, J.; Chou, X. High Sensitivity MEMS Accelerometer Using PZT-Based Four L-Shaped Beam Structure. IEEE Sens. J. 2022, 22, 7627–7636. [Google Scholar] [CrossRef]

- Scardelletti, M.C.; Zorman, C.A. Packaged capacitive pressure sensor system for aircraft engine health monitoring. In Proceedings of the 2016 IEEE SENSORS, Orlando, FL, USA, 30 October 2016—3 November 2016; pp. 1–3. [Google Scholar]

- IIS2ICLX Datasheet. High-Accuracy, High-Resolution, Low-Power, 2-Axis Digital Inclinometer with Embedded Machine Learing Core; STMicroelectronics: Geneva, Switzerland, 2022. [Google Scholar]

- Liu, Y.; Zhang, L.; Wang, B. A low power accelerometer system with hybrid signal output. IEICE Electron. Express 2018, 15, 20171091. [Google Scholar] [CrossRef]

- Takayasu, M.; Dosho, S.; Ito, H.; Yamane, D.; Konishi, T.; Machida, K.; Ishihara, N.; Masu, K. A 0.18-µm CMOS time-domain capacitive-sensor interface for sub-1mG MEMS accelerometers. IEICE Electron. Express 2018, 15, 20171227. [Google Scholar] [CrossRef]

- Liu, Y.; Xiao, Y.; Fu, Q. A low power consumption inverter-based ΣΔ interface for capacitive accelerometer. IEICE Electron. Express 2018, 15, 20171152. [Google Scholar] [CrossRef]

- Peng, Y.; Jeong, S.; Choo, K.; Kim, Y.; Chen, L.-Y.; Rothe, R.; Xu, L.; Gurin, I.; Oliaei, O.; Tsinker, V.; et al. A 184 nW, 121 µg/√Hz Noise Floor Triaxial MEMS Accelerometer with Integrated CMOS Readout Circuit and Variation-Compensated High Voltage MEMS Biasing. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; pp. 84–85. [Google Scholar]

- Utz, A.; Walk, C.; Stanitzki, A.; Mokhtari, M.; Kraft, M.; Kokozinski, R. A High-Precision and High-Bandwidth MEMS-Based Capacitive Accelerometer. IEEE Sens. J. 2018, 18, 6533–6539. [Google Scholar] [CrossRef]

- Ferlito, U.; Grasso, A.D.; Pennisi, S.; Vaiana, M.; Bruno, G. Sub-Femto-Farad Resolution Electronic Interfaces for Integrated Capacitive Sensors: A Review. IEEE Access 2020, 8, 153969–153980. [Google Scholar] [CrossRef]

- Liu, G.; Wang, C.; Jia, Z.; Wang, K.; Ma, W.; Li, Z. A Rapid Design and Fabrication Method for a Capacitive Accelerometer Based on Machine Learning and 3D Printing Techniques. IEEE Sens. J. 2021, 21, 17695–17702. [Google Scholar] [CrossRef]

- Yucetas, M.; Pulkkinen, M.; Kalanti, A.; Salomaa, J.; Aaltonen, L.; Halonen, K. A high-resolution accelerometer with electrostatic damping and improved supply sensitivity. IEEE J. Solid-State Circuits 2012, 47, 1721–1730. [Google Scholar] [CrossRef]

- Lanniel, A.; Boeser, T.; Alpert, T.; Ortmanns, M. Low-Noise Readout Circuit for an Automotive MEMS Accelerometer. IEEE Open J. Solid-State Circuits Soc. 2021, 1, 140–148. [Google Scholar] [CrossRef]

- Tabrizi, H.O.; Forouhi, S.; Farhanieh, O.; Bozkurt, A.; Magierowski, S.; Ghafar-Zadeh, E. Calibration-Free CMOS Capacitive Sensor for Life Science Applications. IEEE Trans. Instrum. Meas. 2021, 70, 1–12. [Google Scholar] [CrossRef]

- ADXL355 Datasheet. Low Noise, Low Drift, Low Power, 3-Axis MEMS Accelerometers; Analog Devices: Wilmington, MA, USA, 2018. [Google Scholar]

- Altini, M.; Penders, J.; Vullers, R.; Amft, O. Estimating Energy Expenditure Using Body-Worn Accelerometers: A Comparison of Methods, Sensors Number and Positioning. IEEE J. Biomed. Health Inform. 2015, 19, 219–226. [Google Scholar] [CrossRef]

- Kamada, Y.; Isobe, A.; Oshima, T.; Furubayashi, Y.; Ido, T.; Sekiguchi, T. Capacitive MEMS Accelerometer with Perforated and Electrically Separated Mass Structure for Low Noise and Low Power. J. Microelectromech. Syst. 2019, 28, 401–408. [Google Scholar] [CrossRef]

- LIS3DH Datasheet. 3-Axis MEMS High-Performance, Ultra-Low-Power Accelerometer; STMicroelectronics: Geneva, Switzerland, 2016. [Google Scholar]

- Lanniel, A.; Boeser, T.; Alpert, T.; Ortmanns, M. Noise Analysis of Charge-Balanced Readout Circuits for MEMS Accelerometers. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 175–184. [Google Scholar] [CrossRef]

- Zhang, H.; Wei, X.; Jiang, Z. Comparison Study of Three Readout Methods for a Capacitive MEMS Accelerometer. In Proceedings of the 2018 IEEE Sensors, New Delhi, India, 28–31 October 2018; pp. 1–4. [Google Scholar]

- Zhong, L.; Xue, L.; Deng, X.; Liu, S.; Zhu, Z. High Power-Efficiency Readout Circuit for MEMS Capacitive Accelerometer. IEEE Trans. Circuits Syst. II Express Briefs 2023. [Google Scholar] [CrossRef]

- Paavola, M.; Kamarainen, M.; Laulainen, E.; Saukoski, M.; Koskinen, L.; Kosunen, M.; Halonen, K.A.I. A Micropower ΔΣ-Based Interface ASIC for a Capacitive 3-Axis Micro-Accelerometer. IEEE J. Solid-State Circuits 2009, 44, 3193–3210. [Google Scholar] [CrossRef]

- Zhong, L.; Xu, D.; Lai, X.; Wang, Y.; Liao, X.; Fang, Z.; Zheng, Y. Precision Improvement of Power-Efficient Capacitive Senor Readout Circuit Using Multi-Nested Clocks. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2578–2587. [Google Scholar] [CrossRef]

- Zhong, L.; Lai, X.; Xu, D. Oversampling Successive Approximation Technique for MEMS Differential Capacitive Sensor. IEEE J. Solid-State Circuits 2018, 53, 2240–2251. [Google Scholar] [CrossRef]

- Zhong, L.; Lai, X.; Song, H.; Xu, D. Differential Capacitive Readout Circuit Using Oversampling Successive Approximation Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 4072–4085. [Google Scholar] [CrossRef]

- Wang, Y.; Lai, X.; Liu, M.; Liu, C. Nested-Oversampling Successive Approximation (OSA) Technique for Readout Circuit of MEMS Capacitive Accelerometer. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 2769–2773. [Google Scholar] [CrossRef]

- Murmann, B. Thermal noise in track-and-hold circuits: Analysis and simulation techniques. IEEE Solid-State Circuits Mag. 2012, 4, 46–54. [Google Scholar] [CrossRef]

- Zhong, L.; Yang, J.; Xu, D.; Lai, X. Bandwidth-Enhanced Oversampling Successive Approximation Readout Technique for Low-Noise Power-Efficient MEMS Capacitive Accelerometer. IEEE J. Solid-State Circuits 2020, 55, 2529–2538. [Google Scholar] [CrossRef]

- Lai, X.; Wang, Y.; Li, Q.; Habib, K. Reset Noise Sampling Feedforward Technique (RNSF) for Low Noise MEMS Capacitive Accelerometer. Electronics 2022, 11, 2693. [Google Scholar] [CrossRef]

- Ghanbari, M.M.M.; Tsai, J.M.; Nirmalathas, A.; Muller, R.; Gambini, S. An Energy-Efficient Miniaturized Intracranial Pressure Monitoring System. IEEE J. Solid-State Circuits 2017, 52, 720–734. [Google Scholar] [CrossRef]

- Jeon, S.; Lee, J.; Hwang, H.; Ryu, W.; Chae, Y. A Parasitic Insensitive Catheter-Based Capacitive Force Sensor for Cardiovascular Diagnosis. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 812–823. [Google Scholar] [CrossRef] [PubMed]

- Cho, S.-I.; Lim, S.-I.; Baek, K.-H.; Kim, S. Capacitive proximity sensor with negative capacitance generation technique. Electron. Lett. 2012, 48, 1409–1411. [Google Scholar] [CrossRef]

- Pavan, S.; Schreier, R.; Temes, G.C. Understanding Delta-Sigma Data Convertersr, 2nd ed.; Wiley Press: Norwood, NJ, USA, 2017. [Google Scholar]

- Mohammadi, A.; Moheimani, S.O.R.; Yuce, M.R. Parallel Averaging for Thermal Noise Mitigation in MEMS Electrothermal Displacement Sensors. J. Microelectromech. Syst. 2015, 24, 4–6. [Google Scholar] [CrossRef]

- Yoo, Y.; Choi, B.-D. Readout Circuits for Capacitive Sensors. Micromachines 2021, 12, 960. [Google Scholar] [CrossRef]

- de Lacalle, L.N.L.; Lamikiz, A.; Sánchez, J.A.; de Bustos, I.F. Simultaneous measurement of forces and machine tool position for diagnostic of machining tests. IEEE Trans. Instrum. Meas. 2005, 54, 2329–2335. [Google Scholar]

| Reference/Paper | Ref [4] Reproduced in This Paper | This Work | |

|---|---|---|---|

| Power/supply | 250 μW/1.8 V | 110 μW/1.8 V | 115 μW/1.8 V |

| Sampling frequency | CVC: 1 MHz ADC: 1 MHZ | CVC: 1 MHz ADC: 31.25 kHz | CVC: 1 MHz ADC: 31.25 kHz |

| Output noise | −100 dBV/√Hz | −88 dBV/√Hz | −100 dBV/√Hz |

| Reference/Paper | Zhong [27] | Yang [7] | Wang [28] | Yucetas [11] | This Work |

|---|---|---|---|---|---|

| Technique/Structure | Bandwidth-Enhanced OSA | High Voltage-Bias | RNSF | Traditional Oversampling | Averaged CVC |

| ) | ±8 | ±1.5 | ±8 | ±1.15 | ±4 |

| z) | 10 k | 200 | 1 k | 200 | 1 k |

| z) | 100 k | - | 50 k | - | 10 k |

| ) | 1.0 | - | 4 | - | 4 |

| ) | 90 | - | −100 | - | 90 |

| ) | 900 | 121 | 250 | 2.0 | 320 |

| ) | 248 | 0.184 | 62 | 3600 | 40 |

| ) | 1.8 | - | 1.8 | 3.6 | 1.8 |

| ) | 2232 | 1.59 | 490 | 509 | 404 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, L.; Lai, X.; Wang, Y.; Niu, Z. High-Power-Efficiency Readout Circuit Employing Average Capacitance-to-Voltage Converter for Micro-Electro-Mechanical System Capacitive Accelerometers. Sensors 2023, 23, 8547. https://doi.org/10.3390/s23208547

Li L, Lai X, Wang Y, Niu Z. High-Power-Efficiency Readout Circuit Employing Average Capacitance-to-Voltage Converter for Micro-Electro-Mechanical System Capacitive Accelerometers. Sensors. 2023; 23(20):8547. https://doi.org/10.3390/s23208547

Chicago/Turabian StyleLi, Linxi, Xinquan Lai, Yuheng Wang, and Zhiwen Niu. 2023. "High-Power-Efficiency Readout Circuit Employing Average Capacitance-to-Voltage Converter for Micro-Electro-Mechanical System Capacitive Accelerometers" Sensors 23, no. 20: 8547. https://doi.org/10.3390/s23208547

APA StyleLi, L., Lai, X., Wang, Y., & Niu, Z. (2023). High-Power-Efficiency Readout Circuit Employing Average Capacitance-to-Voltage Converter for Micro-Electro-Mechanical System Capacitive Accelerometers. Sensors, 23(20), 8547. https://doi.org/10.3390/s23208547