X-band MMICs for a Low-Cost Radar Transmit/Receive Module in 250 nm GaN HEMT Technology

Abstract

1. Introduction

2. X-band Transceiver Front-End Design

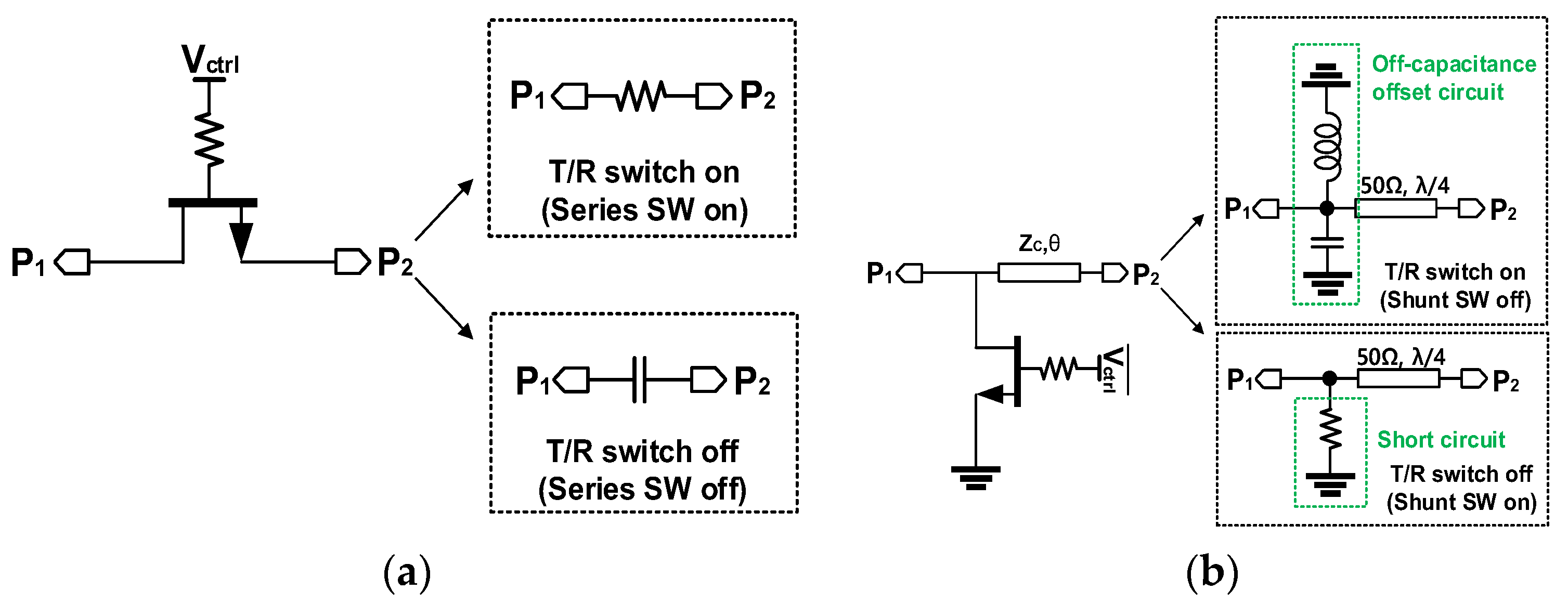

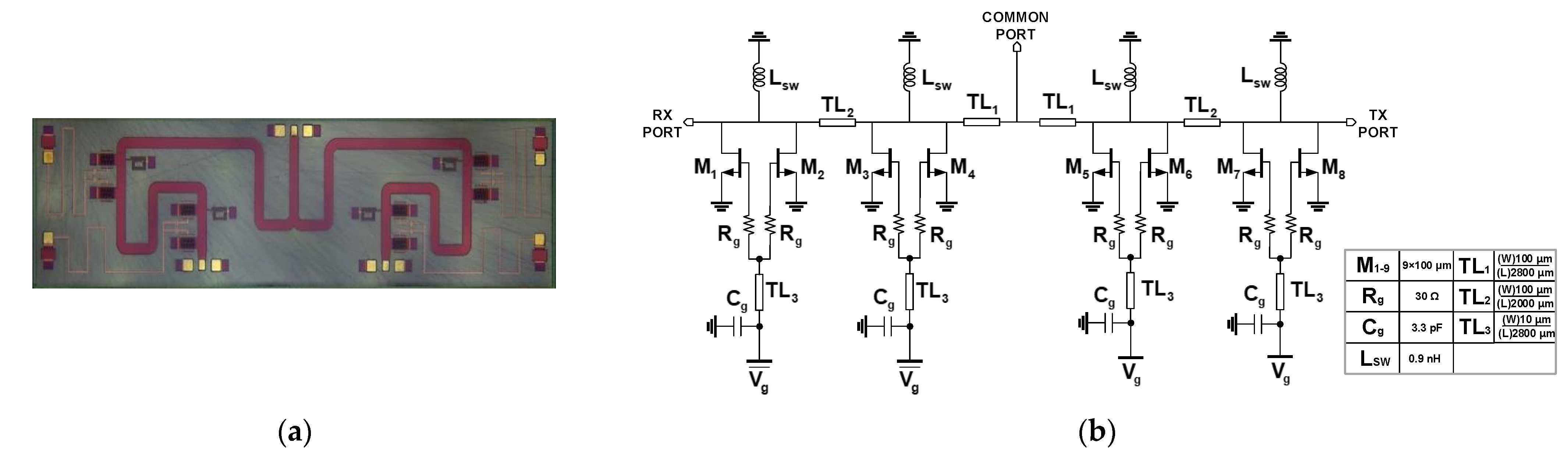

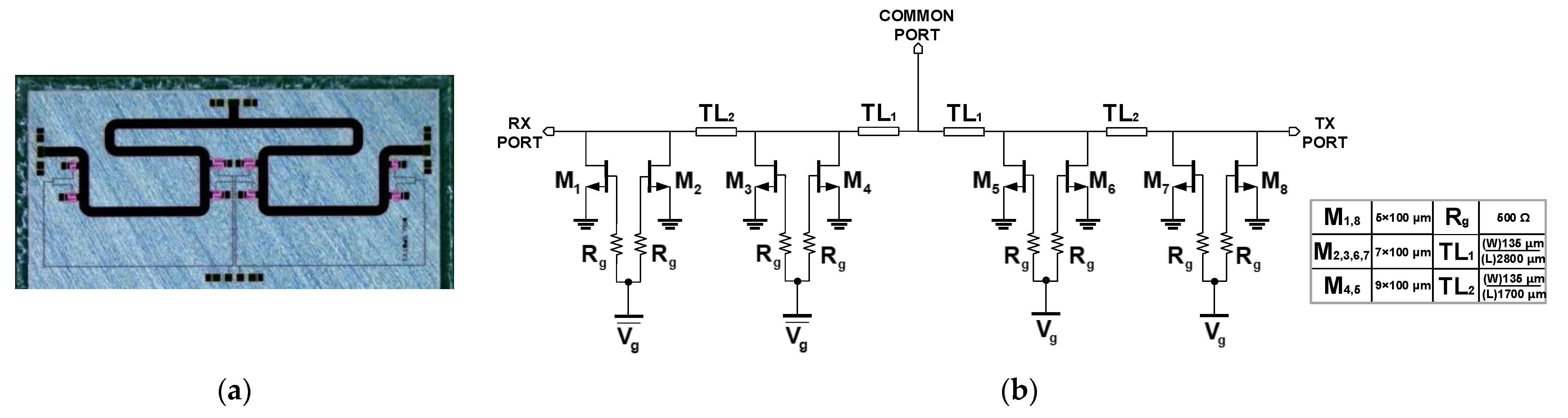

2.1. SPDT Switch as Duplexer

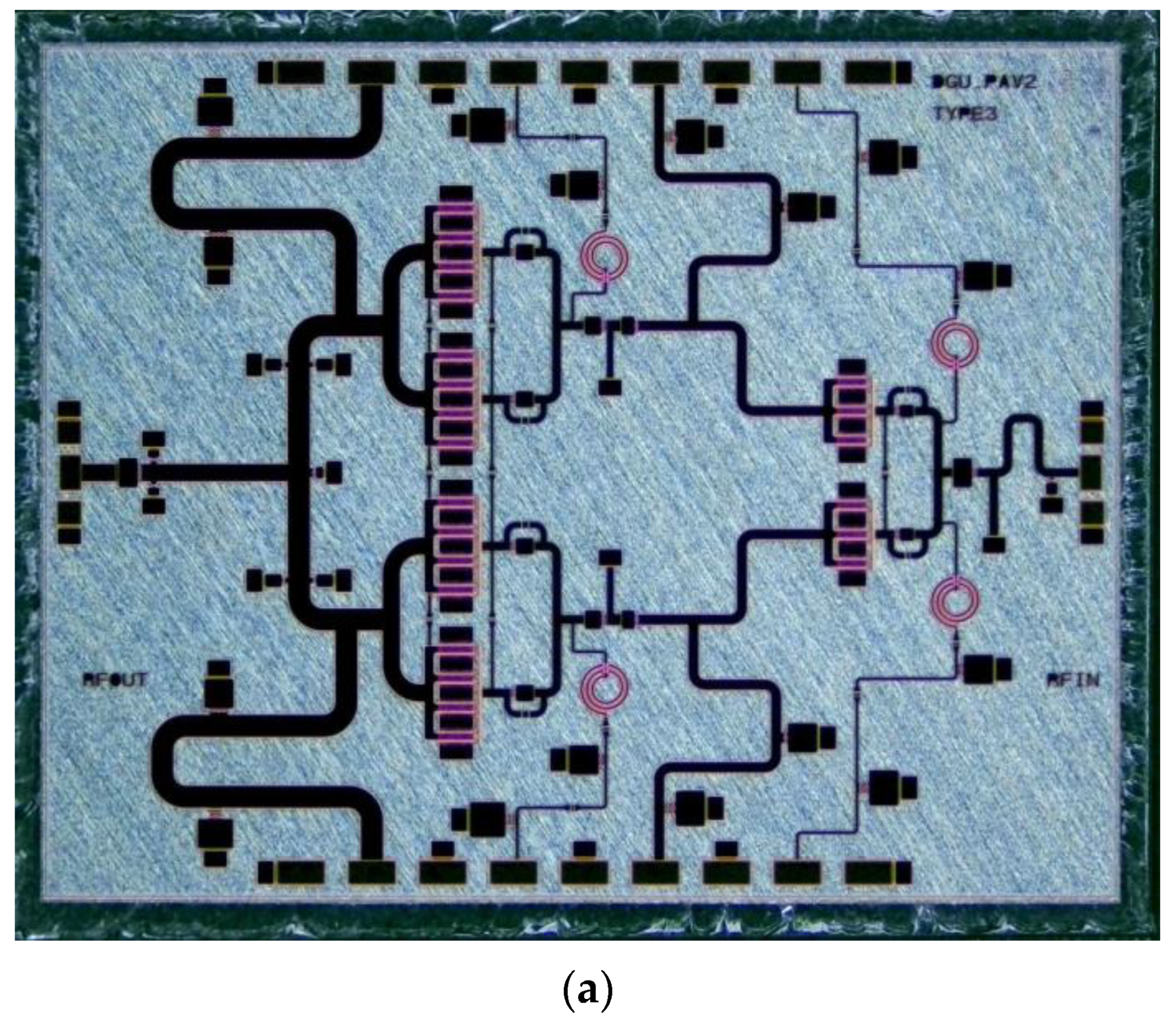

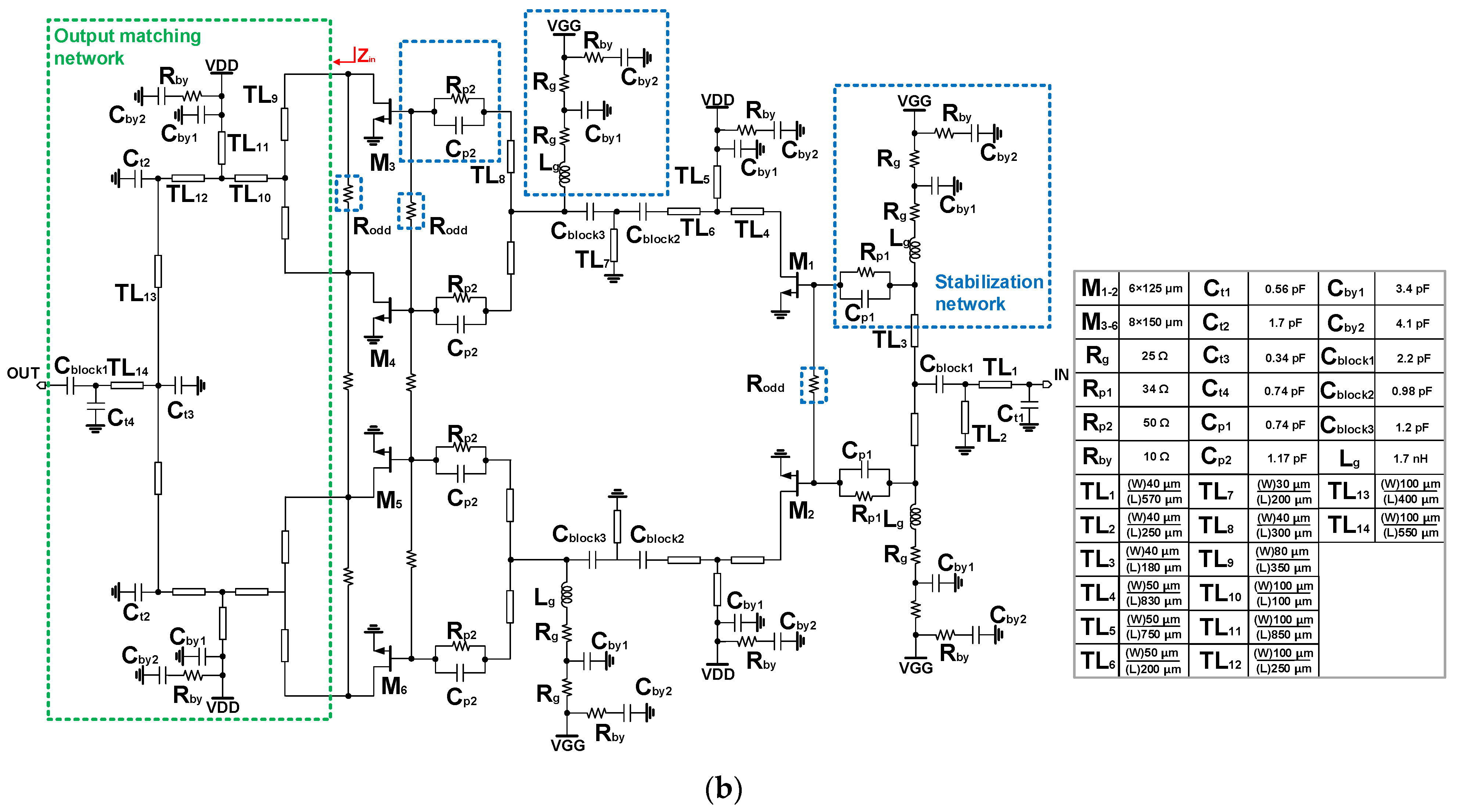

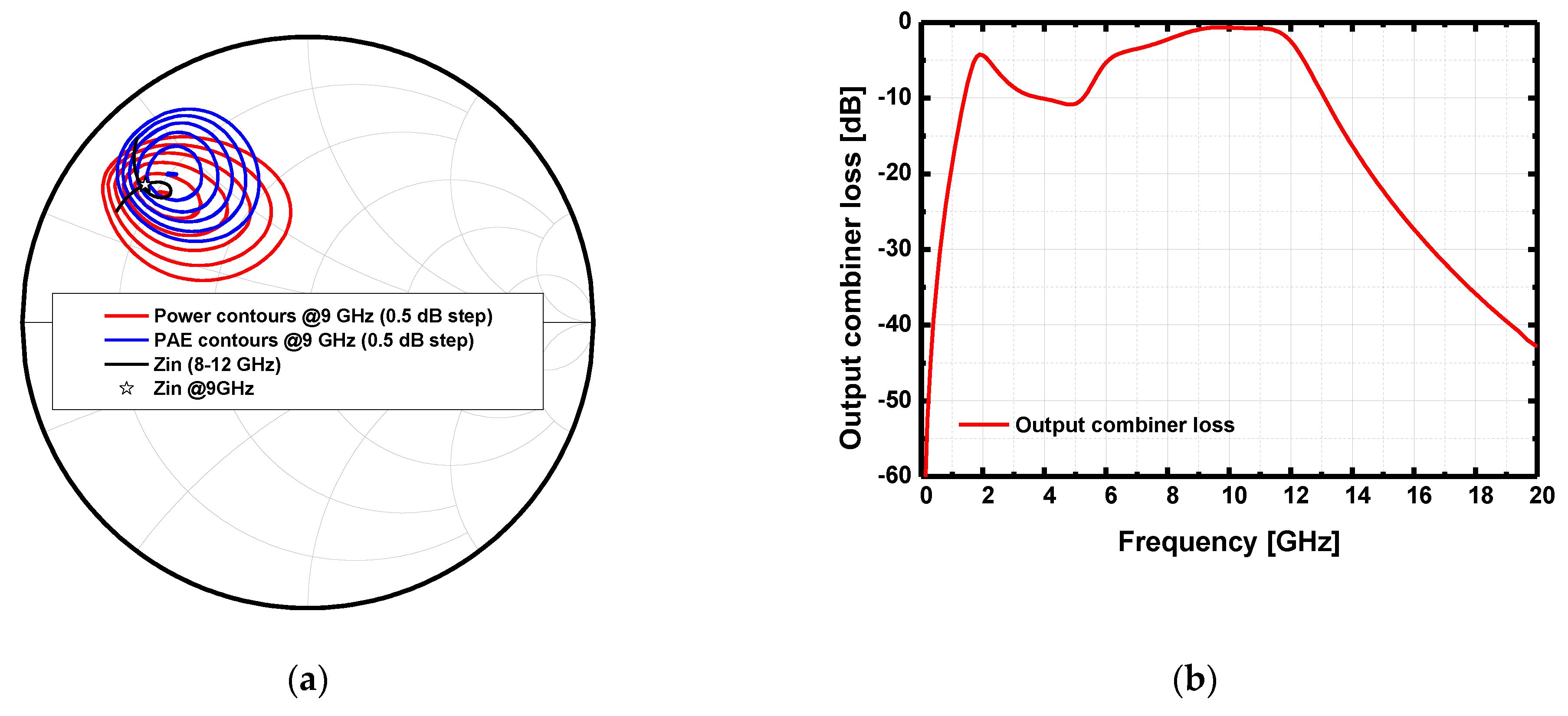

2.2. High Power Amplifier

2.3. Driving Amplifier

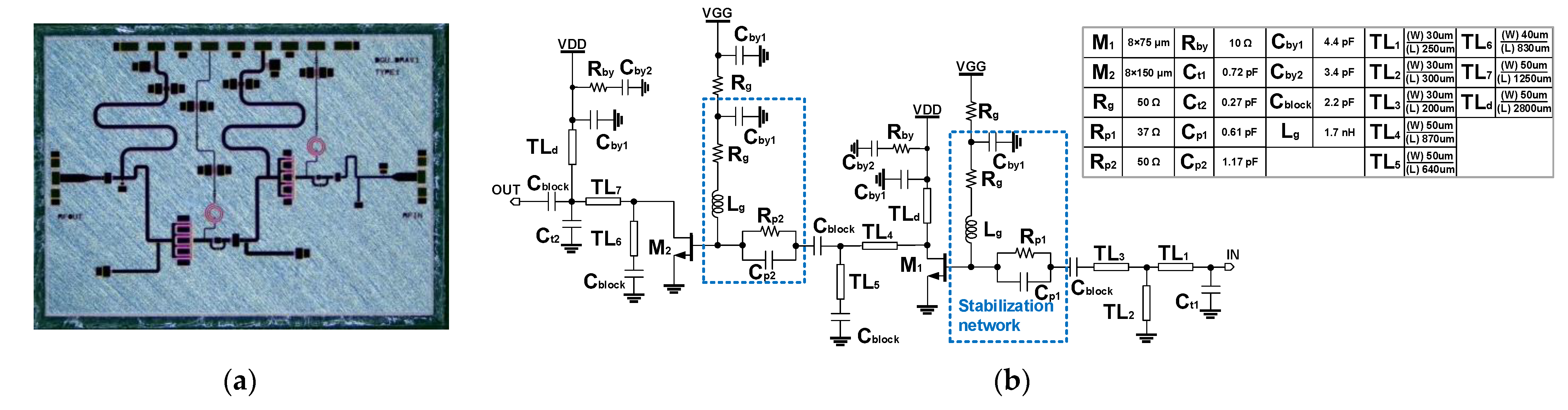

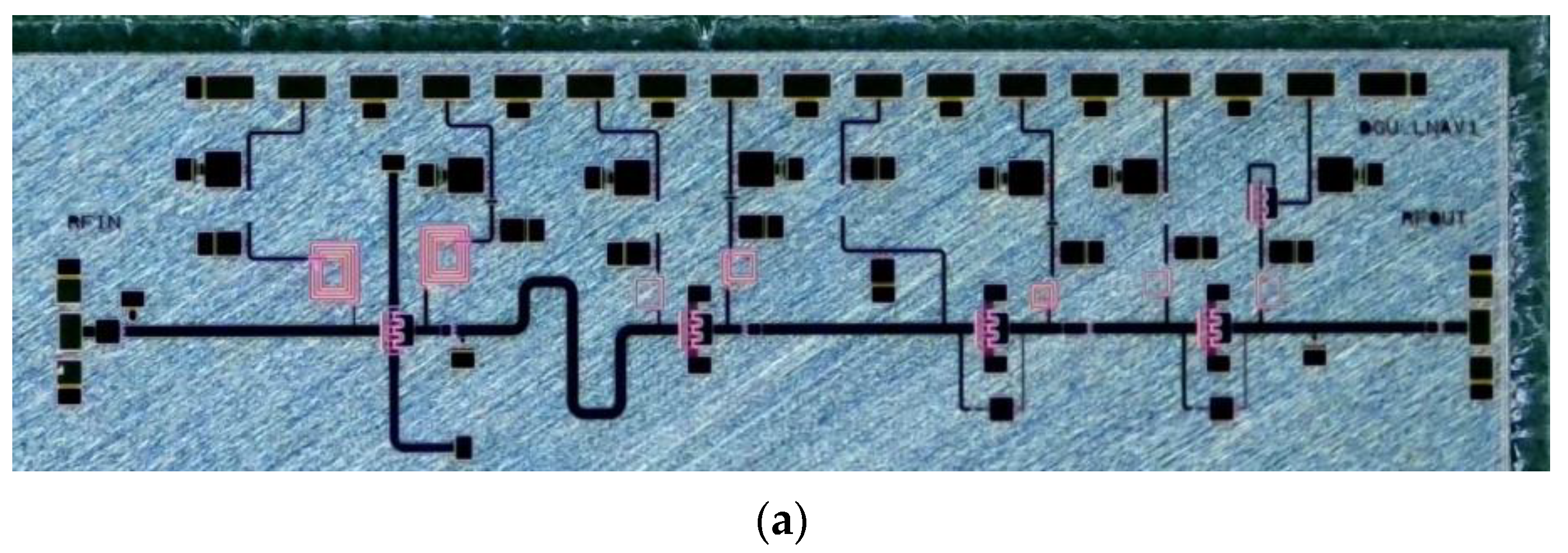

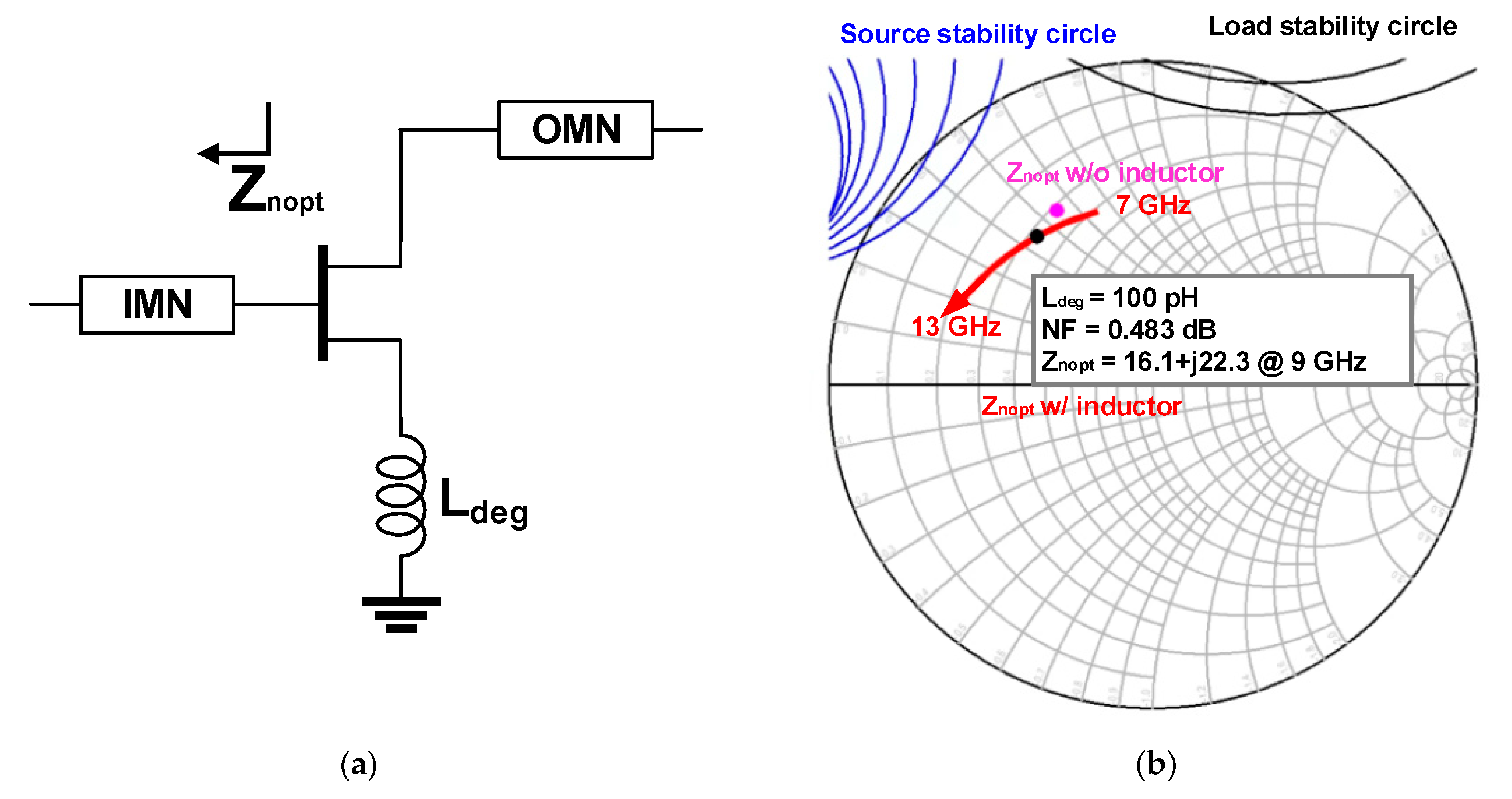

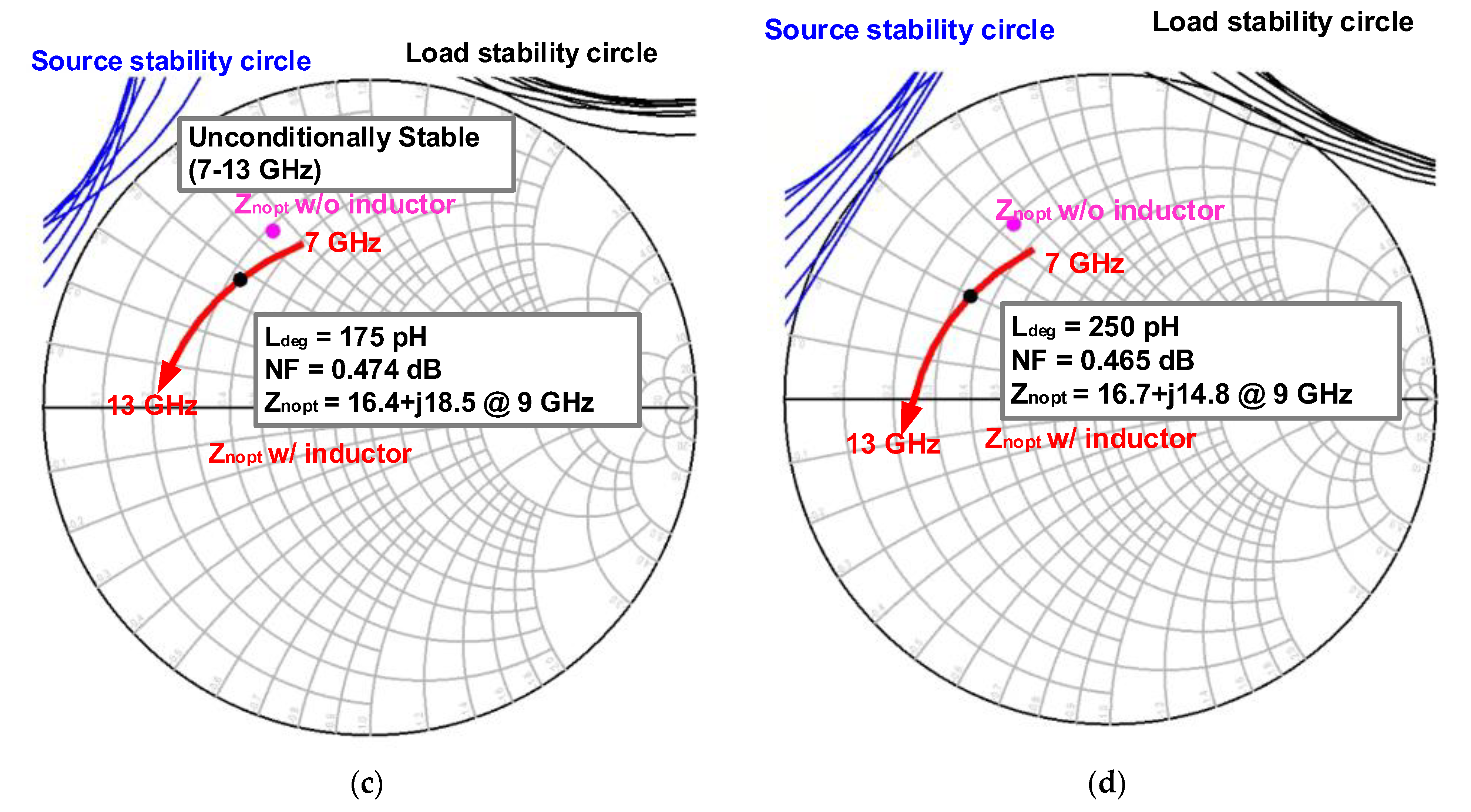

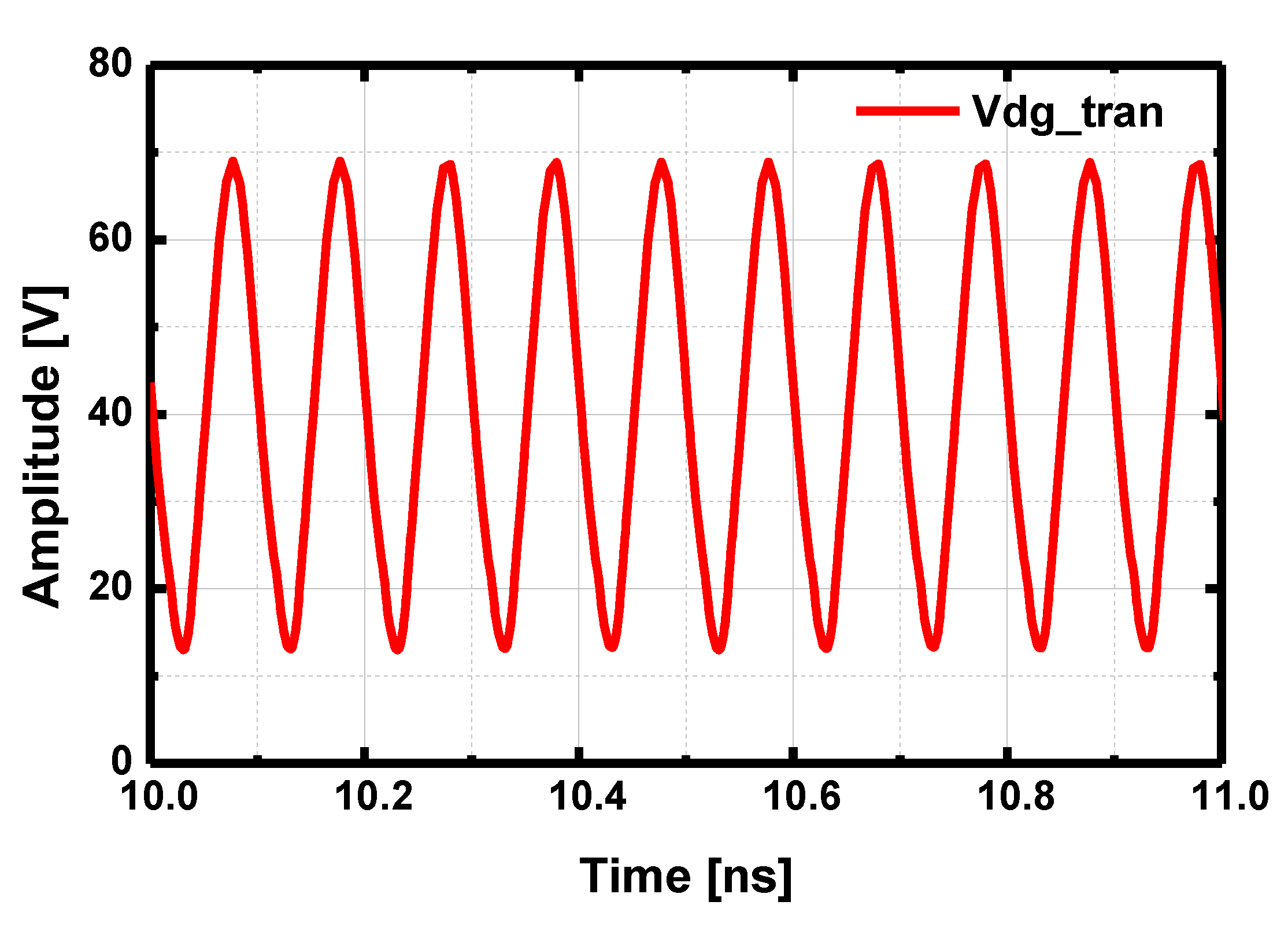

2.4. Low Noise Amplifier

3. Measurement Results

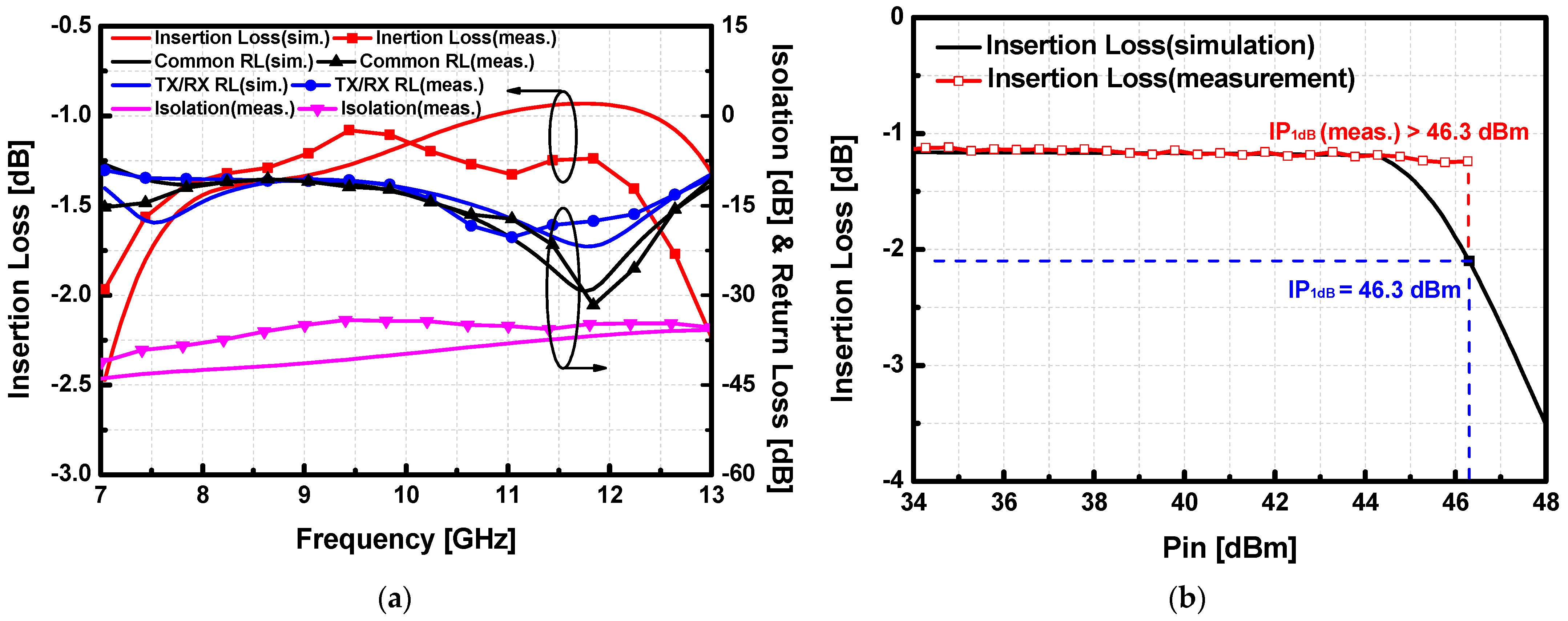

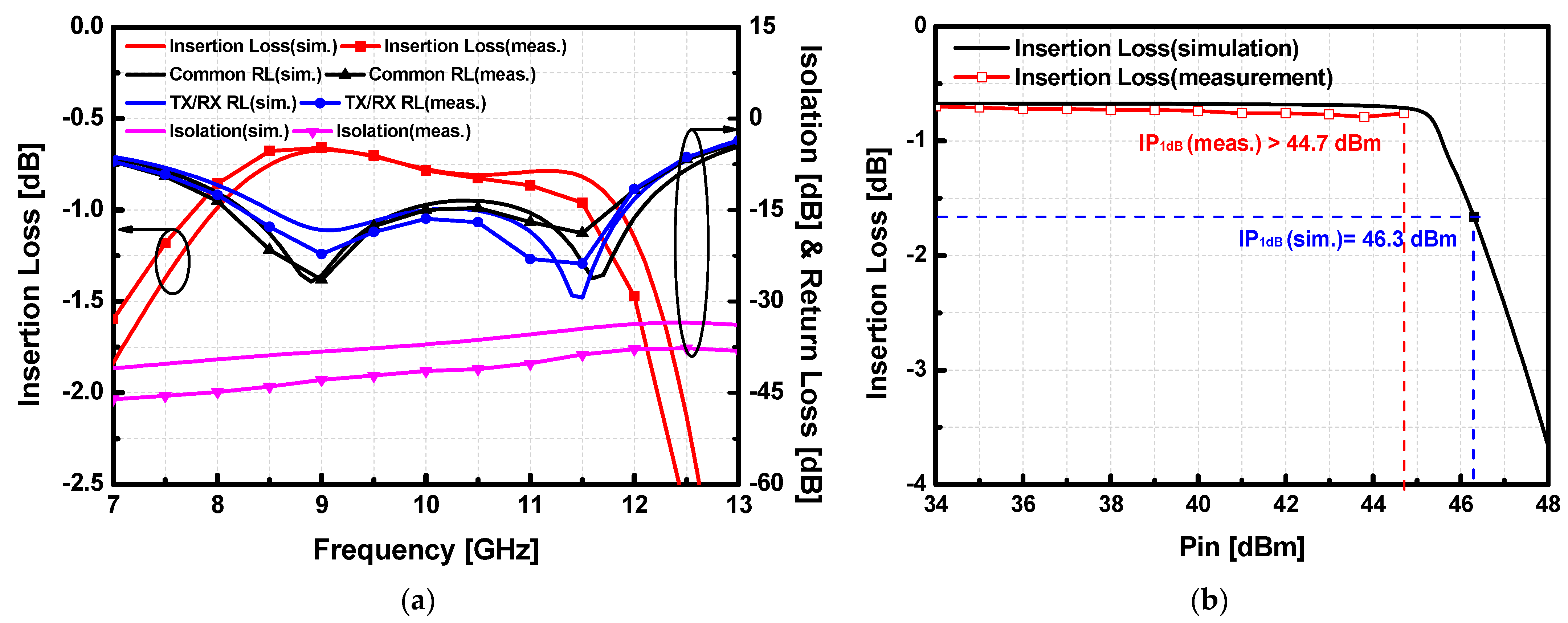

3.1. SPDT T/R Switches

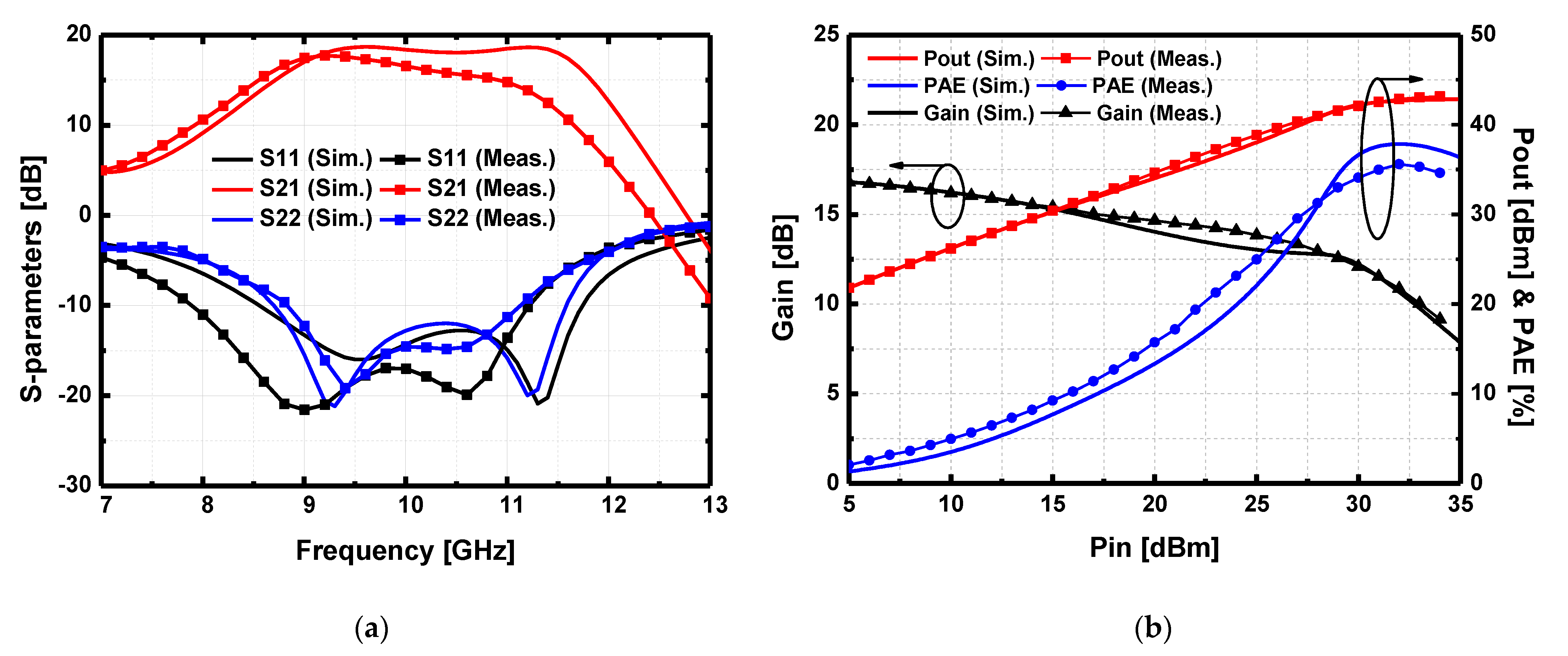

3.2. Driving Amplifier

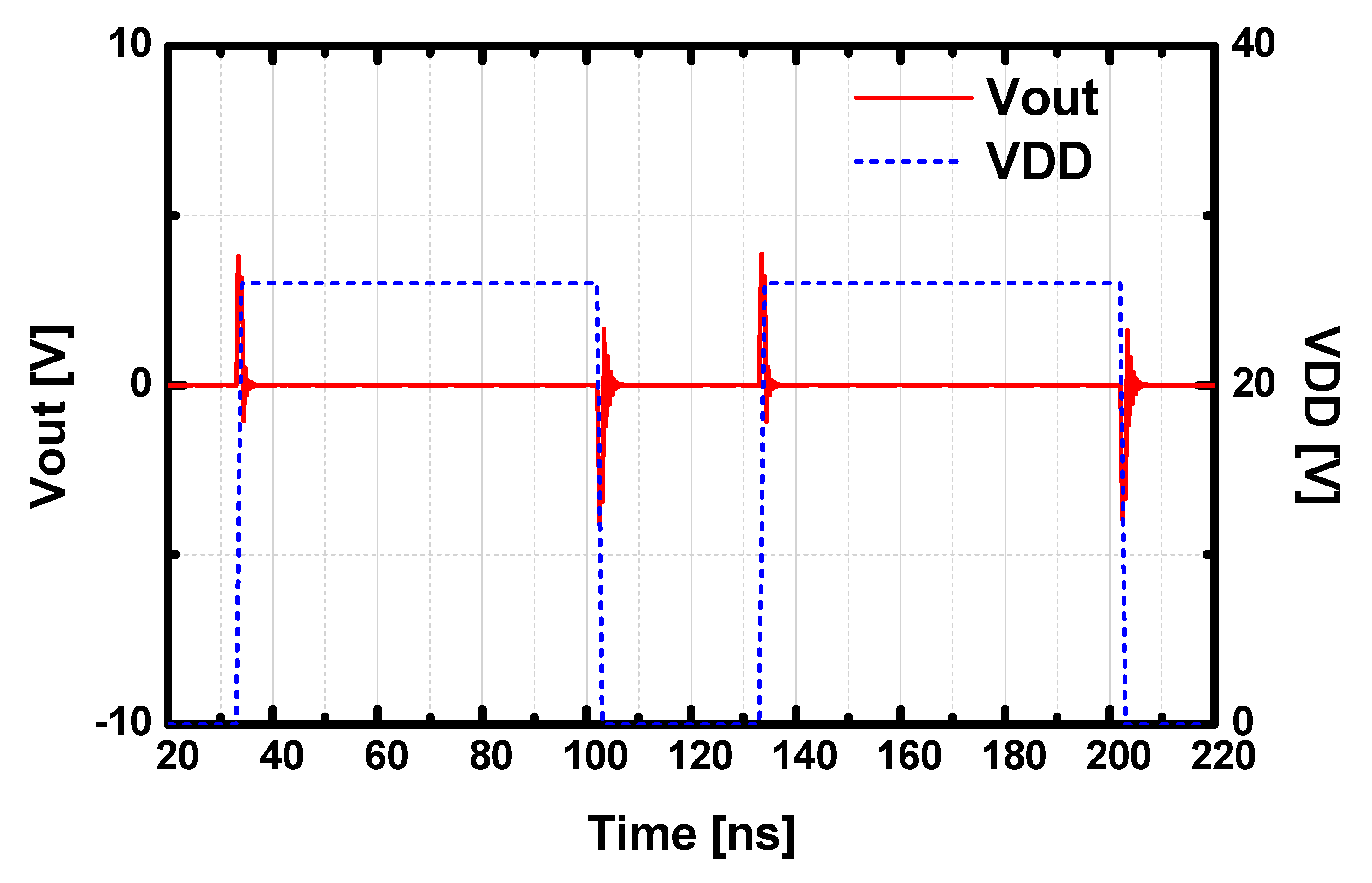

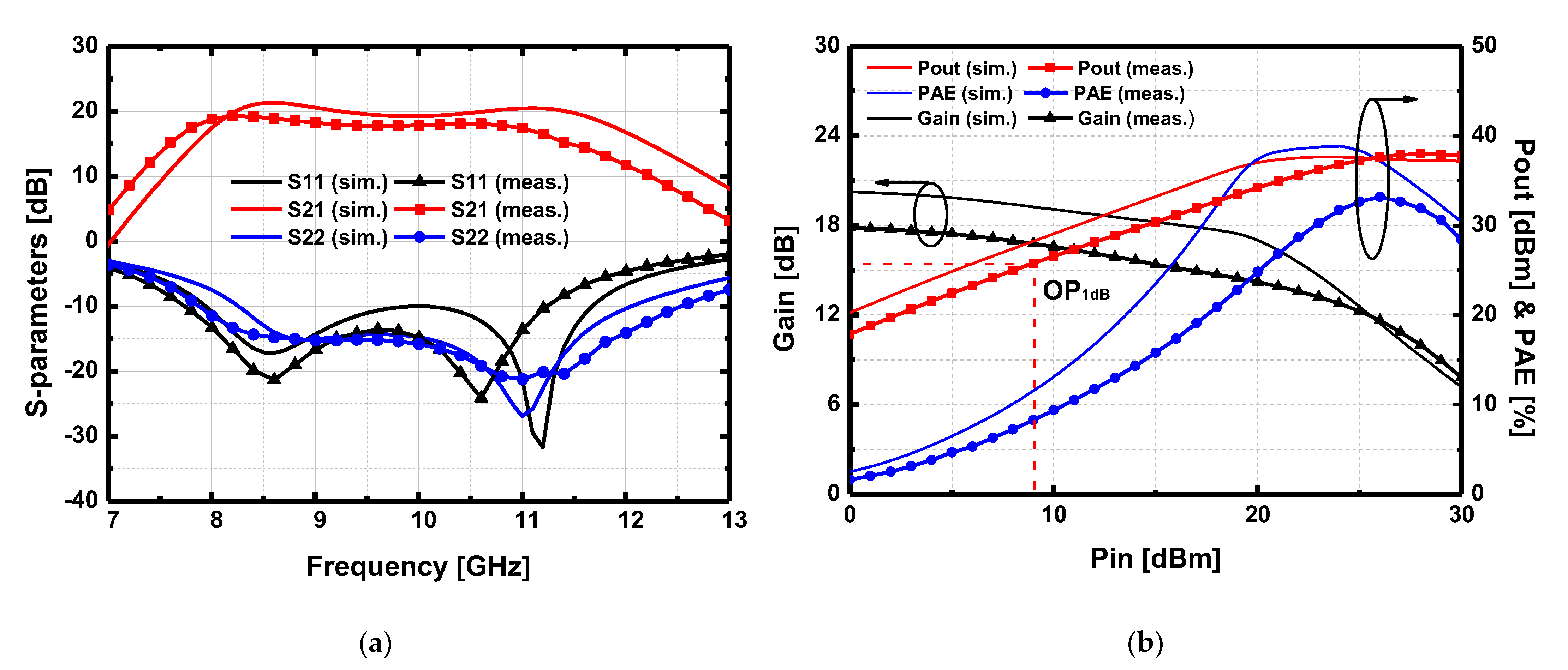

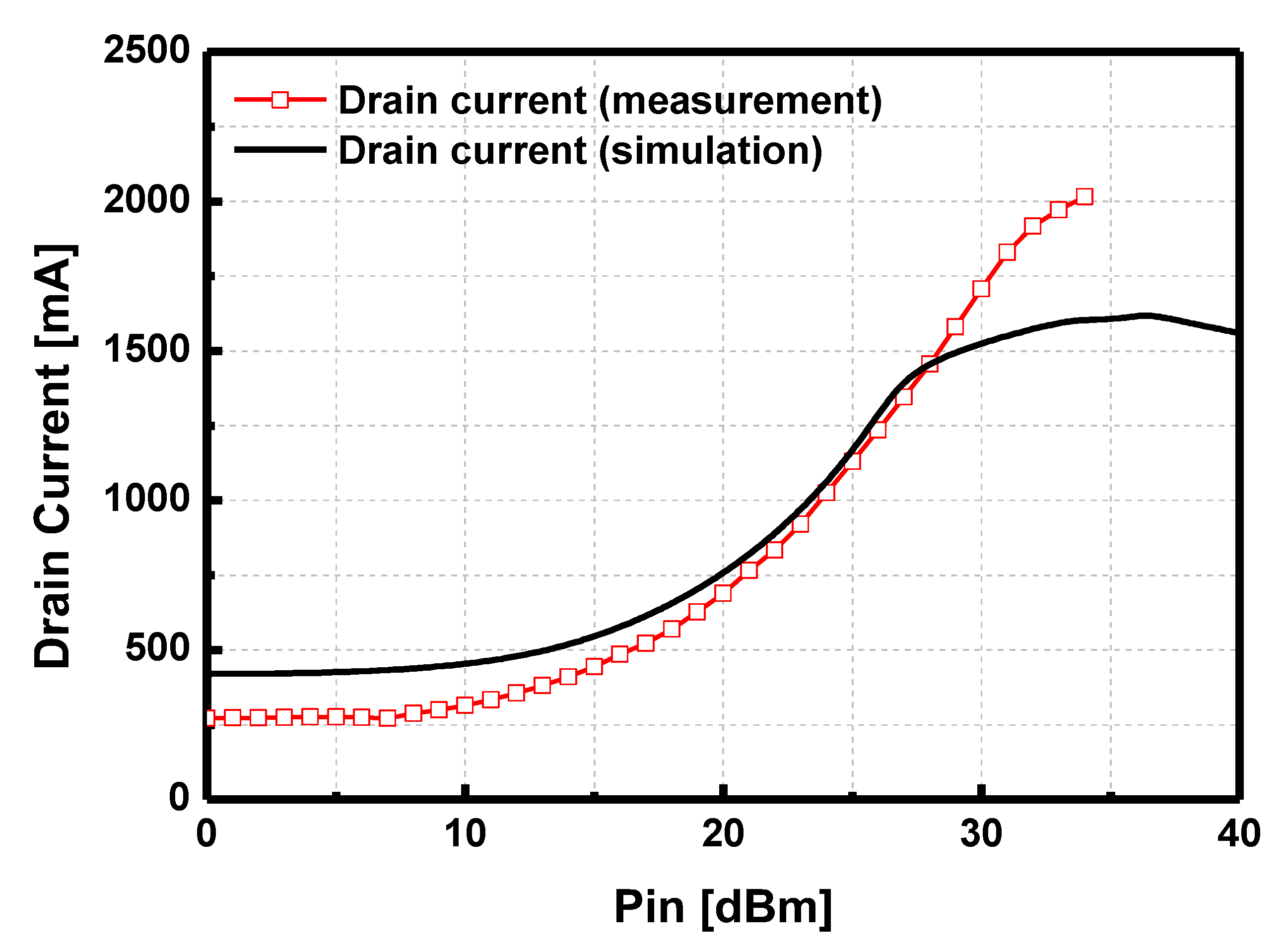

3.3. High Power Amplifier

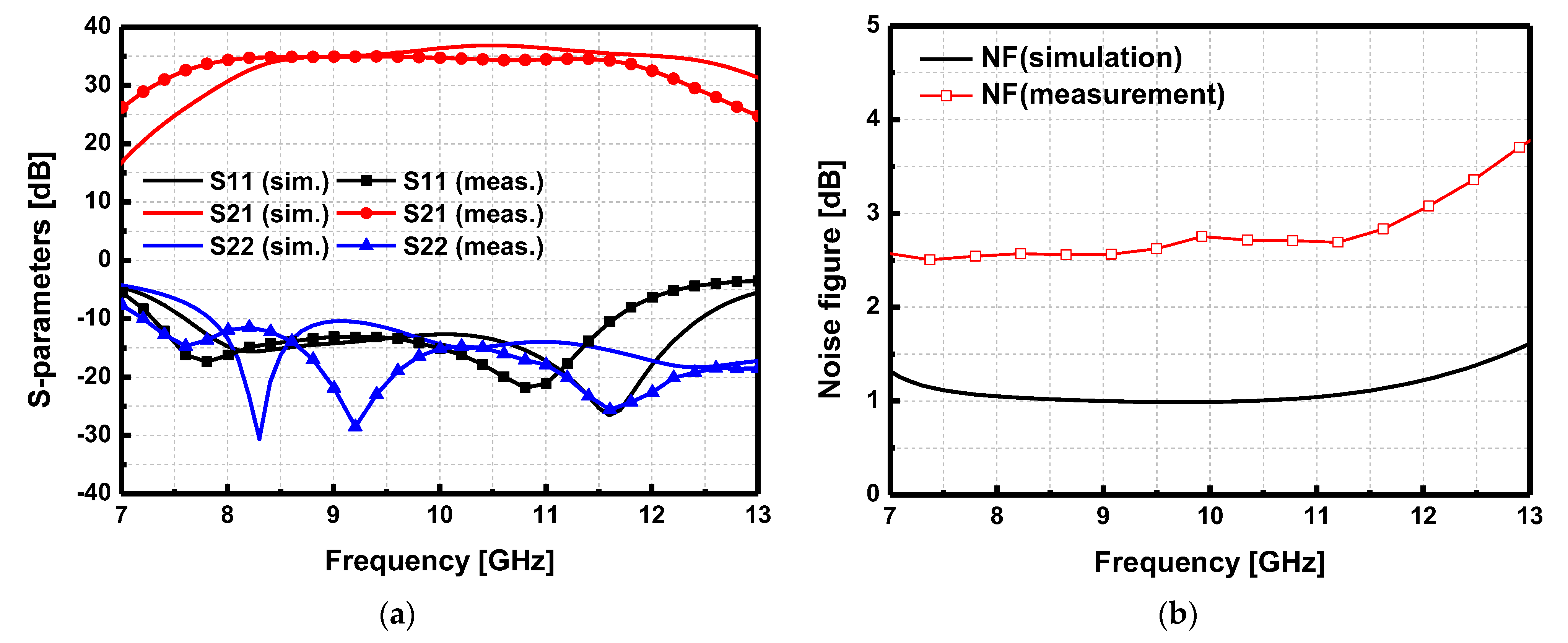

3.4. Low Noise Amplifier

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Rocco, G.; Sergio, C.; Walter, C.; Ferdinando, C.; Giorgio, P.; Alessandro, S.; Marco, V.; Manuela, S.; Maurizio, C.; Ernesto, L. S-Band GaN Single-Chip Front End for Active Electronically Scanned Array with 40-W Output Power and 1.75-dB Noise Figure. IEEE Trans. Microw. Theory Tech. 2018, 66, 5696–5707. [Google Scholar] [CrossRef]

- Fan, B.; Zhao, X.; Zhang, J.; Sun, Y.; Yang, H.; Guo, L.J.; Zhou, S. Monolithically Integrating III-Nitride Quantum Structure for Full-Spectrum White LED via Bandgap Engineering Heteroepitaxial Growth. Laser Photonics Rev. 2023, 17, 2200455. [Google Scholar] [CrossRef]

- Lu, T.; Wang, C. Radiation and Annealing Effects on GaN MOSFETs Irradiated by 1 MeV Electrons. Electronics 2022, 11, 1186. [Google Scholar] [CrossRef]

- Trew, R.J. SiC and GaN transistors—Is there one winner for microwave power applications? Proc. IEEE 2002, 90, 1032–1047. [Google Scholar] [CrossRef]

- Angelov, I.; Zirath, H.; Roshman, N. A new empirical nonlinear model for HEMT and MESFET devices. IEEE Trans. Microw. Theory Tech. 1992, 40, 2258–2266. [Google Scholar] [CrossRef]

- Sadi, T.; Schwierz, F. A Continuous Physics-Based Electrothermal Compact Model for the Study of Non Linearities in III–V HEMTs. In Proceedings of the 40th IEEE International Conference on Solid-State Device Research Conference (ESSDERC), Seville, Spain, 14–16 September 2010; pp. 432–435. [Google Scholar]

- Dasgupta, A.; Ghosh, S.; Chauhan, Y.S.; Khandelwal, S. ASMHEMT: Compact model for GaN HEMTs. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Singapore, 1–4 June 2015; pp. 495–498. [Google Scholar] [CrossRef]

- Radhakrishna, U.; Imada, T.; Palacios, T.; Antoniadis, D. MIT virtual source GaNFET-high voltage (MVSG-HV) model: A physics based compact model for HV-GaN HEMTs. Phys. Status Solidi C 2014, 11, 848–852. [Google Scholar] [CrossRef]

- Jazaeri, F.; Sallese, J.-M. Charge-based EPFL HEMT model. IEEE Trans. Electron Devices 2019, 66, 1218–1229. [Google Scholar] [CrossRef]

- Touchaei, B.J.; Shalchian, M. Non-Quasi-Static Intrinsic GaN-HEMT Model. IEEE Trans. Electron Devices 2022, 69, 6594–6601. [Google Scholar] [CrossRef]

- Nazir, M.S.; Kushwaha, P.; Pampori, A.; Ahsan, S.A.; Chauhan, Y.S. Electrical Characterization and Modeling of GaN HEMTs at Cryogenic Temperatures. IEEE Trans. Electron Devices 2022, 69, 6016–6022. [Google Scholar] [CrossRef]

- Albahrani, S.A.; Mahajan, D.; Hodges, J.; Chauhan, Y.S.; Khandelwal, S. ASM GaN: Industry Standard Model for GaN RF and Power Devices—Part-II: Modeling of Charge Trapping. IEEE Trans. Electron Devices 2019, 66, 87–94. [Google Scholar] [CrossRef]

- Campbell, C.F.; Dumka, D.C.; Kao, M.-Y. Design considerations for GaN-based MMICs. In Proceedings of the 2009 IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems, Tel Aviv, Israel, 9–11 November 2009; pp. 1–8. [Google Scholar] [CrossRef]

- Osmanoglu, S.; Ozbay, E. X-Band High Power GaN SPDT MMIC RF Switches. In Proceedings of the 2019 European Microwave Conference in Central Europe (EuMCE), Prague, Czech Republic, 13–15 May 2019; pp. 83–86. [Google Scholar]

- D’Angelo, S.; Biondi, A.; Scappaviva, F.; Resca, D.; Monaco, V.A. A GaN MMIC chipset suitable for integration in future X-band spaceborne radar T/R module Frontends. In Proceedings of the 2016 21st International Conference on Microwave, Radar and Wireless Communications (MIKON), Krakow, Poland, 9–11 May 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Hettak, K.; Ross, T.N.; Cormier, G.; Wight, J.S. Broadband High-Power GaN SPDT Switch Using Stacked-Shunt FETs and Resonance Inductors. Microw. Opt. Technol. Lett. 2013, 55, 2093. [Google Scholar] [CrossRef]

- Thorsell, M.; Fagerlind, M.; Andersson, K.; Billstrom, N.; Rorsman, N. An X-Band AlGaN/GaN MMIC Receiver Front-End. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 55–57. [Google Scholar] [CrossRef]

- Ciccognani, W.; Ferrari, M.; Limiti, E. High isolation microstrip GaN-HEMT Single-FET Switch. Int. J. RF Microw. Comput.-Aided Eng. 2010, 20, 391–398. [Google Scholar] [CrossRef]

- Janssen, J.; Hilton, K.P.; Maclean, J.O.; Wallis, D.J.; Powell, J.; Uren, M.; Martin, T.; van Heijningen, M.; van Vliet, F. X-Band GaN SPDT MMIC with over 25 Watt Linear Power Handling. In Proceedings of the 2008 European Microwave Integrated Circuit Conference, Amsterdam, The Netherlands, 27–28 October 2008; pp. 190–193. [Google Scholar]

- Rudolph, M.; Behtash, R.; Doerner, R.; Hirche, K.; Wurfl, J.; Heinrich, W.; Trankle, G. Analysis of the Survivability of GaN Low-Noise Amplifiers. IEEE Trans. Microw. Theory Tech. 2007, 55, 37–43. [Google Scholar] [CrossRef]

- Chen, R.; Li, R.; Zhou, S.; Chen, S.; Huang, J.; Wang, Z. An X-Band 40 W Power Amplifier GaN MMIC Design by Using Equivalent Output Impedance Model. Electronics 2019, 8, 99. [Google Scholar] [CrossRef]

- Shin, D.-H.; Yom, I.-B.; Kim, D.-W. X-band GaN MMIC power amplifier for the SSPA of a SAR system. In Proceedings of the 2017 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Seoul, Republic of Korea, 30 August–1 September 2017; pp. 93–95. [Google Scholar] [CrossRef]

- Bae, K.-T.; Lee, I.-J.; Kang, B.; Sim, S.; Jeon, L.; Kim, D.-W. X-Band GaN Power Amplifier MMIC with a Third Harmonic-Tuned Circuit. Electronics 2017, 6, 103. [Google Scholar] [CrossRef]

- Tao, H.-Q.; Hong, W.; Zhang, B.; Yu, X.-M. A Compact 60W X-Band GaN HEMT Power Amplifier MMIC. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 73–75. [Google Scholar] [CrossRef]

- Resca, D.; Raffo, A.; Di Falco, S.; Scappaviva, F.; Vadalà, V.; Vannini, G. X-Band GaN Power Amplifier for Future Generation SAR Systems. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 266–268. [Google Scholar] [CrossRef]

- Giofre, R.; Colantonio, P.; Giannini, F. X-band MMIC GaN power amplifier for SAR systems. Microw. Opt. Technol. Lett. 2013, 55, 2611–2616. [Google Scholar] [CrossRef]

- Piotrowicz, S.; Ouarch, Z.; Chartier, E.; Aubry, R.; Callet, G.; Floriot, D.; Jacquet, J.C.; Jardel, O.; Morvan, E.; Reveyrand, T.; et al. 43W, 52% PAE X-Band AlGaN/GaN HEMTs MMIC amplifiers. In Proceedings of the 2010 IEEE MTT-S International Microwave Symposium, Anaheim, CA, USA, 23–28 May 2010; pp. 505–508. [Google Scholar] [CrossRef]

- Yağbasan, Ç.; Aktuğ, A. Robust X-band GaN LNA with Integrated Active Limiter. In Proceedings of the 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, Spain, 23–25 September 2018; pp. 237–240. [Google Scholar] [CrossRef]

- Kazan, O.; Kocer, F.; Civi, O.A. An X-Band Robust GaN Low-Noise Amplifier MMIC with sub 2 dB Noise Figure. In Proceedings of the 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, Spain, 23–25 September 2018; pp. 234–236. [Google Scholar] [CrossRef]

- Vittori, M.; Colangeli, S.; Ciccognani, W.; Salvucci, A.; Polli, G.; Limiti, E. High performance X-band LNAs using a 0.25 μm GaN technology. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Taormina, Italy, 12–15 June 2017; pp. 157–160. [Google Scholar] [CrossRef]

- Kobayashi, K.W.; Campbell, C.; Lee, C.; Gallagher, J.; Shust, J.; Botelho, A. A reconfigurable S-/X-band GaN cascode LNA MMIC. In Proceedings of the 2017 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Miami, FL, USA, 22–25 October 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, B.; Gao, W. X-Band Robust Current-Shared GaN Low Noise Amplifier for Receiver Applications. In Proceedings of the 2016 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Austin, TX, USA, 23–26 October 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Schuh, P.; Reber, R. Robust X-band low noise limiting amplifiers. In Proceedings of the 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2–7 June 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Chang, W.; Jeon, G.-I.; Park, Y.-R.; Lee, S.; Mun, J.-K. X-band low noise amplifier MMIC using AlGaN/GaN HEMT technology on SiC substrate. In Proceedings of the 2013 Asia-Pacific Microwave Conference Proceedings (APMC), Seoul, Republic of Korea, 5–8 November 2013; pp. 681–684. [Google Scholar] [CrossRef]

- Bettidi, A.; Corsaro, F.; Cetronio, A.; Nanni, A.; Peroni, M.; Romanini, P. X-Band GaN-HEMT LNA performance versus robustness trade-off. In Proceedings of the 2009 European Microwave Integrated Circuits Conference (EuMIC), Rome, Italy, 28–29 September 2009; pp. 439–442. [Google Scholar]

- Janssen, J.P.B.; van Heijningen, M.; Provenzano, G.; Visser, G.C.; Morvan, E.; van Vliet, F.E. X-Band Robust AlGaN/GaN Receiver MMICs with over 41 dBm Power Handling. In Proceedings of the 2008 IEEE Compound Semiconductor Integrated Circuits Symposium, Monterey, CA, USA, 12–15 October 2008; pp. 1–4. [Google Scholar] [CrossRef]

| Ref. | This-A | This-B | [13] | [14] | [15] | [16] | [17] | [18] | [19] |

|---|---|---|---|---|---|---|---|---|---|

| Process | 0.25 μm | 0.25 μm | 0.25 μm | 0.15 μm | 0.25 μm | 0.8 μm | 0.25 μm | 0.25 μm | 0.25 μm |

| Frequency (GHz) | 8–12 | 8–12 | 0–18 | 0–14 | 8.4–10.6 | 8–12 | 2–18 | 8–12 | 8–12 |

| Insertion Loss (dB) | 1.06–1.36 | 0.66–1.5 | 0.3–1.5 | <1.2 | <1.1 | <1.4 | <2.0 | 1 | 3.5 |

| Isolation (dB) | <34 | <35 | <25 | >30 | >28 | 22.2 | >33 | >37 | 35 |

| IP1dB (dBm) | >46 (IP0.1dB) | >44.7 (IP0.1dB) | >41.5 | 40 (IP0.1dB) | >42 | 38 | >33 (IP0.2dB) | >39 | 44 |

| Ref. | This | [15] | [21] | [22] | [23] | [24] | [25] | [26] | [27] |

|---|---|---|---|---|---|---|---|---|---|

| Process | 0.25 μm | 0.25 μm | 0.25 μm | 0.25 μm | 0.25 μm | 0.25 μm | 0.25 μm | 0.5 μm | 0.25 μm |

| Frequency (GHz) | 8.5–11 | 8.8–10.2 | 8–12 | 8.8–10.8 | 8.5–10.5 | 8–12 | 8.8–10.4 | 8.6–10.6 | 9–11 |

| Small-signal Gain (dB) | 17.7(34 *) | >24 | 24.5–28 | 24–26 | >20 | >25 | 25 | 19 | N/A |

| Psat (dBm) | 43.0 | >44.5 | 46.0 | 45.0–46.0 | 43.2–44.7 | 47.5–48.7 | >41.4 | 42.0 | 45.4–46.3 |

| PAE (%) | 35.6(33.4 *) | >36 | 44.7 | 38–44 | 35–37 | 40–45 | >38 | 33 | 40–52 |

| Power Gain (dB) | 10.9(25.9 *) | >18 | 22 | 17.0–18.4 | 17.7–19.6 | 21.5–22.7 | 18 | 16 | 16.3 |

| Pulse (us/%) | 100/10 | 100/30 | 100/10 | 100/10 | 100/10 | 100/10 | 50/15 | 20/1 | 20/10 |

| VDD (V) | 26 | 30 | 28 | 28 | 28 | 28 | 26 | 25 | 25 |

| Ref. | This | [28] | [29] | [30] | [31] | [32] | [33] | [34] | [35] | [36] |

|---|---|---|---|---|---|---|---|---|---|---|

| Process | 0.25 μm | 0.25 μm | 0.25 μm | 0.25 μm | 0.15 μm | 0.25 μm | 0.25 μm | 0.25 μm | N/A | 0.25 μm |

| Frequency (GHz) | 7.6–12 | 8–11 | 8–11 | 8–10 | 9–11 | 8.5–10.5 | 8–12 | 9.7–12.9 | 8–11 | 8–12 |

| Gain (dB) | >33 | >22 | 22–30.8 | 24–27 | >13.5 | >25 | 14 | 20–26 | 21 | >16 |

| NF (dB) | 2.56 | <1.6 | 1.6–1.95 | <1.3 | 1.4–2.2 | <2.5 | 1.6 | 1.7–2.1 | 2.3–2.6 | 2.3 |

| Pin(max) (W) | >6.3 | 5 | 2.5 | N/A | N/A | 5 | 4 | N/A | 9 | 10 |

| Pulse (μs/%) | 100/10 | CW | N/A | N/A | N/A | N/A | N/A | N/A | N/A | 5/10 |

| Pdiss (W) | 1.0 | 0.5 | 0.6 | 0.9 | 1.2 | 0.5 | 0.21 | 1.4 | 2.0 | 0.3 |

| Gain/Pdiss (dB/W) | >33 | >44 | >36.6 | >26.7 | >11.25 | >50 | >66.7 | >14.29 | >10.5 | >53.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, H.; Park, H.-G.; Le, V.-D.; Nguyen, V.-P.; Song, J.-M.; Lee, B.-H.; Park, J.-D. X-band MMICs for a Low-Cost Radar Transmit/Receive Module in 250 nm GaN HEMT Technology. Sensors 2023, 23, 4840. https://doi.org/10.3390/s23104840

Lee H, Park H-G, Le V-D, Nguyen V-P, Song J-M, Lee B-H, Park J-D. X-band MMICs for a Low-Cost Radar Transmit/Receive Module in 250 nm GaN HEMT Technology. Sensors. 2023; 23(10):4840. https://doi.org/10.3390/s23104840

Chicago/Turabian StyleLee, Hyeonseok, Hyeong-Geun Park, Van-Du Le, Van-Phu Nguyen, Jeong-Moon Song, Bok-Hyung Lee, and Jung-Dong Park. 2023. "X-band MMICs for a Low-Cost Radar Transmit/Receive Module in 250 nm GaN HEMT Technology" Sensors 23, no. 10: 4840. https://doi.org/10.3390/s23104840

APA StyleLee, H., Park, H.-G., Le, V.-D., Nguyen, V.-P., Song, J.-M., Lee, B.-H., & Park, J.-D. (2023). X-band MMICs for a Low-Cost Radar Transmit/Receive Module in 250 nm GaN HEMT Technology. Sensors, 23(10), 4840. https://doi.org/10.3390/s23104840