Skew-Circulant-Matrix-Based Harmonic-Canceling Synthesizer for BIST Applications

Abstract

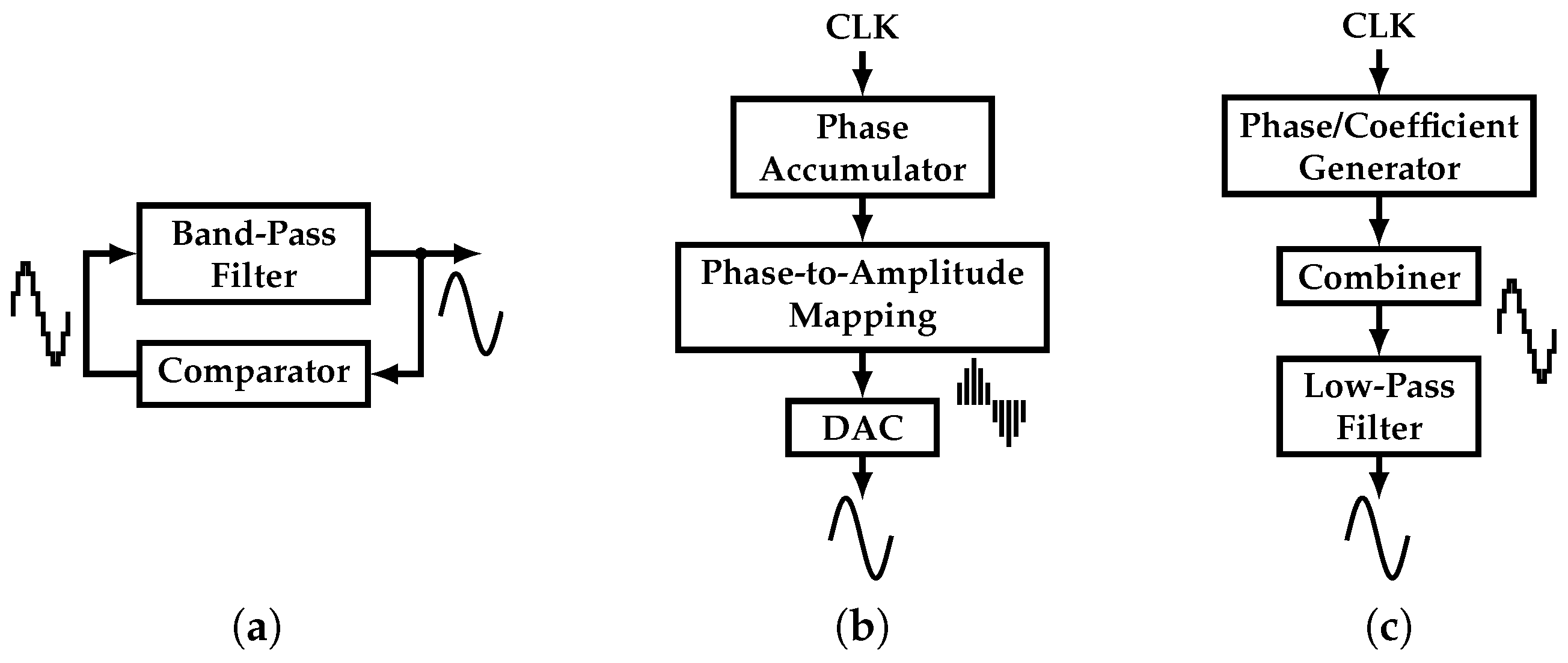

:1. Introduction

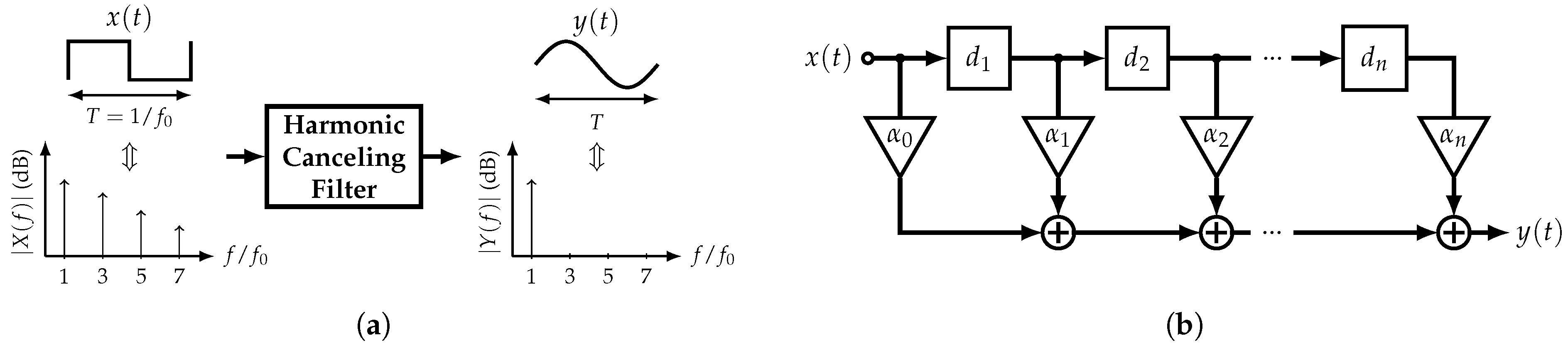

2. Harmonic-Canceling Filter

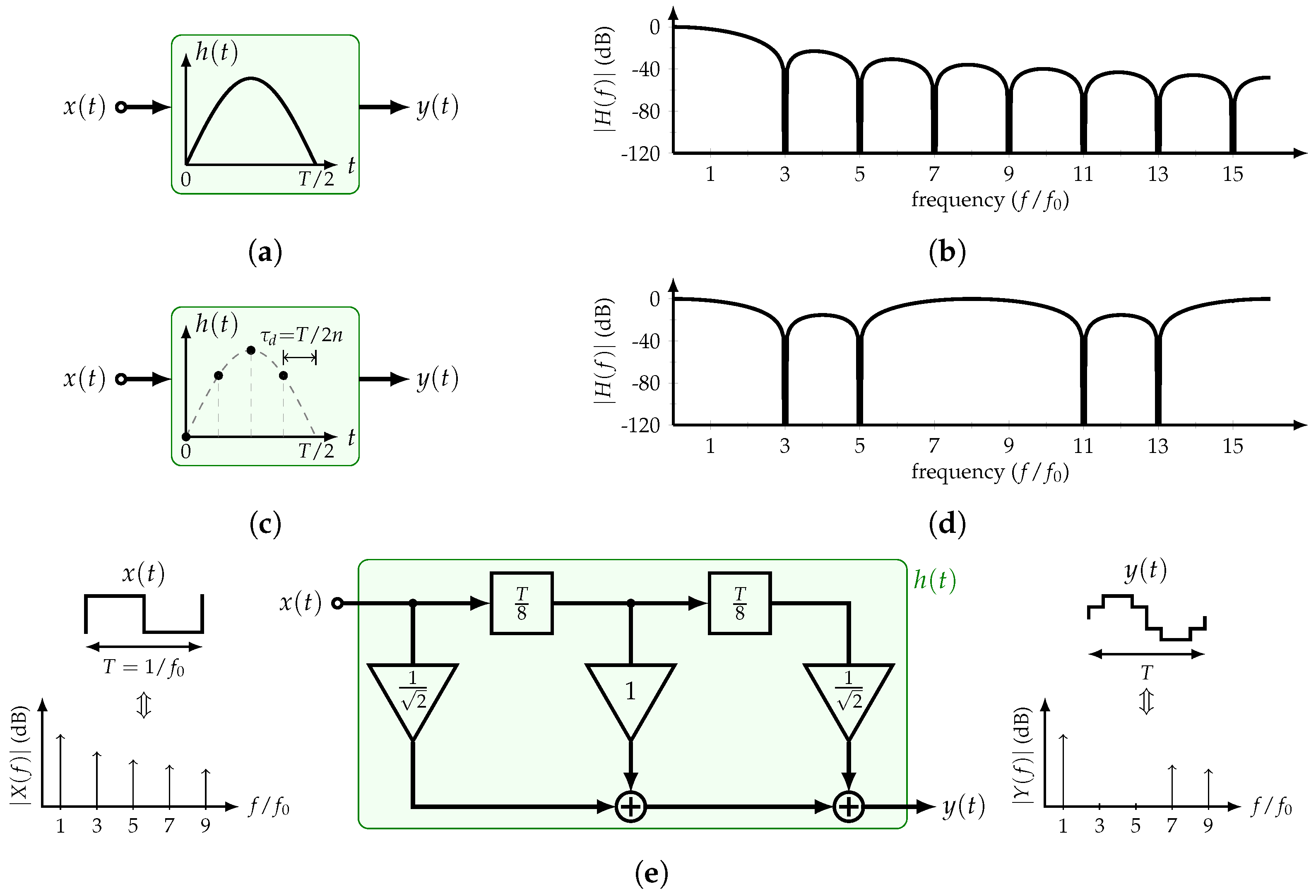

2.1. Constant-Amplitude HCF

2.2. Constant-Delay HCF

3. Proposed SCM-Based HCF

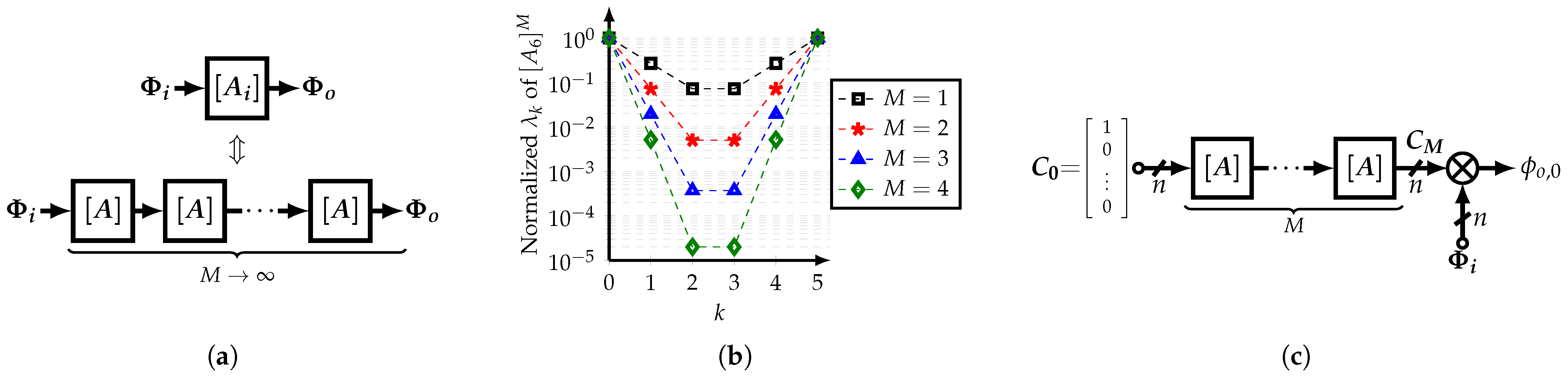

3.1. Matrix Representation of the HCF

3.2. HCF with Multi-Stage Open-Loop SCM-Based Coefficient Generator

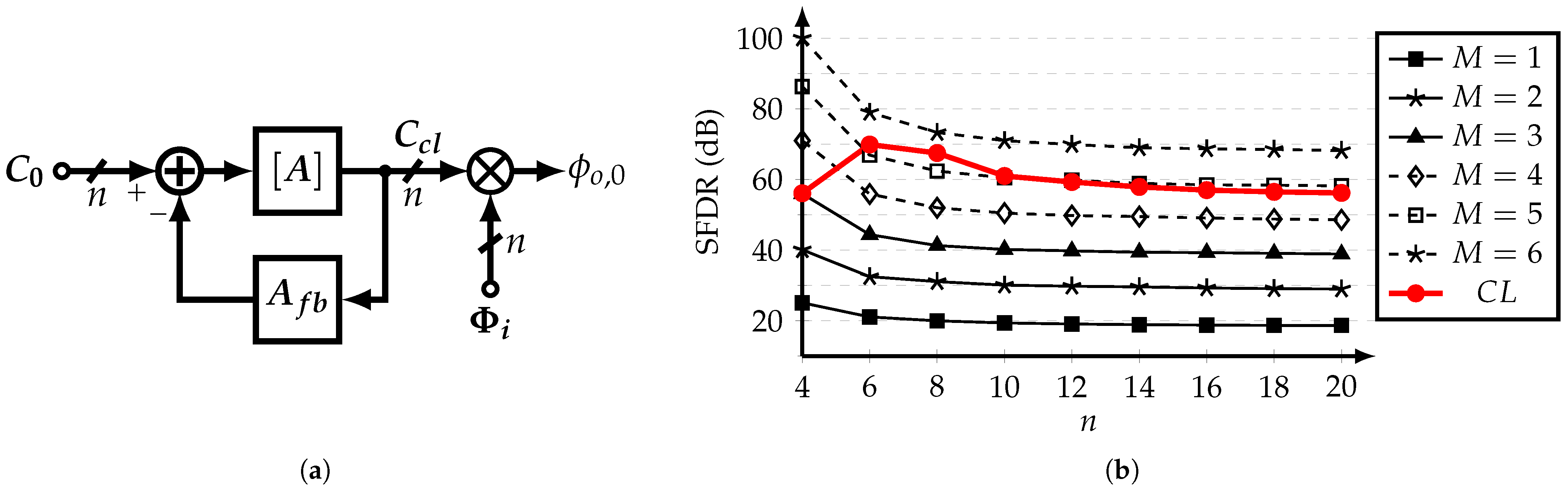

3.3. HCF with Single-Stage Closed-Loop SCM-Based Coefficient Generator

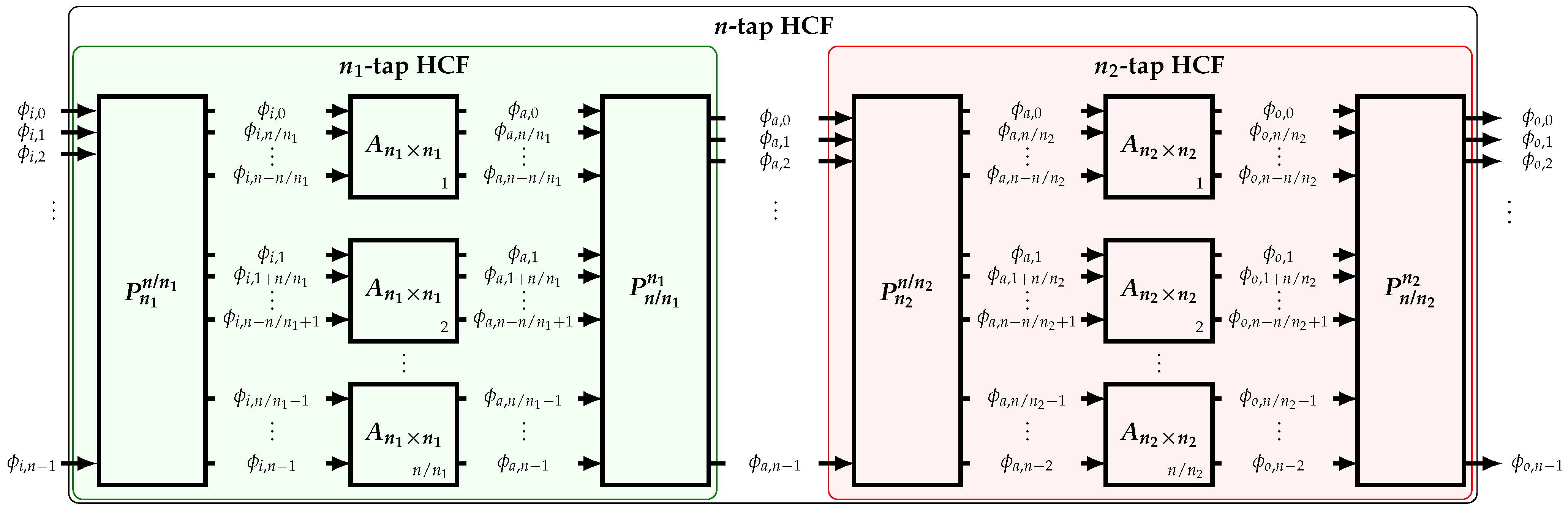

3.4. High-Order HCF

3.5. Band-Pass HCF

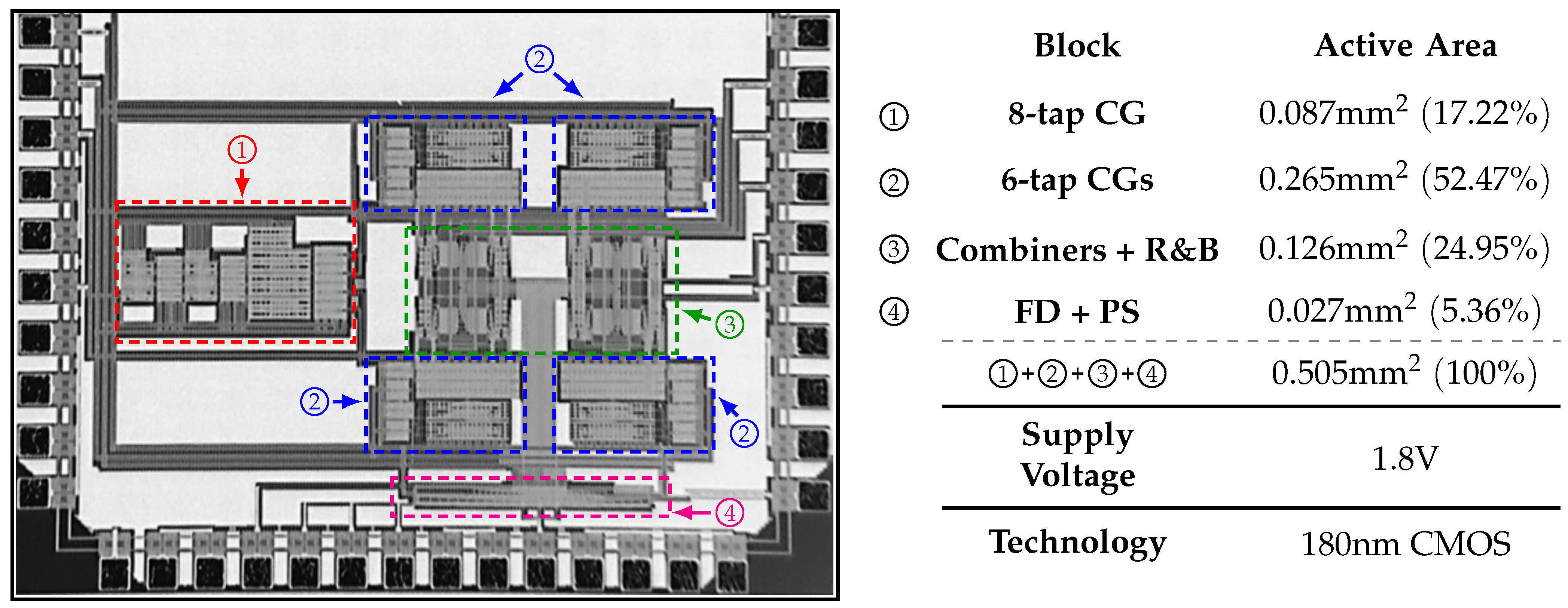

4. Circuit Implementation

4.1. System Architecture

4.2. Frequency Divider

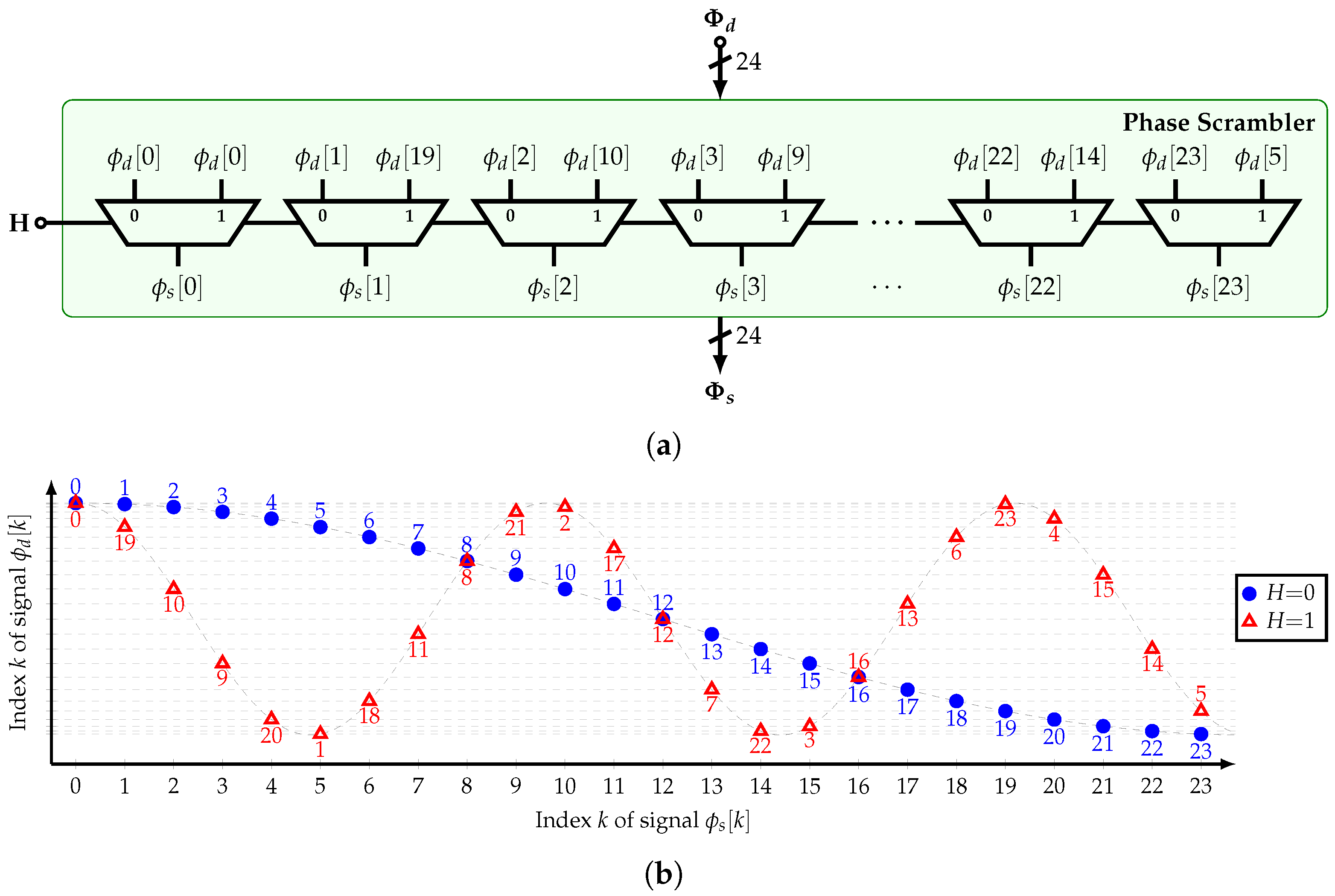

4.3. Phase Scrambler

4.4. Retimer and Buffer

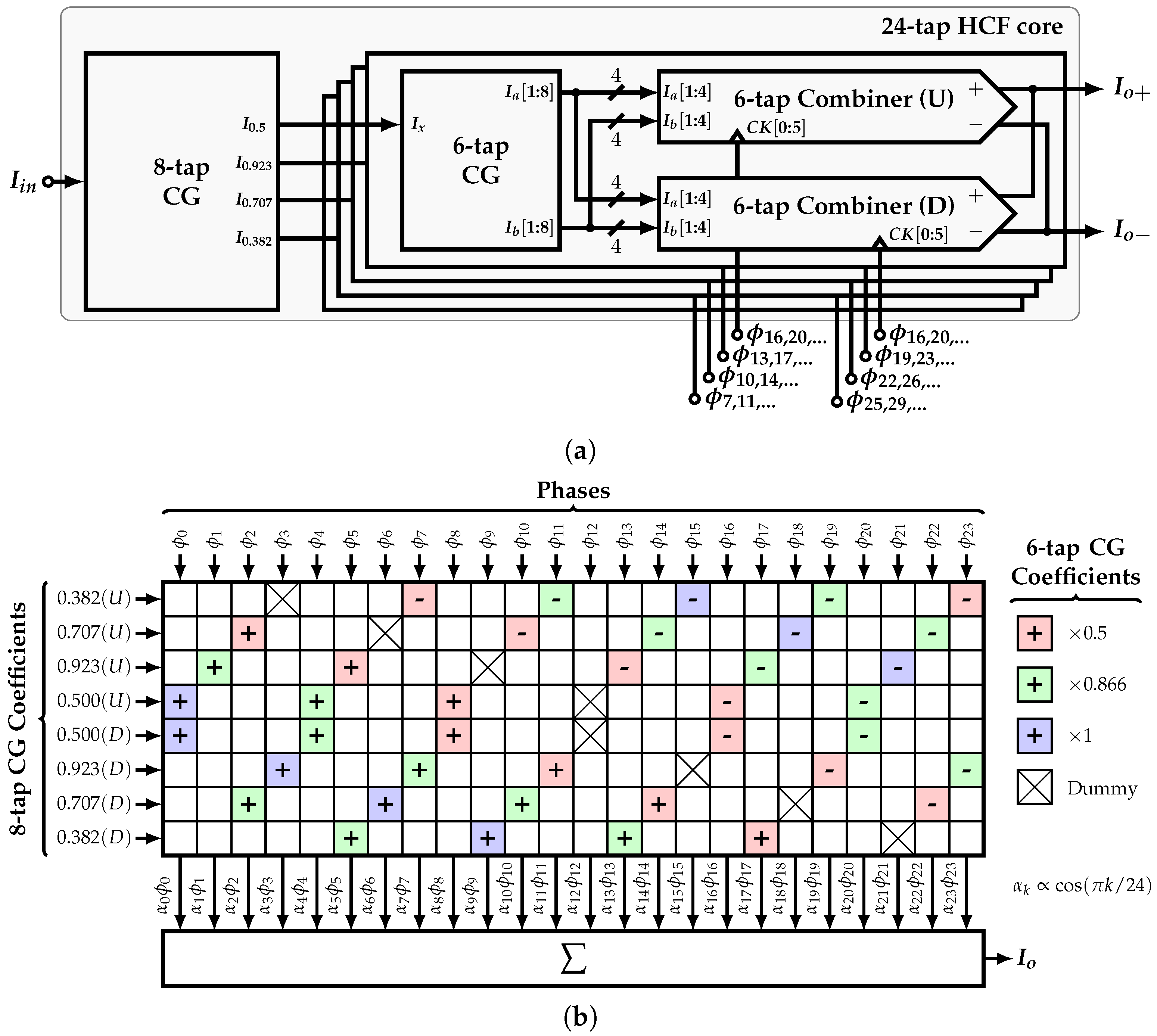

4.5. 24-Tap HCF Core

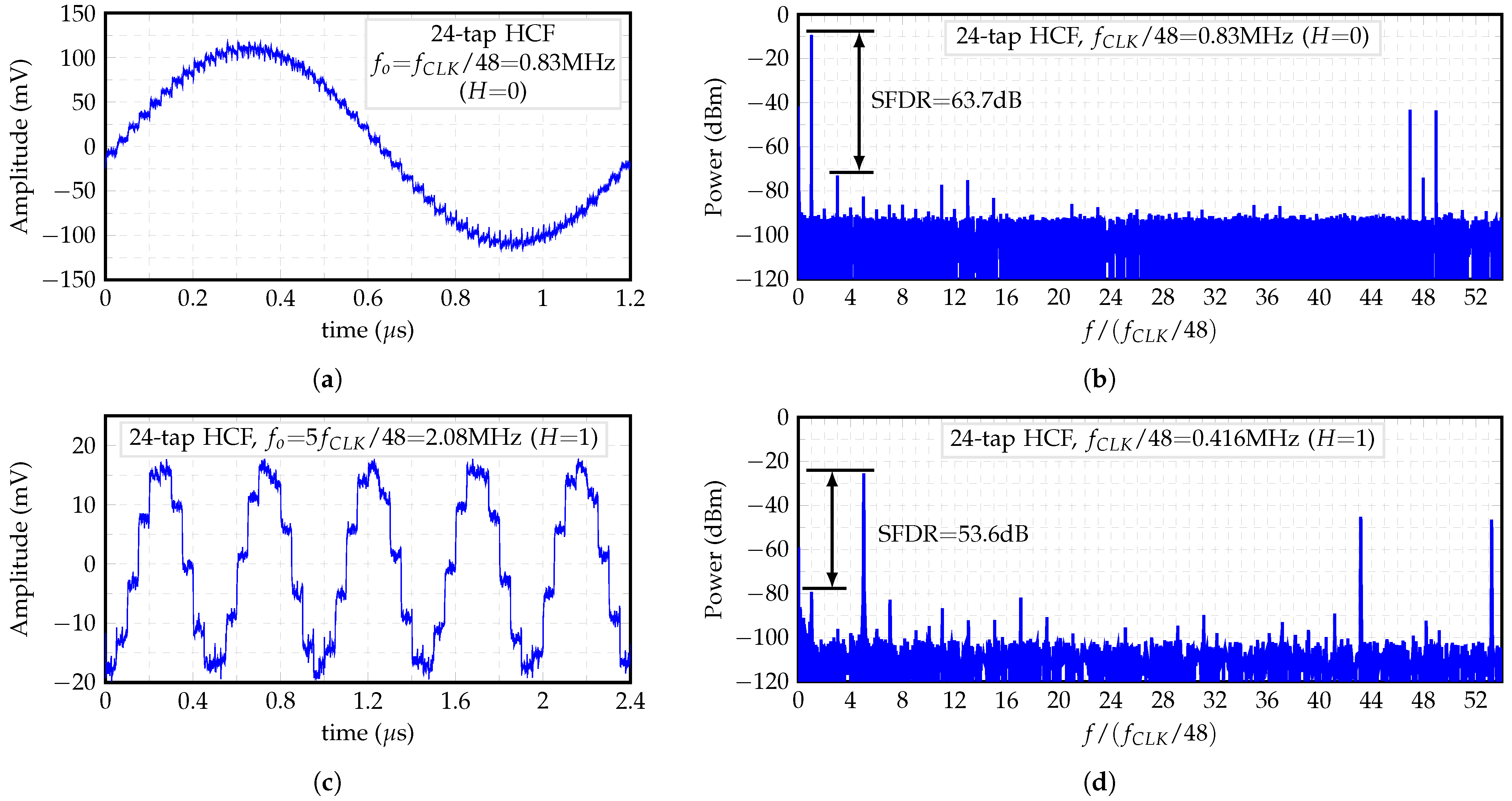

5. Measurement Results

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| BIST | Built-In Self-Test |

| HC | Harmonic Canceling |

| HCF | Harmonic-Canceling Filter |

| SCM | Skew-Circulant Matrix |

| SFDR | Spurious-Free Dynamic Range |

| DUT | Device-Under-Test |

| ADC | Analog-to-Digital Converter |

| THD | Total Harmonic Distortion |

| BPF | Band-Pass Filter |

| DDFS | Direct Digital Frequency Synthesizer |

| P2AM | Phase-to-Amplitude Mapping |

| CG | Coefficent Generator |

| SW | Square-Wave |

| CMOS | Complementary Metal-Oxide Semiconductor |

| CM | Current-Mirror |

| FD | Frequency Divider |

| PS | Phase Scrambler |

| R&B | Retimer and Buffer |

| NR | Not Reported |

| VCCS | Voltage-Controlled Current Source |

| DEM | Dynamic Element Matching |

Appendix A. Eigenvalues of the Even-Order SCM with Ideal (Irrational) HCF Coefficients

Appendix B. Eigenvalues of the Even-Order SCM with Non-Ideal (Integer) HCF Coefficients

Appendix C. Equivalence between a Cascade of Lower Order HCFs and a Higher Order HCF

References

- Stroud, C.E. An Overview of BIST. In A Designer’s Guide to Built-In Self-Test; Springer: Boston, MA, USA, 2002; pp. 1–12. [Google Scholar]

- Garayar-Leyva, G.G.; Osman, H.; Estrada-López, J.J.; Sánchez-Sinencio, E. A Harmonic-Canceling Synthesizer using Skew-Circulant-Matrix-Based Coefficient Generator. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar]

- Bahmani, F.; Sanchez-Sinencio, E. Low THD bandpass-based oscillator using multilevel hard limiter. IET Circuits Devices Syst. 2007, 1, 151–160. [Google Scholar] [CrossRef] [Green Version]

- Park, S.W.; Ausin, J.L.; Bahmani, F.; Sanchez-Sinencio, E. Nonlinear Shaping SC Oscillator With Enhanced Linearity. IEEE J. Solid-State Circuits 2007, 42, 2421–2431. [Google Scholar] [CrossRef] [Green Version]

- Mohieldin, A.N.; Emira, A.A.; Sanchez-Sinencio, E. A 100-MHz 8-mW ROM-less quadrature direct digital frequency synthesizer. IEEE J. Solid-State Circuits 2002, 37, 1235–1243. [Google Scholar] [CrossRef]

- Byung-Do, Y.; Choi, J.H.; Seon-Ho, H.; Lee-Sup, K.; Hyun-Kyu, Y. An 800-MHz low-power direct digital frequency synthesizer with an on-chip D/a converter. IEEE J. Solid-State Circuits 2004, 39, 761–774. [Google Scholar] [CrossRef]

- Yeoh, H.C.; Jung, J.; Jung, Y.; Baek, K. A 1.3-GHz 350-mW Hybrid Direct Digital Frequency Synthesizer in 90-nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 1845–1855. [Google Scholar] [CrossRef]

- Yoo, T.; Yeoh, H.C.; Jung, Y.; Cho, S.; Kim, Y.S.; Kang, S.; Baek, K. A 2 GHz 130 mW Direct-Digital Frequency Synthesizer with a Nonlinear DAC in 55 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 2976–2989. [Google Scholar] [CrossRef]

- Yang, C.; Weng, J.; Chang, H. A 5-GHz Direct Digital Frequency Synthesizer Using an Analog-Sine-Mapping Technique in 0.35-μm SiGe BiCMOS. IEEE J. Solid-State Circuits 2011, 46, 2064–2072. [Google Scholar] [CrossRef]

- Elsayed, M.M.; Sanchez-Sinencio, E. A Low THD, Low Power, High Output-Swing Time-Mode-Based Tunable Oscillator via Digital Harmonic-Cancellation Technique. IEEE J. Solid-State Circuits 2010, 45, 1061–1071. [Google Scholar] [CrossRef]

- Soda, M.; Bando, Y.; Takaya, S.; Ohkawa, T.; Takaramoto, T.; Yamada, T.; Kumashiro, S.; Mogami, T.; Nagata, M. On-chip sine-wave noise generator for analog IP noise tolerance measurements. In Proceedings of the 2010 IEEE Asian Solid-State Circuits Conference, Beijing, China, 8–10 November 2010; pp. 1–4. [Google Scholar]

- Barragan, M.J.; Leger, G.; Vazquez, D.; Rueda, A. On-chip sinusoidal signal generation with harmonic cancelation for analog and mixed-signal BIST applications. Analog. Integr. Circuits Signal Process. 2015, 82, 67–79. [Google Scholar] [CrossRef] [Green Version]

- Shi, C.; Sánchez-Sinencio, E. 150–850 MHz High-Linearity Sine-wave Synthesizer Architecture Based on FIR Filter Approach and SFDR Optimization. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2227–2237. [Google Scholar] [CrossRef]

- Aluthwala, P.D.; Weste, N.; Adams, A.; Lehmann, T.; Parameswaran, S. Partial Dynamic Element Matching Technique for Digital-to-Analog Converters Used for Digital Harmonic-Cancelling Sine-Wave Synthesis. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 296–309. [Google Scholar] [CrossRef]

- Malloug, H.; Barragan, M.J.; Mir, S. A 52 dB-SFDR 166 MHz sinusoidal signal generator for mixed-signal BIST applications in 28 nm FDSOI technology. In Proceedings of the 2019 IEEE European Test Symposium (ETS), Baden-Baden, Germany, 27–31 May 2019; pp. 1–6. [Google Scholar]

- Shi, C.; Sánchez-Sinencio, E. On-Chip Two-Tone Synthesizer Based on a Mixing-FIR Architecture. IEEE J. Solid-State Circuits 2017, 52, 2105–2116. [Google Scholar] [CrossRef]

- Ahmad, S.; Azizi, K.; Zadeh, I.E.; Dabrowski, J. Two-tone PLL for on-chip IP3 test. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 3549–3552. [Google Scholar]

- Méndez-Rivera, M.; Valdes, A.; Silva-Martínez, J.; Sanchez-Sinencio, E. An On-Chip Spectrum Analyzer for Analog Built-In Testing. J. Electron. Test. 2005, 21, 205–219. [Google Scholar] [CrossRef]

- Jose, A.; Jenkins, K.; Reynolds, S. On-chip spectrum analyzer for analog built-in self test. In Proceedings of the 23rd IEEE VLSI Test Symposium (VTS’05), Palm Strings, CA, USA, 1–5 May 2005; pp. 131–136. [Google Scholar]

- Shoghi, P.; Weldon, T.P.; Barnwell, C.J. Experimental results for a Successive Detection Log Video Amplifier in a single-chip frequency synthesized radio frequency spectrum analyzer. In Proceedings of the IEEE Southeastcon 2009, Atlanta, GA, USA, 5–8 March 2009; pp. 379–382. [Google Scholar]

- Nose, K.; Mizuno, M. A 0.016 mm2, 2.4 GHz RF signal quality measurement macro for RF test and diagnosis. In Proceedings of the 2007 IEEE Symposium on VLSI Circuits, Kyoto, Japan, 14–16 June 2007; pp. 212–213. [Google Scholar]

- Chauhan, H.; Choi, Y.; Onabajo, M.; Jung, I.S.; Kim, Y.B. Accurate and Efficient On-Chip Spectral Analysis for Built-In Testing and Calibration Approaches. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 497–506. [Google Scholar] [CrossRef]

- Choi, Y.; Chang, C.H.; Jung, I.S.; Onabajo, M.; Kim, Y.B. A built-in calibration system with a reduced FFT engine for linearity optimization of low power LNA. In Proceedings of the 2014 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Amsterdam, The Netherlands, 1–3 October 2014; pp. 222–227. [Google Scholar]

- Shi, C.; Sánchez-Sinencio, E. An On-Chip Built-in Linearity Estimation Methodology and Hardware Implementation. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 897–908. [Google Scholar] [CrossRef]

- Davies, A.C. Digital Generation of Low-Frequency Sine Waves. IEEE Trans. Instrum. Meas. 1969, 18, 97–105. [Google Scholar] [CrossRef]

- Gray, R.M. Circulant Matrices. In Toeplitz and Circulant Matrices: A Review; Now Publishers Inc.: Boston, MA, USA, 2006; pp. 31–34. [Google Scholar]

| Year | Tech. | (V) | Area (mm) | Coefficient Generation | HCF Order | Bypassed Harmonic | (MHz) | SFDR/-THD * (dBc) | Power (mW) | FoM | |

|---|---|---|---|---|---|---|---|---|---|---|---|

| @ (MHz) | @ (MHz) | ||||||||||

| This Work | 2022 | 180 nm CMOS | 1.8 | 0.505 | SCM-based | 6-tap | 1st | 0.8–60 | 66.4 @ 0.8 | 6.8 @ 0.8 | 1797 |

| 52.9 @ 60 | 19.1 @ 60 | ||||||||||

| 5th | 33–100 | 46.5 @ 33 | 6.1 @ 33 | ||||||||

| 38.4 @ 100 | 8.7 @ 100 | ||||||||||

| 12-tap | 1st | 0.8–32 | 64 @ 0.8 | 6.8 @ 0.8 | |||||||

| 53 @ 32 | 15.3 @ 32 | ||||||||||

| 5th | 8.3–75 | 43.7 @ 8.3 | 5.3 @ 8.3 | ||||||||

| 38.8 @ 75 | 8.7 @ 75 | ||||||||||

| 24-tap | 1st | 0.8–12.5 | 63.7 @ 0.8 | 6.9 @ 0.8 | |||||||

| 54.6 @ 12.5 | 13.3 @ 12.5 | ||||||||||

| 5th | 2–50 | 53.6 @ 2 | 5.1 @ 2 | ||||||||

| 46.2 @ 50 | 10.2 @ 50 | ||||||||||

| [15] | 2019 | 28 nm FDSOI | NR | 0.011 | VCCS + calib. + LPF | 6-tap | 1st | 1–333 | 41.5 @ 166.67 | NR | - |

| 52 @ 166.67 | |||||||||||

| [16] | 2017 | 130 nm CMOS | 1.2–1.5 | 0.056 | CM ratios | 12-tap | 1st | 0.01–1 | NR | 4 (single-tone) | - |

| [14] | 2017 | 130 nm CMOS | 1.2–1.5 | 0.066 | Unit-current switches + DEM | 4-tap | 1st | 2 | 69 | 0.94 | 840 |

| [13] | 2015 | 180 nm CMOS | 1.0–1.8 | 0.08 | Resistor-ratios + calibration + LPF | 6-tap | 1st | 150–850 | 50.5 @ 150 | ||

| 60.3 @ 150 | 9.1 @ 150 | 698 | |||||||||

| 47 @ 750 | 57.2 @ 850 | 6642 | |||||||||

| 70 @ 750 | |||||||||||

| [12] | 2015 | 180 nm CMOS | 1.8 | 0.04 | Capacitor ratios + LPF | 8-tap | 1st | 1.11 | 77 * | 3.24 | 938 |

| [10] | 2010 | 130 nm CMOS | 1.2 | 0.186 | N/A | N/A | 1st | 10 | 72 * | 4 | 716 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Garayar-Leyva, G.G.; Osman, H.; Estrada-López, J.J.; Moreira-Tamayo, O. Skew-Circulant-Matrix-Based Harmonic-Canceling Synthesizer for BIST Applications. Sensors 2022, 22, 2884. https://doi.org/10.3390/s22082884

Garayar-Leyva GG, Osman H, Estrada-López JJ, Moreira-Tamayo O. Skew-Circulant-Matrix-Based Harmonic-Canceling Synthesizer for BIST Applications. Sensors. 2022; 22(8):2884. https://doi.org/10.3390/s22082884

Chicago/Turabian StyleGarayar-Leyva, Guillermo G., Hatem Osman, Johan J. Estrada-López, and Oscar Moreira-Tamayo. 2022. "Skew-Circulant-Matrix-Based Harmonic-Canceling Synthesizer for BIST Applications" Sensors 22, no. 8: 2884. https://doi.org/10.3390/s22082884

APA StyleGarayar-Leyva, G. G., Osman, H., Estrada-López, J. J., & Moreira-Tamayo, O. (2022). Skew-Circulant-Matrix-Based Harmonic-Canceling Synthesizer for BIST Applications. Sensors, 22(8), 2884. https://doi.org/10.3390/s22082884