Abstract

This paper presents newly developed two high-precision CMOS proximity capacitance image sensors: Chip A with 12 μm pitch pixels with a large detection area of 1.68 cm2; Chip B with 2.8 μm pitch 1.8 M pixels for a higher resolution. Both fabricated chips achieved a capacitance detection precision of less than 100 zF (10−19 F) at an input voltage of 20 V and less than 10 zF (10−20 F) at 300 V due to the noise cancelling technique. Furthermore, by using multiple input pulse amplitudes, a capacitance detection dynamic range of up to 123 dB was achieved. The spatial resolution improvement was confirmed by the experimentally obtained modulation transfer function for Chip B with various line and space pattens. The examples of capacitance imaging using the fabricated chips were also demonstrated.

1. Introduction

Image sensors can capture two-dimensional distribution of physical quantities in the real world. There are various types of image sensors depending on the information to be acquired, such as optical image sensors that detect the intensity of light, and ToF image sensors that detect distance based on time differences. These image sensors are used not only in digital cameras for ornamental photography, but also in various fields to improve safety, security, and productivity, such as in-vehicle cameras for autonomous driving and machine vision cameras for factory automation [1,2,3].

Capacitance sensors can nondestructively measure the capacitance between a sensor and a target. By measuring the capacitance, it is possible to detect the presence or absence of an object near the sensor and the distance between the object and the sensor. It is used in noncontact switches, level sensors, continuous cell density measurement devices [4], and pressure sensors [5].

A proximity capacitance image sensor, which consists of an array of capacitance sensors, can detect and visualize two-dimensional distributions of capacitance between sensor and target. Unlike optical image sensors, these sensors can detect electrical connections as well as microstructures and minute irregularities on the surface of objects and distribution of substances inside organic, solid, and liquid materials. Because of these features, they are used in various applications such as wiring inspection for flat panel displays and printed circuit boards [6,7,8], fingerprint authentication [9,10,11,12], observation of cellular reaction processes [13,14], and so on. These applications require high detection precision of aF (10−18 F) or lower, as well as the ability to capture a sufficiently large area and a clear image of minute targets. For example, in fingerprint authentication, an area of about 1 cm2 is required to capture the entire fingerprint, and in wiring inspection, it is desirable to have as large a detection area as possible to efficiently inspect the entire large area of the substrate. In addition, a resolution on the order of µm is necessary for wiring inspection of high-resolution displays with fine wiring and for cell observation. Furthermore, it is desirable to have a wide dynamic range performance that can capture a wide range of capacitance in a single image.

There are several methods of detecting capacitance, such as those that convert capacitance to frequency [13], current [9,10,11], or voltage [6]. In the method of converting the capacitance to frequency or current, it is difficult to reduce the pixel pitch and to detect the capacitance with high precision due to its circuit configuration. Therefore, in this work, we adopted the method of converting to voltage, which has a simple circuit structure, to realize high-precision detection in minute pixels.

Previous works have reported discrete sensors with aF-order detection precision [13,15,16] and an array sensor with a detection area of 8.73 cm2 with 11.4 µm pitch pixels [6]. Previously, we have presented a prototype CMOS proximity capacitance image sensor with 256H × 256V 16 µm pitch pixels achieving 100 zF detection precision due to an advanced noise cancelling technique [17,18,19,20,21,22]. However, the simultaneous achievement of a detection precision of less than aF and a detection area of more than 1 cm2, or a pixel pitch of less than 10 μm toward a higher resolution, has not been reported yet.

In the paper of IISW 2021 [23], we presented two newly developed chips for increasing imaging area and spatial resolution: Chip A with large format 12 µm pixels for practical inspection applications and Chip B with high-resolution 2.8 µm pitch pixels. Large-area and high-resolution capacitance detection with a precision of less than 1 aF by using these two chips has been demonstrated. In this paper, we additionally describe the more detailed design and characterization results, calculation and verification results of the detection precision, and the measurement results of the resolution using the modulation transfer function analysis. Furthermore, examples of images for wiring inspection applications will be presented.

2. Design and Structure of Developed Chips

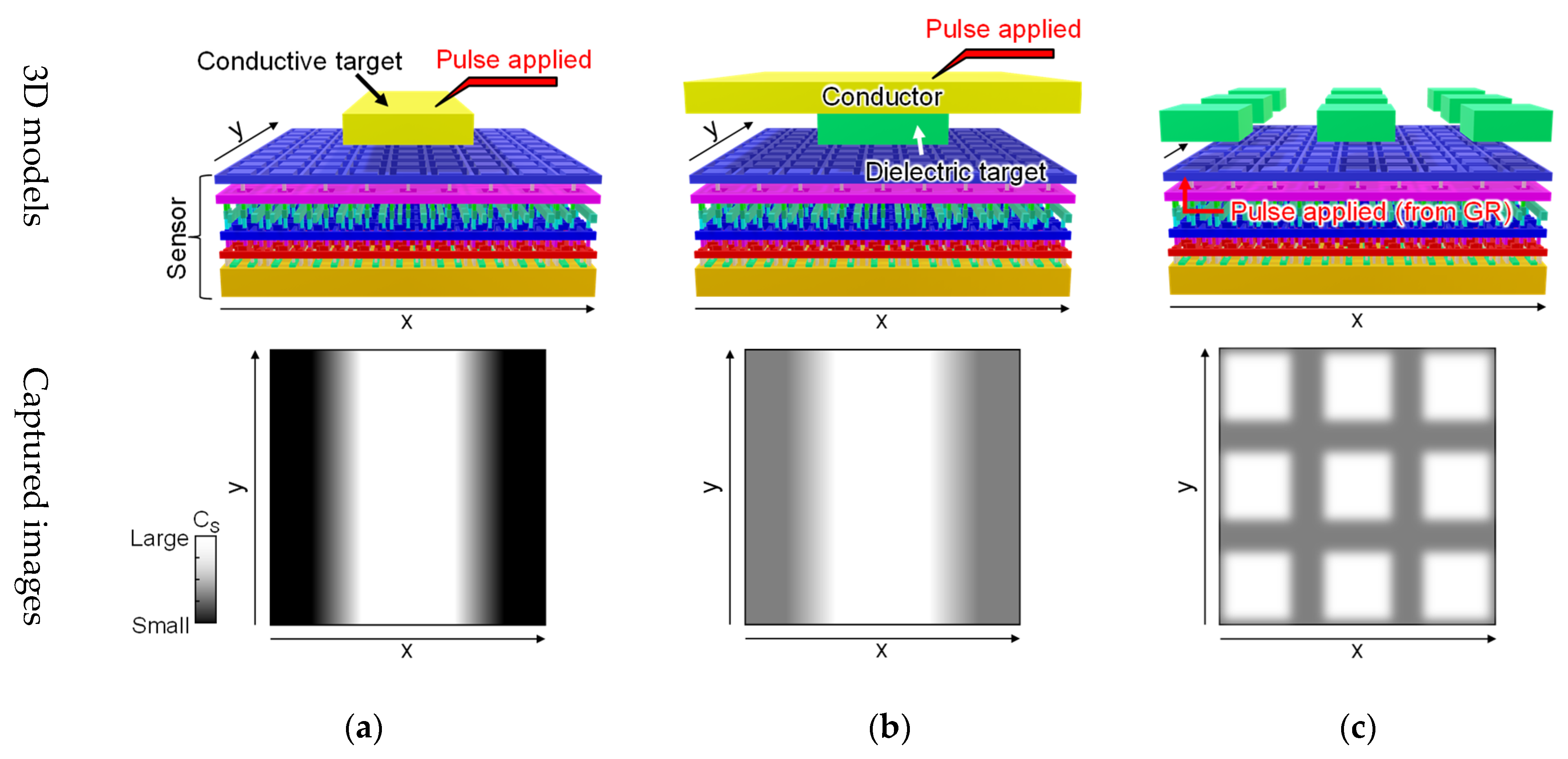

Figure 1 shows 3D models illustrating the proximity capacitance imaging setup and the images captured for each target. For the proposed proximity capacitance sensors, a counter electrode was introduced to which the input pulse signal was supplied. For a conductor target, the input pulse signal was supplied by a probe and the target itself was used as the counter electrode, as in Figure 1a. It was also possible to measure proximity capacitance without a probe by supplying the input pulse signal through a coupling capacitance between the target and the counter electrode in the chip. For a dielectric target, the measurement was performed by placing a flat counter electrode and supplying an input pulse signal to it, as in Figure 1b. For particle targets, measurement was performed by using the guard ring in the sensor as a counter electrode and supplying the input pulse signal to it, as in Figure 1c. By using an appropriate measurement method, various targets could be measured.

Figure 1.

The 3D models of the sensor and the target, and the captured images for each target: (a) conductive target; (b) dielectric target; (c) particulate targets.

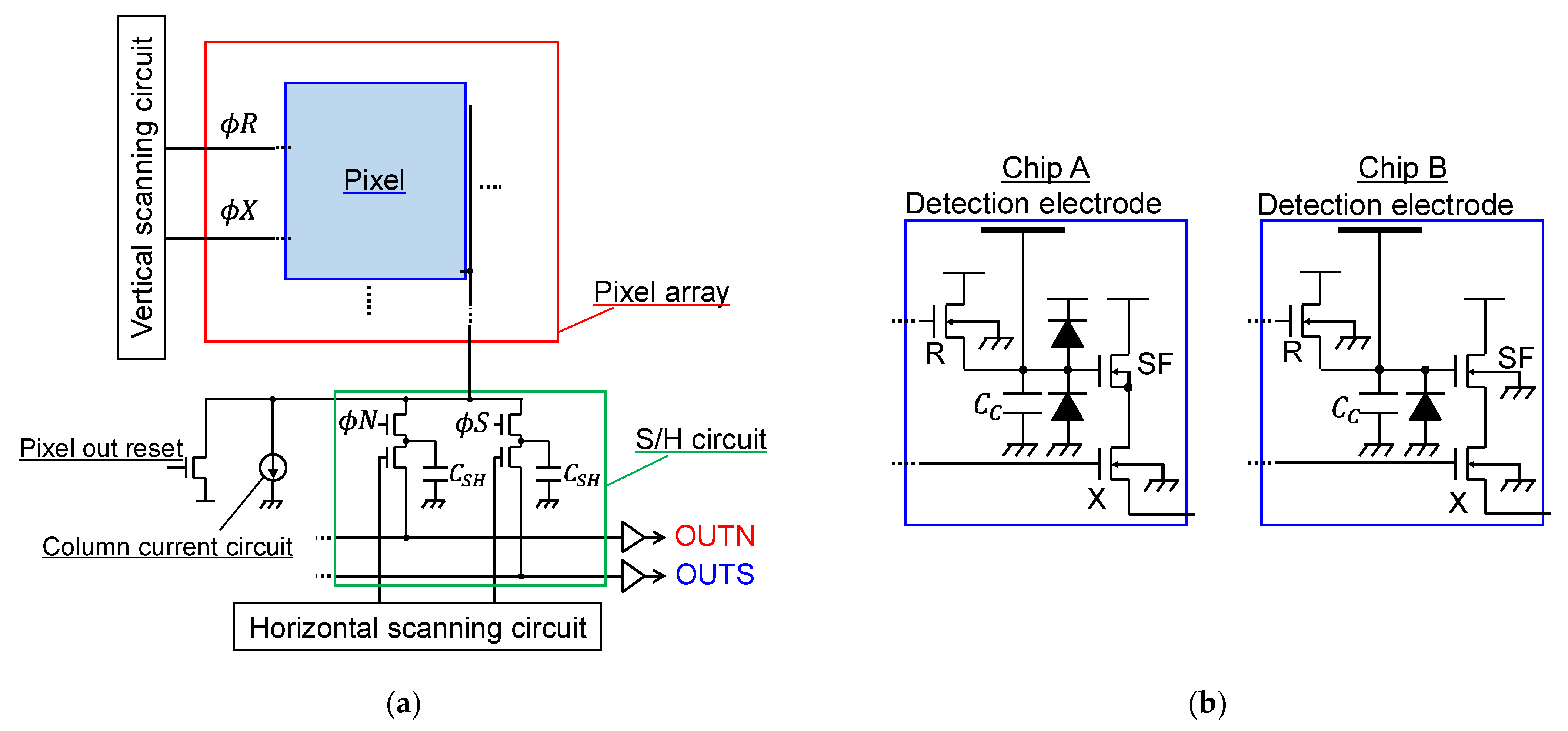

Figure 2 shows the circuit block diagram of the developed chips. A schematic of the overall circuit is shown in Figure 2a, which employed the rolling shutter method used in general CMOS image sensors. When capturing an image, the vertical scanning circuit first selected a row to acquire the signal for one row, then, the column S/H circuit held the signal, and the horizontal scanning circuit selected a column to read the analog signal out of chip in turn. Here, the signal was readout from the column S/H circuit to the horizontal signal readout lines by capacitive charge division operation. The analog output signal was digitized by on-board ADC with 20 MHz signal sampling rate. This was repeated for all the rows to obtain the signals for one frame. In this way, high-speed and low-noise readout was achieved. As shown in Figure 2b, the pixel circuits were equipped with a capacitance detection circuit using a capacitance–voltage conversion method, and consisted of a detection electrode, a reset transistor (R), an SF transistor (SF), a select transistor (X), a protection diode, and detection electrode parasitic capacitance (CC). Chip A used an isolated P-well in a deep N-well for the SF transistor, which was to improve the gain and extend the linear range of the SF by eliminating the substrate bias effect. It also allowed the formation of a PN protection diode for the high-voltage side. Chip B, on the other hand, used a normal SF transistor structure and removed the protection diode for the high-voltage side to reduce the layout area and greatly reduce the pixel pitch. Furthermore, by using only one type of protection diode, it was possible to calculate CC from the photon transfer curve using the parasitic light sensitivity of the protection diode [24].

Figure 2.

The schematics of the two chips: (a) the circuit block diagram; (b) the circuit schematic of the pixels.

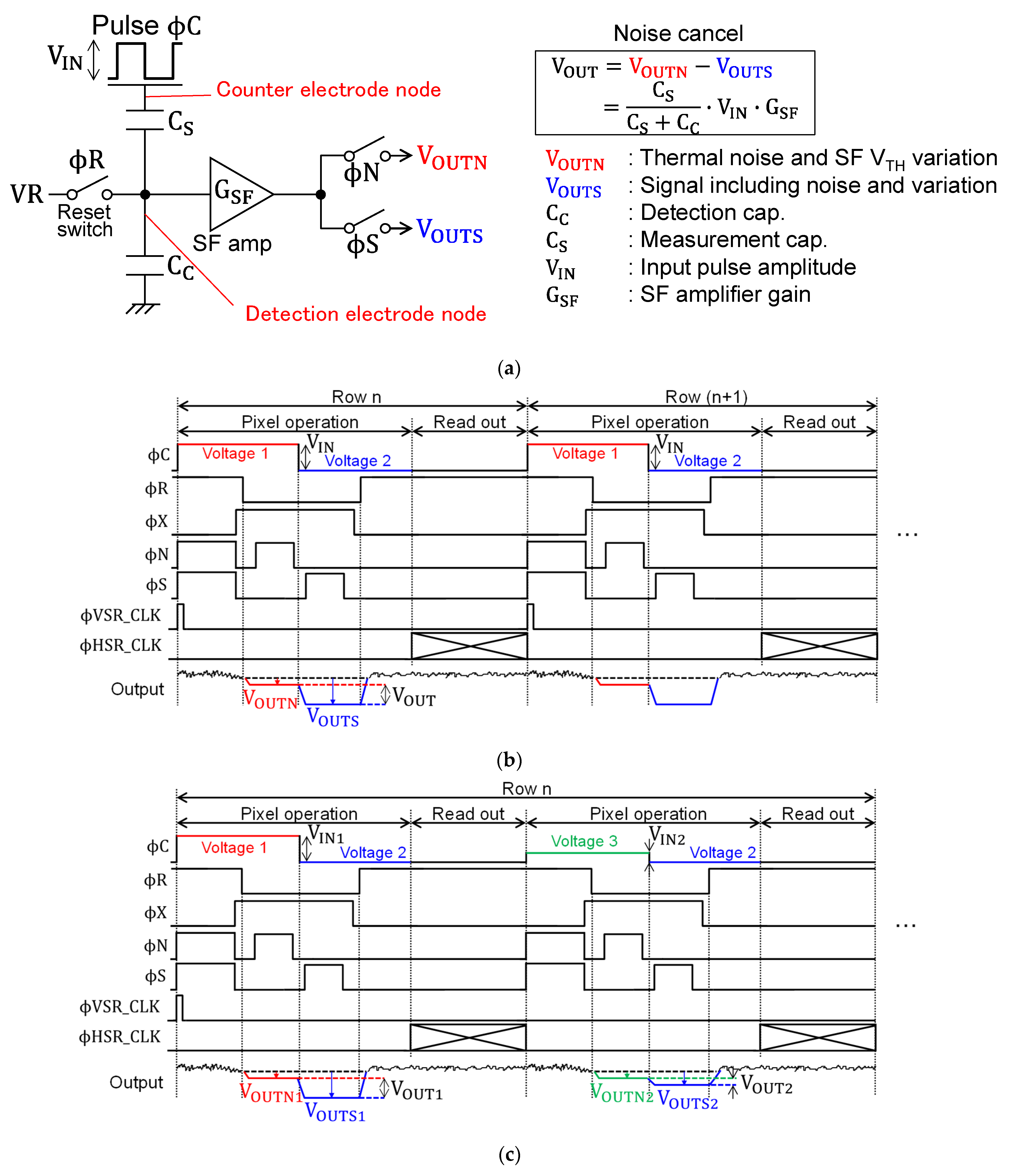

Figure 3 shows a simplified sensor circuit and operational timing diagrams of the normal and the high dynamic range (HDR) modes. As shown in Figure 3a, each pixel contained detection electrode capacitance (CC) which was connected to the measurement capacitance (CS) in series. When detecting the capacitance, the detection electrode node in the pixel was reset by the reset switch, φC was applied, and the voltage of the floating detection electrode node was read out by the SF amplifier. After resetting and turning off the reset switch, thermal noise remained at the detection electrode node. It was due to the thermal fluctuations of the charge, and it was random in time. Therefore, every time the reset switch was turned off, the voltage at the detection electrode node was changed, which appeared as temporal random noise (RN) in the output signal without noise cancelling. Furthermore, since the threshold voltage of the SF transistor used for readout varies from pixel to pixel, the gain and offset values also varied from pixel to pixel. This was to appear as a fixed pattern noise in the image without noise cancelling. These noises degraded the precision of capacitance detection.

Figure 3.

Principle of operation of proximity capacitance image sensor: (a) simplified circuit and noise cancelling principle; (b) timing diagram of normal mode; (c) timing diagram of HDR mode.

In this work, a noise-cancelling technique was introduced to reduce these noises and achieved high-precision capacitance detection. Figure 3b shows the pulse timing diagram in the normal mode with the noise cancelling technique applied. First, the counter electrode was set to the first voltage by φC, and φR was turned on to reset the detection electrode node. Then, when φR was turned off, thermal noise remained in the detection electrode node. At this time, the voltage of the detection electrode node was read out by the SF amplifier with φN turned on and was designated as VOUTN. After that, when the counter electrode was changed to the second voltage level, the voltage of the detection electrode in the floating state changed according to the ratio of CC and CS and the input pulse amplitude VIN. Then, φS was turned on and read out, the voltage of the detection electrode node used the same SF amplifier as the S signal, and the result was VOUTS. VOUTN included noise components such as thermal noise and VTH variation, and VOUTS included signal components superimposed on them. Finally, by taking the difference between VOUTN and VOUTS, only the signal component with noise component removed could be obtained. The output VOUT was expressed by the following Equation (1).

Here, the proximity capacitance signal (VOUT) is proportional to the voltage amplitude (VIN) applied to the counter electrode. For the chips presented in the paper, VOUTN and VOUTS were readout to the column S/H circuit during the pixel operation period, then, these signals were readout in parallel using the two horizontal signal lines and output buffers as described in Figure 2a. An on-board differential ADC was employed to achieve signal subtraction of VOUTN and VOUTS and digitize the VOUT. Since VOUTN and VOUTS were output in parallel, the noise canceling did not impact the horizontal signal readout period. The additional operation time by the introduced noise canceling was only the signal readout time of VOUTN during the pixel operation period, and it was about eight microseconds or fewer per one row. The larger the applied VIN, the smaller the CS detected, but if the CS was large, the signal output would saturate beyond the signal readout range of the chips. In HDR mode, as shown in Figure 3c, the third voltage was used in addition to the first and second voltages, and two types of signals could be obtained by applying large and small VIN to each row. This made it possible to capture the region with small CS and large CS simultaneously. Therefore, it was possible to expand the dynamic range of the detection capacitance compared to that of the normal mode with one type of VIN.

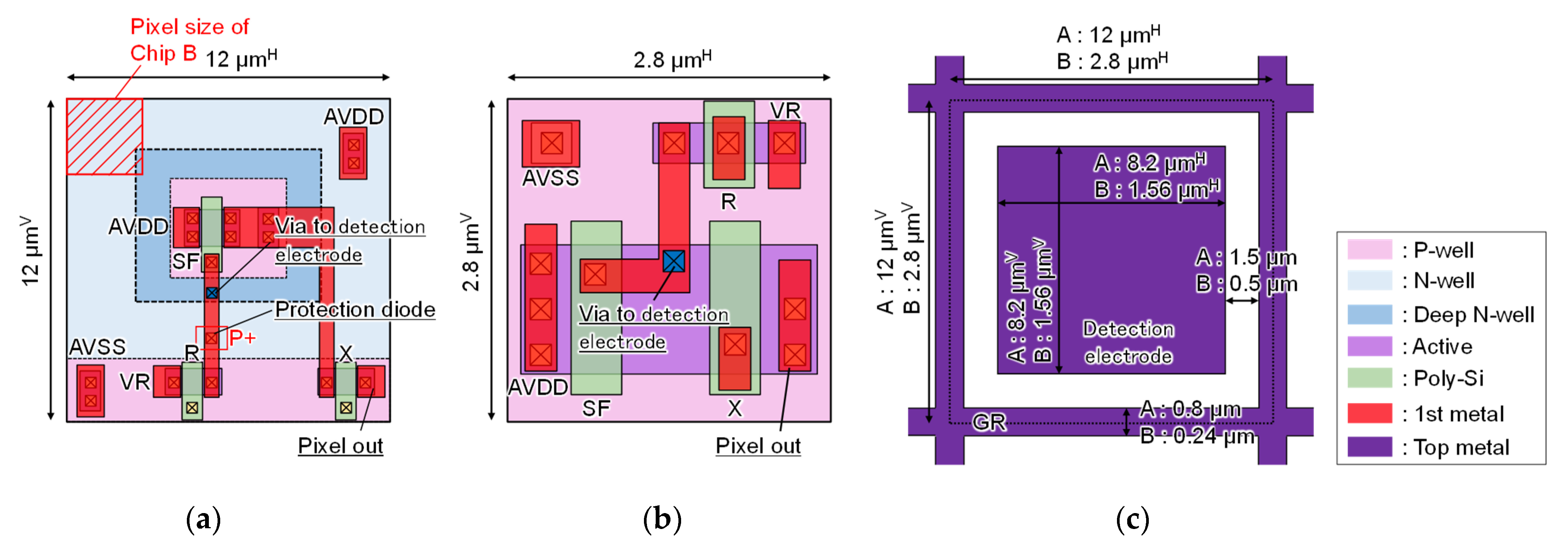

Figure 4 shows the layout diagrams of the developed pixels, Figure 4a for Chip A and Figure 4b for Chip B, up to the first metal layer. The pixel of Chip A had a 12 μm pitch, a well-in-well structure for the SF transistor, and an N+P protection diode. The pixel of Chip B had a pitch of 2.8 μm and used a standard p-well structure for the SF transistor. In addition, in both pixels, the source of the reset transistor was used as an N+P protection diode. Figure 4c shows the top metal layout of both chips. The center was the detection electrode, which was connected to the gate of the SF transistor on the lower layer through vias. Typically, the guard ring around the detection electrode was connected to the GND, which suppressed the crosstalk of the electric field between adjacent pixels and improved the resolution. It was also possible to detect capacitance by applying φC directly from the guard ring without using an external probe. Additionally, strict light shielding was used to suppress the light effect during capacitance detection. The value of Cc was determined by the parasitic capacitance with respect to the detection electrode. Thus, control of the parasitic capacitance in the pixel was very important in the developed sensors. In order to minimize Cc to improve the sensitivity, the metal wiring layout was carefully designed to reduce the parasitic capacitance.

Figure 4.

The pixel layout diagrams of the two chips: (a) up to the 1st metal layer of Chip A; (b) up to the 1st metal layer of Chip B; (c) the top metal layer.

3. Chip Fabrication and Measurement Results

Figure 5 shows the micrographs of the fabricated chips. A 0.18 µm 1-poly-Si 5-metal CIS technology was employed. The chip size, number of pixels, and pixel pitch were 14.4 × 14.4 mm2, 1080H × 1080V, and 12 µm for Chip A, and 4.8 × 4.8 mm2, 1408H × 1280V, and 2.8 µm for Chip B, respectively. Chip B had an on-chip counter electrode to apply φC through the coupling capacitance to the conductive target.

Figure 5.

The micrograph of the fabricated CMOS proximity capacitance image sensors: (a) Chip A; (b) Chip B.

Figure 6 shows the cross-sectional pixel TEM images of the two chips. The first through the fourth metal layer was used for wiring and light shielding, and the fifth metal on the top layer was used as a detection electrode and guard ring. The detection electrode was protected by a passivation film, and the detection electrode and transistor were connected through vias.

Figure 6.

The cross-sectional pixel TEM image of the two chips: (a) Chip A; (b) Chip B.

Figure 7 shows the measurement system. It consisted of a headboard with a fabricated sensor chip mounted face-up, an analog front-end (AFE) circuit board with voltage regulators and a 14-bit differential ADC directly connected to VOUTN and VOUTS, a FPGA board to supply operation pulses to the sensor chip, and a PC. A function generator was used to apply φC to the counter electrode, and a trigger signal was input from the FPGA to synchronize with the sensor operation. The function generator alone could generate φC up to VIN = 20 V, and the sensor was measured at a maximum of VIN = 300 V using a high-speed high-voltage amplifier.

Figure 7.

The measurement system for characterizing the performance of fabricated sensor chips: (a) picture; (b) block diagram.

Figure 8 shows examples of chip assembly methods: Figure 8a is the assembly into a ceramic package using bonding wires. This was the simplest assembly method, and the capacitance was detected by placing a target directly in proximity to the sensor surface. In Figure 8b, the chip in Figure 8a, except for the pixel area, was encapsulated with a thermoplastic resin. The resin protected bonding wires and created a bank outside the pixel area of the chip, which enabled capacitance detection of liquid or particulate targets. Image Figure 8c shows the assembly using a polyimide film and flexible wiring. In this method, the chip surface and wiring were protected, and the sensor surface could be made flat, so that capacitance could be detected for large-area targets such as fingerprints and flat-panel displays.

Figure 8.

Various assembly methods of the sensor chips: (a) ceramic package with bonding wires; (b) resin potting; (c) polyimide film with flexible wires.

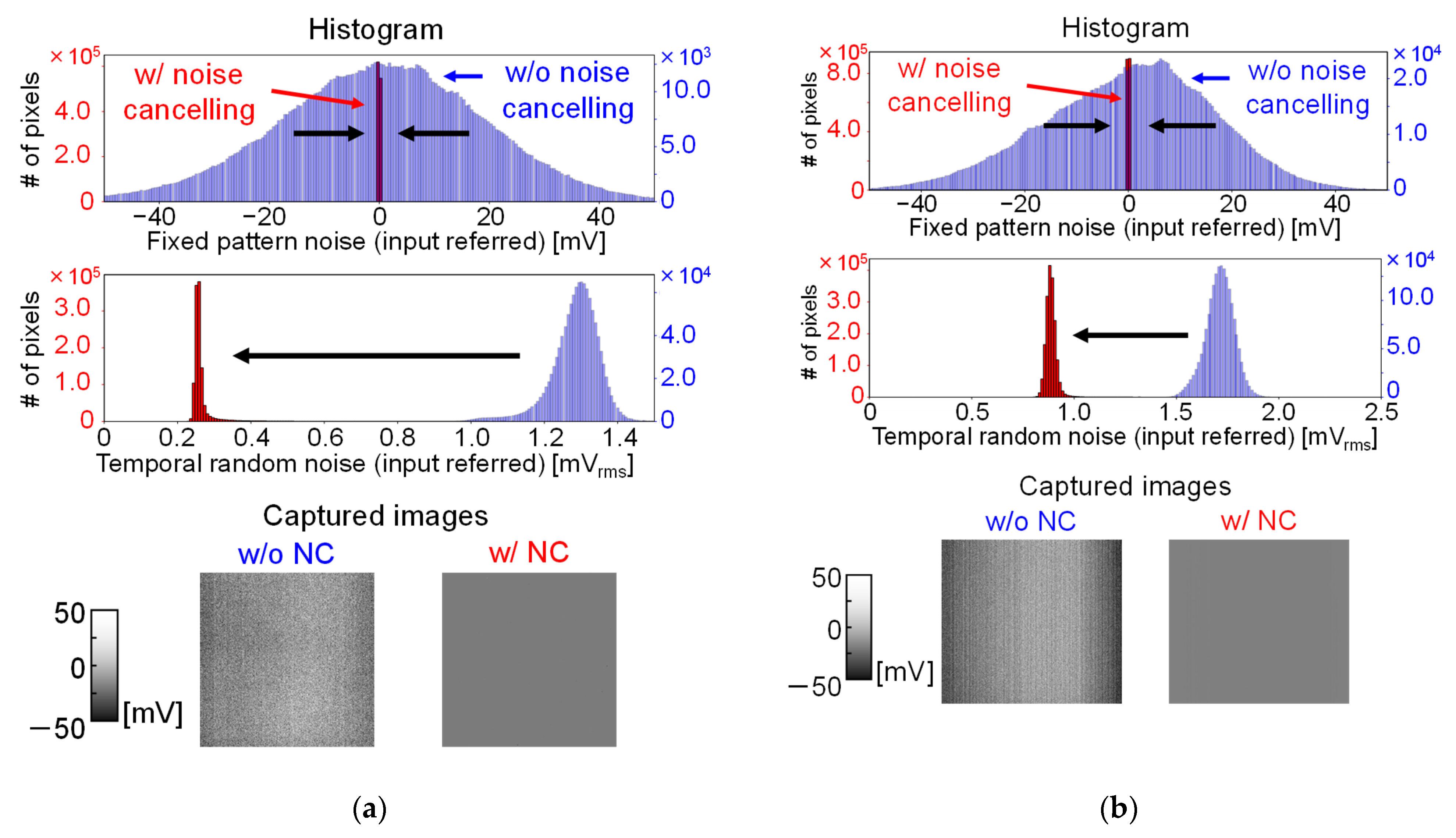

Figure 9 and Table 1 show the measured noise characteristics without any measurement targets obtained without and with the noise cancelling. Without the noise cancelling, the input referred fixed pattern noise and temporal random noise arose mainly due to the threshold voltage variation of SF and column fixed pattern noise, and the kTC noise at the detection electrode node. Without noise cancelling and averaging, VFPN and VRN were 19.3 and 1.29 mVrms, respectively for Chip A and 16.4 and 1.71 mVrms for Chip B, respectively. For Chip B, the histogram of the FPN was not symmetrical. It was considered that this asymmetrical noise histogram was due to the column FPN and shading appearing in the image without noise canceling. We considered that the cause of the column FPN and the shading were due to the IR drop of the VSS node, which induced the variation of the current for the column current sources. When noise cancelling technique was applied here, the noise was significantly reduced to 37.8 and 267 µVrms for Chip A and 137 and 887 µVrms for Chip B, respectively. The column FPN and shading were also cancelled in this readout operation. Furthermore, by averaging multiple frames, the RN decreased in inverse proportion to the square root of the number of averaged frames and could be reduced to about 1/10 when 100 frames were averaged. We thus achieved high detection precision with the noise cancelling technique and confirmed further precision improvement by averaging multiple frames.

Figure 9.

Captured images without and with noise cancelling and their histograms in the absence of targets: (a) Chip A; (b) Chip B.

Table 1.

Measured noise value of the two chips.

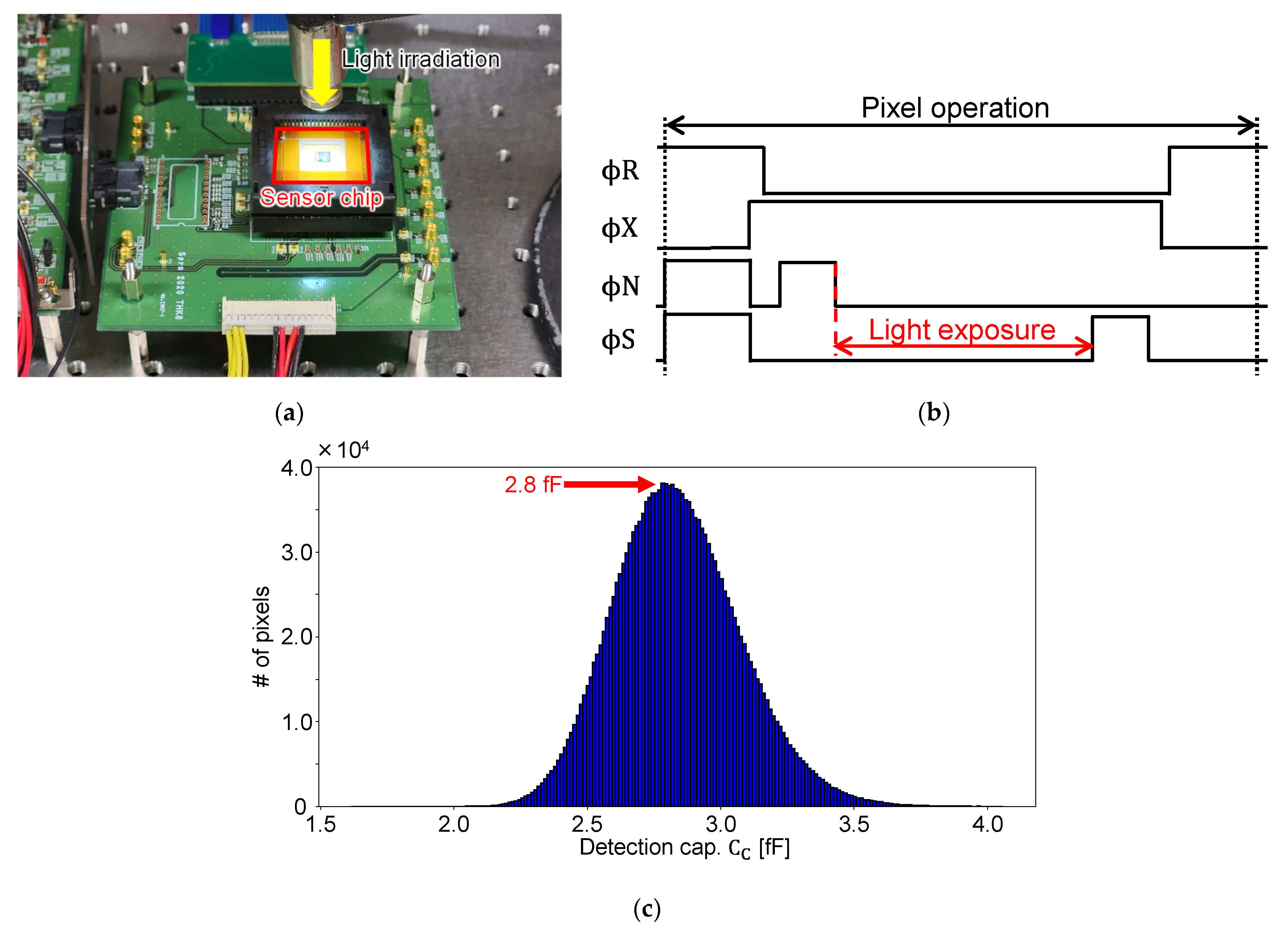

In the proximity capacitance image sensor of this work, an input–output relation expressed in Equation (1) indicated that the capacitance value of CC must be obtained to calculate CS. Therefore, two methods were used to calculate the capacitance value of CC: one by simulation and the other by measurement using the fabricated chip. In the first method, for both chips, the parasitic wire capacitance of the wiring was extracted from the post-layout simulation, and the parasitic capacitance of the transistors was calculated from AC analysis results. In the second method, the photoelectric conversion characteristics were measured from the parasitic light sensitivity in the protection diodes in the pixels using the fabricated chip, and the capacitance value was calculated from the photon transfer curve (PTC). The calculation from this measurement could be done only with Chip B, which had only one protection diode type. We utilized this protection diode as a pixel photodiode. This measurement method is shown in Figure 10a,b. The measurement was performed by irradiating a high-intensity light from near the front of the chip, as shown in Figure 10a. Since the diffusion layer in the pixel was shielded by the metal wiring layer, no optical signal could be obtained when it was operated normally as a capacitance sensor. However, as shown in Figure 10b, by expanding the exposure time significantly and the time between N and S sampling, it was possible to obtain an optical signal sufficient for measurement from the parasitic light sensitivity. Image Figure 10c shows the histogram of CC for Chip B obtained by the measurement and the values of CC for both chips. During this experiment, no counter electrode signal was provided, and we assumed that the value of Cs was negligibly small in comparison to Cc. From the measurement, we obtained a CC of 2.8 fF for Chip B, which was close to the extracted value of 2.5 fF. The extracted value by the simulation agreed well with the measured one, indicating the parasitic capacitance extraction was accurately conducted. For Chip A, the value of 5.4 fF was obtained from the simulation.

Figure 10.

Measurement to determine the capacitance value of CC: (a) sensor chip irradiated with light; (b) pulse timing; (c) histogram of measured CC of Chip B and CC values of the two chips.

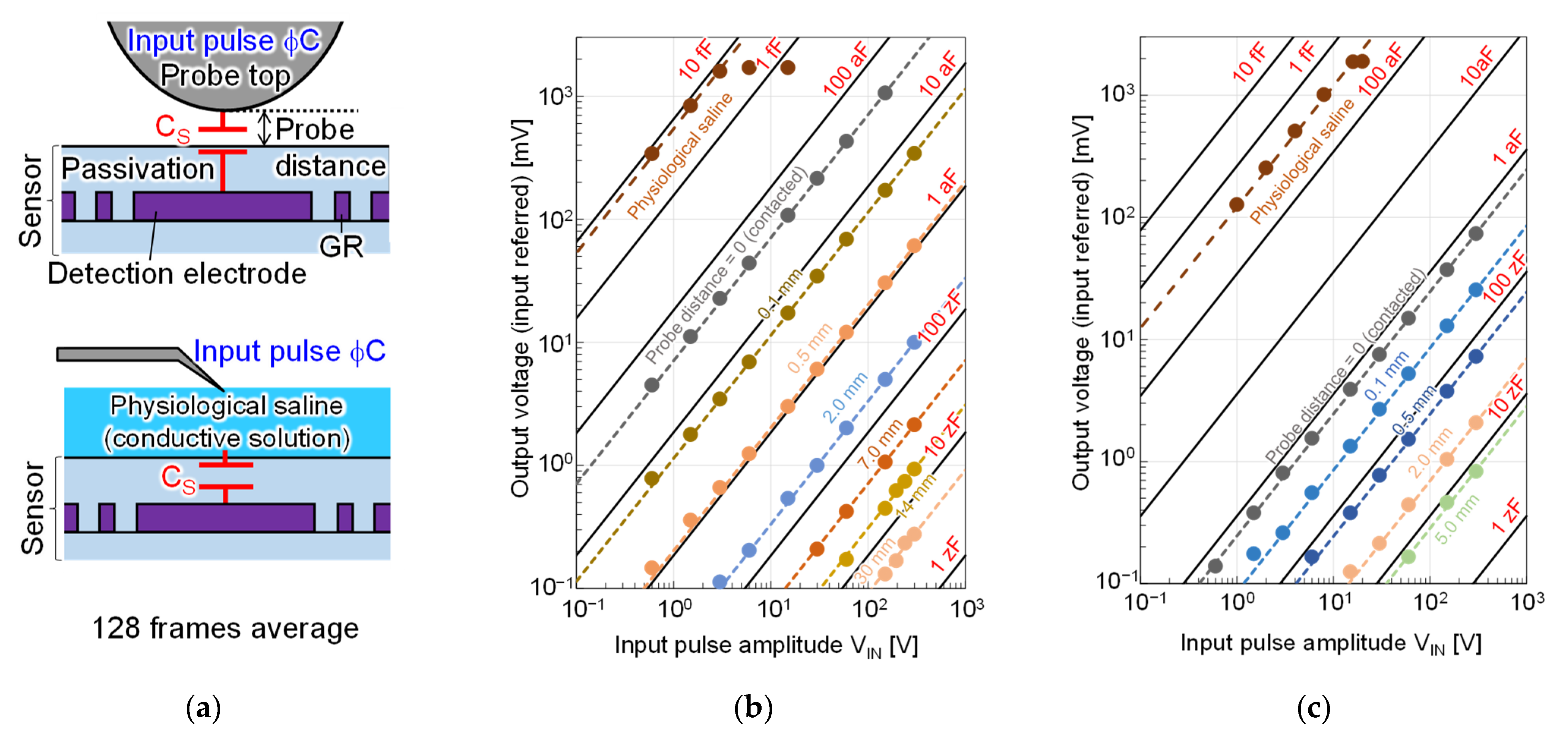

Figure 11 shows the measured transfer characteristic of the two chips with various measurement capacitance conditions. As shown in Figure 11a, the measurements were performed by changing the distance between the chip surface and the probe, which was the counter electrode, or by dropping saline, which was a conductor, on the chip surface. Image Figure 11b shows the measurement results of Chip A, and Figure 11c shows the measurement results of Chip B. Here, the signal output was plotted as a function of the voltage amplitude of the input pulse. Colored dots show the measured values, and the black lines are the calculated characteristics at each capacitance value, using Equation (1) and the CC obtained from the simulation and the measurement for the Chips A and B, respectively. The measurement results show that the input referred signal range was confirmed to be over 1.0 V with good linearity for both chips. Chip A achieved a lower limit of detection capacitance of 70 zF when VIN was 20 V, which was confirmed to be safe when applied with a target in contact with the chip surface or applied to the human body, and 5 zF when VIN was 300 V, which was the maximum voltage that can be applied in the measurement system used. By adjusting VIN in the range below 300 V, a wide dynamic range of 123 dB from 5 zF to 6.9 fF, which is the limit determined by the structure, was shown. The highest SNR was 76 dB. Similarly, Chip B was shown to achieve a lower limit of detection capacitance of 100 zF at VIN of 20 V and 8 zF at 300 V, with a dynamic range of 94 dB from 8 zF to 0.4 fF and a maximum SNR of 61 dB.

Figure 11.

Measured transfer characteristics of the two chips: (a) measurement methods; (b) Chip A; (c) Chip B.

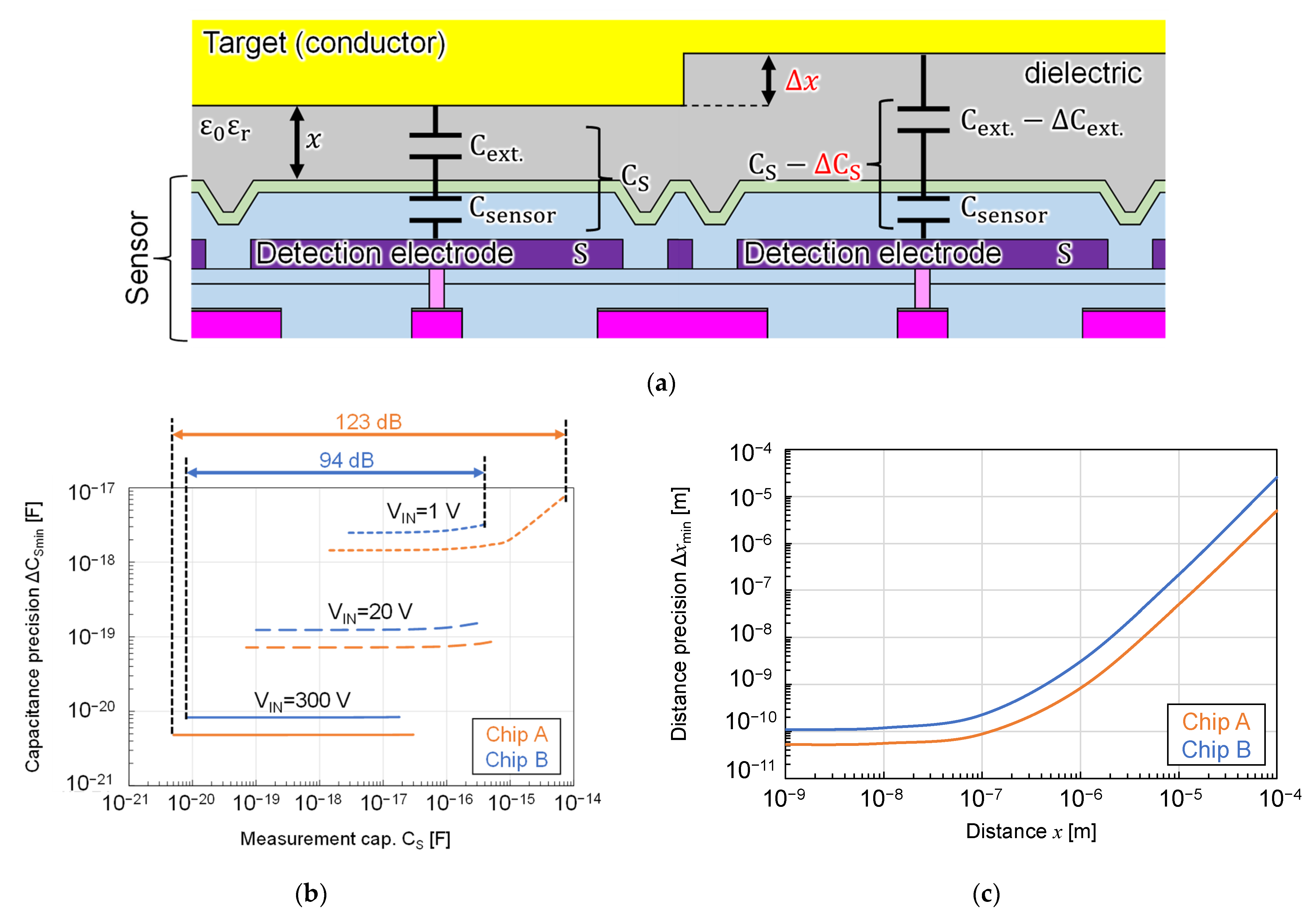

The detection precision of the sensors was calculated from the noise and CC values and transfer characteristics obtained so far. Figure 12a shows the cross-sectional diagram of the chip surface and the conductive target. Assume that a capacitance CS was formed between the detection electrode and the target when the distance between the chip surface and the target was x. When CS became smaller by ΔCS, the minimum ΔCS that could detect this small change was determined by the capacitance detection precision ΔCSmin. This ΔCSmin can be expressed as the following Equation (2). It assumed that the capacitance could be measured when its signal was larger or equal to the noise level.

Figure 12.

Calculation of capacitance and distance detection precision: (a) cross-sectional schematic diagram of a chip surface and a conductor target with small irregularities; (b) calculation results of the relation between the measurement capacitance CS and the capacitance detection precision ΔCSmin at each input voltage VIN; (c) relation between the reference distance x between the chip surface and the target and the distance detection precision Δxmin.

From this equation, we can see that ΔCSmin varies with ΔCS. Image Figure 12b shows the relation between CS and ΔCSmin at each VIN of both chips calculated using the values obtained so far. From this graph, we can see that as CS became smaller, ΔCSmin also became smaller, and when CS was sufficiently small, ΔCSmin became constant and almost equal to the capacitance detection lower limit. Therefore, the maximum capacitance detection precision of Chip A was 70 zF when VIN was 20 V and 5 zF when VIN was 300 V, and that of Chip B was 100 zF when VIN was 20 V and 8 zF when VIN was 300 V. The plotted range at each VIN corresponded to the detectable capacitance range. The lower limit of the capacitance detection range was determined by the chip noise level, while the upper limit was determined by the signal range of the chip or the distance and electro permittivity between the detection electrode and the measurement target, whichever was smaller.

Next, consider the distance detection precision. As shown in Figure 12a, CS could be seen as a composite capacitance Csensor from the detection electrode to the chip surface, which was calculated from the passivation film thickness, and capacitance Cext. from the chip surface to the object. The distance detection precision Δxmin was the minimum Δx at which this distance change could be detected as a capacitance change when x increases by Δx. This Δxmin can be expressed as the following Equation (3).

Csensor is an intrinsic value determined by the structure of the chip. Substituting each value into this equation, the relation between x and Δxmin for both chips is shown in Figure 12c. Here, VIN was set to 5.2 V for Chip A and 59 V for Chip B so that the output signal of each chip was close to saturation when x was 0. As shown in this figure, the smaller the x, the higher the distance precision, and both chips could detect distance differences on the order of nanometer when x was less than 1 μm.

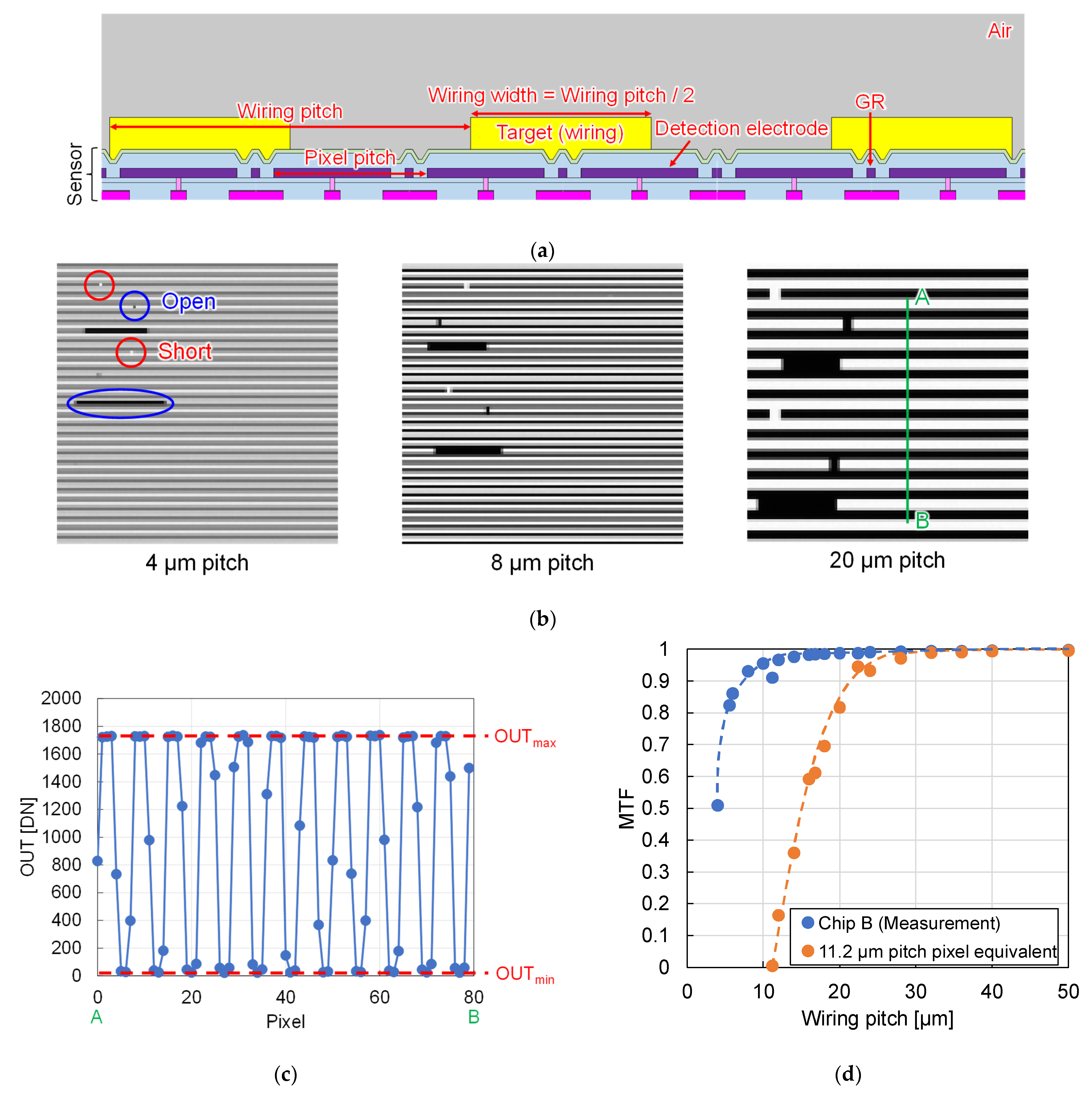

Figure 13 shows the resolution measurement of Chip B. In order to calculate MTF, which is an index of resolution, TiN metal wires of 100 nm thickness having several different pitches were formed in the chip fabrication process as targets on the surface of Chip B as shown in Figure 13a, and images were captured by applying φC to these wires with a probe. The captured images are shown in Figure 13b. The visualization of intentionally designed open and short parts were confirmed even for the smallest 4 μm pitch wiring. For the 20 µm pitch wiring, the shape of the wiring was clearly captured. The output of pixels along with the line A-B in Figure 13b is shown in Figure 13c. From these results, MTF was calculated using the following Equation (4).

Figure 13.

Resolution measurement of Chip B: (a) cross-sectional structure of the chip with metal wiring created on the surface; (b) captured images of the wiring for each pitch; (c) output signal for each pixel when 20 µm pitch wiring captured by Chip B; (d) MTF calculated from the measurement results.

MTF at each wiring pitch was calculated from Equation (4) when the wiring pitch was varied between 4 and 50 μm, and the plotted MTF curve is shown in Figure 13d. The blue points were calculated from the measurement results using Chip B, and the orange points were calculated from the results of converting the measurement results of Chip B to a pixel pitch of 11.2 μm. With Chip B, MTF values of about 0.5, 0.9, and 0.99 were obtained when the wiring pitch was 4, 8, and 20 μm, respectively. These results show that the resolution of Chip B was greatly improved at a wiring pitch of 20 μm or less, and it was also resolved at 10 μm or less. This indicates that Chip B was useful for visualization of fine wiring and cells.

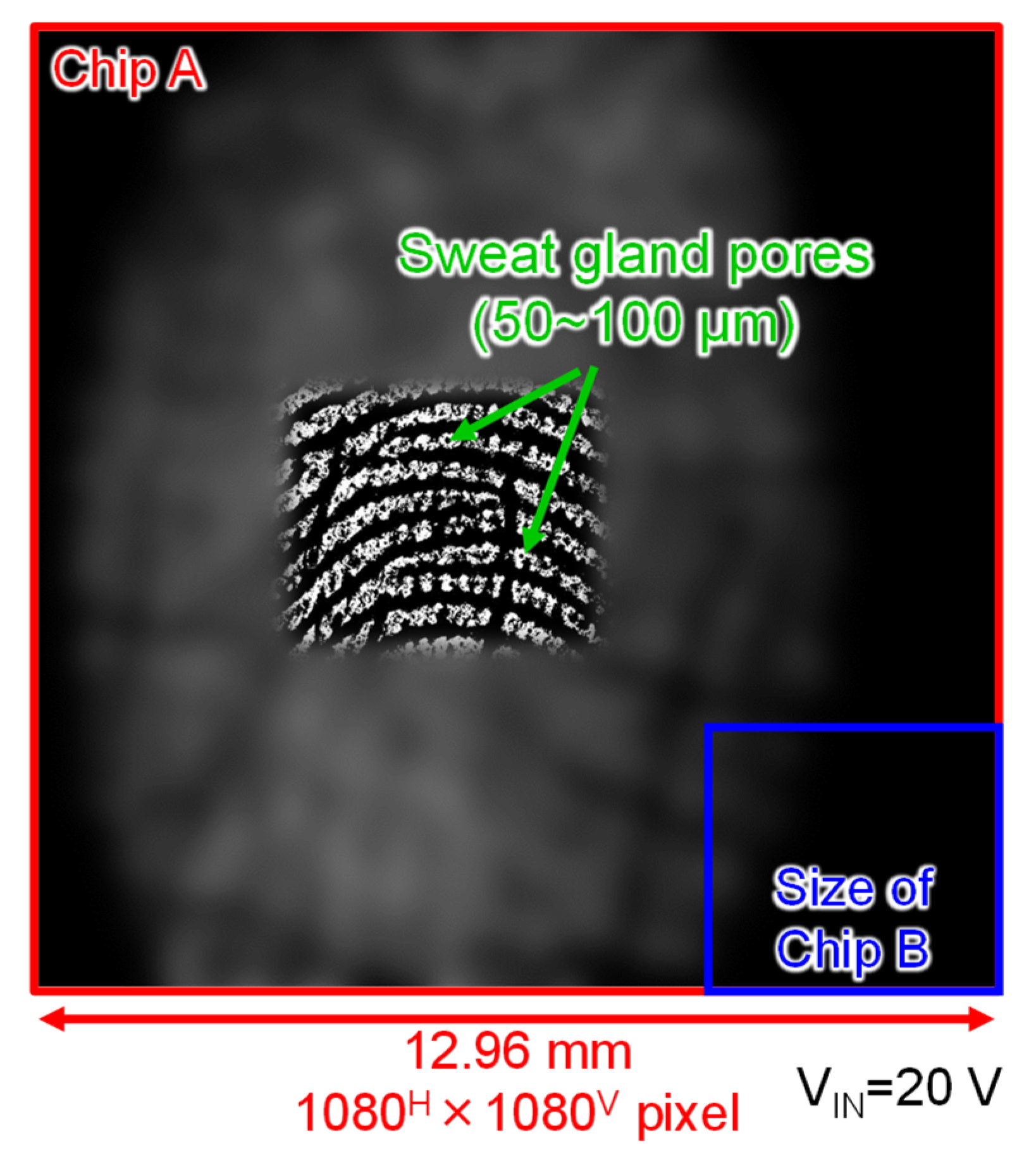

Figure 14 shows a fingerprint image captured by Chip A (some areas are blurred to protect personal information). This image was captured by placing a finger in contact with Chip A, which was assembled in the manner shown in Figure 8c, and a probe applying φC with VIN of 20 V was placed in contact with the body. The large pixel area allowed us to capture the entire fingerprint. Furthermore, sweat gland pores of several tens of micrometers in diameter were clearly captured.

Figure 14.

Captured image of a fingerprint by the large format Chip A (blurred for privacy).

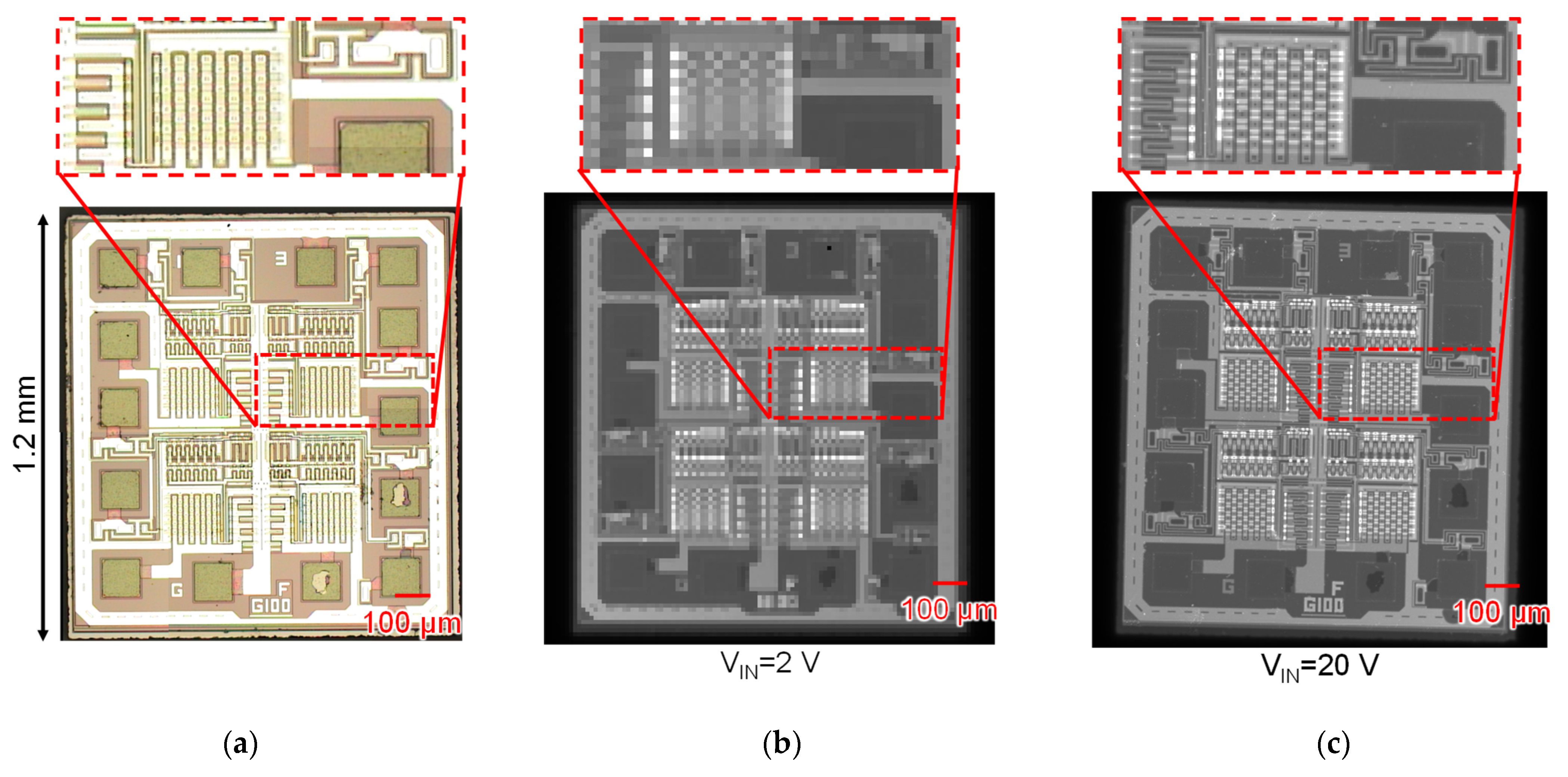

Figure 15 shows images of a general-purpose logic IC chip captured by an optical image sensor and Chip A and B. The target is a general-purpose logic IC chip; TC74HC02 fabricated by around 3 μm CMOS process. Image Figure 15a is a composite image of six images taken in each region using a 200× optical microscope and an optical image sensor. Furthermore, Figure 15b,c are images captured by contacting TC74HC02 with Chip A and B assembled by the method shown in Figure 8a, respectively, and applying φC by contacting the probe with the back surface of the target. In Chip B, the shape of transistors and wiring with a width of 10 μm or less could be clearly captured, indicating that the resolution has been improved compared to Chip A. Additionally, comparing Figure 15a,c, the capacitance image sensor was able to capture the shape of the wiring near the pad and the shape of the contacts and was able to visualize the difference in dielectric constant and unevenness.

Figure 15.

Captured images of a general-purpose logic IC (TC74HC02): (a) captured by optical image sensor using a microscope; (b) captured by Chip A; (c) captured by Chip B.

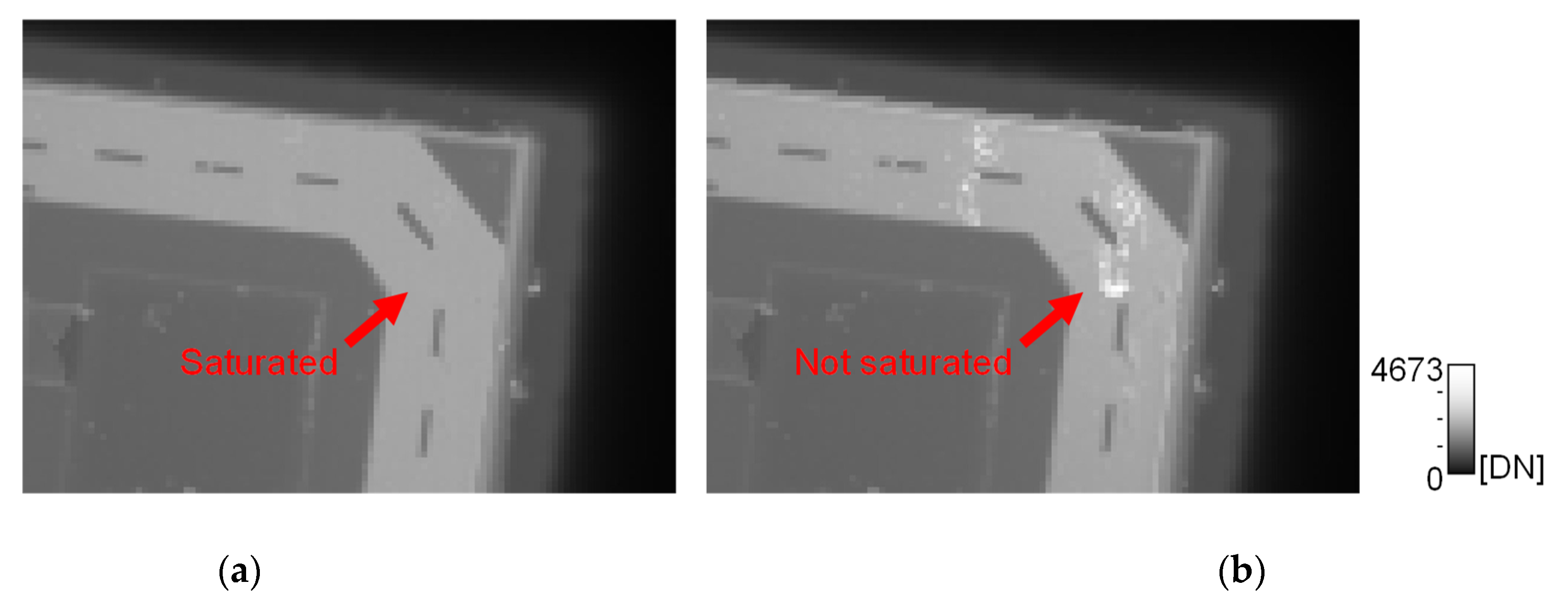

Figure 16 shows enlarged images of the logic IC chip captured by Chip B operating in Normal mode and HDR mode. In Figure 16a, the image was captured in Normal mode with VIN as a single 120 V. In Figure 16b, the image was captured in HDR mode with multiple VIN applied at 15 V intervals below 120 V. Both images show the same signal range. In Figure 16a, the signal was saturated in the region with large capacitance, and it was impossible to distinguish the unevenness, but in Figure 16b, by using the signal with small VIN in the region with large capacitance, it was possible to visualize the small unevenness without saturation. Thus, HDR mode expanded the range of detectable capacitance and enabled the detection of small capacitance differences while maintaining high SNR.

Figure 16.

Comparison of images captured of a general-purpose IC chip with the sensor operating in normal mode and HDR mode: (a) Normal mode; (b) HDR mode.

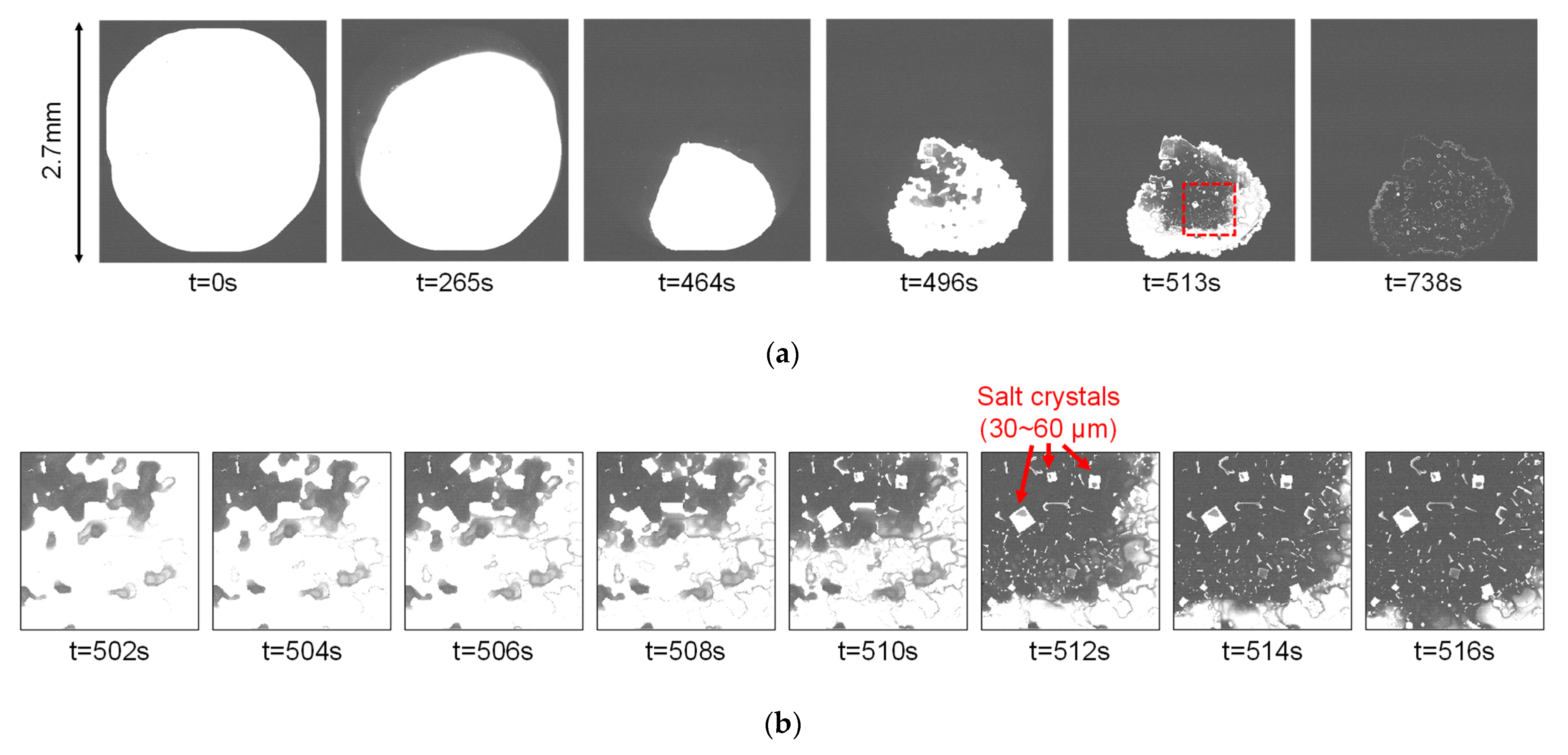

Figure 17 shows images of the evaporation of saline solution dropped on the surface of Chip B assembled by the method shown in Figure 8b. Here, the images were captured by applying φC from the GR of a pixel in the chip, without using an external counter electrode. The images clearly show the evaporation of water with the passage of time and the eventual precipitation of salt crystals with a size of several tens of micrometers.

Figure 17.

Captured images of a drop of saline solution on the sensor surface drying out as time advances captured by Chip B: (a) sample images; (b) closed-up images of red rectangle in (a).

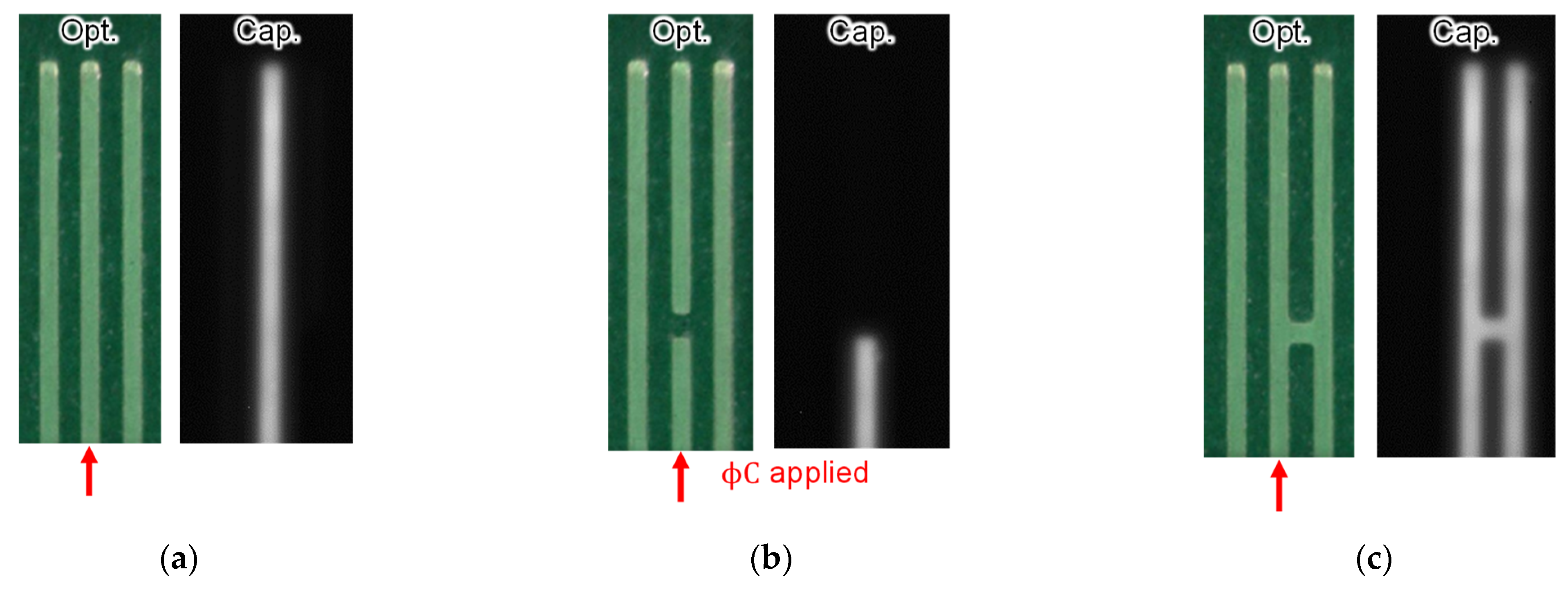

Figure 18 shows images of the wiring of a printed circuit board captured by an optical image sensor and a capacitance image sensor. The capacitance images were captured by Chip A, which was assembled in the manner shown in Figure 8c. φC was applied only to the center wire indicated by the red arrows in the figures. In Figure 18a, since there was no defect, only the center wire to which φC was applied appears in the capacitance image. In Figure 18b, the center wiring contained an open spot, and the wiring beyond it did not appear in the capacitance image. In Figure 18c, the center and right wires were shorted via a spot, so both wires appeared in the image. As shown above, in the capacitance image, only the wiring connected to the parts where φC was applied was visualized. Therefore, it was easy to identify the defect position, and the existence of the defect could be detected even if the defective part was outside the field of view.

Figure 18.

Captured images of printed circuit board wiring by optical image sensor and Chip A: (a) no defects; (b) open defect; (c) short defect. φC was applied only to the center wire indicated by the red arrows.

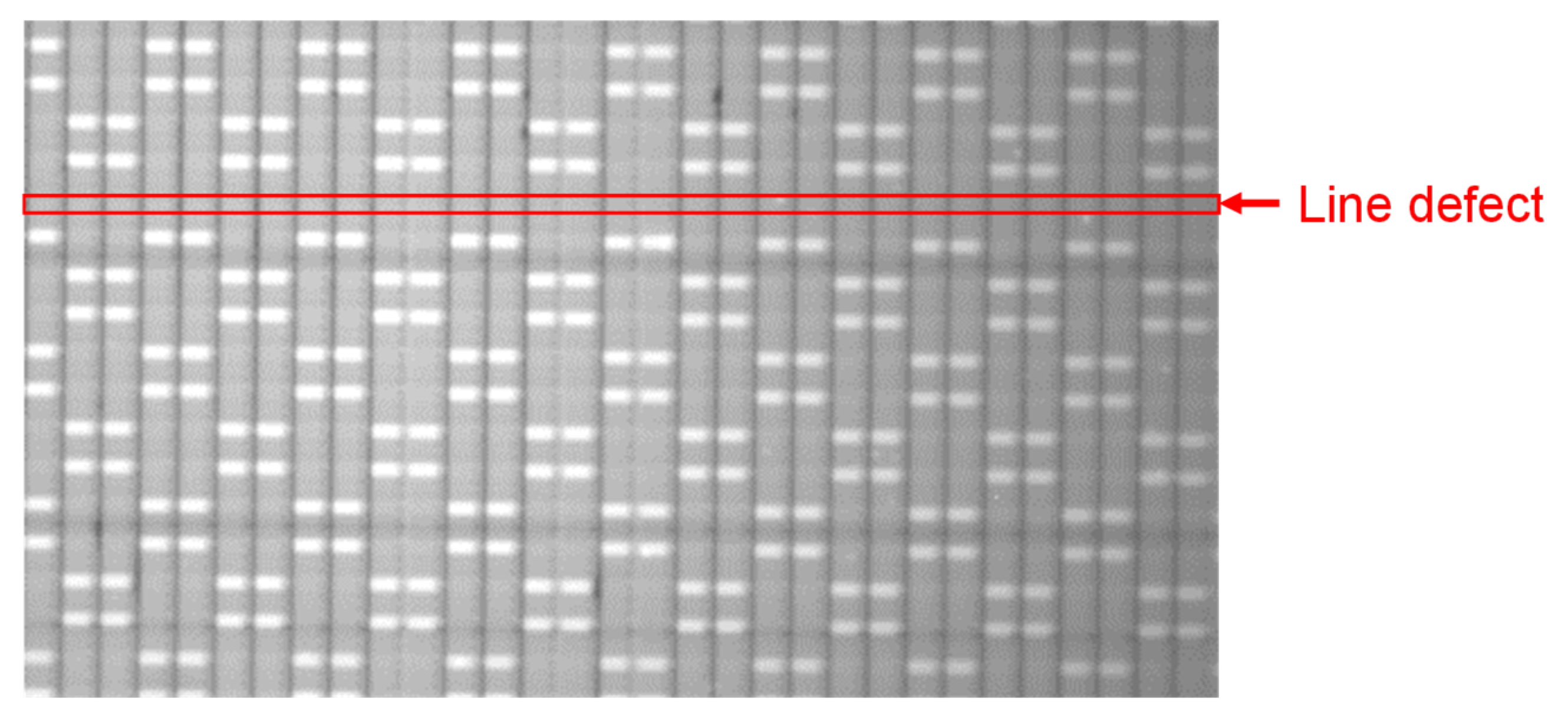

Figure 19 shows an image of a flat panel display (FPD) taken with Chip B. Since FPD used indium tin oxide, which has a high transmittance of visible light, as an electrode, it was difficult to inspect the wiring of FPD using an optical image sensor. Therefore, using a capacitance image sensor made it easier to visualize the electrical connections. In Figure 19, transparent electrodes with a pitch of 216 µm were lined up, and the electrode to which φC was applied appeared white. However, in the line indicated by the red arrow, no signal appeared, indicating a line defect. As shown above, the capacitance image sensor could be used for wiring inspection of FPD.

Figure 19.

Captured image of flat panel display with a line defect by Chip A.

When detecting the capacitance of a large object, such as a wiring inspection, the sensor position was shifted one after another and then captured images while repeating the process (step-and-repeat). Therefore, by enlarging the sensor area, the number of shots could be reduced, and the inspection will be faster and more efficient.

Table 2 shows the performance of the developed chips. Compared to our previous work, Chip A achieved 10 times larger imaging area and a higher precision, and Chip B achieved 33 times higher resolution while maintaining the precision. Comparing the performances among Chips A and B, the input referred temporal random noise was smaller for Chip A, which resulted in a better detection precision. It was because chip A had a higher signal readout gain at the in-pixel SF and at the horizontal signal readout circuit using capacitive charge division operation. The temporal random noise of Chip B could be improved by increasing the signal readout gain by introducing column parallel gain amplifiers and ADC for instance.

Table 2.

Performance summary of the developed sensors.

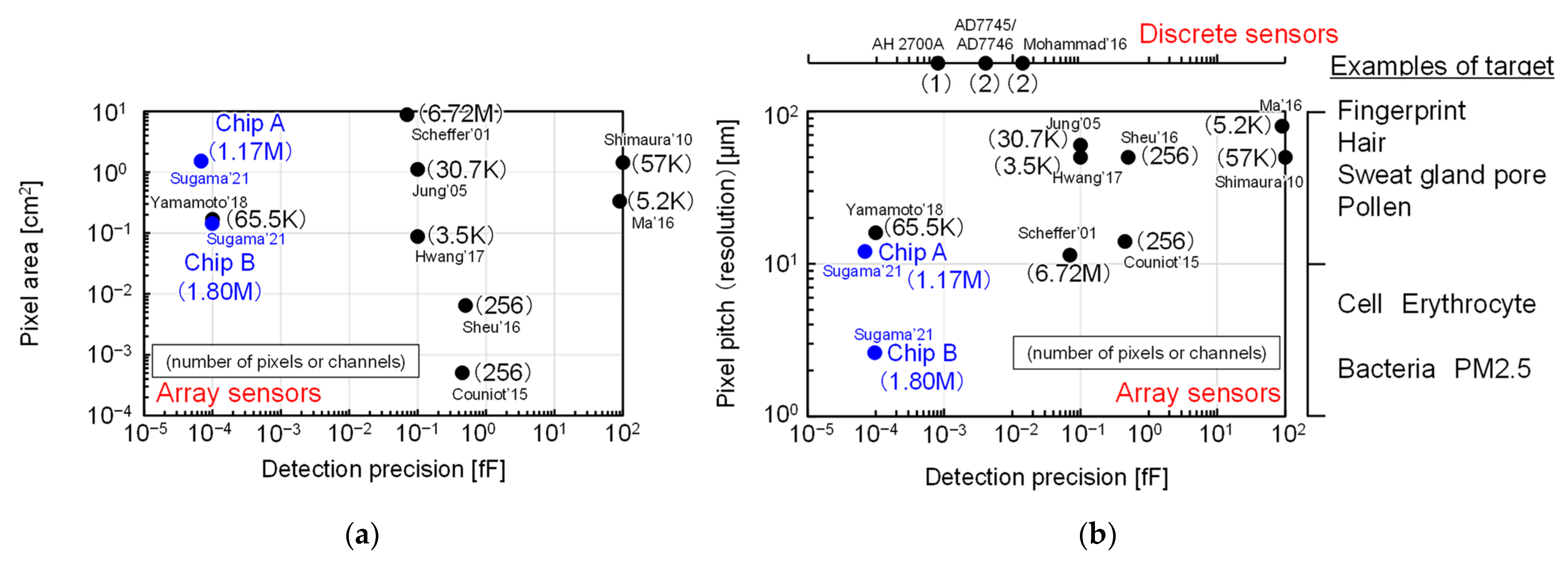

Figure 20 shows the benchmarking of the developed proximity capacitance CMOS image sensors with other array and discrete capacitance sensors [6,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,26]. The developed sensors had a large pixel area and a higher resolution while achieving higher detection accuracy than those of other sensors.

Figure 20.

Benchmark comparison with other sensors [6,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,26]: (a) comparison of detection precision and pixel area; (b) comparison of detection precision and pixel pitch and examples of target.

4. Conclusions

Two high-precision proximity capacitance CMOS image sensors were presented in this paper. Both chips successfully achieved real-time proximity capacitance imaging with high precision. Using Chip A with a large pixel area, the measurement efficiency was improved especially for large measurement targets like flat panel displays. It was production-ready for wiring inspection applications. For Chip B, with high-resolution pixels, it was expected to be useful for visualization of microscopic objects such as living cells. The developed sensors could be utilized for high-efficiency measurement tools in manufacturing, biomedical, life science fields, and more.

Author Contributions

Conceptualization, R.K., T.G. and S.S.; methodology, Y.S., Y.W., M.Y., R.K. and S.S.; software, Y.S., Y.W. and M.Y.; validation, Y.S., Y.W., R.K. and S.S.; formal analysis, Y.S., Y.W., R.K. and S.S.; investigation, Y.S., Y.W., M.Y., R.K. and S.S.; resources, T.Y., H.H. and N.K.; chip fabrication, N.K.; data curation, Y.S., Y.W., R.K. and T.Y.; writing—original draft preparation, Y.S.; writing—review and editing, R.K.; visualization, Y.S., Y.W., M.Y., R.K. and S.S.; supervision, R.K. and S.S.; project administration, R.K. and S.S.; funding acquisition, R.K., H.H. and S.S. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Informed Consent Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interests.

Abbreviations

The following abbreviations and Parameters are used in this manuscript:

| CMOS | Complementary Metal Oxide Semiconductor |

| a | Atto (10−18) |

| z | Zepto (10−21) |

| S/H | Sample and Hold |

| SF | Source Follower |

| HDR | High Dynamic Range |

| RN | Random Noise |

| FPN | Fixed Pattern Noise |

| GR | Guard Ring |

| GND | Ground |

| CIS | CMOS Image Sensor |

| TEM | Transmission Electron Microscope |

| AFE | Analog Front End |

| FPGA | Analog to Digital Converter |

| NC | Noise Cancelling |

| PTC | Photon Transfer Curve |

| f | Femto (10−15) |

| SNR | Signal to Noise Ratio |

| MTF | Modulation Transfer Function |

| IC | Integrated Circuit |

| FPD | Flat Panel Display |

| Parameters | |

| CC | Detection electrode capacitance |

| CS | Measurement capacitance |

| VIN | Input pulse amplitude |

| VTH | Transistor threshold voltage |

| VOUTN | Voltage of thermal noise and SF VTH variation |

| VOUTS | Voltage of signal including noise and variation |

| VOUT | Signal voltage after noise cancelling |

| GSF | SF amplifier gain |

| VFPN | Voltage of FPN |

| VRN | Voltage of RN |

| ΔCSmin | Capacitance detection precision |

| Csensor | Capacitance between detection electrode and chip surface |

| Cext. | Capacitance between chip surface and counter electrode |

| x | Distance between chip surface and counter electrode |

| Δxmin | Distance detection precision |

| ε0 | Permittivity of vacuum |

| εr | Relative permittivity |

| S | Detection electrode area |

References

- Sukhavasi, S.B.; Sukhavasi, S.B.; Elleithy, K.; Abuzneid, S. Abdelrahman Elleithy CMOS Image Sensors in Surveillance System Applications. Sensors 2021, 21, 488. [Google Scholar] [CrossRef] [PubMed]

- Ohta, J. Smart CMOS Image Sensors and Applications; CRC Press: Boca Raton, FL, USA, 2020. [Google Scholar]

- Oike, Y. Imaging Devices and Systems for Future Society. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM) Tutorial, Virtual, 12-16 December 2020. [Google Scholar]

- Viable Cell Density Sensors Process Analytics Hamilton Company. Available online: https://www.hamiltoncompany.com/process-analytics/sensors/cell-density-sensors/viable-cell-density-sensors (accessed on 7 February 2022).

- CCMT-10D CCMT-D Series Ceramic Capacitance Manometer Transducer Type Vacuum Gauge Products ULVAC SHOWCASE. Available online: https://showcase.ulvac.co.jp/en/products/vacuum-gauge/transducer-type-g-tran/capacitance-manometer/ccmt-d-series/ccmt-10d.html (accessed on 7 February 2022).

- Scheffer, D.; Meynants, G.; Dierickx, B.; Fujii, T. A 6.6Mpixel Pixel CMOS Image Sensor for Electrostatic PCB Inspection. In Proceedings of the 2001 IEEE Workshop CCD and Advanced Image Sensors, Lake Tahoe, CA, USA, 7–9 June 2001; pp. 145–148. [Google Scholar]

- Yasuda, T.; Kobayashi, K.; Yamamoto, Y.; Hamori, H.; Teramoto, A.; Kuroda, R.; Sugawa, S. High Resolution Array Tester for Flat Panel Display Using Proximity Capacitance Image Sensor. In Proceedings of the 28th International Display Workshops, Virtual, 1–3 December 2021; pp. 258–261. [Google Scholar]

- Koerdel, M.; Alatas, F.; Schick, A.; Kragler, K.; Weisfield, R.L.; Rupitsch, S.J.; Lerch, R. Contactless Inspection of Flat-Panel Displays and Detector Panels by Capacitive Coupling. IEEE Trans. Electron Devices 2011, 58, 3453–3462. [Google Scholar] [CrossRef]

- Shimamura, T.; Morimura, H.; Shigematsu, S.; Nakanishi, M.; Machida, K. Capacitive-Sensing Circuit Technique for Image Quality Improvement on Fingerprint Sensor LSIs. IEEE J. Solid-State Circuits 2010, 45, 1080–1087. [Google Scholar] [CrossRef]

- Ma, H.; Liu, Z.; Heo, S.; Lee, J.; Na, K.; Jin, H.B.; Jung, S.; Park, K.; Kim, J.J.; Bien, F. On-Display Transparent Half-Diamond Pattern Capacitive Fingerprint Sensor Compatible With AMOLED Display. IEEE Sens. J. 2016, 16, 8124–8131. [Google Scholar] [CrossRef]

- Jung, S.-M.; Nam, J.-M.; Yang, D.-H.; Lee, M.-K. A CMOS integrated capacitive fingerprint sensor with 32-bit RISC microcontroller. IEEE J. Solid-state Circuits 2005, 40, 1745–1750. [Google Scholar] [CrossRef]

- Sheu, M.L.; Tsao, L.J. A Sub-fF Capacitive Fingerprint Sensor with Neighbor Pixel Difference Sensing. In Proceedings of the 2016 5th International Symposium on Next-Generation Electronics (ISNE), Hsinchu, Taiwan, 4–6 May 2016; pp. 1–2. [Google Scholar]

- Mohammad, K.; Buchanan, D.A.; Douglas, J.T. Integrated 0.35 µm CMOS Capacitance Sensor with Atto-Farad Sensitivity for Single Cell Analysis. In Proceedings of the 2016 IEEE Biomedical Circuits and Systems Conference (BioCAS), Shanghai, China, 17–19 October 2016; pp. 22–25. [Google Scholar]

- Couniot, N.; Francis, L.A.; Flandre, D. A 16 x 16 CMOS Capacitive Biosensor Array Towards Detection of Single Bacterial Cell. IEEE Trans. Biomed. Circuits Syst. 2015, 10, 364–374. [Google Scholar] [CrossRef] [PubMed]

- AD7745/AD7746. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD7745_7746.pdf (accessed on 31 January 2022).

- Andeen-Hagerling 2700A Bridge. Available online: http://www.andeen-hagerling.com/ah2700a.htm (accessed on 31 January 2022).

- Yamamoto, M.; Kuroda, R.; Suzuki, M.; Goto, T.; Hamori, H.; Murakami, S.; Yasuda, T.; Sugawa, S. A CMOS Proximity Capacitance Image Sensor with 16μm Pixel Pitch, 0.1aF Detection Accuracy and 60 Frames Per Second. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 660–663. [Google Scholar]

- Yamamoto, M.; Kuroda, R.; Suzuki, M.; Goto, T.; Hamori, H.; Murakami, S.; Yasuda, T.; Yokomichi, Y.; Sugawa, S. A CMOS Proximity Capacitance Image Sensor with 0.1aF Detection Accuracy. ITE Tech. Rep. 2019, 43, 49–54. [Google Scholar]

- Kuroda, R.; Yamamoto, M.; Sugawa, S. High Sensitivity, High Resolution and Real-Time Proximity Capacitance Image Sensors. Oyo Butsuri 2020, 89, 328–332. [Google Scholar]

- Kuroda, R.; Yamamoto, M.; Sugama, Y.; Watanabe, Y.; Suzuki, M.; Goto, T.; Yasuda, T.; Murakami, S.; Yokomichi, Y.; Hamori, H.; et al. High Accuracy High Spatial Resolution and Real-Time CMOS Proximity Capacitance Image Sensor Technology and Its Applications. ITE Trans. Media Technol. Appl. 2021, 9, 122–127. [Google Scholar] [CrossRef]

- Sugawa, S.; Goto, T.; Kuroda, R.; Sugama, Y.; Watanabe, Y.; Yasuda, T.; Hamori, H. High Accuracy Proximity Capacitance Image Sensors and Applications Thereof. Keisoku Gijyutsu 2021, 7, 40–45. [Google Scholar]

- Rihito Kuroda; Yuki Sugama; Yoshiaki Watanabe; Tetsuya Goto; Shigetoshi Sugawa Development of Sub-aF Accuracy High Resolution and Realtime CMOS Proximity Capacitance Image Sensors. ITE Tech. Rep. 2021, 45, 1–4.

- Sugama, Y.; Watanabe, Y.; Kuroda, R.; Yamamoto, M.; Goto, T.; Yasuda, T.; Murakami, S.; Hamori, H.; Kuriyama, N.; Sugawa, S. High-Precision CMOS Proximity Capacitance Image Sensors with Large-Format 12 µm and High-Resolution 2.8 µm Pixels. In Proceedings of the 2021 International Image Sensor Workshop (IISW), Online, 20–23 September 2021; pp. 288–291. [Google Scholar]

- James, R.J. Photon Transfer; SPIE Press Monograph: Bellingham, WA, USA, 2007; Volume PM170. [Google Scholar]

- Kuroda, R.; Sugama, Y.; Watanabe, Y.; Goto, T.; Yasuda, T.; Murakami, S.; Hamori, H.; Sugawa, S. Sub-aF Detection Accuracy CMOS Proximity Capacitance Image Sensors for Inspection, Authentification and More. In Proceedings of the 28th International Display Workshops, Virtual, 1–3 December 2021; pp. 1003–1004. [Google Scholar]

- Hwang, H.; Lee, H.; Han, M.; Kim, H.; Chae, Y. A 1.8-V 6.9-mW 120-fps 50-Channel Capacitive Touch Readout With Current Conveyor AFE and Current-Driven ΔΣ ADC. IEEE J. Solid-State Circuits 2018, 53, 204–218. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).