1. Introduction

With the commercialization of Intel’s Optane SSD [

1], cross-point memory has attracted great interest for its high density, high capacity, and low latency. In the one-selector-one-resistor (1S1R) configuration, the memory density can reach the smallest cell size of 4 F

2 (F is the feature size of a technology node) [

2]. However, a critical challenge for 1S1R arrays is the large number of sneak paths that reduce the reliability and performance of the system [

3]. To address this issue, on the one hand, Ovonic threshold switching (OTS) devices have shown immense potential with their low-temperature process, ultra-low off current, large drive current density, high selectivity (the ratio of on current and off current), and fast operating speed [

4]. On the other hand, V/2, V/3, and other bias schemes are proposed to avoid unintentional read and write operations in cross-point arrays [

5,

6,

7,

8]. The typical V/2 bias scheme for the read operation is shown in

Figure 1. V/2 bias is applied on all the word lines (WLs) and bit lines (BLs) in the standby phase. When the read-enable pulse occurs, the selected BL and selected WL turn to V and the ground, respectively. Meanwhile, the load current of the V/2 bias is transiently changed from no load to heavy load. Therefore, a reliable V/2 bias with a fast transient response is essential for the read operation.

In the V/2 bias scheme, the load current is limited since the sneak path current only exists in half-selected memory cells. In addition, advanced OTS devices with high selectivity can significantly limit the off current [

9,

10]. The parasitic capacitance of the selector and memory cell is dependent on the material. Moreover, the load capacitance of 1S1R memories is directly related to the size of arrays. As a result, the V/2 read bias needs to remain stable over a wide range of load capacitances.

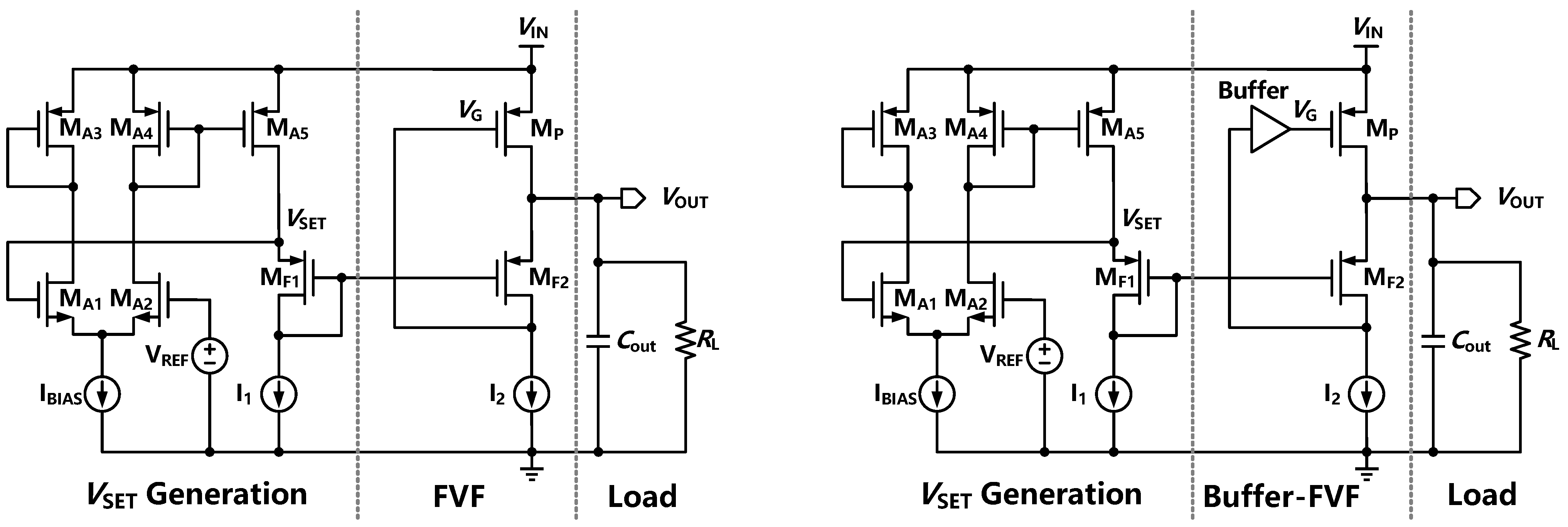

Compared with the switching converter, a low-dropout regulator (LDO) is more suitable to drive the V/2 bias due to its low noise, small area, and fast transient response. Although novel bias schemes have been proposed for cross-point memory, few circuit-level designs have been presented. To achieve a fast transient response, flipped voltage follower (FVF) topology has been adopted in advanced LDOs [

11,

12]. A large on-chip output capacitor was adopted to push the output pole to a lower frequency and became the dominant pole. The fully integrated LDOs achieved good transient responses that could respond to less than 10 ns load-transient edges but occupied a large area. A trip-loop LDO based on FVF topology was proposed with only a 0.65 ns response time and 43 mV undershoot when the load changed from 0 to 10 mA within 200 ps [

11]. It required an on-chip capacitor of 140 pF, consuming a large chip area. In addition, the power supply rejection (PSR) was only −20 dB at low frequencies. Some LDO systems have been proposed to supply the fast operating bias for nonvolatile memories [

13,

14]. However, the large on-chip capacitor was not suitable for the cross-point memory with high storage density. An internal dominant pole was designed in a LDO that significantly reduced the chip area [

15], but this LDO suffered from instability at zero current load condition and could only maintain system stability within a small range of load capacitance from 0 to 25 pF. Its PSR degraded to −5 dB while reaching 1 MHz. An LDO without an output capacitor and with a direct voltage-spike detection circuit was presented with little overhead [

16]. However, the edge time of load switching was 1 µs, which is too long for advanced memory. Recently, NMOS-based LDOs were proposed for low output impedance, better transient responses, and other benefits [

17,

18,

19,

20]. To drive the power transistor for low-dropout voltage, charge pumps or extra batteries must be introduced. A charge pump circuit powering the error amplifier would introduce switching noise and consume extra current and area overhead. In the cross-point memory, a read voltage (V

read) can be set between the threshold voltage of the memory cell in the RESET state (V

tR) and the SET state (V

tS). The V/2 bias scheme results in an inevitable voltage difference, so there is no need to minimize the dropout voltage between the input and output voltages during the read operation. For the conventional V/2 bias scheme, the read operation voltages in previous designs ranged from approximately 2.5 V to 4 V [

21,

22,

23]. Therefore, the dropout voltage is high enough to drive the NMOS regulation FET [

24]. In summary, exists is a research gap for a fully integrated LDO with a fast transient response and high area efficiency or a non-fully-integrated LDO with high performance to provide a V/2 bias for different sizes of memory arrays.

In this article, a fast-transient-response NMOS LDO based on FVA topology was proposed. The fast FVA loop provides a wide unity-gain bandwidth (UGB), which leads to a short settling time. Meanwhile, the regulator can maintain stability within a wide range of output capacitors from 0 to 10 nF and ESR conditions. This design is suitable to provide V/2 read bias for different sizes of 1S1R arrays.

The rest of this paper is organized as follows.

Section 2 describes considerations of the LDO architecture.

Section 3 explains the details of the proposed circuit.

Section 4 shows the simulation results and a comprehensive comparison.

Section 5 concludes the paper.

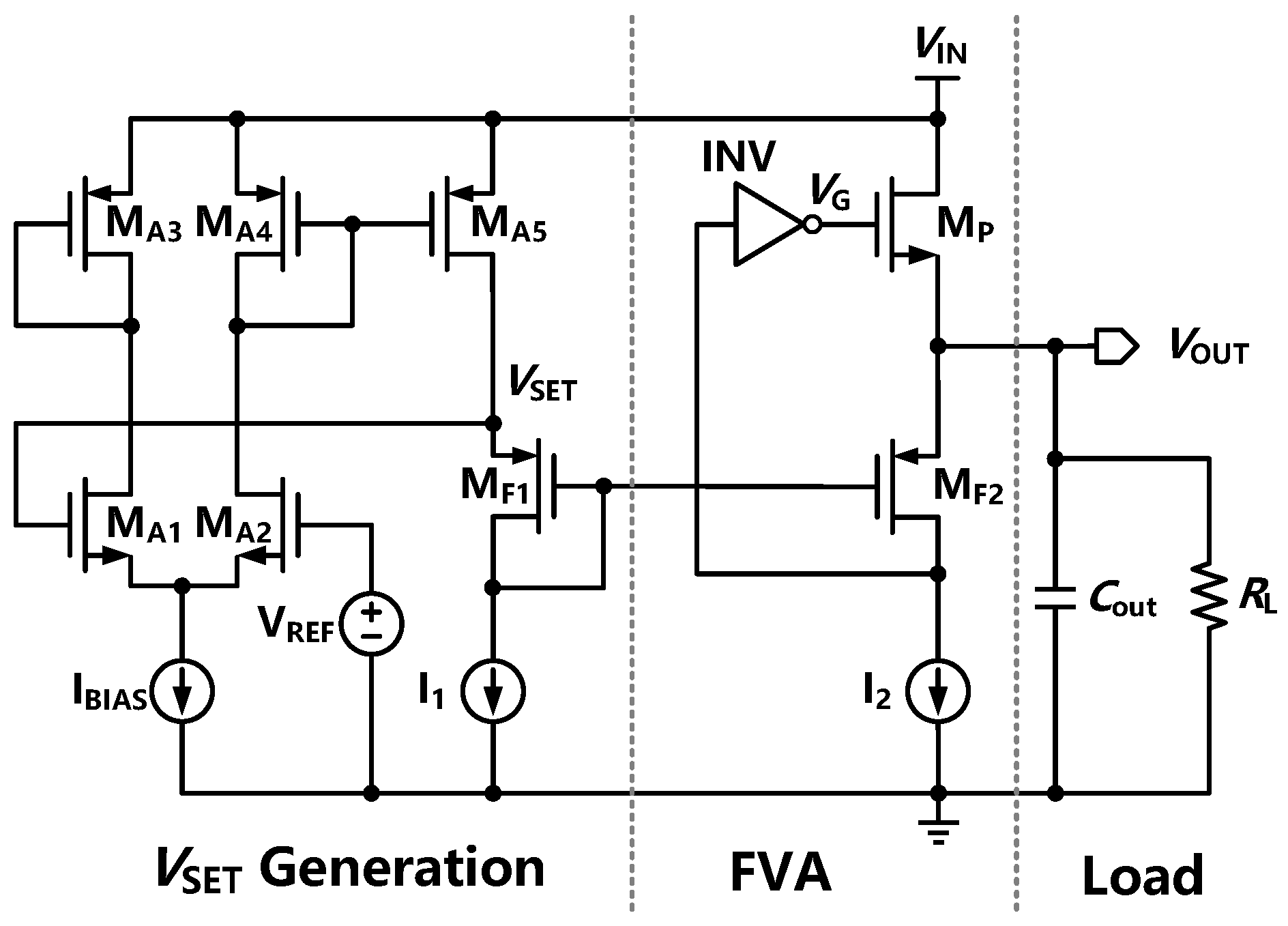

3. Proposed FVA Low-Dropout Regulator

Figure 5 shows the transistor level schematic of the proposed flipped voltage amplifier-based LDO. This circuit can be divided into four parts: main LDO, output capacitor, conventional bias, and adaptive bias. Two loops are adopted in the system, including a slow loop to generate the

VOUT and a fast loop to achieve better dynamics accuracy while load changes. For the slow loop, the

VSET is generated by a simple error amplifier or a simple LDO circuit that could drive µA-level current. The

W/

L ratio of transistors M1 and M2 was set to 1:4, which is the same rate as the bias current generated by the cascode current mirror consisting of M3, M4, M10, and M11. Thus, the source-to-gate voltage of M1 (

VSG1) is equal to the source-to-gate voltage of M2 (

VSG2). Furthermore,

VOUT is given by:

Therefore, VOUT can be adjusted according to the setting of VSET. The slow loop consisting of the above M1, M2, and VSET generation circuit could easily satisfy the stability. It provides accurate DC operating points for the circuit and ensures that VOUT is equal to VSET.

Similar to the FVF-based LDO, there is another fast loop to provide fast transient responses when the load current varies. To guarantee the stability of the negative feedback loop, the buffer of the FVF structure is replaced by an inverting amplifier with a wide bandwidth in the FVA topology. The fast loop consists of M2, M6, MP, and current bias. As a result, the NMOS-based LDO has more area efficiency, smaller output resistance, and smaller CG. The load regulation is less affected by different load currents or capacitances because the power transistor works as a source follower. Moreover, the FVA loop with a high UGB could provide fast transient responses within a short edge time.

The mechanism for the fast loop to respond to current transients is expressed as follows. When the load current changes from light load to heavy load, VOUT is lower than the preset voltage, and the drain voltage of M2 drops since the decrease of VSG2. The gate voltage of M9 drops and the gate voltage of MP increases due to the inverting amplifier. Consequently, the output voltage is forced to increase. In addition, the power transistor can directly provide negative feedback while voltage drops. Meanwhile, when the load current changes from heavy load to light load, VOUT is higher than the preset voltage, and the drain voltage of M2 increases as VSG2 grows. The gate voltage of M9 grows, and the gate voltage of MP is reduced as well. As a result, the output voltage is forced to decrease.

Conventional bias circuits are proposed to provide a reliable current bias for the main LDO module. The conventional bias consists of a simple current mirror and a voltage-spike detection circuit. Additionally, the voltage-spike detection circuit is added at the gate of M5 and the output terminal. The purpose of introducing the voltage-spike detection circuit is to improve the limited SR and transient response without an extra quiescent current. The output voltage is kept constant under a stable load current provided by the conventional bias circuit. When the load current varies,

VOUT changes and leads to a voltage spike (Δ

V) rapidly. Therefore, the current is momentarily changed, resulting in an extra dynamic current (Δ

I) generation. The total and dynamic current can be expressed as follows:

where

μn,

Cox,

W/

L, and

VTHP are the mobility of electrons, gate oxide capacitance per unit of area, aspect ratio, and threshold voltage of a PMOS device, respectively. Moreover,

C1 and

R1 will introduce a pole-zero doublet at the frequency of 1/

R1C1, which needs to be set lower than the minimum bandwidth of LDO at different load conditions. The high-pass characteristic of this circuit could increase the low-frequency gain of the fast FVA loop.

Without an off-chip capacitor, the internal pole pgate at the gate of the power transistor is designed as the dominant pole in the proposed FVA topology. Meanwhile, pout is designed as a nondominant pole due to the super-low output impedance at heavy load. As the load current decreases, the output impedance is increased, and pout moves to a lower frequency. Therefore, it is necessary to satisfy stability requirements at light and zero load conditions. The dominant pole pgate is high due to the lower CG and pout getting closer to the pgate, which leads to insufficient phase margin. To satisfy the stability of the fast FVA loop, R-C compensation is added to introduce an LHP zero zgate. This zero is designed as lower than pout to ensure both UGB extension and loop stability. In addition, the increase in load capacitance would result in lower frequencies of pout. Nevertheless, the system could remain stable under a wide range of load capacitances due to the small output impedance and R-C compensation. To deal with a faster transient response, the UGB of the FVA loop is designed to be wide. Meanwhile, an on-chip output capacitor is adopted to guarantee a fast transient response and filter out noise from the supply. Additionally, a small resistance is connected to the output capacitor for counteracting the phase shift of the pin.

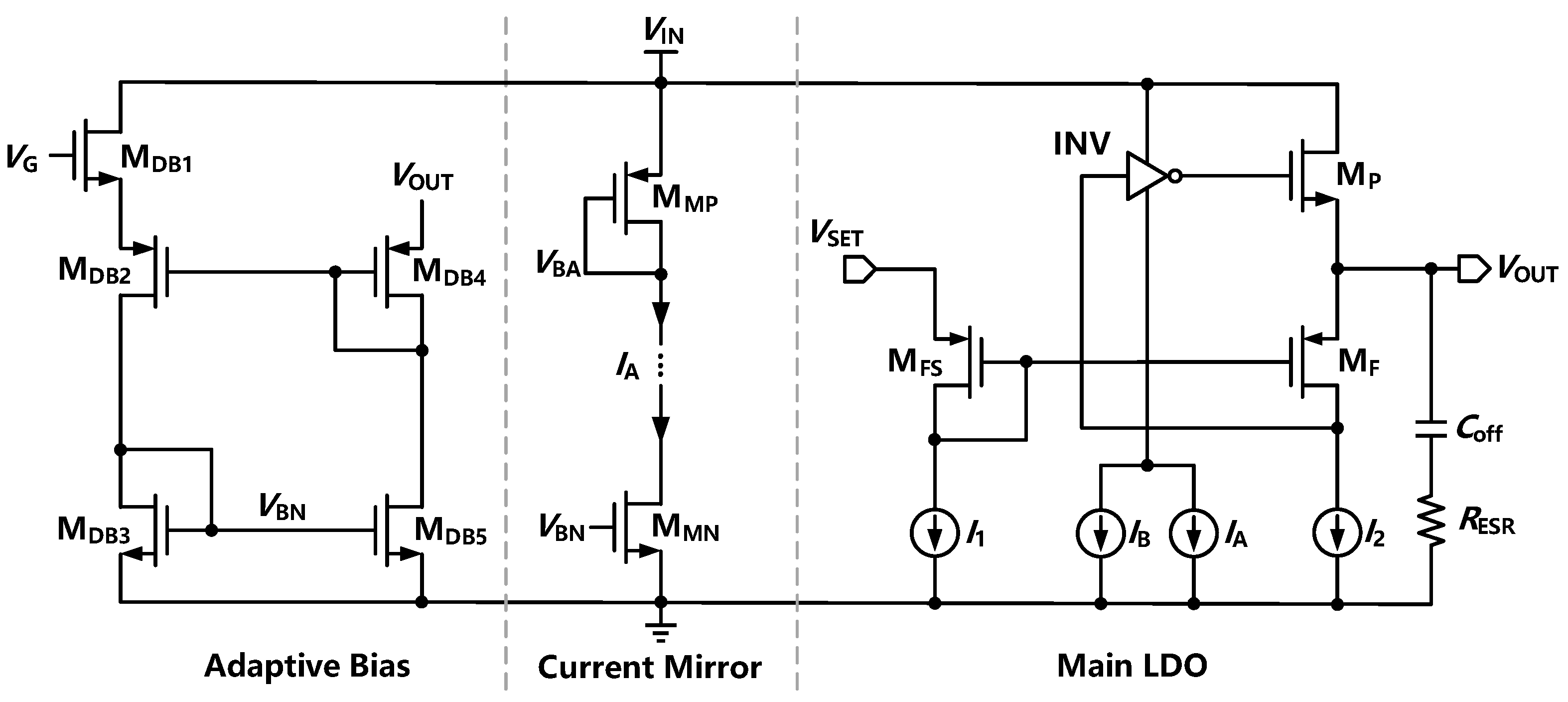

When a large external capacitor is adopted in FVA-based LDO,

pout is pushed to a low frequency and becomes the dominant pole. The ESR zero

zESR could counteract the phase shift of the

pgate, and R-C compensation is not required to be adopted. Since a large current would lead to a small output impedance and push

pout to higher frequencies, an adaptive bias is proposed to improve the stability load regulation within a large load current.

Figure 6 expresses the function of the adaptive bias module consisting of current mirrors MDB2 and MDB4. The input current obtained from the sensing load current shows a high accuracy. At a heavy load, adaptive bias is used to improve stability and load regulation. At light load, MDB3 works in the deep subthreshold region, and the adaptive bias circuit consumes ultra-low quiescent current. The generated adaptive current is added to the inverting amplifier for better stability of the FVA loop. In general, the transient response can be effectively enhanced by introducing an off-chip capacitor. This design exhibits a wider UGB and better transient response characteristics than FVF-based LDOs with off-chip capacitors. Meanwhile, it could achieve superior PSR and higher current efficiency. In fact, the introduction of large external capacitors will realize an improved transient response and lower power while sacrificing chip integration.

4. Simulation Results

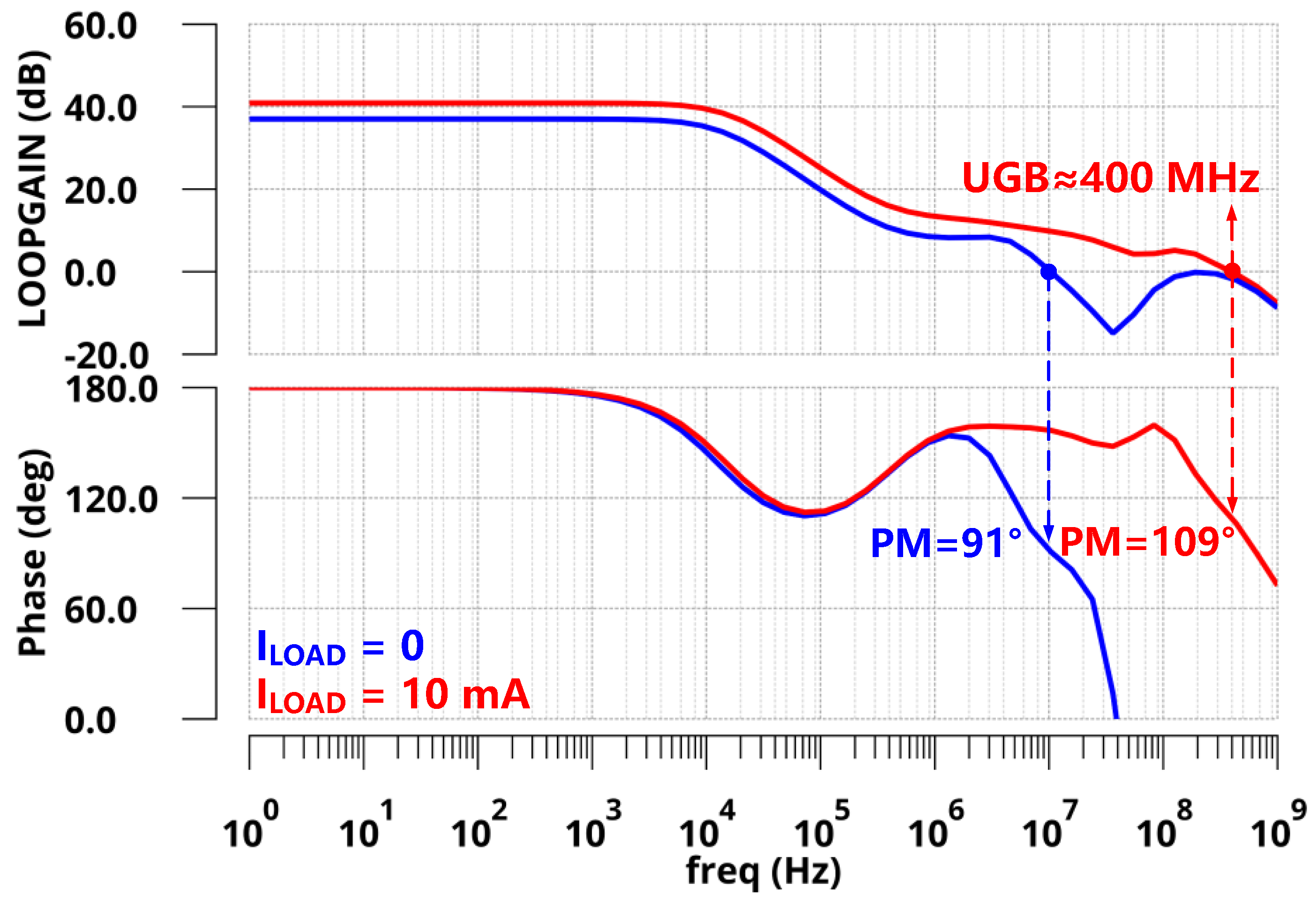

The proposed design was implemented in a standard 110 nm CMOS process. At the no off-chip capacitor condition, the FVA-based LDO delivered a maximum load current of 10 mA with a 3.3 V output voltage and 1.65 V output voltage to provide V/2 read bias for cross-point memory. Additionally, the quiescent current was 70 µA.

Figure 7 shows the Bode plots of the FVA loops at both zero and full load conditions (

ILOAD = 0 µA and 10 mA) with zero load capacitance (

CL = 0 pF). From the simulation, the

zgate introduced by R-C compensation could counteract the phase shift of the

pout at both conditions. To address another internal pole

pin at the heavy condition, a small resistance connected to the output capacitor was adopted to generate an LHP zero at high frequencies. As expected, the phase margins of the FVA loop were 91° and 109° under 0 µA and 10 mA loads, respectively. The UGB of the system reached approximately 400 MHz at full load, leading to fast transient responses. In addition, the pole-zero doublet introduced by the voltage-spike detection circuit in low-middle frequency increases the low-frequency gain. The stability of the system does not deteriorate. To verify the stability of the system under variable load capacitance,

Figure 8 presents the phase margin of the proposed LDO with a range of

CL from 0 pF to 10 nF. The simulation results indicated that the phase margin was larger than 50° at both zero and full load conditions. Therefore, for a wide range of

CL, the proposed LDO is stable at light and heavy load current conditions.

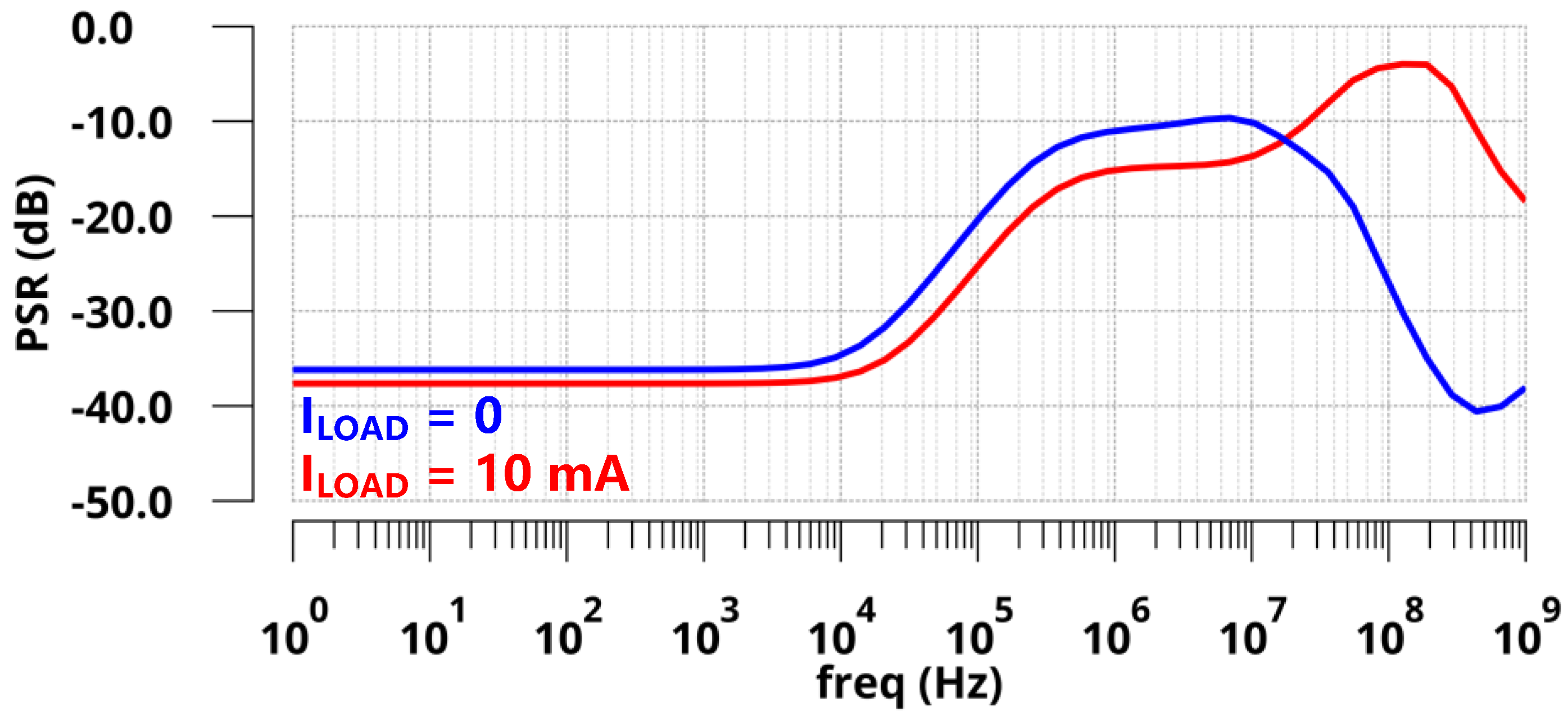

The simulated PSRs of the regulator at zero and full load conditions are presented in

Figure 9. With zero

CL, the simulated PSR of the proposed LDO was −17.8 dB at 1 GHz under a 10 mA load and −37.4 dB at 1 GHz under zero load.

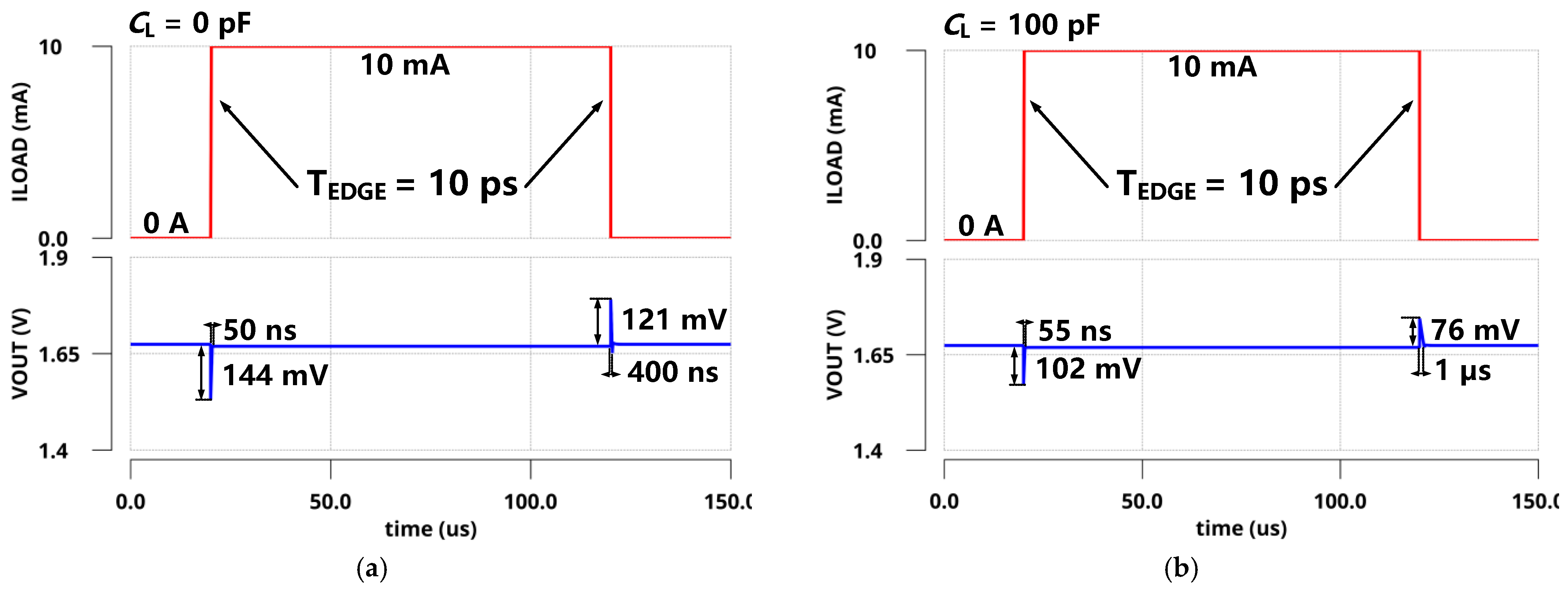

Figure 10 shows the simulated transient response of

VOUT with a full current step (

ILOAD changed from 0 µA to 10 mA) within an edge time of 10 ps. As shown in

Figure 10a, the undershoot voltage and settling time were only 144 mV and 50 ns without

CL due to the fast FVA loop. Additionally, the overshoot voltage and settling time were 121 mV and 400 ns, respectively. As shown in

Figure 10b, the simulated undershoot and overshoot voltages were reduced to 102 mV and 76 mV with 100 pF

CL. Furthermore, the simulation results are shown in

Figure 11 under the same on-chip capacitor and quiescent current conditions compared with FVF-based LDO. By replacing the PMOS and FVF structure with NMOS and FVA topology, both the undershoot and overshoot were effectively reduced with different load capacitors. As a remark, the proposed LDO exhibits a fast transient response under various load conditions.

For the ESR case, a large off-chip capacitor of 1 µF with

RESR = 100 mΩ was adopted for a large load current and better transient response.

Figure 12 shows the Bode plots of the FVA loops at both zero and full load conditions (

ILOAD = 0 µA and 100 mA). From the simulation,

pout is pushed to low frequencies and becomes the dominant pole. At the zero load current condition,

zESR and

pgate are locked at frequencies higher than the loop UGB, resulting in a phase margin of 90°, as expected. At the full load current condition,

pout shifted to higher frequencies owing to the decrease in output impedance. However,

zESR could counteract the phase shift of

pgate, and another internal pole

pin was higher than UGB. Therefore, the phase margin at full condition is shown as 63.4°.

Figure 13 presents the PSR of the regulator at zero and full load conditions. With the introduction of

Coff, PSR was significantly improved, especially at high frequencies. The simulated PSRs of the proposed LDO were −36 dB at 10 kHz and −46.3 dB at 1 GHz under a 100 mA load. Meanwhile, the PSR reached up to −50 dB at 10 kHz and −79.8 dB at 1 GHz under a zero load. Different load steps were applied and are shown in

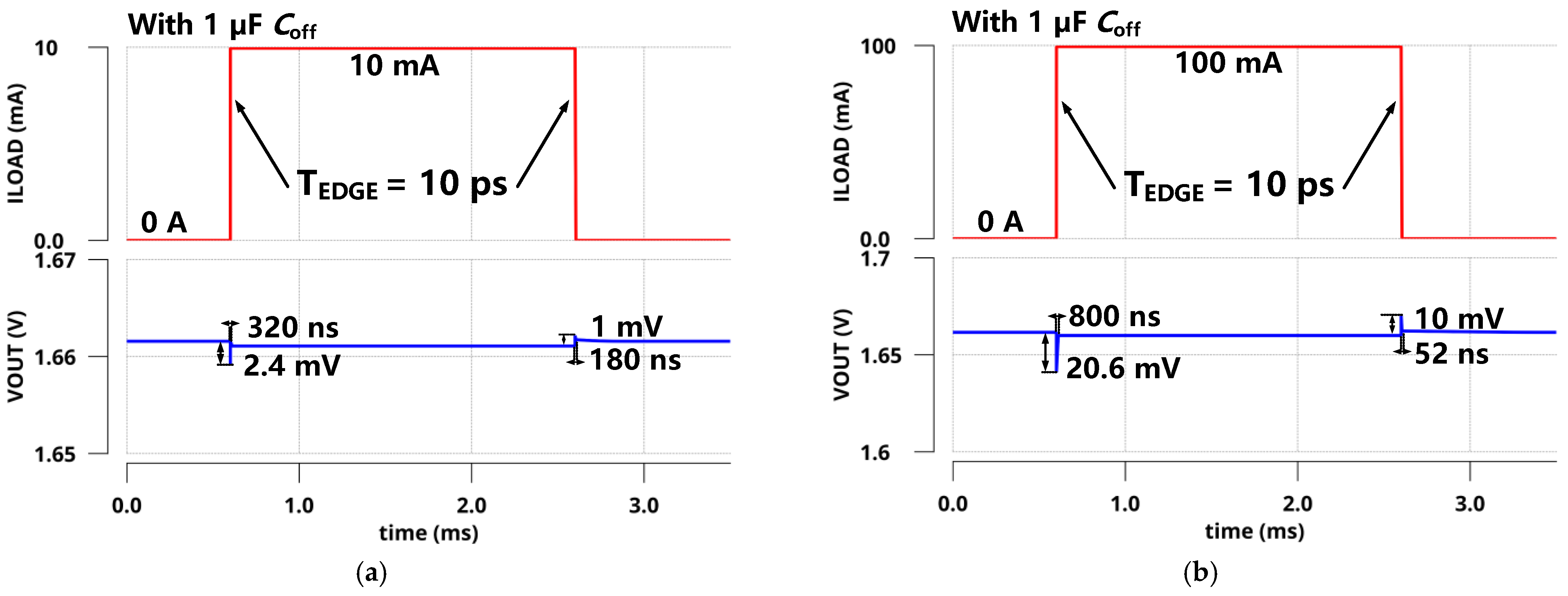

Figure 14 to confirm the transient response characteristics of

VOUT within an edge time of 10 ps. When the load current changed from 0 µA to a moderate load (10 mA), as shown in

Figure 14a, the undershoot and overshoot voltages were 2.4 mV and 1 mV, respectively. In addition, when the load current changed from zero load (0 µA) to a full load (100 mA), as shown in

Figure 14b, the undershoot and overshoot voltages were 20.6 mV and 10 mV, respectively. The simulated load transient responses at other ESR conditions are shown in

Figure 15. Obviously, this design could guarantee the stability of the system with good performance under the abovementioned conditions. From the simulation results, it is obvious that the transient response of the proposed LDO is significantly improved with the off-chip capacitor.

Figure 16 shows the quiescent current from −20 °C to 85 °C at different process corners and both zero and full current load conditions. Due to the high gate voltage of MP at the full load condition, the current replicated from the current mirror to the inverting amplifier is slightly reduced. It is obvious that there was a decrease in quiescent current at full load compared to the zero load condition. It reduced the loop gain at low frequencies slightly but did not deteriorate the circuit stability. Similarly, the quiescent current characteristics of the regulator with off-chip capacitors are illustrated in

Figure 17. Due to the introduction of

Coff, good transient characteristics can be realized without consuming a high current for a high UGB. As a result, the current efficiency is significantly improved. In addition, adaptive bias was adopted to improve the stability and load regulation of the system. Under a light current load, the adaptive bias consumes an ultra-low quiescent current. Meanwhile, under full current load, the increased current consumption is completely acceptable, as shown in

Figure 17b.

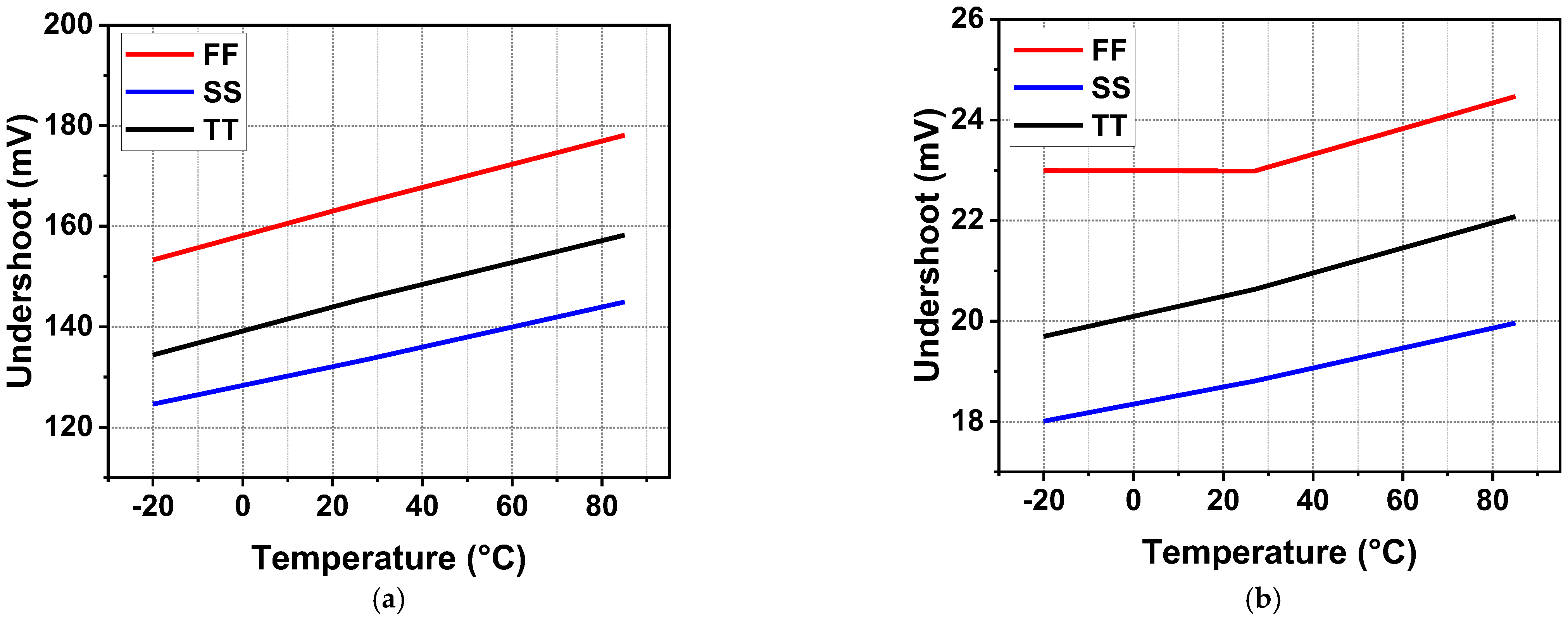

To further verify the reliability of the transient response for the circuit, the undershoot voltage from −20 °C to 85 °C at different process corners is shown in

Figure 18. When the load current changed from zero load to full load, load-transient undershoots could be observed. For the no off-chip capacitor case, the minimum undershoot was 124.6 mV at −20 °C, SS process, and the maximum undershoot was 178 mV at 85 °C, FF process. For a 1.65 V output voltage, the abovementioned undershoot voltage simulation results are acceptable with a quite small settling time. In addition, the load-transient undershoot results of the regulator with off-chip capacitors are illustrated in

Figure 18b. The undershoot voltage is significantly reduced, with a minimum undershoot of 18 mV at −20 °C, SS process, and a maximum undershoot of 24.4 mV at 85 °C, FF process.

Simulation results of the 500-run Monte Carlo analysis for mismatch and process variations at −20 °C, 25 °C, and 85 °C are shown in

Figure 19 and

Figure 20. For the no off-chip capacitor case, the average undershoot µ is between 133 mV and 157 mV, and the standard deviation σ is approximately 2 mV. Moreover, for the off-chip capacitor case, as shown in

Figure 20, the average undershoot µ is between 20 mV and 22 mV, and the standard deviation σ is approximately 420 µV.

To evaluate the speed of the transient response, an important parameter response time

TR is defined in refs. [

15,

27]. For a fair evaluation,

CL is replaced by the total capacitance adopted by the LDO

CTotal, including the load capacitance and compensation capacitor. In the case that

TEDGE is much smaller than

TR, the current drawn from

CL can be seen as a constant. It can be expressed as:

Another estimation of

TR is needed for fast LDOs in the case that

TR <

TEDGE. It reads:

where

TEDGE is the load-transient edge time. In addition, the figure of merit (FOM) defined in [

17] is used as a baseline for LDOs, which is as follows:

where

K,

IQ, and

ILMIN are the ratio of the measured

TEDGE to the minimum

TEDGE, average value of quiescent current, and the minimum load current, respectively.

Table 1 summarizes the comparison between the proposed FVA-based LDO and other state-of-the-art LDOs. For the no off-chip capacitor case, the

TR of the design is not the smallest compared with other regulators. However, neither the transient characteristics nor the allowable range of the load capacitance meet the requirements of V/2 bias in cross-point memory [

15]. For the regulator in [

18], the parameter is obtained under the condition that the

IL changes from 1 mA (not zero load) to the full load current. In addition, the proposed FVA-based LDO without

Coff achieves the smallest FOM of 1.01 mV among previous works and can maintain stability over a wide range of load capacitances. For the off-chip capacitor condition, the transient response characteristics of the FVA-based LDO are also well improved. The smallest

TR and FOM are achieved compared with other LDOs with

Coff.