A Simplified Correlation Index for Fast Real-Time Pulse Shape Recognition

Abstract

1. Introduction

2. Related Works

3. Pulse Shape Recognition through Pattern Correlation

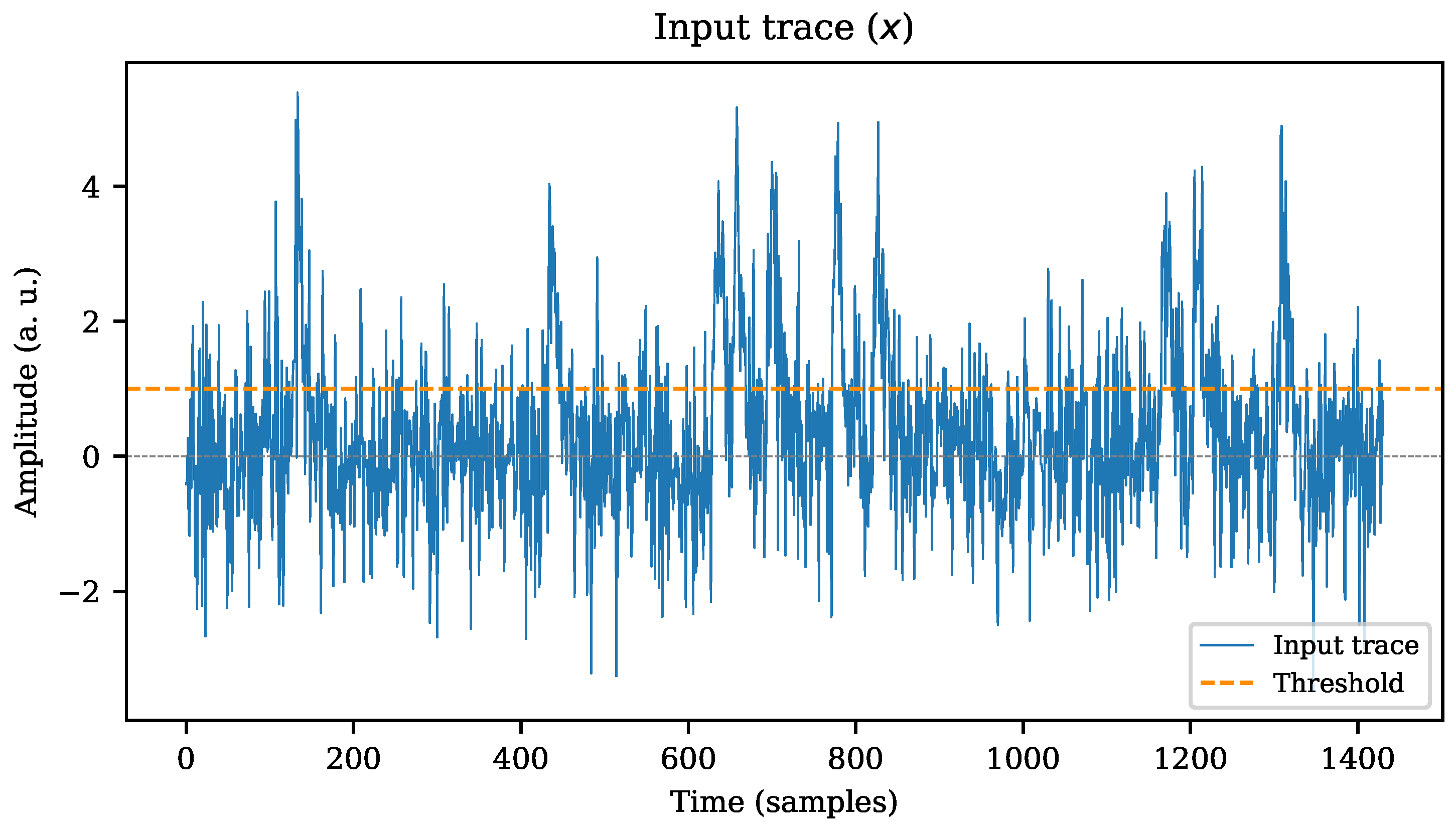

3.1. Simple Cross-Level Trigger

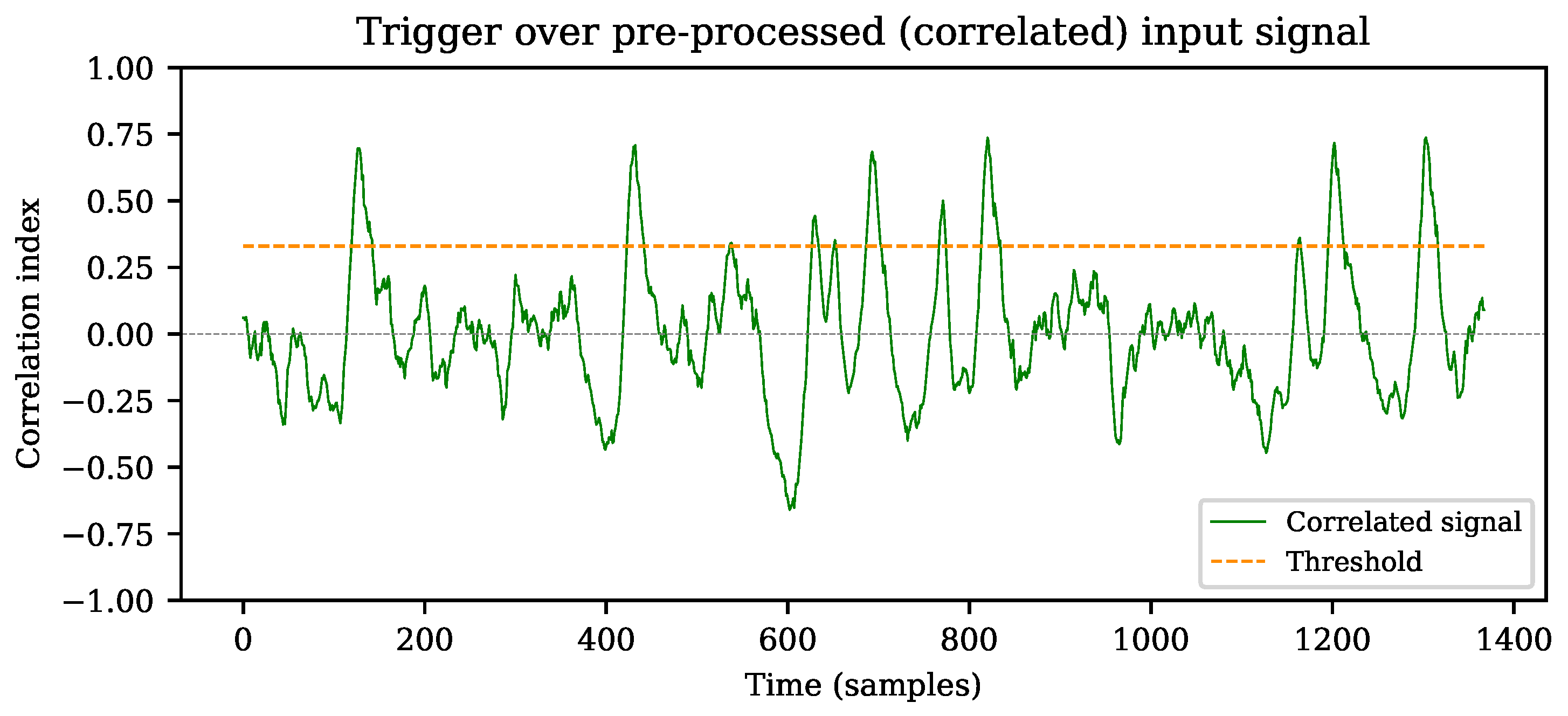

3.2. Two-Stage Triggering

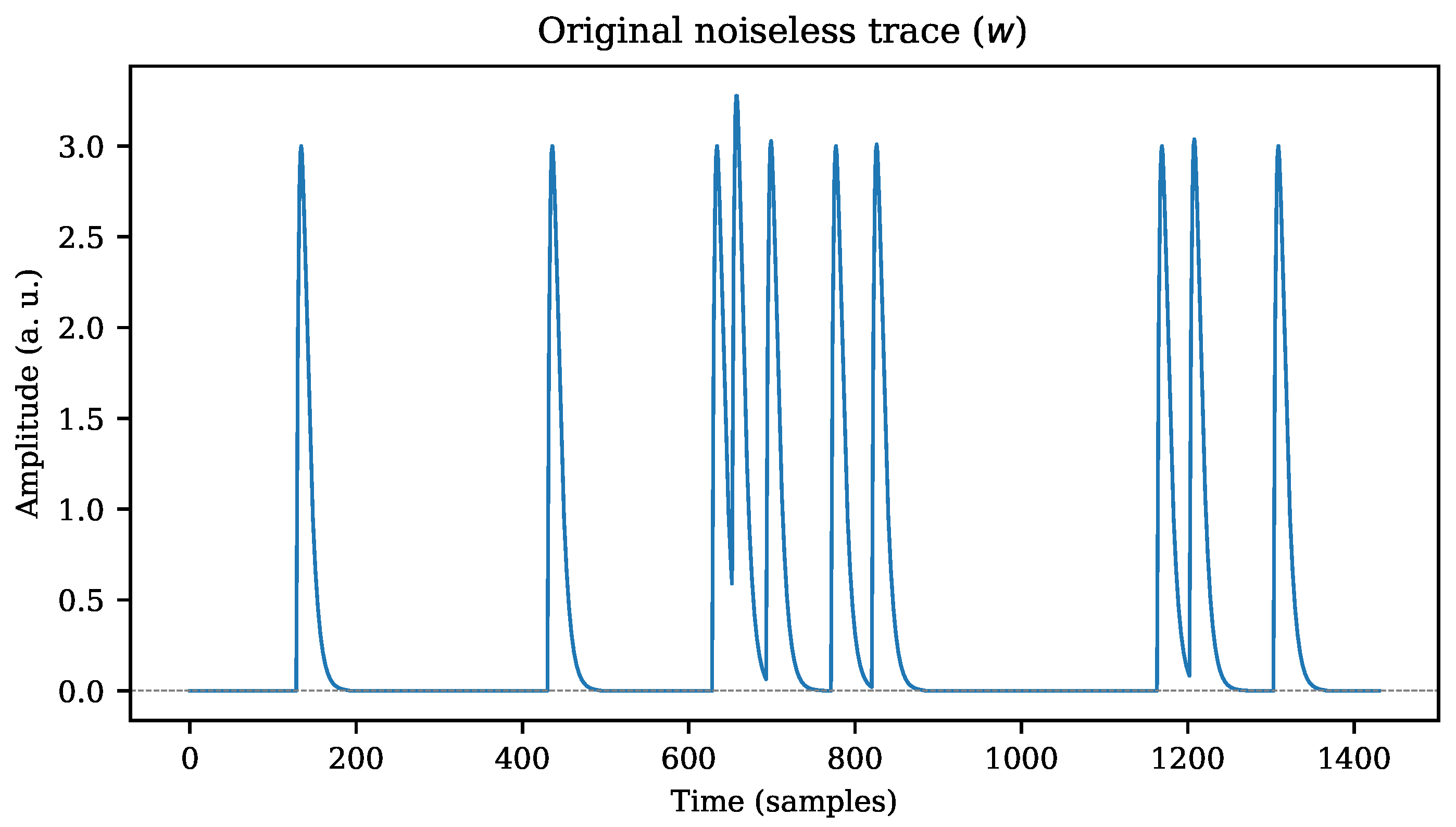

Pulse-Count Scenario

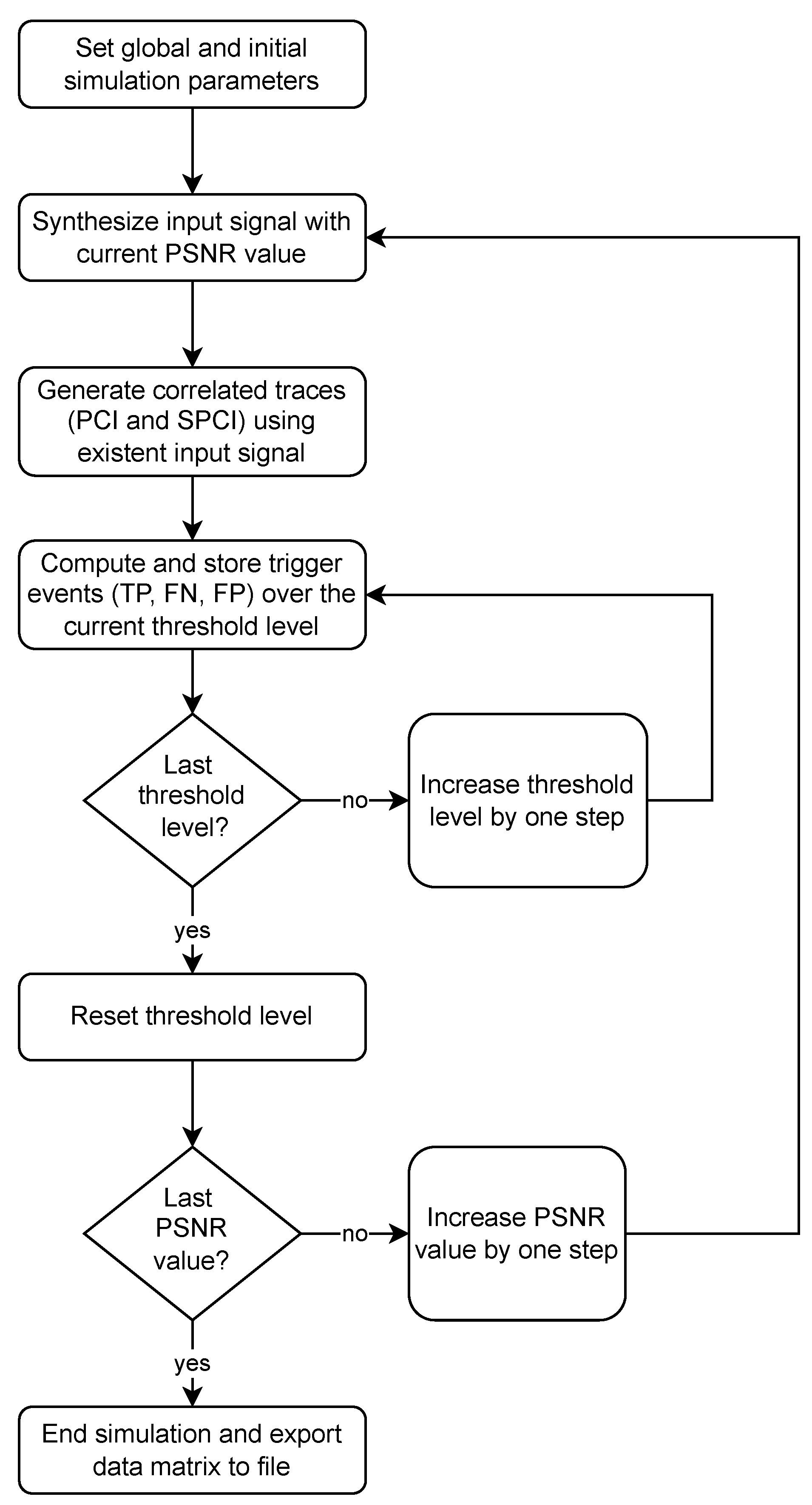

- True positive () events: since the original noiseless trace w is known, the simulator is capable of tagging the expected pulse positions and look for triggered events in the current threshold level.

- False negative () events: following the same reasoning than with s, but looking for missing expected triggers.

- False positives () events: after seeking the s, the triggered events list for the current threshold level is analyzed again, but excluding every index. The remaining triggers in the list belong to the unexpected count set. This class corresponds to events that were detected but were not meant to be there.

4. Simplified Correlation Index

4.1. Pearson Correlation Definition for a Fixed-Length Sliding Window

4.2. Simplified Correlation Index Definition

4.3. Simulation

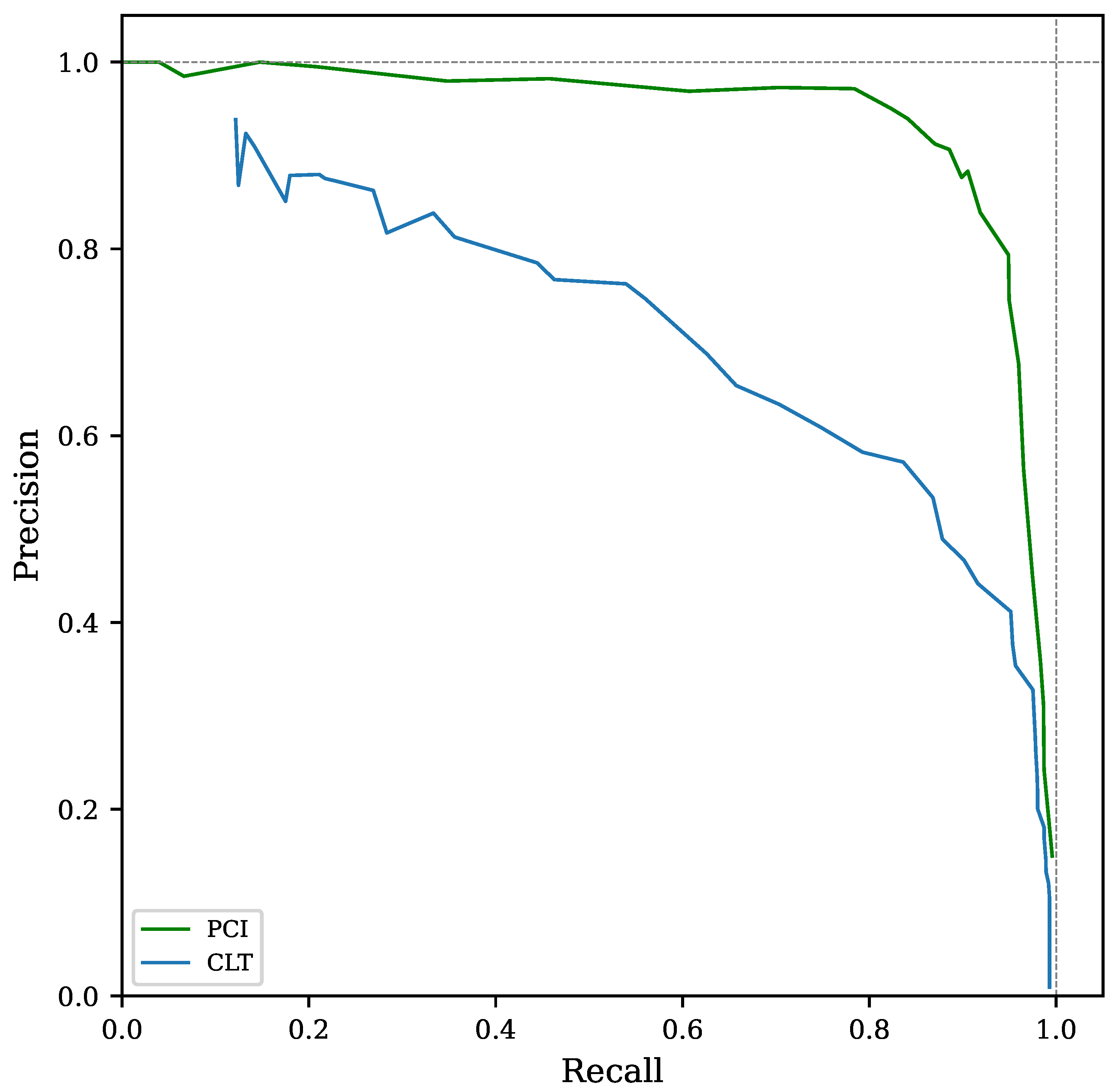

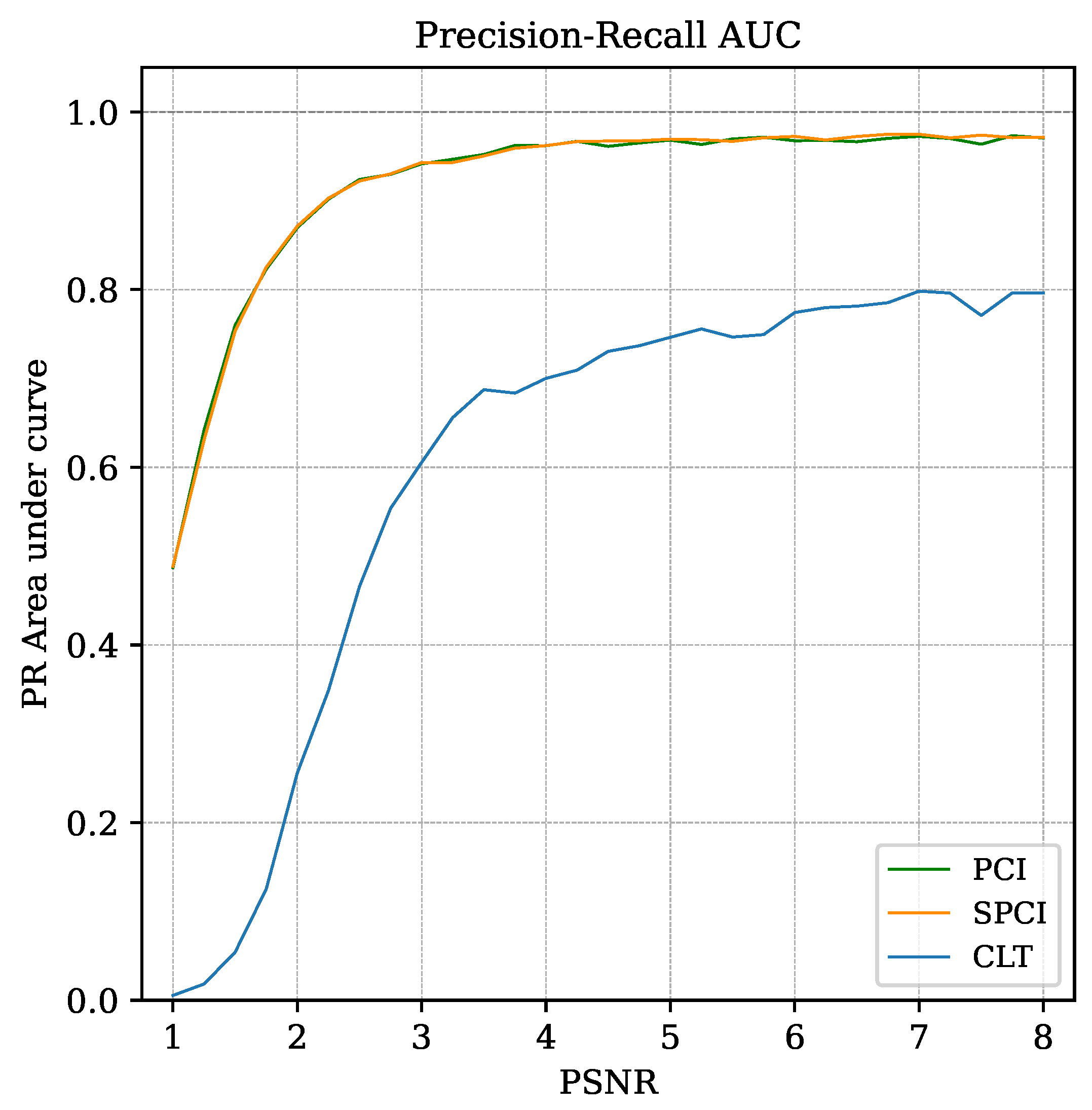

- Using a simple cross-level trigger (set to a static threshold value) over the original data stream x.

- Computing in a continuous fashion the PCI between x (the windowed portion of x) and the pattern c. Subsequently, triggering over the obtained PCI trace.

- Continuously computing sample-by-sample the SPCI and triggering in the same way than with the original PCI algorithm.

4.3.1. Simulation Validation

- Self-correlation of a pattern signal with itself (validation of perfect correlation);

- Correlation of a static-length stimulus signal with a pattern;

- Correlation of a streaming signal in a sliding window with the pattern.

4.3.2. Simulation Parameters

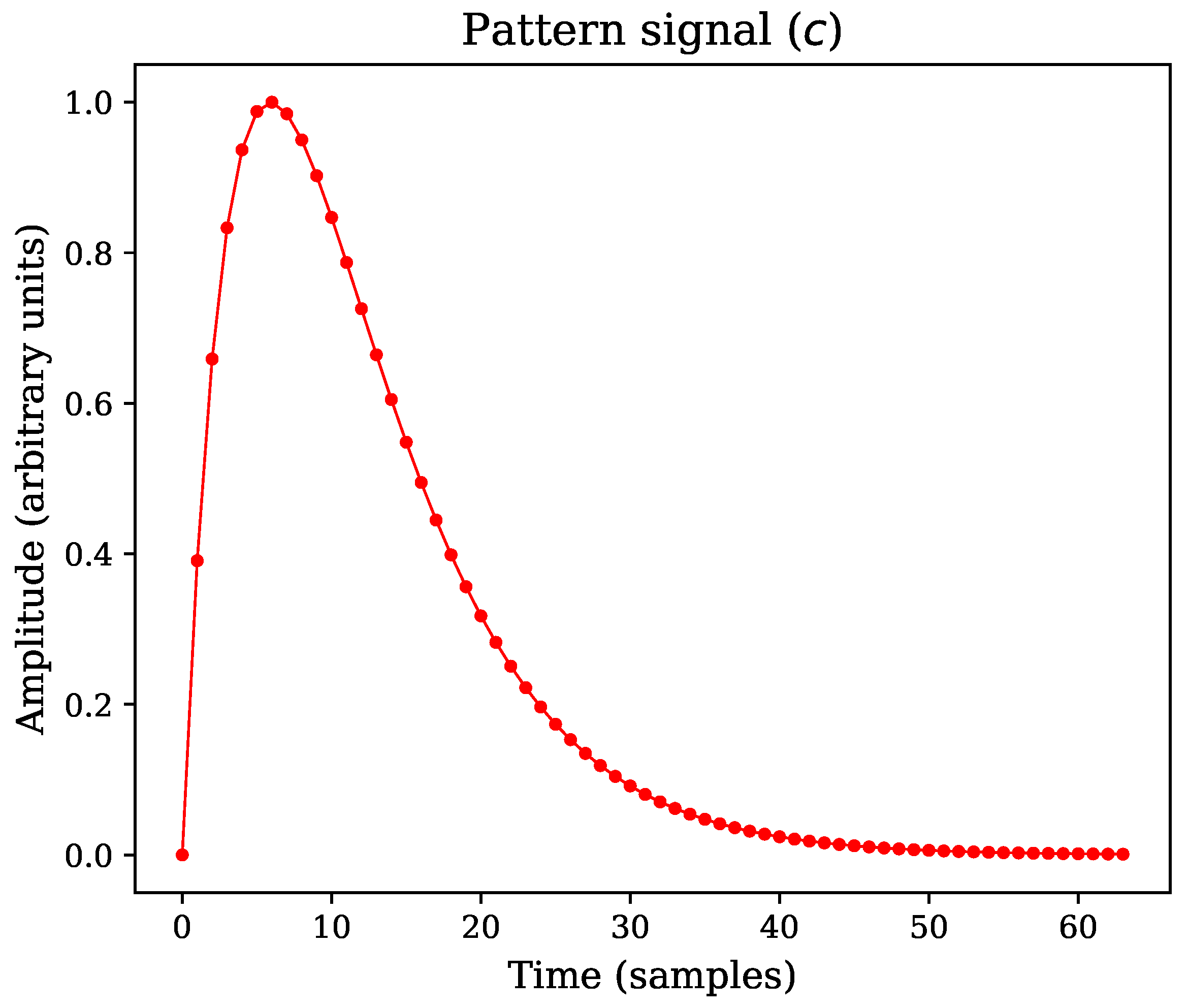

- Pattern type: double-exponential pulse model [1], triangular, rectangular, and Kronecker delta.

- Pattern length N: defines the number of discrete samples of the template.

- Asymmetry factor p: affects the asymmetry of the pulses.

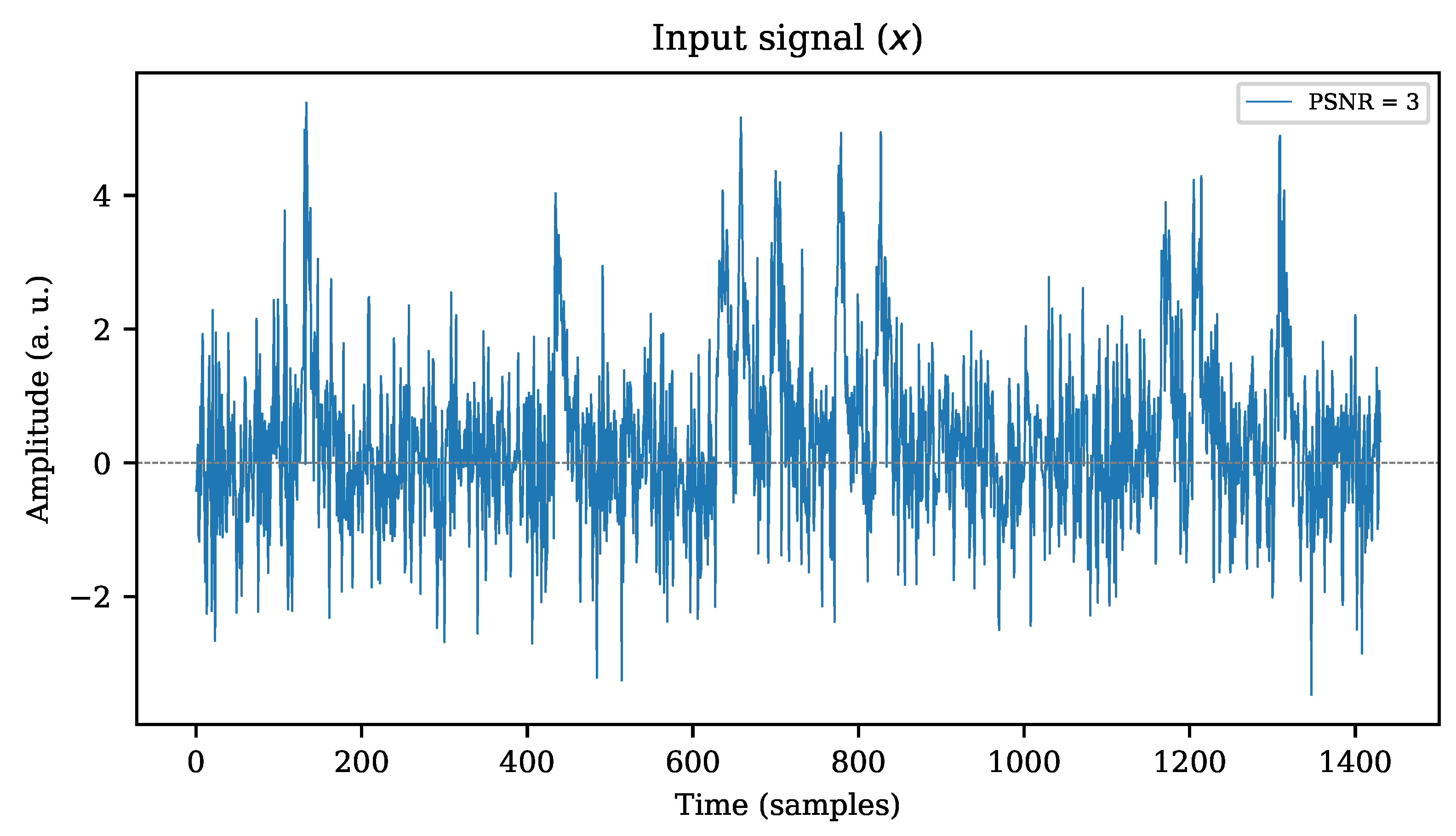

- Number of pulses per trace k: sets how many times the pattern c is replicated to synthesize the stimulus signal x.

- PSNR range: each simulation run comprises the performance grading of both correlation algorithms ( and ) over diverse noise levels. The PSNR range sets the lower and upper PSNR limits, for which the stimulus signal x is synthesized on each run.

- PSNR step: the step size sets the granularity of the expected results. The smaller the step is set, the larger the number of simulation runs are executed. Multiple stimulus signals x are synthesized and evaluated with diverse PSNR values within the imposed range.

- Threshold level range: the algorithms’ performance evaluation depends on how well they detect real events, and their ability to reject spurious ones. Thus, multiple runs are executed to sweep over diverse threshold values at each PSNR step. A cross-level trigger algorithm is run over each correlated output ( and ) as a means of two-stage discrimination. Since the trigger is meant to be executed over a correlated index, real values between 0 and 1 are expected.

- Threshold level step: similarly to the PSNR step, the threshold level step sets the granularity of the threshold level sweep within the corresponding range.

- The exponential parameter sets the mean interval time between successive pulses. The larger this constant, the lower the probability of pulse overlapping (pile-up) [1]. This constant is expressed in units of pattern length N. As a special case, if , pulse overlapping never occurs.

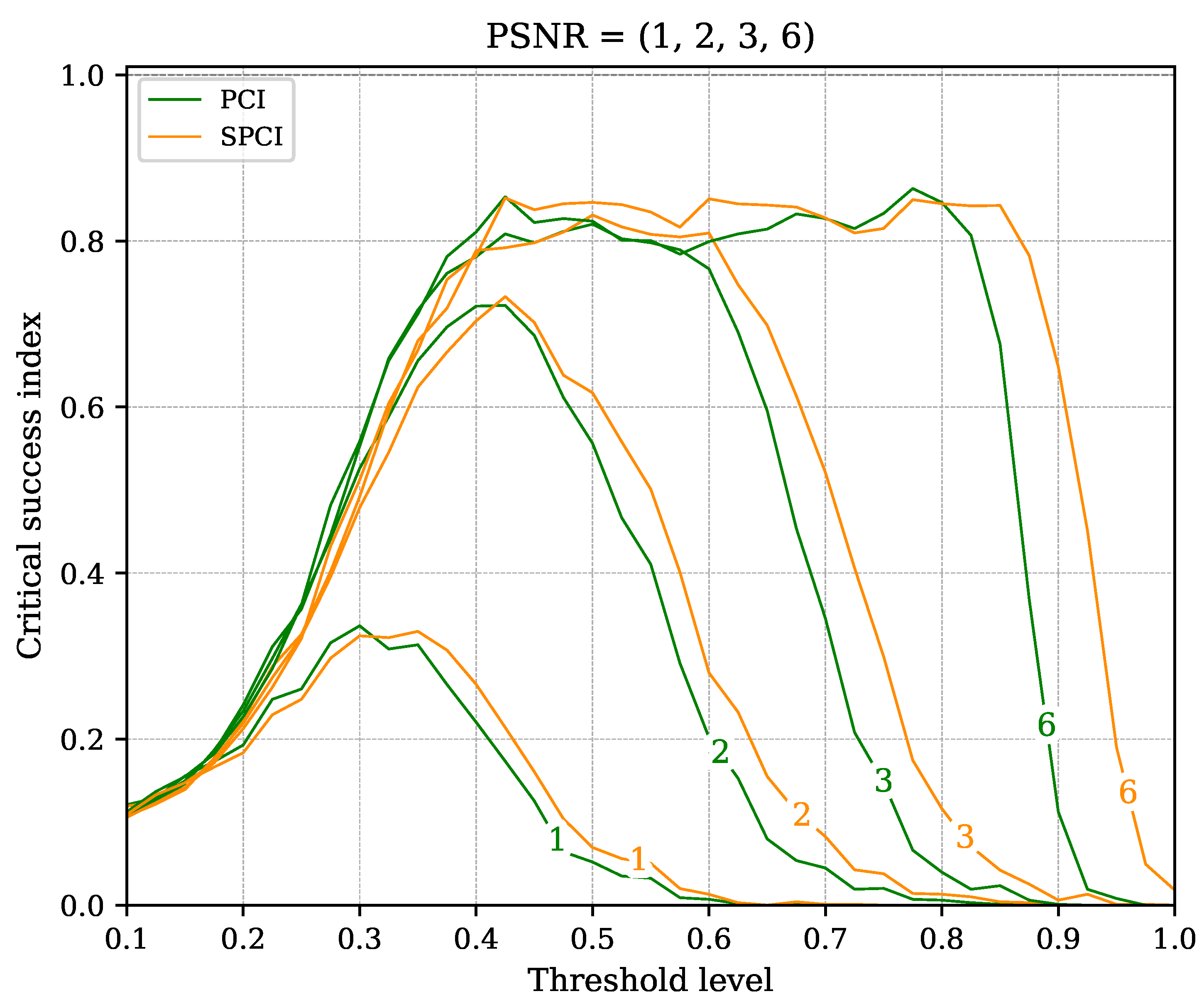

4.3.3. Amplitude Discrimination Using Threshold Level

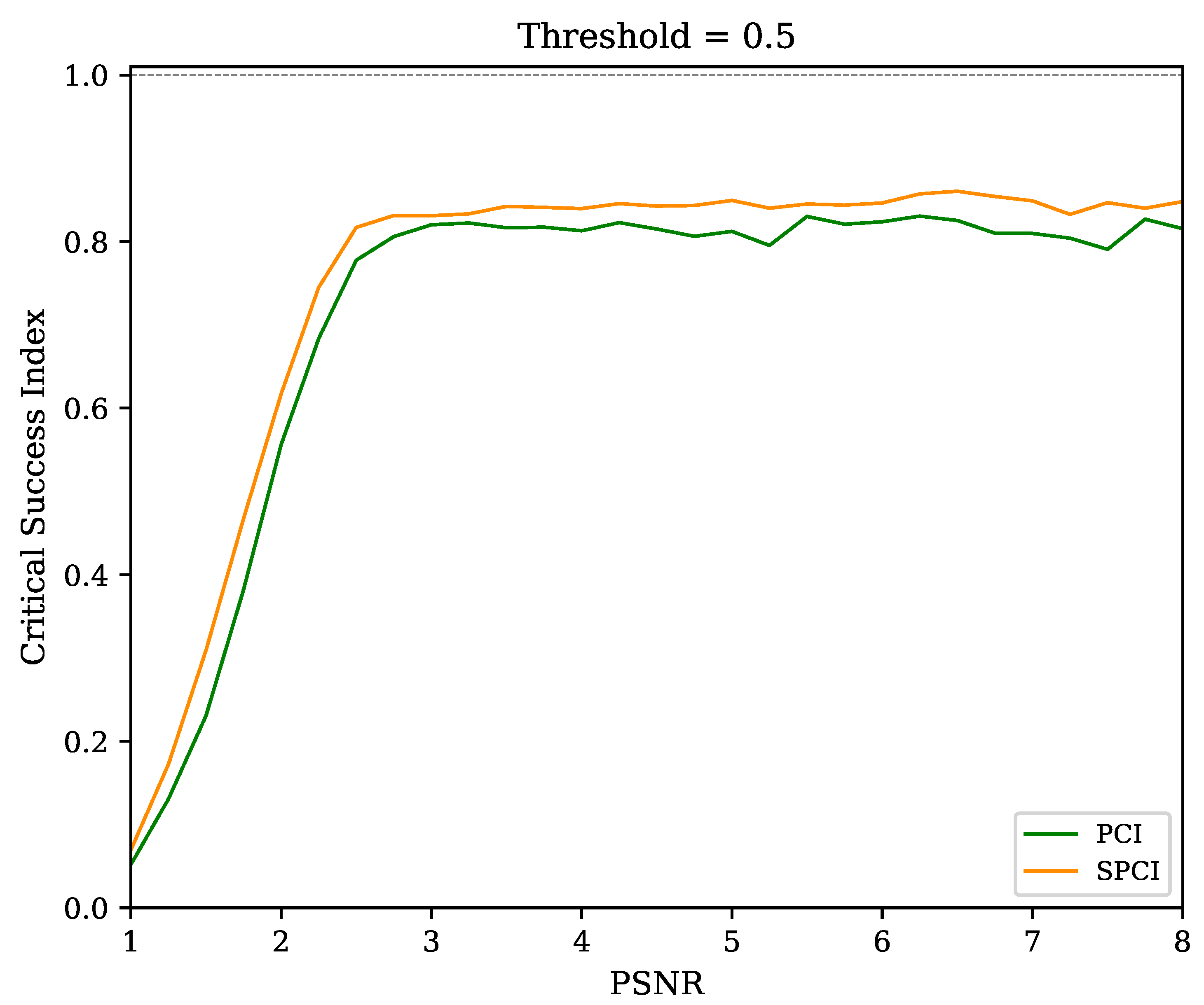

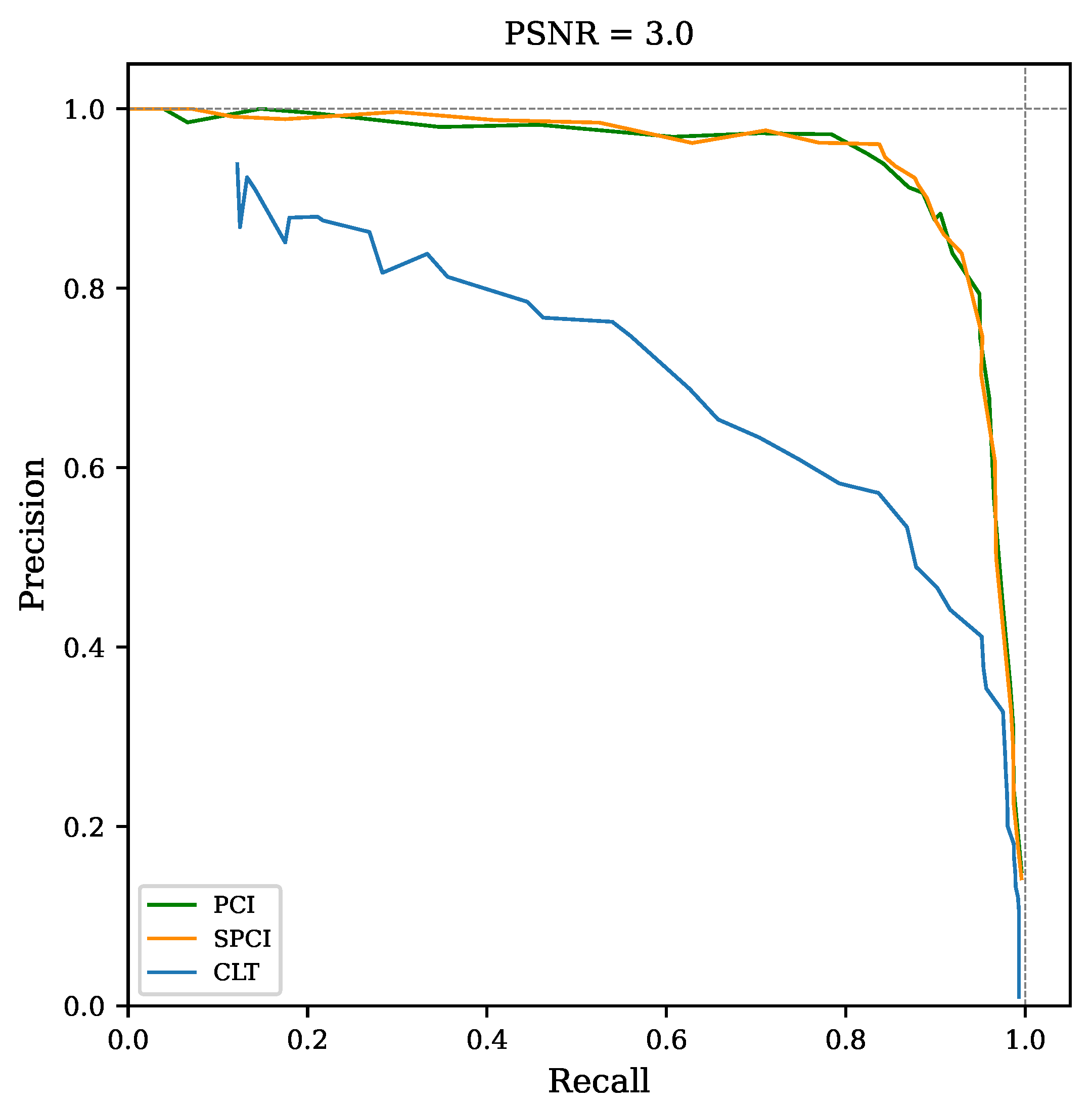

4.3.4. Detection Performance Estimation

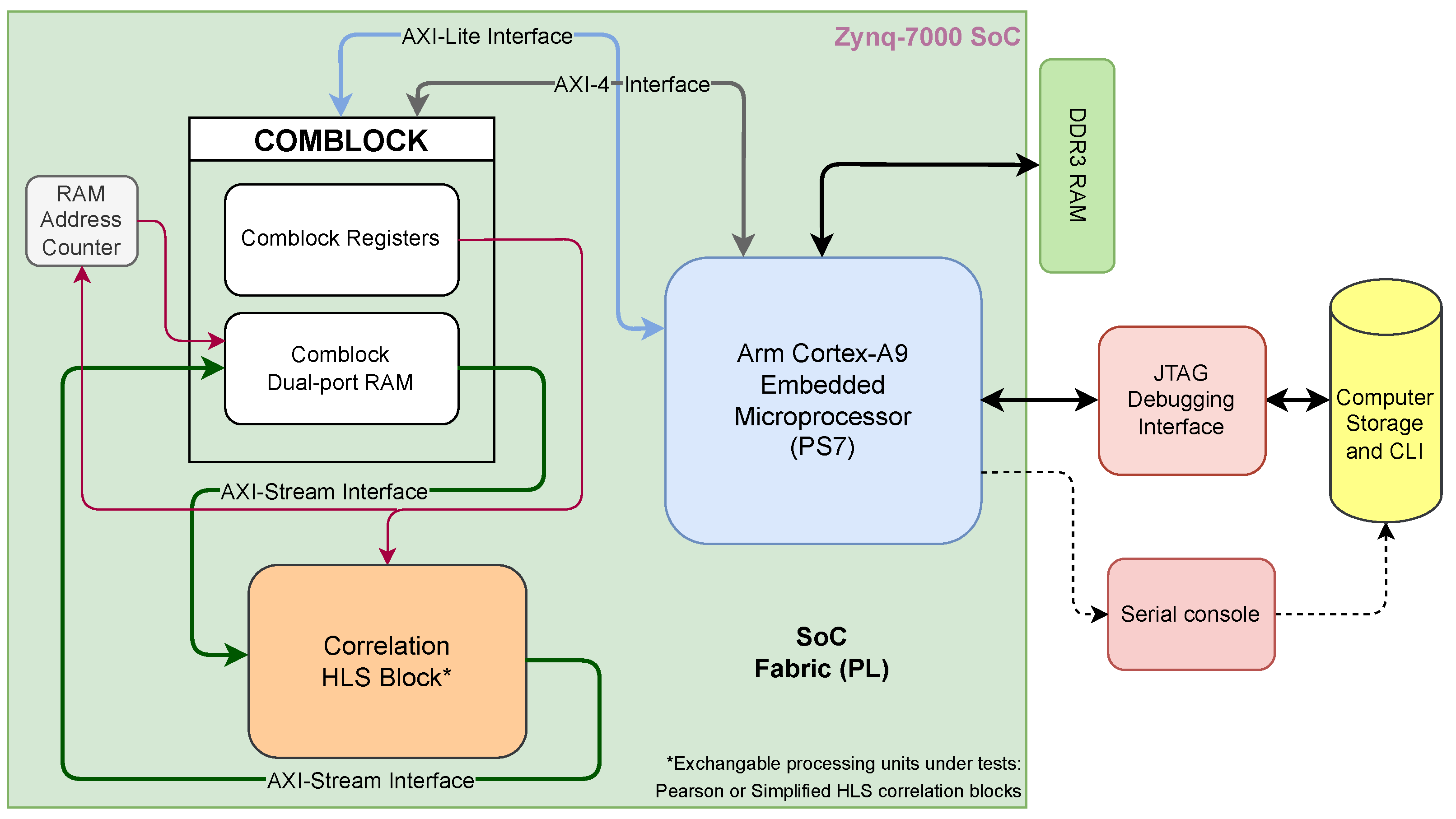

4.4. Hardware Implementation

- An important compression ratio was achieved by quantizing the data to a 14-bit fixed-point representation (as done by [45,46]), rather than using the double-precision floating-point numeric resolution of the original Python simulation. Such optimization methods have been proven to reduce the required hardware resources in PSD and machine learning applications without significantly affecting the accuracy [47,48,49].

- The stimulus signal x was fed into the IPs from a circular buffer in a triggered fashion. This synchronization technique allowed us to easily align the processed output data and compare them with the expected (simulated) results.

5. Results

- Pattern signal vector size: samples;

- Pattern signal type: double exponential pulse;

- Asymmetry factor: ;

- Number of pulses per trace: ;

- Exponential distribution constant: ;

- Variable PSNR between 1.0 and 8.0 with 0.25 step size;

- Variable threshold level between 0.1 and 1.75 with 0.025 step size.

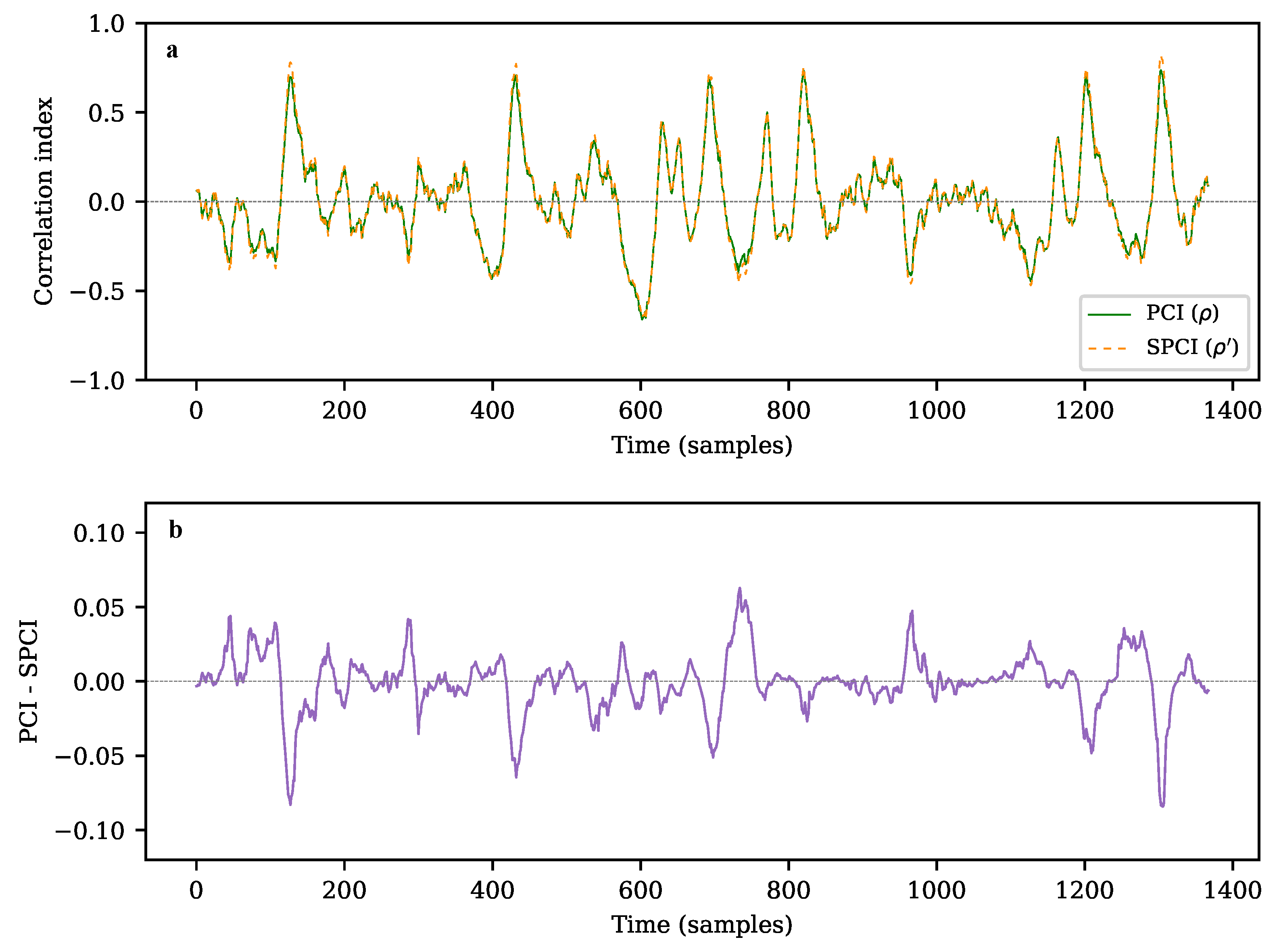

5.1. Simulation

5.1.1. Noise Immunity

5.1.2. Recognition Performance

5.1.3. Simulation Execution Benchmark

5.2. Hardware Implementation

6. Discussion

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| PCI | Pearson’s correlation index |

| SPCI | Simplified Pearson’s correlation index |

| CLT | Cross-level trigger |

| FPGA | Field-programmable gate array |

| PL | Programmable logic |

| PS7 | Processing System |

| SoC | System-on-a-chip |

| IP Core | Intellectual Property Core |

| ComBlock | Communication Block IP Core |

| HLS | High-level synthesis |

| DSP | Digital signal processor |

| PSD | Pulse-shape discrimination |

| FIR | Finite impulse response |

| ILA | Integrated logic analyzer |

| CSI | Critical success index |

| PR | Precision-recall |

| AUC | Area under curve |

| PSNR | Peak signal-to-noise ratio |

| TP | True positives |

| FP | False positives |

| FN | False negatives |

| TN | True negatives |

| MAE | Mean absolute error |

| NMAE | Normalized mean absolute error |

Appendix A. Pseudocode of HLS IP Cores

| Algorithm A1 Pseudocode of HLS IP Cores |

|

| Algorithm A2 Pseudocode snippet of standardization (SD) for Pearson’s correlation index (PCI) |

|

| Algorithm A3 Pseudocode snippet of standardization (MAD) for simplified correlation index (SPCI). |

|

References

- Knoll, G.F. Radiation Detection and Measurement; John Wiley & Sons: Hoboken, NJ, USA, 2010. [Google Scholar]

- Angelucci, B.; Anzivino, G.; Avanzini, C.; Biino, C.; Bizzeti, A.; Bucci, F.; Cassese, A.; Cenci, P.; Ciaranfi, R.; Collazuol, G.; et al. Pion–Muon separation with a RICH prototype for the NA62 experiment. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2010, 621, 205–211. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, Y.; Zhao, Q. Adaptive ViBe Algorithm Based on Pearson Correlation Coefficient. In Proceedings of the IEEE 2019 Chinese Automation Congress (CAC), Hangzhou, China, 22–24 November 2019; pp. 4885–4889. [Google Scholar] [CrossRef]

- Zhang, C.C.; Fang, J.D. Edge Detection Based on Improved Sobel Operator; Atlantis Press: Dordrecht, The Netherlands, 2016. [Google Scholar] [CrossRef][Green Version]

- Nakhostin, M. A General-Purpose Digital Pulse Shape Discrimination Algorithm. IEEE Trans. Nucl. Sci. 2019, 66, 838–845. [Google Scholar] [CrossRef]

- Wurtz, R.E. Consistent Principles for Particle ID from PSD Systems; SPIE: Bellingham, WA, USA, 2019; p. 34. [Google Scholar] [CrossRef]

- Chandhran, P.; Holbert, K.E.; Johnson, E.B.; Whitney, C.; Vogel, S.M. Neutron and gamma ray discrimination for CLYC using normalized cross correlation analysis. In Proceedings of the 2014 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), Seattle, WA, USA, 8–15 November 2014; pp. 1–8. [Google Scholar] [CrossRef]

- Digilent. ZedBoard Hardware User’s Guide. Available online: https://files.digilent.com/resources/programmable-logic/zedboard/ZedBoard_HW_UG_v2_2.pdf (accessed on 21 March 2022).

- Cong, J.; Liu, B.; Neuendorffer, S.; Noguera, J.; Vissers, K.; Zhang, Z. High-Level Synthesis for FPGAs: From Prototyping to Deployment. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2011, 30, 473–491. [Google Scholar] [CrossRef]

- Huang, Y.; Bao, H.; Qi, X. Seismic Random Noise Attenuation Method Based on Variational Mode Decomposition and Correlation Coefficients. Electronics 2018, 7, 280. [Google Scholar] [CrossRef]

- Pani, D.; Barabino, G.; Citi, L.; Meloni, P.; Raspopovic, S.; Micera, S.; Raffo, L. Real-Time Neural Signals Decoding onto Off-the-Shelf DSP Processors for Neuroprosthetic Applications. IEEE Trans. Neural Syst. Rehabil. Eng. 2016, 24, 993–1002. [Google Scholar] [CrossRef] [PubMed]

- Ordóñez, L.G.G.; Molina, R.S.; Morales, I.R.; Crespo, M.L.; Cicuttin, A.; Carrato, S.; Ramponi, G.; Figueroa, H.E.P.; Escobar, M.G.B. Pulse Shape Discrimination for Online Data Acquisition in Water Cherenkov Detectors Based on FPGA/SoC. In Proceedings of the 37th International Cosmic Ray Conference (ICRC2021), Berlin, Germany, 12–23 July 2021; Sissa Medialab: Trieste, Italy, 2021; p. 274. [Google Scholar] [CrossRef]

- Blair, B.; Chen, C.; Glenn, A.; Kaplan, A.; Ruz, J.; Simms, L.; Wurtz, R. Gaussian mixture models as automated particle classifiers for fast neutron detectors. Stat. Anal. Data Mining ASA Data Sci. J. 2019, 12, 479–488. [Google Scholar] [CrossRef]

- Iniguez-Lomeli, F.J.; Bornat, Y.; Renaud, S.; Barron-Zambrano, J.H.; Rostro-Gonzalez, H. A real-time FPGA-based implementation for detection and sorting of bio-signals. Neural Comput. Appl. 2021, 33, 12121–12140. [Google Scholar] [CrossRef]

- Pollastrone, F.; Riva, M.; Marocco, D.; Belli, F.; Centioli, C. Automatic pattern recognition on electrical signals applied to neutron gamma discrimination. Fusion Eng. Des. 2017, 123, 969–974. [Google Scholar] [CrossRef]

- Glenn, A.; Cheng, Q.; Kaplan, A.D.; Wurtz, R. Pulse pileup rejection methods using a two-component Gaussian Mixture Model for fast neutron detection with pulse shape discriminating scintillator. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2021, 988, 164905. [Google Scholar] [CrossRef]

- Simms, L.M.; Blair, B.; Ruz, J.; Wurtz, R.; Kaplan, A.D.; Glenn, A. Pulse discrimination with a Gaussian mixture model on an FPGA. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2018, 900, 1–7. [Google Scholar] [CrossRef]

- Alharbi, T. Distance metrics for digital pulse-shape discrimination of scintillator detectors. Radiat. Phys. Chem. 2019, 156, 205–209. [Google Scholar] [CrossRef]

- Moore, C.H.; Lin, W. FPGA Correlator for Applications in Embedded Smart Devices. Biosensors 2022, 12, 236. [Google Scholar] [CrossRef] [PubMed]

- Wang, L.; Pun, S.H.; Mak, P.U.; Klug, A.; Zhang, B.J.; Vai, M.I.; Lei, T.C. A real-time correlational combination algorithm to improve SNR for multi-channel neural recordings. In Proceedings of the 2021 IEEE Asia Pacific Conference on Circuit and Systems (APCCAS), Penang, Malaysia, 22–26 November 2021; pp. 213–216. [Google Scholar] [CrossRef]

- Lee, D.; Lee, S.; Oh, S.; Park, D. Energy-Efficient FPGA Accelerator With Fidelity-Controllable Sliding-Region Signal Processing Unit for Abnormal ECG Diagnosis on IoT Edge Devices. IEEE Access 2021, 9, 122789–122800. [Google Scholar] [CrossRef]

- He, X.; Li, L.; Liu, Y.; Yu, X.; Meng, J. A Two-Stage Biomedical Event Trigger Detection Method Integrating Feature Selection and Word Embeddings. IEEE/ACM Trans. Comput. Biol. Bioinform. 2018, 15, 1325–1332. [Google Scholar] [CrossRef]

- Sevilla, D.J.R. Probability distributions for Poisson processes with pile-up. arXiv 2013, arXiv:1310.7566. [Google Scholar]

- Romo, R.; Hernández, A.; Zainos, A.; Salinas, E. Correlated Neuronal Discharges that Increase Coding Efficiency during Perceptual Discrimination. Neuron 2003, 38, 649–657. [Google Scholar] [CrossRef]

- Faisal, M.; Schiffer, R.T.; Flaska, M.; Pozzi, S.A.; Wentzloff, D.D. A correlation-based pulse detection technique for gamma-ray/neutron detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2011, 652, 479–482. [Google Scholar] [CrossRef]

- Rodgers, J.L.; Nicewander, W.A. Thirteen Ways to Look at the Correlation Coefficient. Am. Stat. 1988, 42, 59–66. [Google Scholar] [CrossRef]

- Goadrich, M.; Oliphant, L.; Shavlik, J. Learning Ensembles of First-Order Clauses for Recall-Precision Curves: A Case Study in Biomedical Information Extraction; Springer: Berlin/Heidelberg, Germany, 2004; pp. 98–115. [Google Scholar] [CrossRef]

- Johnson, R.A.; Chawla, N.V.; Hellmann, J.J. Species distribution modeling and prediction: A class imbalance problem. In Proceedings of the 2012 Conference on Intelligent Data Understanding, Boulder, CO, USA, 24–26 October 2012; pp. 9–16. [Google Scholar] [CrossRef]

- Saito, T.; Rehmsmeier, M. The Precision-Recall Plot Is More Informative than the ROC Plot When Evaluating Binary Classifiers on Imbalanced Datasets. PLoS ONE 2015, 10, e0118432. [Google Scholar] [CrossRef]

- Rana, K.; Singh, R.; Sayann, K. Correlation based novel technique for real time oscilloscope triggering for complex waveforms. Measurement 2010, 43, 299–311. [Google Scholar] [CrossRef]

- Eldukhri, E.E.; Anayi, F.J.; Fahmy, A.A.; Etumi, A.A.A. New Algorithm Based on Auto-Correlation and Cross-Correlation Scheme to Detect the Internal Fault in Single Phase Transformer; Institution of Engineering and Technology: Stevenage, England, 2014; p. 12.79. [Google Scholar] [CrossRef]

- Gorard, S. An Absolute Deviation Approach to Assessing Correlation. Br. J. Educ. Soc. Behav. Sci. 2015, 5, 73–81. [Google Scholar] [CrossRef]

- Schaefer, J.T. The Critical Success Index as an Indicator of Warning Skill. Weather. Forecast. 1990, 5, 570–575. [Google Scholar] [CrossRef]

- Baldwin, M.E.; Kain, J.S. Sensitivity of Several Performance Measures to Displacement Error, Bias, and Event Frequency. Weather. Forecast. 2006, 21, 636–648. [Google Scholar] [CrossRef]

- Larner, A. Assessing cognitive screeners with the critical success index. Prog. Neurol. Psychiatry 2021, 25, 33–37. [Google Scholar] [CrossRef]

- Tharwat, A. Classification assessment methods. Appl. Comput. Inform. 2021, 17, 168–192. [Google Scholar] [CrossRef]

- Berrar, D. On the Noise Resilience of Ranking Measures; Springer International Publishing: Berlin, Germany, 2016; pp. 47–55. [Google Scholar] [CrossRef]

- Sofaer, H.R.; Hoeting, J.A.; Jarnevich, C.S. The area under the precision-recall curve as a performance metric for rare binary events. Methods Ecol. Evol. 2019, 10, 565–577. [Google Scholar] [CrossRef]

- Davis, J.; Goadrich, M. The Relationship between Precision-Recall and ROC Curves; ACM Press: New York, NY, USA, 2006; pp. 233–240. [Google Scholar] [CrossRef]

- kyu Choi, Y.; Cong, J. HLS-based optimization and design space exploration for applications with variable loop bounds. In Proceedings of the 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Marrakech, Morocco, 5–8 November 2018; pp. 1–8. [Google Scholar] [CrossRef]

- Tsoutsouras, V.; Koliogeorgi, K.; Xydis, S.; Soudris, D. An Exploration Framework for Efficient High-Level Synthesis of Support Vector Machines: Case Study on ECG Arrhythmia Detection for Xilinx Zynq SoC. J. Signal Process. Syst. 2017, 88, 127–147. [Google Scholar] [CrossRef]

- Florian, W.; Valinoti, B.; García, L.G.; Cervetto, M.; Marchi, E.; Crespo, M.L.; Carrato, S.; Cicuttin, A. An Open-Source Hardware/Software Architecture for Remote Control of SoC-FPGA Based Systems. In Proceedings of the International Conference on Applications in Electronics Pervading Industry, Environment and Society, Genova, Italy, 26–27 September 2022; pp. 69–75. [Google Scholar] [CrossRef]

- Ordóñez, L.G.G.; Morales, I.R.; Crespo, M.L.; Carrato, S.; Cicuttin, A.; Perez, H.D.L.T.; Barrientos, D.; Levorato, S.; Valinoti, B.; Florian, W.; et al. DAQ platform based on SoC-FPGA for high resolution time stamping in cosmic ray detection. In Proceedings of the 36th International Cosmic Ray Conference (ICRC2019)-CRI-Cosmic Ray Indirect, Madison, WI, USA, 24 July–1 August 2019; Sissa Medialab: Trieste, Italy, 2019; p. 266. [Google Scholar] [CrossRef]

- Roy, S.; Banerjee, P. An Algorithm for Trading Off Quantization Error with Hardware Resources for MATLAB-Based FPGA Design. IEEE Trans. Comput. 2005, 54, 886–896. [Google Scholar] [CrossRef]

- Coelho, C.N.; Kuusela, A.; Li, S.; Zhuang, H.; Ngadiuba, J.; Aarrestad, T.K.; Loncar, V.; Pierini, M.; Pol, A.A.; Summers, S. Automatic heterogeneous quantization of deep neural networks for low-latency inference on the edge for particle detectors. Nat. Mach. Intell. 2021, 3, 675–686. [Google Scholar] [CrossRef]

- Duarte, J.; Han, S.; Harris, P.; Jindariani, S.; Kreinar, E.; Kreis, B.; Ngadiuba, J.; Pierini, M.; Rivera, R.; Tran, N.; et al. Fast inference of deep neural networks in FPGAs for particle physics. J. Instrum. 2018, 13, P07027. [Google Scholar] [CrossRef]

- Molina, R.S.; Garcia, L.G.; Morales, I.R.; Crespo, M.L.; Ramponi, G.; Carrato, S.; Cicuttin, A.; Perez, H. Compression of NN-Based Pulse-Shape Discriminators in Front-End Electronics for Particle Detection. In Proceedings of the International Conference on Applications in Electronics Pervading Industry, Environment and Society, Genova, Italy, 26–27 September 2022; pp. 93–99. [Google Scholar] [CrossRef]

- Fahim, F.; Hawks, B.; Herwig, C.; Hirschauer, J.; Jindariani, S.; Tran, N.; Carloni, L.P.; Guglielmo, G.D.; Harris, P.; Krupa, J.; et al. hls4ml: An Open-Source Codesign Workflow to Empower Scientific Low-Power Machine Learning Devices. arXiv 2021, arXiv:2103.05579. [Google Scholar] [CrossRef]

- Garcia, L.G.; Molina, R.S.; Crespo, M.L.; Carrato, S.; Ramponi, G.; Cicuttin, A.; Morales, I.R.; Perez, H. Muon–Electron Pulse Shape Discrimination for Water Cherenkov Detectors Based on FPGA/SoC. Electronics 2021, 10, 224. [Google Scholar] [CrossRef]

- Aarrestad, T.; Loncar, V.; Ghielmetti, N.; Pierini, M.; Summers, S.; Ngadiuba, J.; Petersson, C.; Linander, H.; Iiyama, Y.; Guglielmo, G.D.; et al. Fast convolutional neural networks on FPGAs with hls4ml. Mach. Learn. Sci. Technol. 2021, 2, 045015. [Google Scholar] [CrossRef]

- Xiao, Q.; Liang, Y.; Lu, L.; Yan, S.; Tai, Y.W. Exploring Heterogeneous Algorithms for Accelerating Deep Convolutional Neural Networks on FPGAs. In Proceedings of the 54th Annual Design Automation Conference 2017, Austin, TX, USA, 18–22 June 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Chen, K.; Chen, H.; Wu, W.; Xu, H.; Yao, L. Optimization on fixed low latency implementation of the GBT core in FPGA. J. Instrum. 2017, 12, P07011. [Google Scholar] [CrossRef]

- Nottbeck, N.; Schmitt, D.C.; Büscher, P.D.V. Implementation of high-performance, sub-microsecond deep neural networks on FPGAs for trigger applications. J. Instrum. 2019, 14, P09014. [Google Scholar] [CrossRef]

- Willmott, C.; Matsuura, K. Advantages of the mean absolute error (MAE) over the root mean square error (RMSE) in assessing average model performance. Clim. Res. 2005, 30, 79–82. [Google Scholar] [CrossRef]

| Area Optimization | Performance Optimization | |||

|---|---|---|---|---|

| PCI | SPCI | PCI | SPCI | |

| Resources utilization | ||||

| LUT (53,200) | 11.21% (5962) | 15.15% (8058) | 40.13% (21,349) | 42.70% (22,718) |

| Registers (106,400) | 4.71% (5016) | 4.74% (5040) | 20.23% (21,524) | 22.06% (23,468) |

| Block RAM (140) | 0.00% (0) | 0.00% (0) | 0.00% (0) | 0.00% (0) |

| DSP Blocks (220) | 29.55% (65) | 0.45% (1) | 54.55% (120) | 24.09% (53) |

| Timing results | ||||

| Max. frequency (MHz) | 119.3 | 122.4 | 137.8 | 143.4 |

| Latency (clock cycles) | ||||

| Estimated power consumption @ 100 MHz | ||||

| Average power (mW) | 190 | 118 | 796 | 705 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cicuttin, A.; Morales, I.R.; Crespo, M.L.; Carrato, S.; García, L.G.; Molina, R.S.; Valinoti, B.; Folla Kamdem, J. A Simplified Correlation Index for Fast Real-Time Pulse Shape Recognition. Sensors 2022, 22, 7697. https://doi.org/10.3390/s22207697

Cicuttin A, Morales IR, Crespo ML, Carrato S, García LG, Molina RS, Valinoti B, Folla Kamdem J. A Simplified Correlation Index for Fast Real-Time Pulse Shape Recognition. Sensors. 2022; 22(20):7697. https://doi.org/10.3390/s22207697

Chicago/Turabian StyleCicuttin, Andres, Iván René Morales, Maria Liz Crespo, Sergio Carrato, Luis Guillermo García, Romina Soledad Molina, Bruno Valinoti, and Jerome Folla Kamdem. 2022. "A Simplified Correlation Index for Fast Real-Time Pulse Shape Recognition" Sensors 22, no. 20: 7697. https://doi.org/10.3390/s22207697

APA StyleCicuttin, A., Morales, I. R., Crespo, M. L., Carrato, S., García, L. G., Molina, R. S., Valinoti, B., & Folla Kamdem, J. (2022). A Simplified Correlation Index for Fast Real-Time Pulse Shape Recognition. Sensors, 22(20), 7697. https://doi.org/10.3390/s22207697