1. Introduction

A low-noise amplifier (LNA) is one of the key elements in a wide-band receiver. As the first element in the receiving chain, its noise figure (NF) and gain have a greater impact than other modules on the overall performance. Source impedance matching is also required to limit reflections. Conventional broadband LNA designs, such as resistive-loaded common source (CS) or common gate (CG) amplifiers, have proven difficult to meet the above requirements [

1]. On the other hand, amplifiers employing a global negative feedback can achieve low NF with good input matching, but they are prone to becoming unstable [

2]. Other alternatives, such as distributed amplifiers (DAs) [

3] or cascode amplifiers with LC broadband input-matching networks [

4,

5,

6], provide good impedance matching and high gain in a larger frequency range, but they need several inductors. Another topology used to design broadband LNAs is based on the use of current conveyors (CC) [

7,

8,

9]. Although they have many advantages, such as good input matching, high linearity, and low power consumption, they suffer from the drawback of having a relatively high NF. In this paper we explore the use of noise-canceling techniques [

10,

11,

12] to obtain a significant reduction in the NF of CC-based broadband LNAs. The goal is to present an amplifier topology that combines the advantages of a CC-based circuit with the possibility of reducing the NF at the output of the circuit.

The organization of the paper is as follows. In

Section 2, a wide-band amplifier based on CC is discussed. In

Section 3, the noise-canceling technique of a CG amplifier is presented. The CC-based amplifier with noise cancelation is introduced in

Section 4.

Section 5 reports the simulation results of the proposed LNA implemented in a UMC 65-nm CMOS process. Finally, conclusions of this work are drawn in

Section 6.

2. CMOS Current Conveyor Based LNA

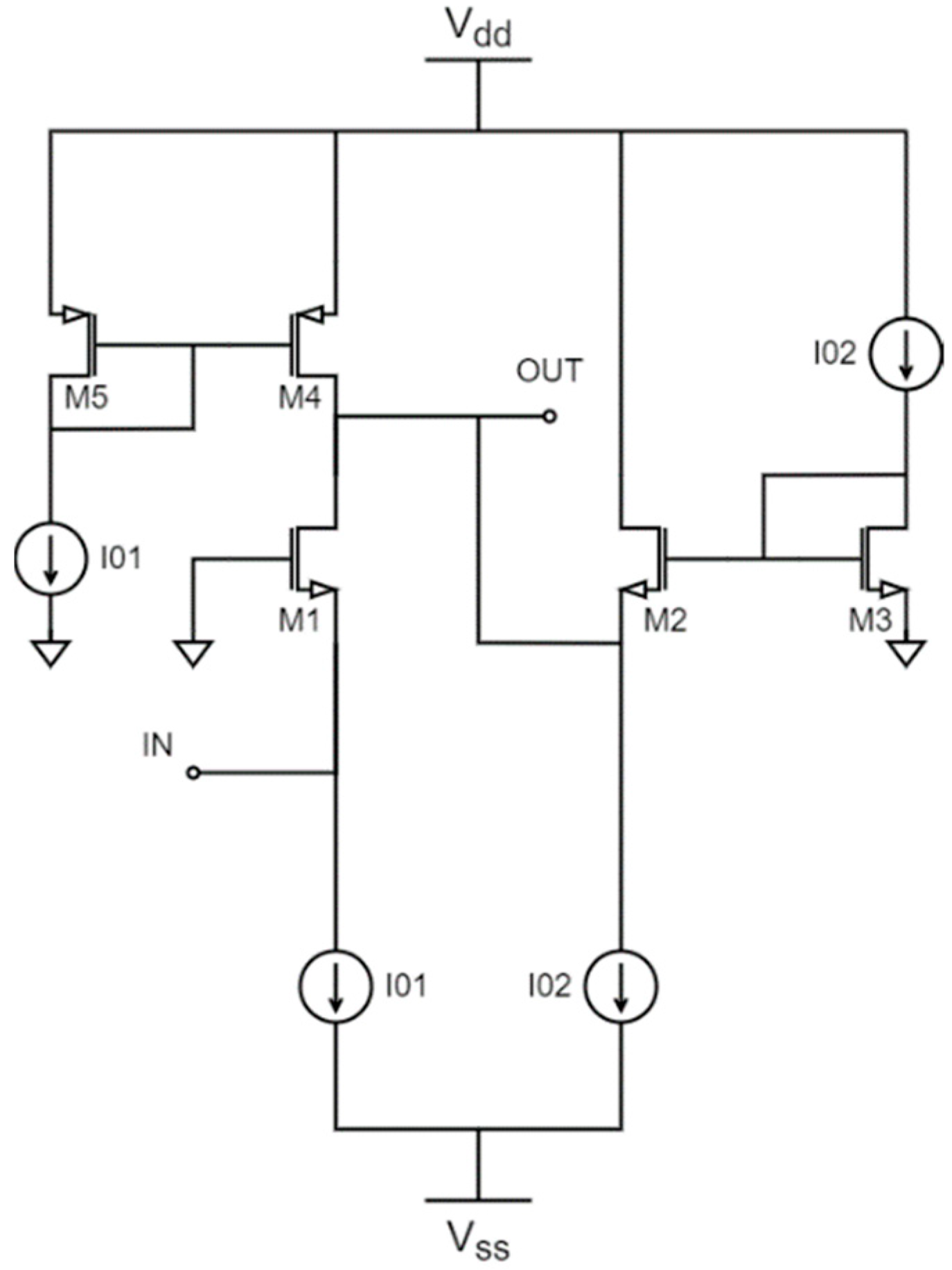

The basic topology of a CC-based amplifier using CMOS technology is shown in

Figure 1. It consists of an input CG gain stage (M1), followed by a source follower stage (M2) [

8].

The DC gain (

G), bandwidth (

), and noise factor (

F) can be calculated as shown by (1), (2), and (3), respectively, where

gm1 and

gm2 are the M1 and M2 transconductances,

CT represents the total parasitic capacitance at the output node, and γ is the excess noise factor, which is a constant that depends on the transistor size.

The circuit’s input and output impedances can be easily computed as

There is a trade-off between gm1 and gm2 and, consequently, between the transistor sizes and bias currents. Current I01 affects the gain through gm1, but has no effect on the bandwidth, while I02 controls the gain and bandwidth through gm2 (if I02 is increased, the bandwidth increases, but the gain is decreased). On the other hand, when gm1 increases, F decreases, as shown in (3). This can be done by increasing the size of M1 or the current I01. Likewise, if M2 and M4 are either smaller or biased with a lower I02, F decreases. Finally, the input and output impedances are directly related to their associated transistors and bias currents. For example, through I01, Zin can be matched to the source impedance without resorting to matching networks, allowing for a much smaller circuit when compared to conventional topologies. This is one of the main advantages of this approach. Following this discussion, the bias currents I01 and I02 are selected as 1 mA and 200 µA, respectively, to maintain a reasonable power consumption.

The complete implementation of the circuit schematic is shown in

Figure 2, where the ideal current sources have been replaced by current mirrors. The high number of transistors certainly affects the performance of the circuit, especially bandwidth, noise, and power consumption. Due to the low output conductance of transistors in deep submicron technologies, the input impedance also deviates from the conventional 1/

gm value. This, rather than being a problem, can be useful to isolate the input-matching condition from the noise-canceling one, providing a degree of freedom in the input-matching design [

12].

3. Noise-Canceling Technique Applied to a CG Stage

Equation (3) shows that the input common-gate transistor (M1) is the main noise contributor. Various architectures can be found in the literature to cancel the noise of this topology [

10,

11,

12]. The simplified diagram of a common-gate stage with noise cancelation is depicted in

Figure 3. With this technique, the noise of the input transistor passes through two different paths (transistors MX and MY), and is canceled at the output, while the input signal is boosted. This can be seen better in the inset of

Figure 4, where the noise and the signals are plotted on the schematic. Transistor M1 is the main noise contributor, and a noise source (i

noise) represents its contribution in the circuit. This source generates a voltage at the source of M1 and a fully correlated voltage at the drain with the same magnitude and opposite sign. The noise reaches the output through two different paths, and thanks to the CS inverting stages composed by transistors MX and MY, it is canceled at the output. In contrast, the input signal is amplified through the same paths thanks to the CS-CG inverting amplifier (transistors M1 and MY) and the CS inverting amplifier (MX) and is amplified at the output instead of being canceled.

To achieve perfect noise cancelation, the two noise paths should have the same gain. Therefore, transistors MX and MY must be independently biased. It is important to note that transistors MX and MY also introduce noise into the circuit, so they must be carefully designed. Thus, the key to achieve a low overall NF has now shifted to a low noise implementation in the noise-canceling stage.

4. LNA Based on CC with Noise Canceling

To better understand the improvements introduced by the noise-canceling technique, two different implementations were developed with the same sizing and bias currents. On the one hand, a current conveyor-based LNA is implemented following the schematic depicted in

Figure 2. On the other hand, a second implementation of the LNA applying the noise cancelation technique is developed following the schematic shown in

Figure 4.

The circuits are developed using UMC 65-nm CMOS technology with a ±1.2 V DC supply voltage. A summary of the device sizing information is given in

Table 1, where the length of all the MOSFETs is fixed to the minimum allowed value of 65 nm. Note that the bias currents I

01 and I

02 are selected as 1 mA and 200 µA, respectively, and the DC voltages V

BF and V

BX are 0.35 V each. In addition, the resistor R

Y is selected as 220 ohms. The schematic of the proposed noise-canceling LNA based on CC is presented in

Figure 4. This circuit combines the CC-based approach shown in

Figure 2 with the noise-canceling technique presented in

Section 3. As explained above, the input transistor generates a noise contribution of equal magnitude but opposite phase at its drain and source terminals. These two noise signals pass through two inverting paths and are canceled at the output. On the contrary, the input signal has the same sign on the drain and source terminals of the input transistor, so it passes through the two inverting paths, and it is added at the output. In the design of this circuit, the size of the input stage should be determined to obtain a good broadband input impedance match. The noise-canceling stage must be designed to achieve broadband noise cancelation while introducing as little noise as possible and degrading gain, bandwidth, power consumption, and input matching as little as possible. Using a CC-based LNA as the input stage instead of a simple CG stage gives a degree of freedom in satisfying the input-matching conditions.

5. Simulation Results and Analysis

The simulated performance comparison of the LNA based on CC (CC) and the proposed LNA based on CC with noise cancelation (CCNC) is shown in

Figure 5. The proposed technique reduces the noise figure from 4.85 dB to 3.25 dB at 1 GHz. At frequencies below 6 GHz, both circuits present a reasonable input matching, with an input return loss (S11) < −10 dB. However, at higher frequencies the input matching deteriorates slightly. This can be solved by simply increasing the bias current I

02, but at the expense of increasing the power consumption.

The layout of the proposed LNA is shown in

Figure 6. To reduce the circuit area, the BIAS-T inductor needed to bias the MX transistor is replaced by a large resistor, which is implemented in practice by the large leakage resistance of a reverse-biased p-n junction of a diode-connected MOS transistor operating in the cutoff region (2 × 0.5 µm). Note that the exact value of this resistance or its temperature and voltage dependence are not relevant, provided that it remains large enough not to influence the circuit operation at the lowest frequency required. As no inductor is present, the LNA core occupies an area of only 160 × 80 μm

2, which is among the smallest designs available in the literature.

Linearity is a very important feature of an LNA since a higher 1-dB compression point means a larger capability of receiving weak signals in the presence of strong ones. This technique presents the advantage of significantly boosting the circuit’s linearity, since the same mechanism leading to noise cancelation can also cancel partially the nonlinear distortions [

13]. The simulation results shown in

Figure 7 demonstrate an input 1-dB compression point of –2 dBm. Finally, the power dissipation of the circuit is 18.57 mW, with a DC supply of ±1.2 V.

The performance of the proposed LNA is compared in

Table 2 with recently reported LNAs available in the literature. To fairly compare the proposed CCNC LNA with the other designs, we have defined the following figure of merit (

FoM), which considers a positive contribution of amplifier gain, bandwidth, and

IIP3, and a negative contribution of power consumption, noise factor, and active area:

The proposed CCNC LNA presents the highest FoM value among the reported designs. This is because the proposed technique achieves a high bandwidth and IIP3 values using a very small area, while the gain and NF are within the average. The price to pay is a slightly higher power consumption than most of the other designs in the comparison.

6. Conclusions

A wide-band CMOS noise-canceling current conveyor-based LNA is proposed in this paper and is implemented in a standard 65-nm CMOS process. The design exploits a noise-canceling technique consisting of an amplifying stage based on a CC that provides input impedance matching, and a noise-canceling stage composed of two transistors in CS configuration that subtracts the input transistor noise contribution while adding the signal contributions. The simulation results show that the proposed CCNC LNA achieves wide-band input impedance matching (0–6.2 GHz), with high gain (15.3 dB) and low noise (4.8 dB), in a very small area (160 × 80 μm2). The circuit presents a power dissipation of 18.57 mW from a DC supply of ±1.2 V. In addition, the proposed noise-canceling technique also improves the linearity because it is capable of partially canceling nonlinear distortions. The proposed circuit achieves a remarkable IIP3 of 7.6 dB and an input P1dB of –2 dBm. The price to pay with this approach is the additional power dissipation introduced by the auxiliary amplifier in the noise-canceling path. As shown in the comparison with similar works, the proposed circuit presents the highest FoM value among the reported designs.

Author Contributions

Investigation, H.G.-V.; supervision, S.L.K. and J.d.P.; writing—original draft, D.G.-S. and J.d.P. All authors have read and agreed to the published version of the manuscript.

Funding

This work is partially supported by the Spanish Ministry of Science, Innovation and Universities (RTI2018-099189-B-C22 and PID2021-127712OB-C21) and the Canary Agency for Research, Innovation, and Information Society (ACIISI) by the TESIS2019010100 grant.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Díaz-Ortega, R.; Khemchandani, S.L.; García-Vázquez, H.; del Pino, J. Design of Low-Noise Amplifiers for Ultra-Wideband Communications; McGraw-Hill Education: New York, NY, USA, 2014. [Google Scholar]

- Vázquez, H.G.; Khemchandani, S.L.; Pulido, R.; Goñi-Iturri, A.; del Pino, J. A wideband active feedback LNA with a modified 3D inductor. Microw. Opt. Technol. Lett. 2010, 52, 1561–1567. [Google Scholar] [CrossRef]

- Del Pino, J.; Diaz, R.; Khemchandani, S. Area reduction techniques for full integrated distributed amplifier. AEU. Int. J. Electron. Commun. 2010, 64, 1055–1062. [Google Scholar] [CrossRef]

- García-Vázquez, H.; Khemchandani, S.L.; Arias-Perez, J.; del Pino, J. Flatness Improvement for a Shunt-Peaked Ultra-Wideband Low Noise Amplifier. Microw. J. 2010, 53, 74–82. [Google Scholar]

- Khemchandani, S.L.; Ramos-Valido, D.; García-Vázquez, H.; Pulido-Medina, R.; del Pino, J. A low voltage folded cascode LNA for ultra-wideband applications. Microw. Opt. Technol. Lett. 2010, 52, 2495–2500. [Google Scholar] [CrossRef]

- Del Pino, J.; Khemchandani, S.L.; Díaz-Ortega, R.; Pulido, R.; Garcia-Vazquez, H. On-Chip Inductors Optimization for Ultra Wide Band Low Noise Amplifiers. J. Circuits Syst. Comput. 2011, 20, 1231–1242. [Google Scholar] [CrossRef]

- Fabre, A.; Saaid, O.; Wiest, F.; Boucheron, C. High frequency applications based on a new current controlled conveyor. IEEE Trans. Circuits Syst. I Regul. Pap. 1996, 43, 82–91. [Google Scholar] [CrossRef]

- Seguin, F.; Godara, B.; Alicalapa, F.; Fabre, A. A Gain-Controllable Wide-Band Low-Noise Amplifier in Low-Cost 0.8-/spl mu/m Si BiCMOS technology. IEEE Trans. Microw. Theory Tech. 2004, 52, 154–160. [Google Scholar] [CrossRef]

- Touati, F.; Mnif, F. Low-noise low-power 0.35.MU.m SiGe amplifiers for 3.1–10.6GHz UWB radio receivers. IEICE Electron. Express 2004, 1, 317–321. [Google Scholar] [CrossRef][Green Version]

- Liao, C.-F.; Liu, S.-I. A Broadband Noise-Canceling CMOS LNA for 3.1–10.6-GHz UWB Receivers. IEEE J. Solid-State Circuits 2007, 42, 329–339. [Google Scholar] [CrossRef]

- Forouzanfar, M.; Naseh, S. High gain CMOS UWB LNA employing thermal noise cancellation. In Proceedings of the 2009 IEEE International Conference on Ultra-Wideband, Vancouver, BC, Canada, 9–11 September 2009; pp. 118–122. [Google Scholar] [CrossRef]

- Gao, M.; Wang, Y.; Wang, Y.; Guo, N. Design of wideband CMOS LNA with active inductor and using noise-canceling technique. In Proceedings of the 2009 3rd International Conference on Anti-Counterfeiting, Security, and Identification in Communication, Hong Kong, China, 20–22 August 2009; pp. 262–265. [Google Scholar] [CrossRef]

- Mirvakili, A.; Yavari, M. A noise-canceling CMOS LNA design for the upper band of UWB DS-CDMA receivers. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, 24–27 May 2009; pp. 217–220. [Google Scholar] [CrossRef]

- Soleymani, F.; Bastan, Y.; Amiri, P.; Maghami, M.H. A 0.3–1.4 GHz inductorless CMOS variable gain LNA based on the inverter cell and self-forward-body-bias technique. AEU. Int. J. Electron. Commun. 2019, 113, 152974. [Google Scholar] [CrossRef]

- Iji, A.; Zhu, X.; Heimlich, M. High gain/power quotient variable-gain wideband low-noise amplifier for capsule endoscopy application. Microw. Opt. Technol. Lett. 2012, 54, 2563–2565. [Google Scholar] [CrossRef]

- Baumgratz, F.D.; Li, H.; Tavernier, F.; Bampi, S.; Saavedra, C.E. A 0.4–3.3 GHz low-noise variable gain amplifier with 35 dB tuning range, 4.9 dB NF, and 40 dBm IIP2. Analog. Integr. Circuits Signal Processing 2017, 94, 9–17. [Google Scholar] [CrossRef]

- Wang, J.; Zhu, Z.; Liu, S.; Ding, R. A low-noise programmable gain amplifier with fully balanced differential difference amplifier and class-AB output stage. Microelectron. J. 2017, 64, 86–91. [Google Scholar] [CrossRef]

- Liu, H.; Boon, C.C.; He, X.; Zhu, X.; Yi, X.; Kong, L.; Heimlich, M.C. A Wideband Analog-Controlled Variable-Gain Amplifier With dB-Linear Characteristic for High-Frequency Applications. IEEE Trans. Microw. Theory Tech. 2016, 64, 533–540. [Google Scholar] [CrossRef]

- Baumgratz, F.D.; Saavedra, C.; Steyaert, M.; Tavernier, F.; Bampi, S. A Wideband Low-Noise Variable-Gain Amplifier With a 3.4 dB NF and up to 45 dB Gain Tuning Range in 130-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 1104–1108. [Google Scholar] [CrossRef]

- Hsieh, J.-Y.; Lin, K.-Y. A 0.6-V Low-Power Variable-Gain LNA in 0.18-$\mu$ m CMOS Technology. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 23–26. [Google Scholar] [CrossRef]

- Soleymani, F.; Amiri, P.; Maghami, M.H. A 0.3–5 GHz, low-power, area-efficient, high dynamic range variable gain low-noise amplifier based on tunable active floating inductor technique. Int. J. Circuit Theory Appl. 2021, 49, 3230–3247. [Google Scholar] [CrossRef]

| Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).