Design and Analysis of Soft Error Rate in FET/CNTFET Based Radiation Hardened SRAM Cell

Abstract

:1. Introduction

2. Background

3. Proposed Methodology

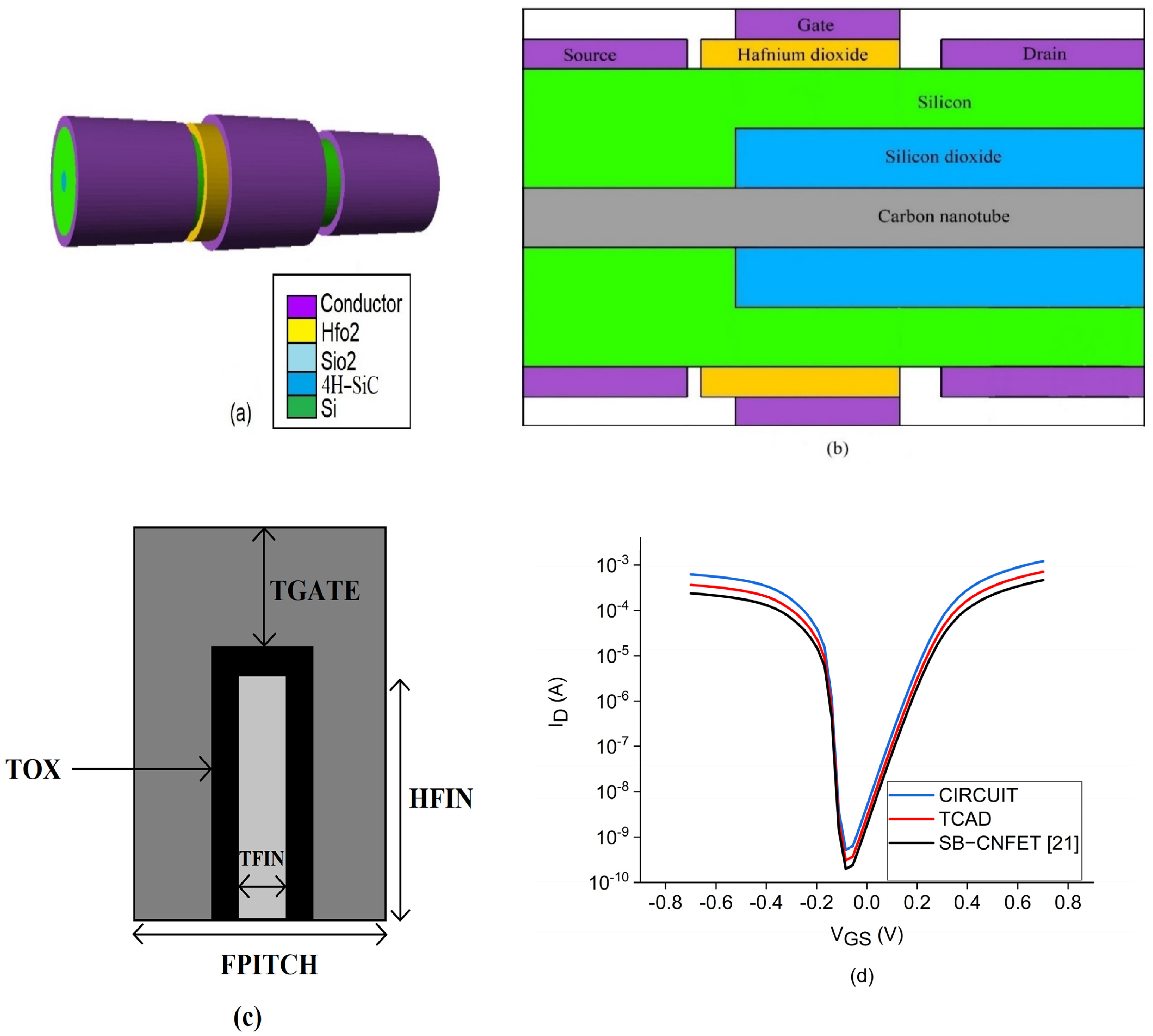

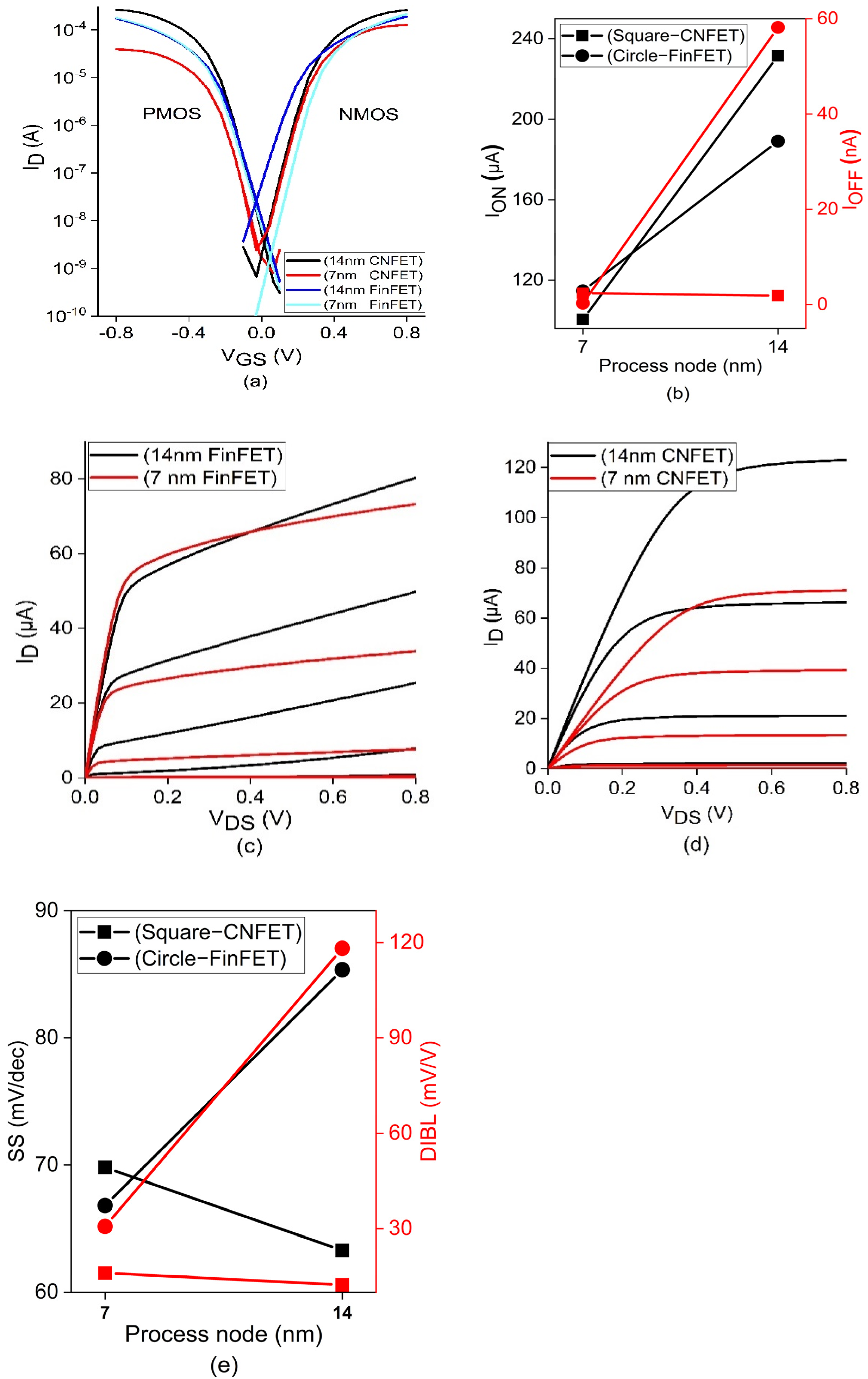

3.1. Proposed CNTFET Device Structure and Its I–V Characteristics

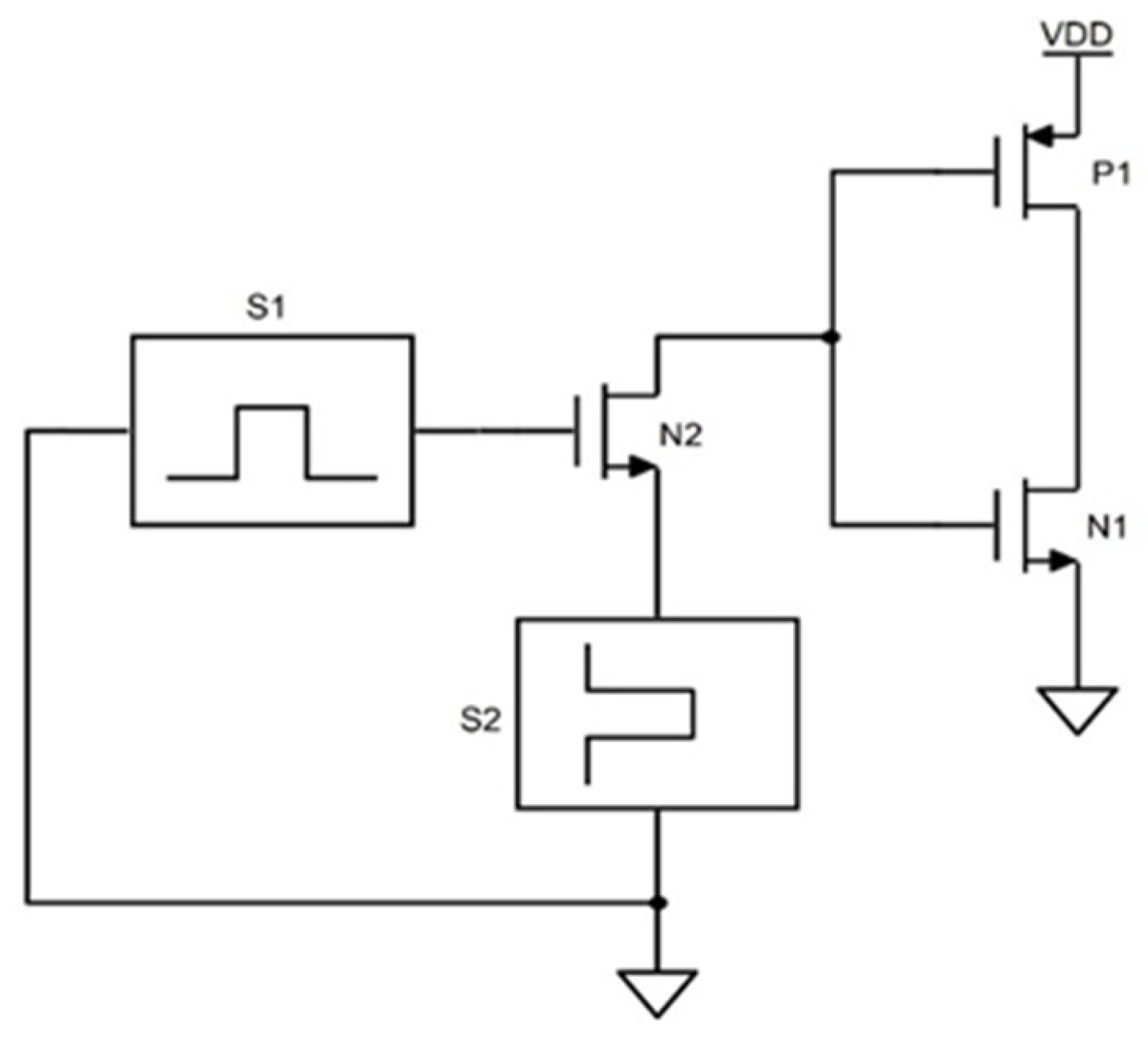

3.2. Proposed Testing Circuit for Memories

4. Architecture of RHBD Circuits

4.1. 6T Memory Cell

4.2. PS-10T Memory Cell

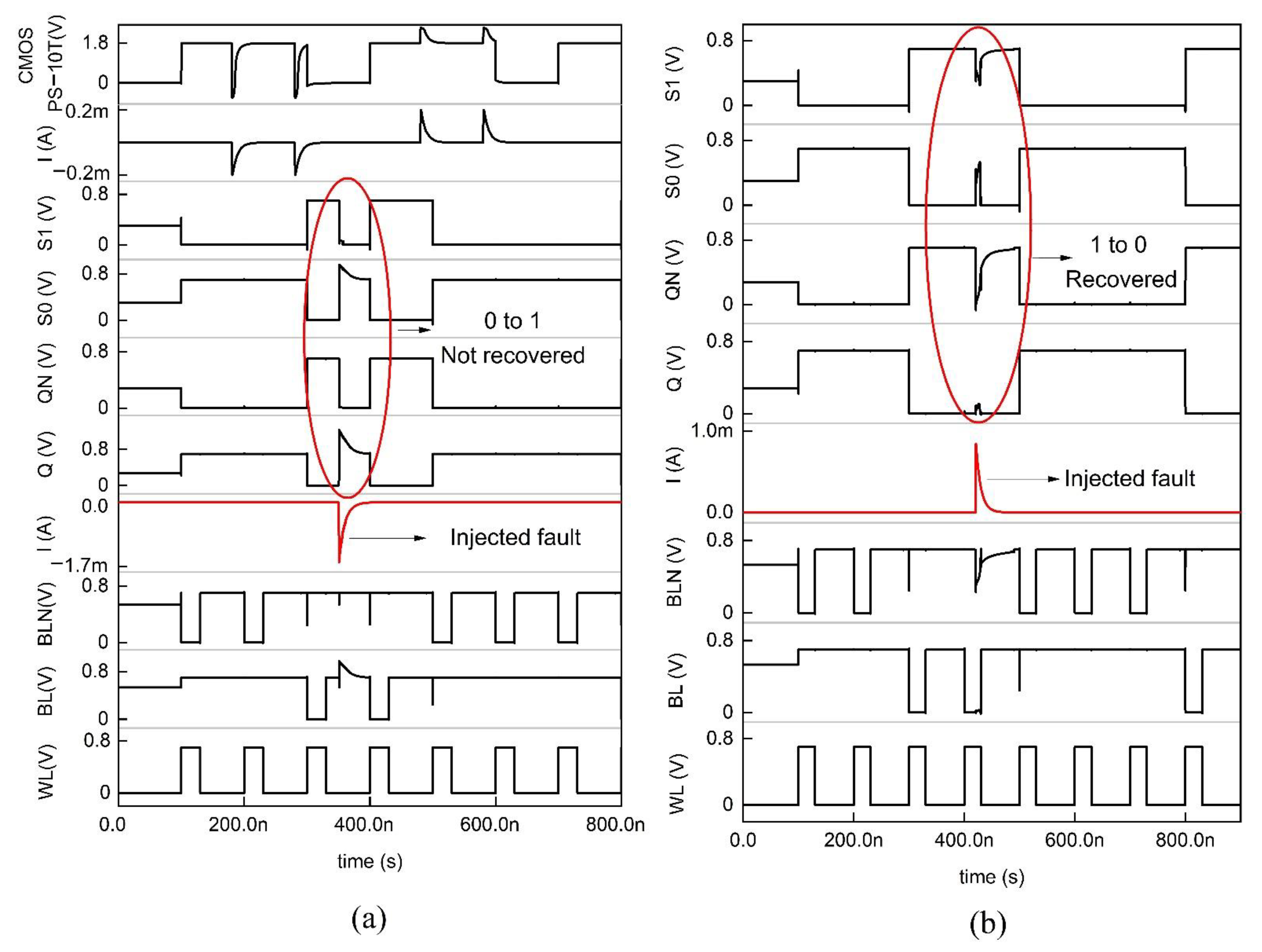

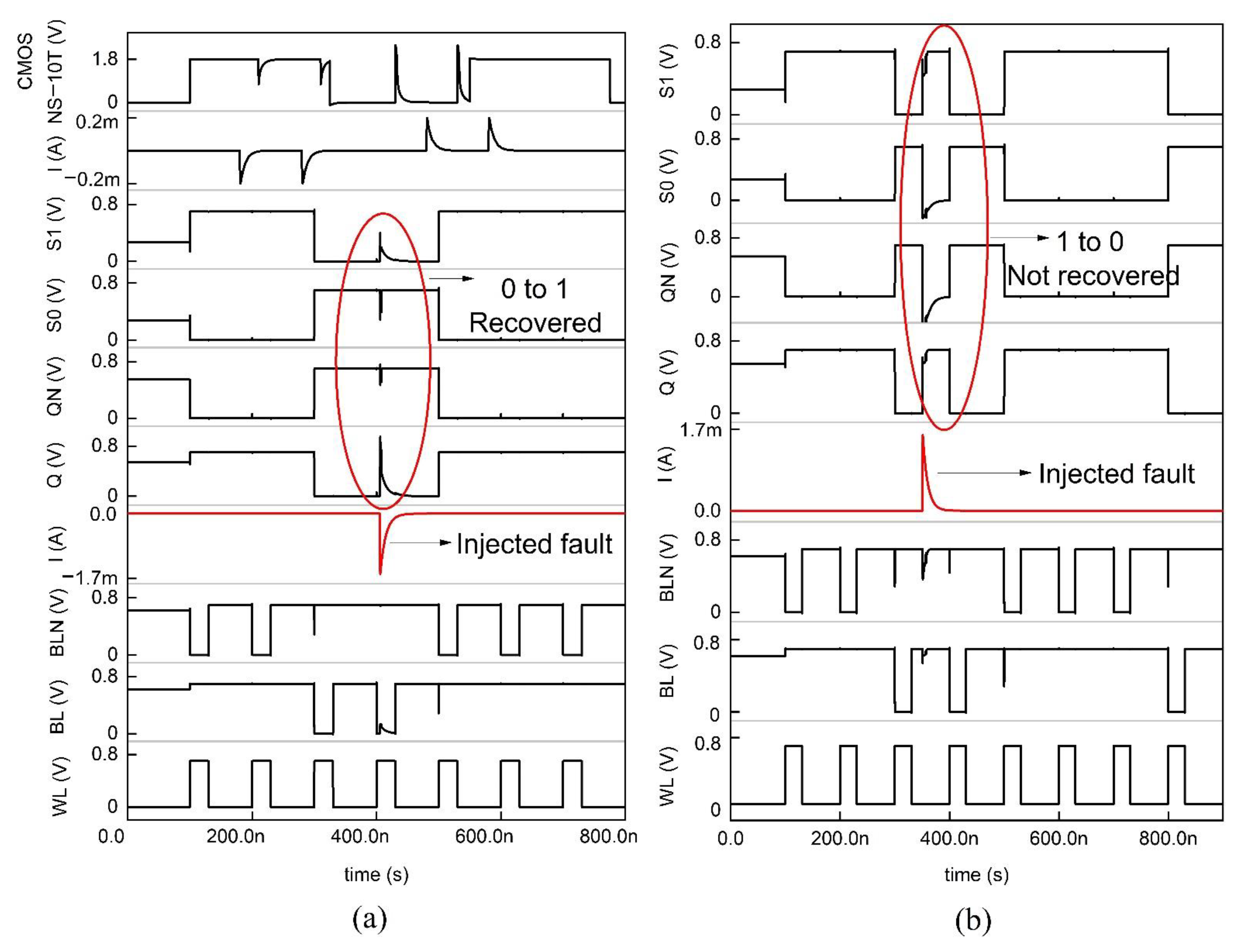

4.3. NS-10T Memory Cell

4.4. 10T Memory Cell

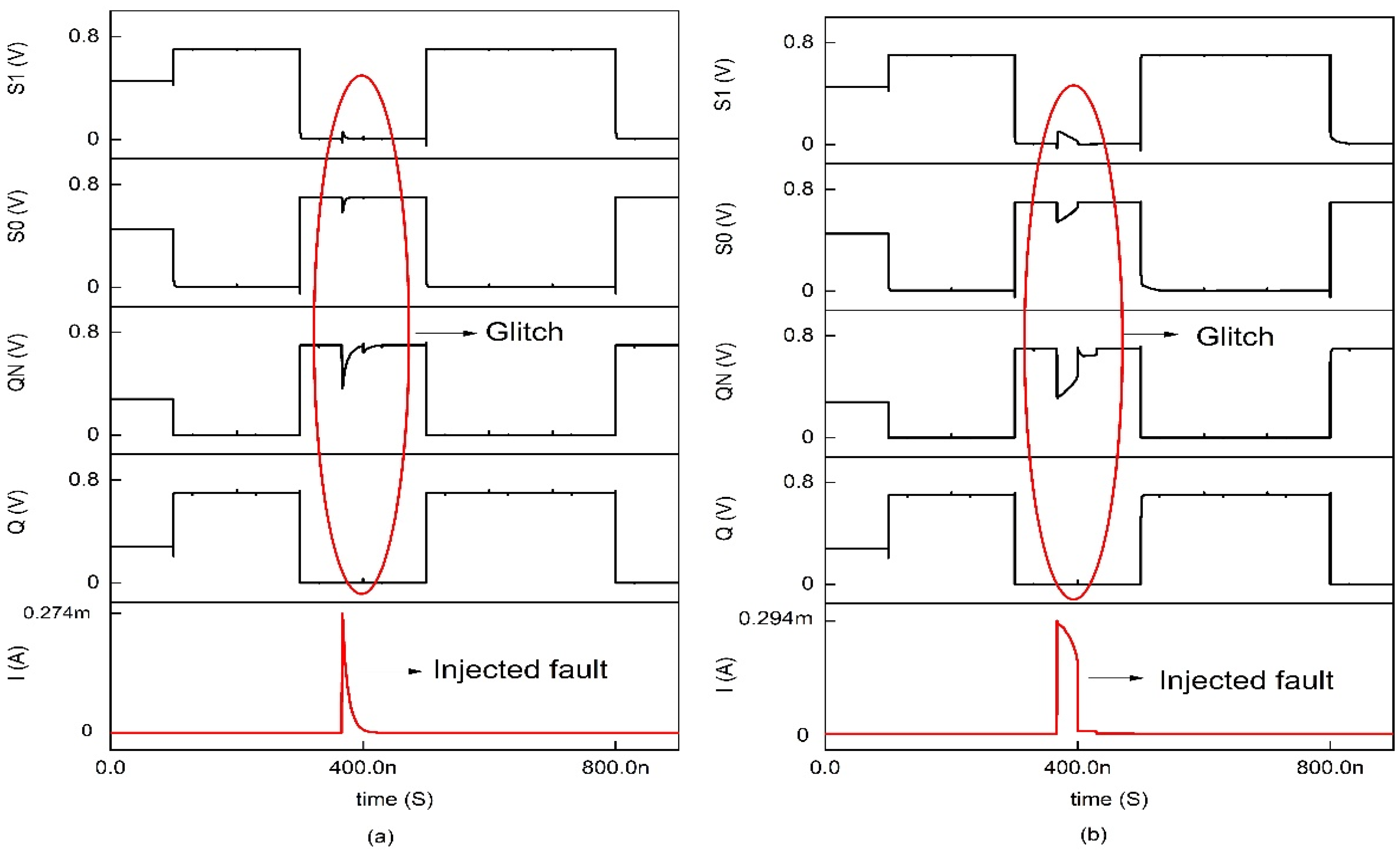

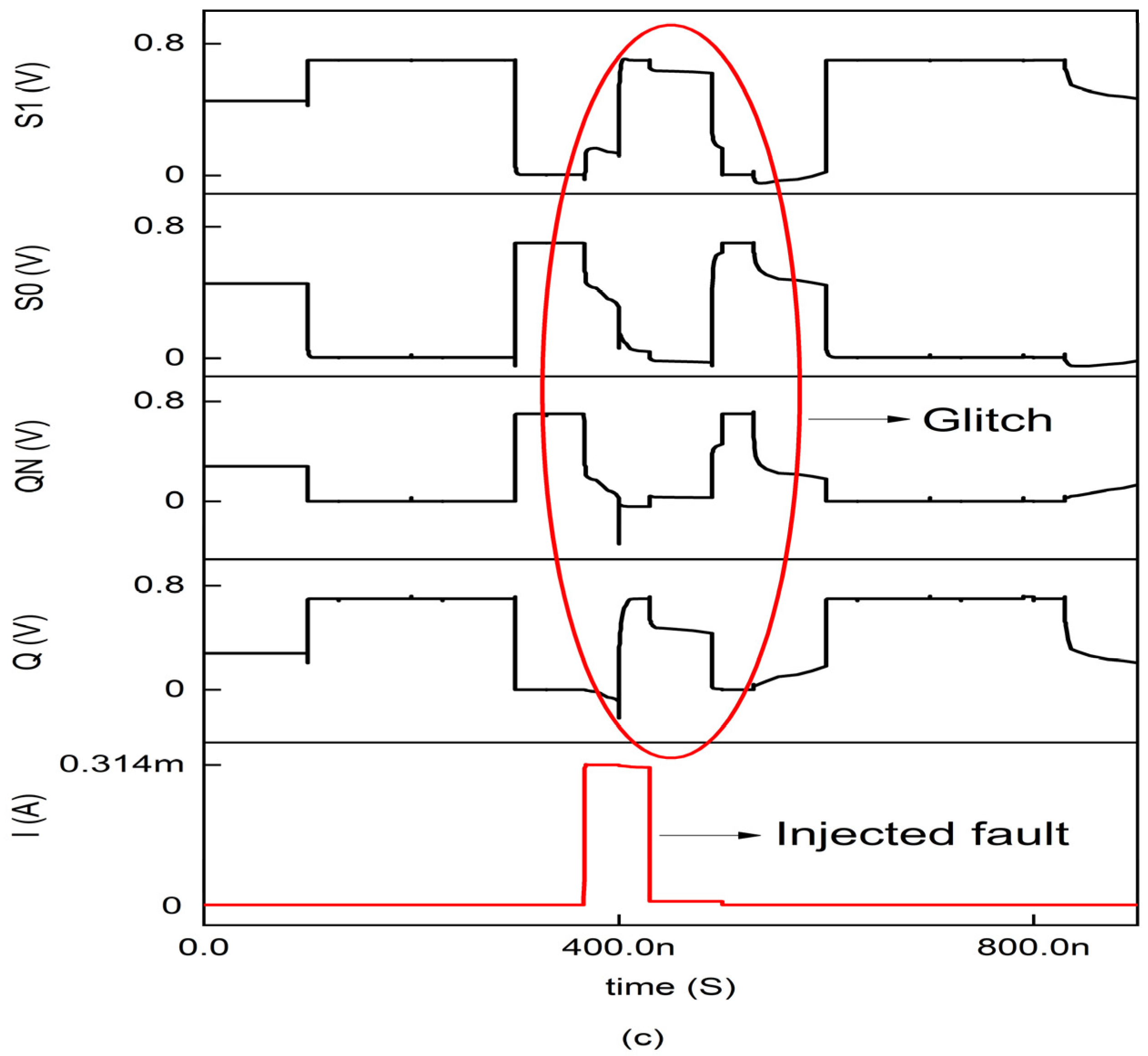

5. Results and Discussion

5.1. Static Noise Margin (SNM)

5.2. Read and Write Access Time

5.3. Power Consumption

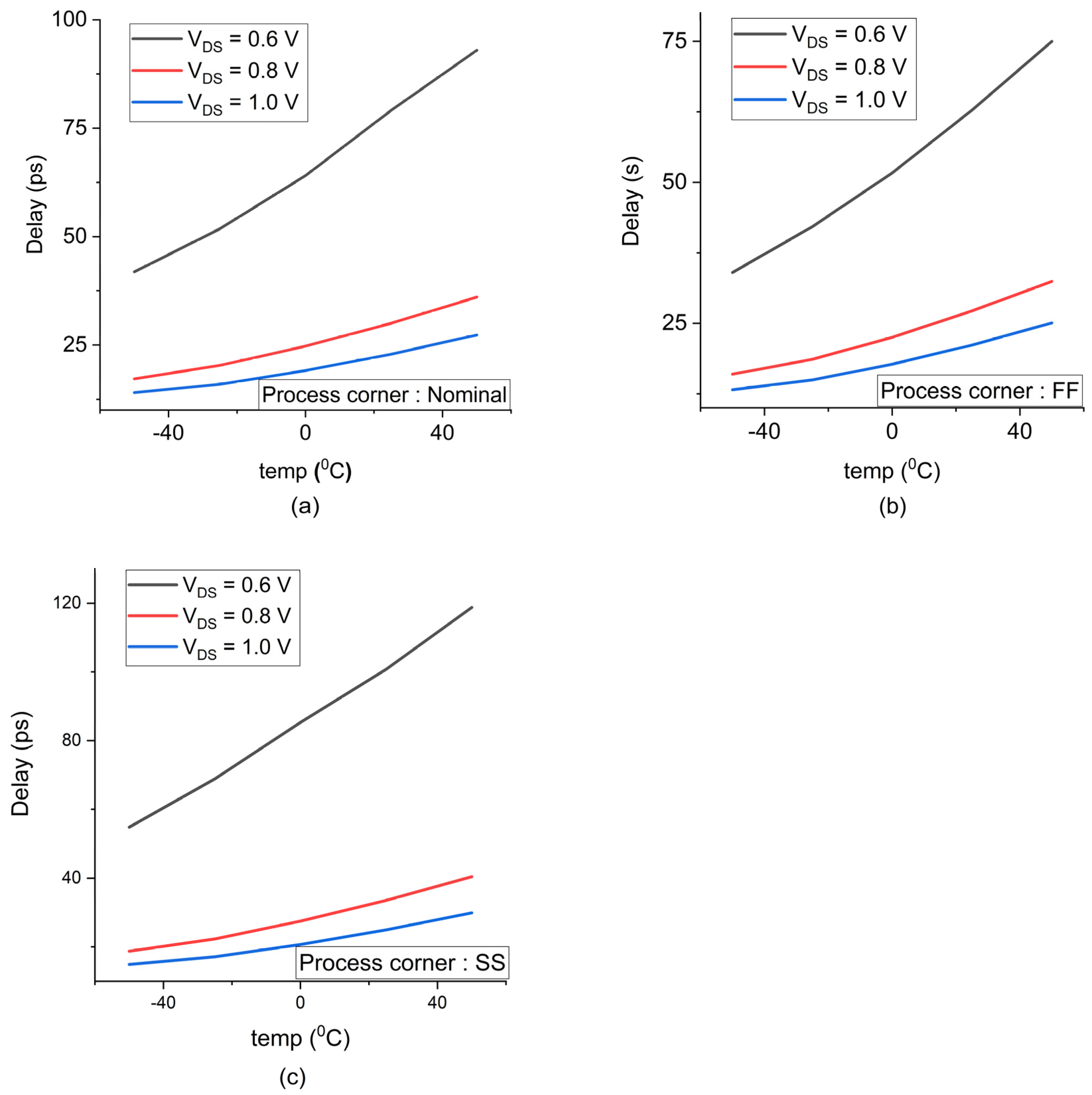

5.4. Impact of Process, Supply Voltage and Temperature in Memories

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Ferain, I.; Colinge, C.A.; Colinge, J.-P. Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 2011, 479, 310–316. [Google Scholar] [CrossRef] [PubMed]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Normand, E. Single-event effects in avionics. IEEE Trans. Nucl. Sci. 1996, 43, 461–474. [Google Scholar] [CrossRef]

- Jahinuzzaman, S.M.; Rennie, D.J.; Sachdev, M. A Soft Error Tolerant 10T SRAM Bit-Cell with Differential Read Capability. IEEE Trans. Nucl. Sci. 2009, 56, 3768–3773. [Google Scholar] [CrossRef]

- Seifert, N.; Gill, B.; Jahinuzzaman, S.; Basile, J.; Ambrose, V.; Shi, Q.; Allmon, R.; Bramnik, A. Soft Error Susceptibilities of 22 nm Tri-Gate Devices. IEEE Trans. Nucl. Sci. 2012, 59, 2666–2673. [Google Scholar] [CrossRef]

- Detcheverry, C.; Dachs, C.; Lorfevre, E.; Sudre, C.; Bruguier, G.; Palau, J.; Gasiot, J.; Ecoffet, R. SEU critical charge and sensitive area in a submicron CMOS technology. IEEE Trans. Nucl. Sci. 1997, 44, 2266–2273. [Google Scholar] [CrossRef]

- Asli, R.N.; Taghipour, S. Reliable and high performance asymmetric FinFET SRAM cell using back-gate control. Microelectron. Reliab. 2020, 104, 113545. [Google Scholar] [CrossRef]

- Tamersit, K. Sub-10 nm junctionless carbon nanotube field-effect transistors with improved performance. AEU-Int. J. Electron. Commun. 2020, 124, 153354. [Google Scholar] [CrossRef]

- Peng, L.-M.; Zhang, Z.; Qiu, C. Carbon nanotube digital electronics. Nat. Electron. 2019, 2, 499–505. [Google Scholar] [CrossRef]

- Qi, C.; Xiao, L.; Wang, T.; Li, J.; Li, L. A Highly Reliable Memory Cell Design Combined with Layout-Level Approach to Tolerant Single-Event Upsets. IEEE Trans. Device Mater. Reliab. 2016, 16, 388–395. [Google Scholar] [CrossRef]

- Ramamurthy, C.; Chellappa, S.; Vashishtha, V.; Gogulamudi, A.; Clark, L.T. High Performance Low Power Pulse-Clocked TMR Circuits for Soft-Error Hardness. IEEE Trans. Nucl. Sci. 2015, 62, 3040–3048. [Google Scholar] [CrossRef]

- Guo, J.; Xiao, L.; Mao, Z.; Zhao, Q.; Guo, J.; Xiao, L.; Mao, Z.; Zhao, Q. Enhanced Memory Reliability Against Multiple Cell Upsets Using Decimal Matrix Code. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2013, 22, 127–135. [Google Scholar] [CrossRef]

- Guo, J.; Zhu, L.; Sun, Y.; Cao, H.; Huang, H.; Wang, T.; Qi, C.; Zhang, R.; Cao, X.; Xiao, L.; et al. Design of Area-Efficient and Highly Reliable RHBD 10T Memory Cell for Aerospace Applications. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2018, 26, 991–994. [Google Scholar] [CrossRef]

- Guo, J.; Zhu, L.; Liu, W.; Huang, H.; Liu, S.; Wang, T.; Xiao, L.; Mao, Z. Novel Radiation-Hardened-by-Design (RHBD) 12T Memory Cell for Aerospace Applications in Nanoscale CMOS Technology. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2017, 25, 1593–1600. [Google Scholar] [CrossRef]

- Jung, I.-S.; Kim, Y.-B.; Lombardi, F. A novel sort error hardened 10T SRAM cells for low voltage operation. In Proceedings of the 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, USA, 5–8 August 2012; IEEE: Piscataway, NJ, USA, 2012. [Google Scholar] [CrossRef]

- Vinodhkumar, N.; Bhuvaneshwari, Y.; Nagarajan, K.; Srinivasan, R. Heavy-ion irradiation study in SOI-based and bulk-based junctionless FinFETs using 3D-TCAD simulation. Microelectron. Reliab. 2015, 55, 2647–2653. [Google Scholar] [CrossRef]

- Nilamani, S.; Chitra, P.; Ramakrishnan, V.N. Topological variation on sub-20 nm double-gate inversion and Junction-less-FinFET based 6T-SRAM circuits and its SEU radiation performance. Microelectron. Reliab. 2018, 82, 11–19. [Google Scholar] [CrossRef]

- Zhang, R.; Liu, Z.; Yang, K.; Liu, T.; Cai, W.; Milor, L. Impact of front-end wearout mechanisms on FinFET SRAM soft error rate. Microelectron. Reliab. 2019, 100–101, 113487. [Google Scholar] [CrossRef]

- de Aguiar, Y.Q.; Artola, L.; Hubert, G.; Meinhardt, C.; Kastensmidt, F.L.; Reis, R.A. Evaluation of radiation-induced soft error in majority voters designed in 7 nm FinFET technology. Microelectron. Reliab. 2017, 76, 660–664. [Google Scholar] [CrossRef] [Green Version]

- Vashishtha, V.; Clark, L.T. Comparing bulk-Si FinFET and gate-all-around FETs for the 5 nm technology node. Microelectron. J. 2021, 107, 104942. [Google Scholar] [CrossRef]

- Singh, A.; Khosla, M.; Raj, B. Design and analysis of electrostatic doped Schottky barrier CNTFET based low power SRAM. AEU-Int. J. Electron. Commun. 2017, 80, 67–72. [Google Scholar] [CrossRef]

- Jooq, M.K.Q.; Mir, A.; Mirzakuchaki, S.; Farmani, A. A robust and energy-efficient near-threshold SRAM cell utilizing ballistic carbon nanotube wrap-gate transistors. AEU-Int. J. Electron. Commun. 2019, 110, 152874. [Google Scholar] [CrossRef]

- Kanhaiya, P.S.; Lau, C.; Hills, G.; Bishop, M.D.; Shulaker, M.M. Carbon Nanotube-Based CMOS SRAM: 1 kbit 6T SRAM Arrays and 10T SRAM Cells. IEEE Trans. Electron. Devices 2019, 66, 5375–5380. [Google Scholar] [CrossRef]

- Lee, C.-S.; Pop, E.; Franklin, A.D.; Haensch, W.; Wong, H.-S.P. A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime—Part I: Intrinsic elements. IEEE Trans. Electron Devices 2015, 62, 3061–3069. [Google Scholar] [CrossRef] [Green Version]

- Sinha, S.; Yeric, G.; Chandra, V.; Cline, B.; Cao, Y. Exploring sub-20nm FinFET design with predictive technology models. In Proceedings of the DAC Design Automation Conference, San Francisco, CA, USA, 3–7 June 2012; IEEE: Piscataway, NJ, USA, 2012. [Google Scholar]

- Clark, L.T.; Vashishtha, V.; Shifren, L.; Gujja, A.; Sinha, S.; Cline, B.; Ramamurthy, C.; Yeric, G. ASAP7: A 7-nm finFET predictive process design kit. Microelectron. J. 2016, 53, 105–115. [Google Scholar] [CrossRef]

- Franklin, A.D.; Luisier, M.; Han, S.-J.; Tulevski, G.; Breslin, C.M.; Gignac, L.; Lundstrom, M.S.; Haensch, W. Sub-10 nm Carbon Nanotube Transistor. Nano Lett. 2012, 12, 758–762. [Google Scholar] [CrossRef] [PubMed]

- Kumar, G.S.; Singh, A.; Raj, B. Design and analysis of a gate-all-around CNTFET-based SRAM cell. J. Comput. Electron. 2018, 17, 138–145. [Google Scholar] [CrossRef]

- Jiang, J.; Xu, Y.; Zhu, W.; Xiao, J.; Zou, S. Quadruple Cross-Coupled Latch-Based 10T and 12T SRAM Bit-Cell Designs for Highly Reliable Terrestrial Applications. IEEE Trans. Circuits Syst. I: Regul. Pap. 2018, 66, 967–977. [Google Scholar] [CrossRef]

- Sinha, A.; Anand, N.; Islam, A.; Sinha, A. Design metrics improvement of 10TSRAM cell using CNFET. In Proceedings of the 2014 International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCICCT), Kanyakumari, India, 10–11 July 2014; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar] [CrossRef]

- Sun, L.; Mathew, J.; Shafik, R.A.; Pradhan, D.K.; Li, Z. A low power and robust carbon nanotube 6T SRAM design with metallic tolerance. In Proceedings of the 2014 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 24–28 March 2014; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar] [CrossRef]

| Conventional MOSFET | GPDK 90 nm | GPDK 45 nm |

|---|---|---|

| Length | 100 nm | 45 nm |

| Total width | 120 nm | 120 nm |

| Finger Width | 120 nm | 120 nm |

| Fingers | 1 | 1 |

| Source/Drain metal width | 120 nm | 60 nm |

| CNTFET | Scale (nm) | FinFET | (Scale) nm |

|---|---|---|---|

| Gate length (Lg) | 18 | Fin height (HFIN) | 30 |

| Contact length (Lc) | 18 | Gate length (LG) | 16 |

| Source/Drain extension length (Lext) | 3 | Fin thickness (TSI) | 10 |

| Device width (W) | 120 | oxide thickness (TOX) | 0.9 |

| Gate height | 20 | Front/Backgate spacer thickness LSPF, LSPB | 8 |

| Gate oxide thickness (tox) | 0.9 | underlap near souce/drain LUN | 6 |

| Carbon nanotube diameter (d) | 1.2 | Fin pitch FP | 40 |

| Carbon nanotube spacing (s) | 10 |

| Transistor Model | ION (µA) | IOFF (A) | SS (mv/dec) | DIBL (mv/v) | rON kΩ) | Power (µW) |

|---|---|---|---|---|---|---|

| GPDK 45 nm | 87.09 | 47.33p | 87.09 | 60.38 | 12.92 | 77.34 |

| GPDK 90 nm | 108.69 | 46.70n | 107.34 | 134.6 | 11.04 | 130.43 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Muthu, B.R.; Pushpa, E.P.; Dhandapani, V.; Jayaraman, K.; Vasanthakumar, H.; Oh, W.-C.; Sagadevan, S. Design and Analysis of Soft Error Rate in FET/CNTFET Based Radiation Hardened SRAM Cell. Sensors 2022, 22, 33. https://doi.org/10.3390/s22010033

Muthu BR, Pushpa EP, Dhandapani V, Jayaraman K, Vasanthakumar H, Oh W-C, Sagadevan S. Design and Analysis of Soft Error Rate in FET/CNTFET Based Radiation Hardened SRAM Cell. Sensors. 2022; 22(1):33. https://doi.org/10.3390/s22010033

Chicago/Turabian StyleMuthu, Bharathi Raj, Ewins Pon Pushpa, Vaithiyanathan Dhandapani, Kamala Jayaraman, Hemalatha Vasanthakumar, Won-Chun Oh, and Suresh Sagadevan. 2022. "Design and Analysis of Soft Error Rate in FET/CNTFET Based Radiation Hardened SRAM Cell" Sensors 22, no. 1: 33. https://doi.org/10.3390/s22010033

APA StyleMuthu, B. R., Pushpa, E. P., Dhandapani, V., Jayaraman, K., Vasanthakumar, H., Oh, W.-C., & Sagadevan, S. (2022). Design and Analysis of Soft Error Rate in FET/CNTFET Based Radiation Hardened SRAM Cell. Sensors, 22(1), 33. https://doi.org/10.3390/s22010033