Design and Analysis of a Reconfigurable Gilbert Mixer for Software-Defined Radios

Abstract

1. Introduction

2. Motivation

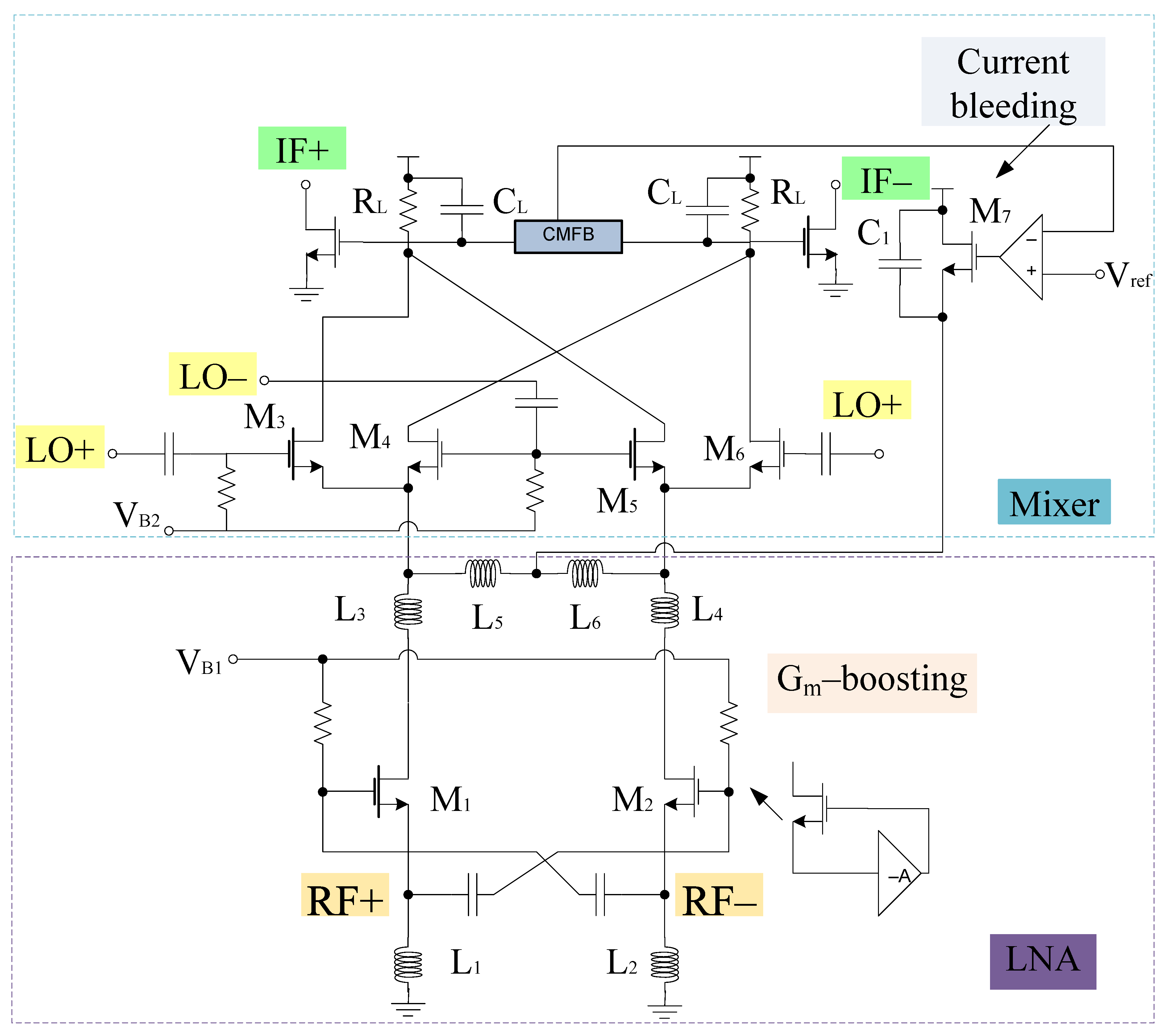

3. Proposed Mixer Topology

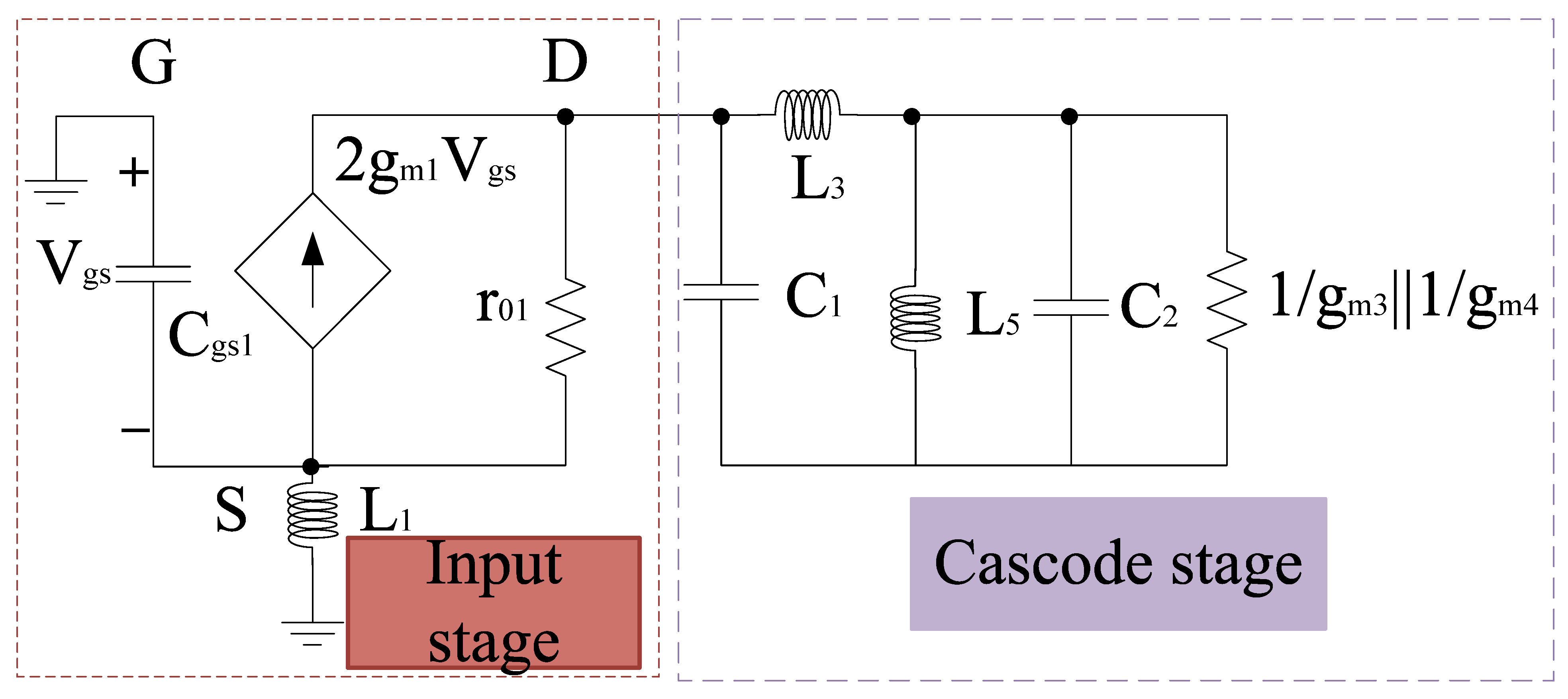

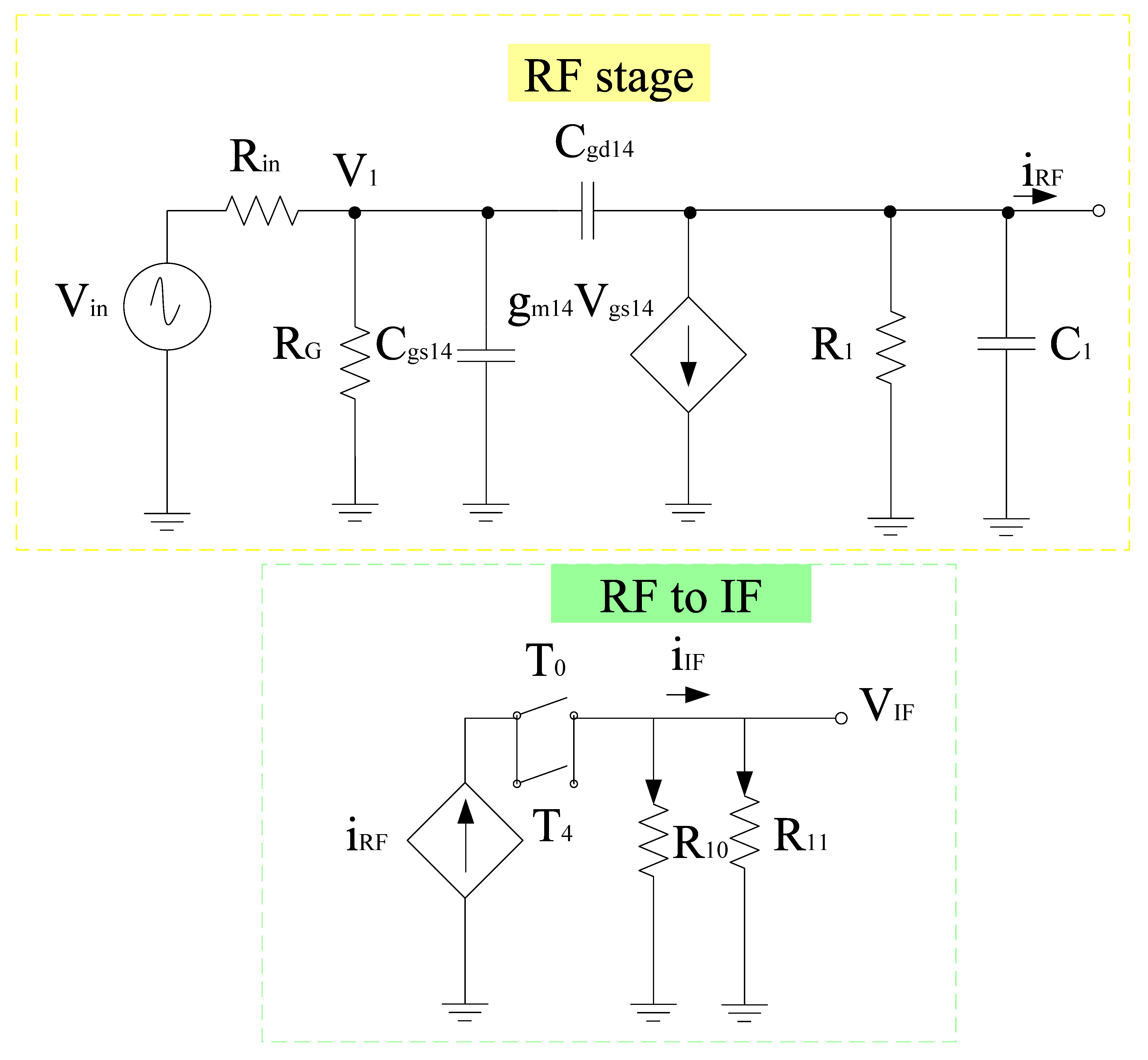

3.1. Tranconductance Stage

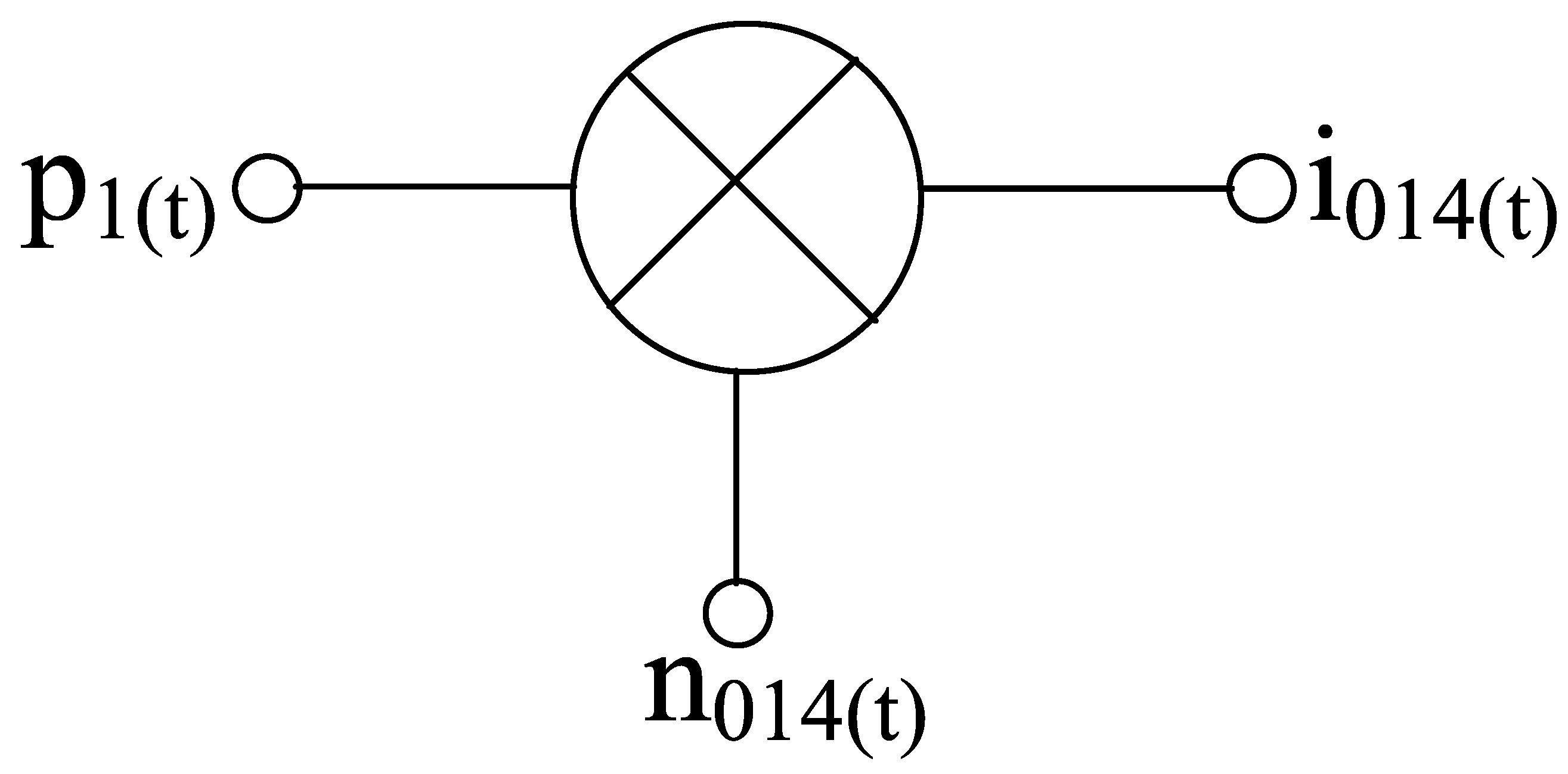

3.2. Core Stages

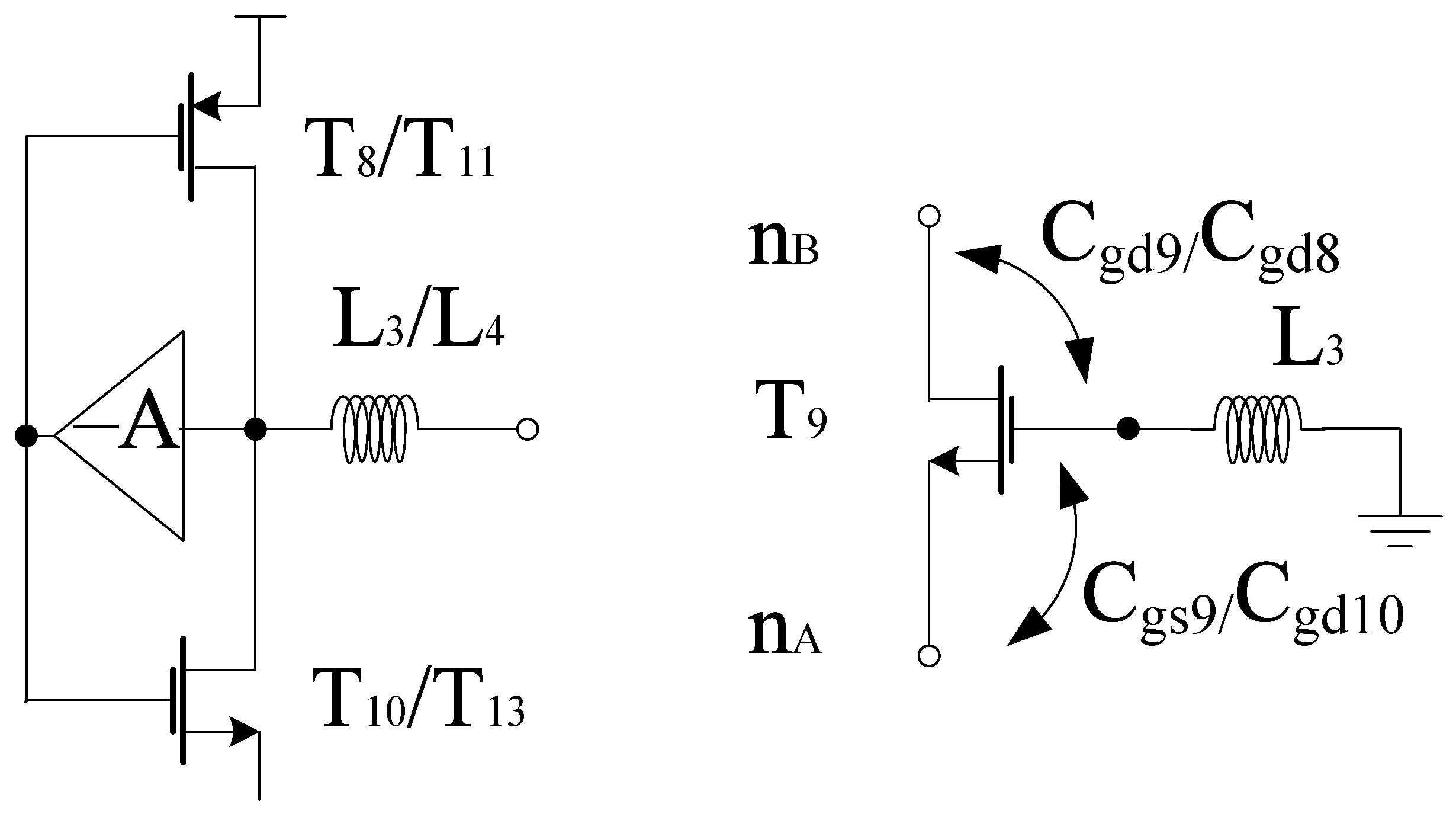

3.3. Gm-Boosting Section

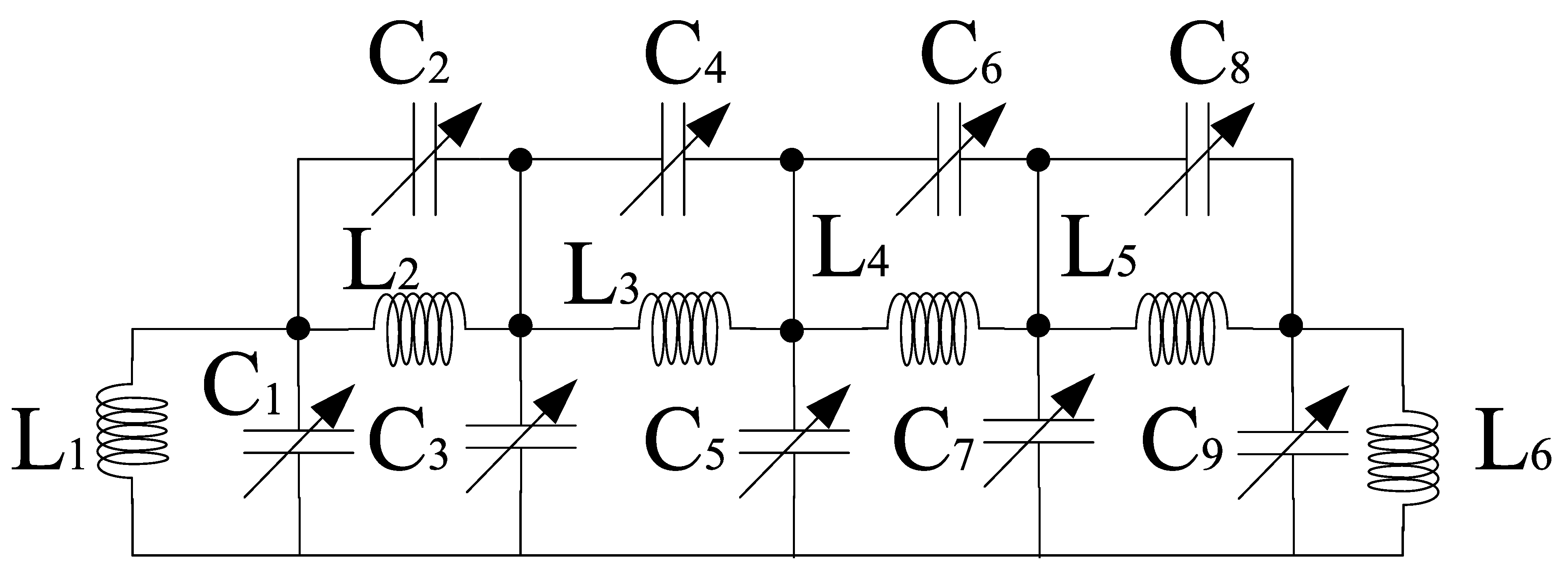

3.4. Filter Section

4. Mixer Design Analysis

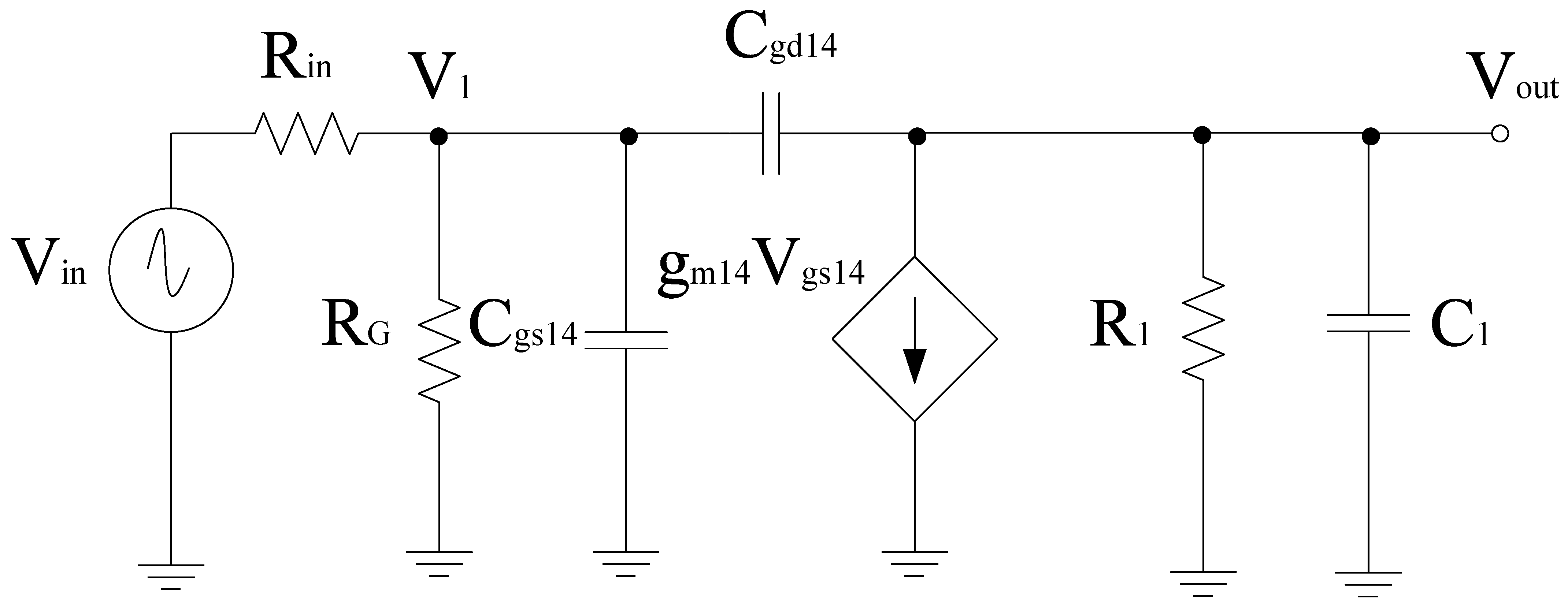

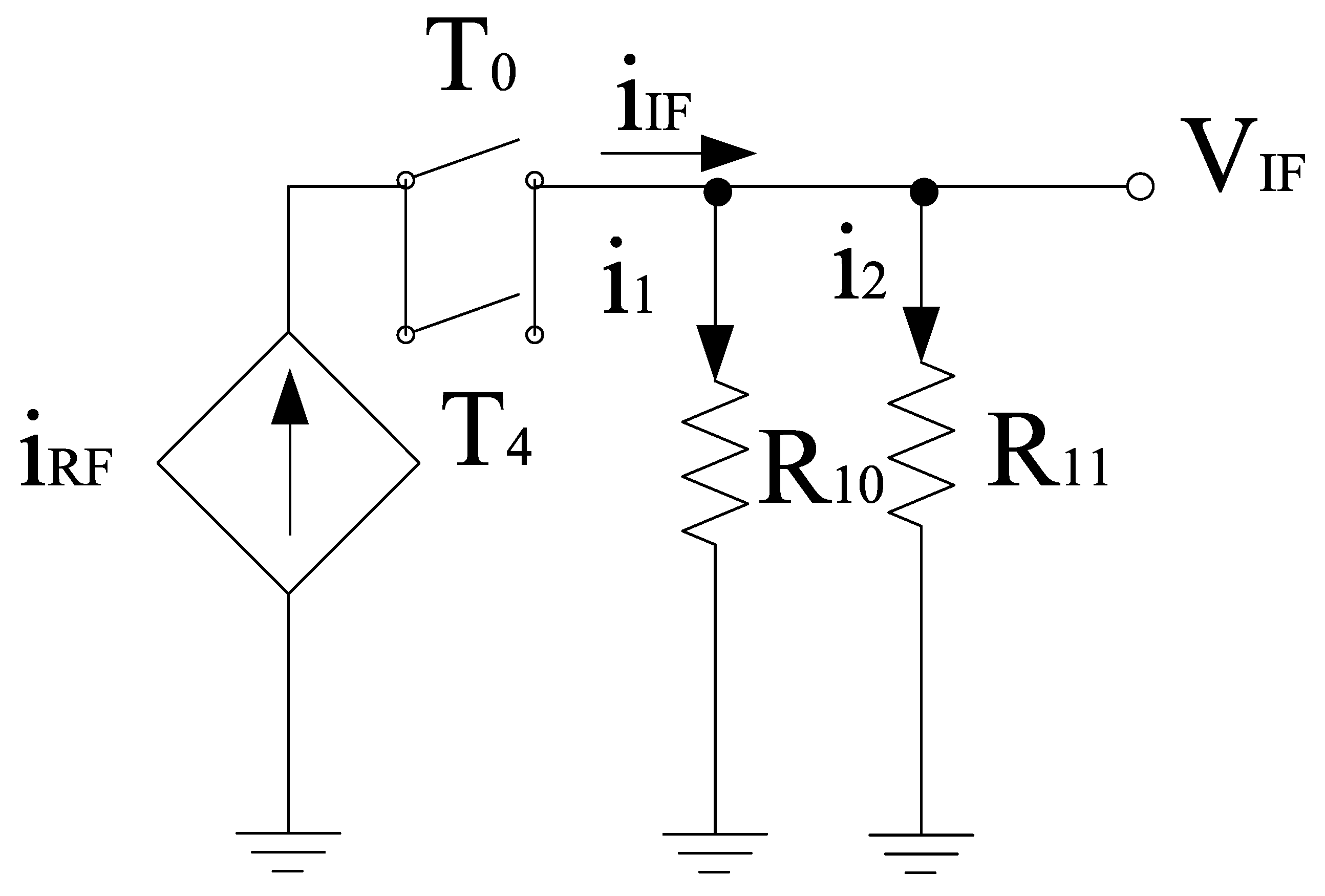

4.1. Conversion Gain

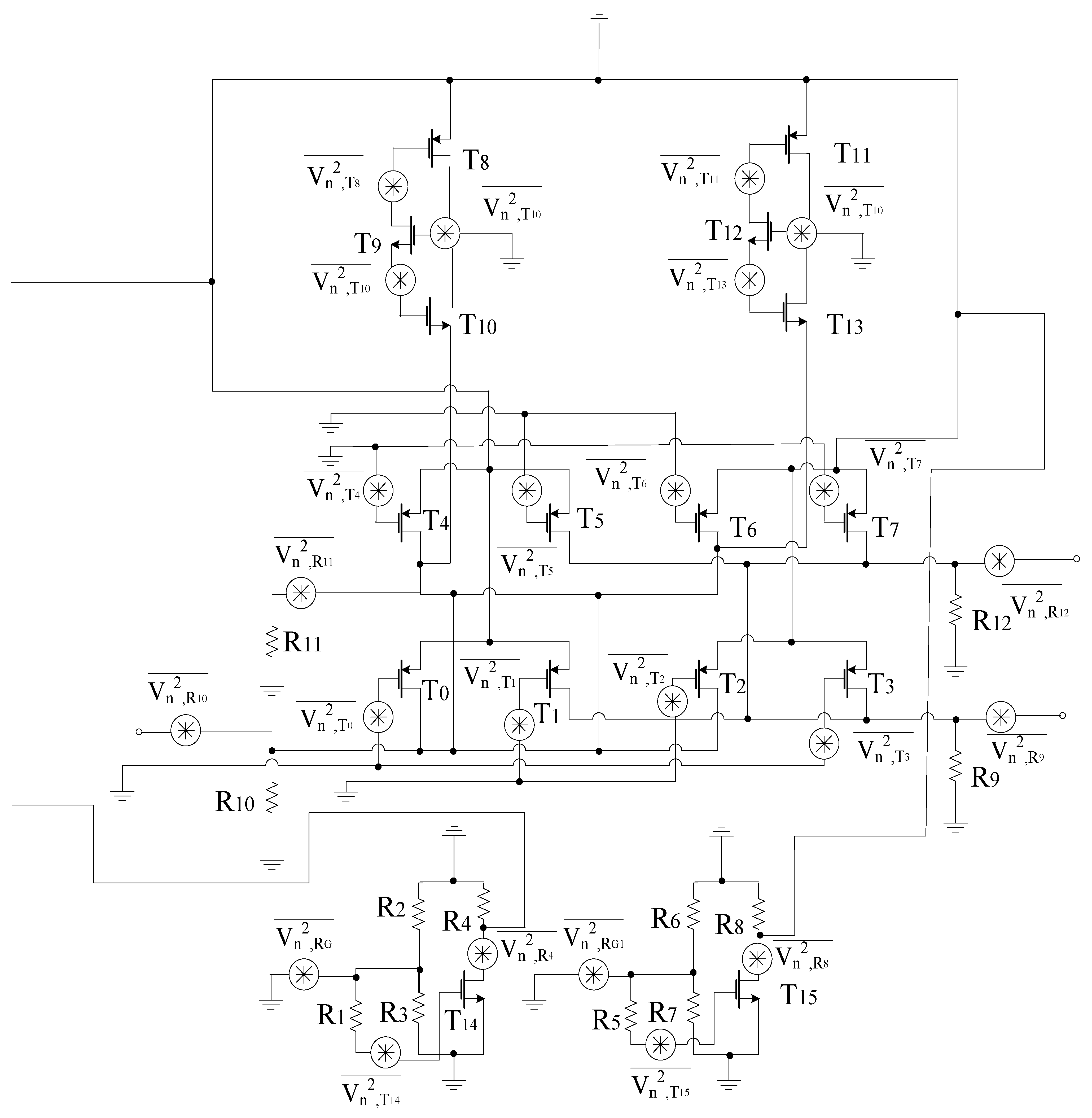

4.2. Noise Figure

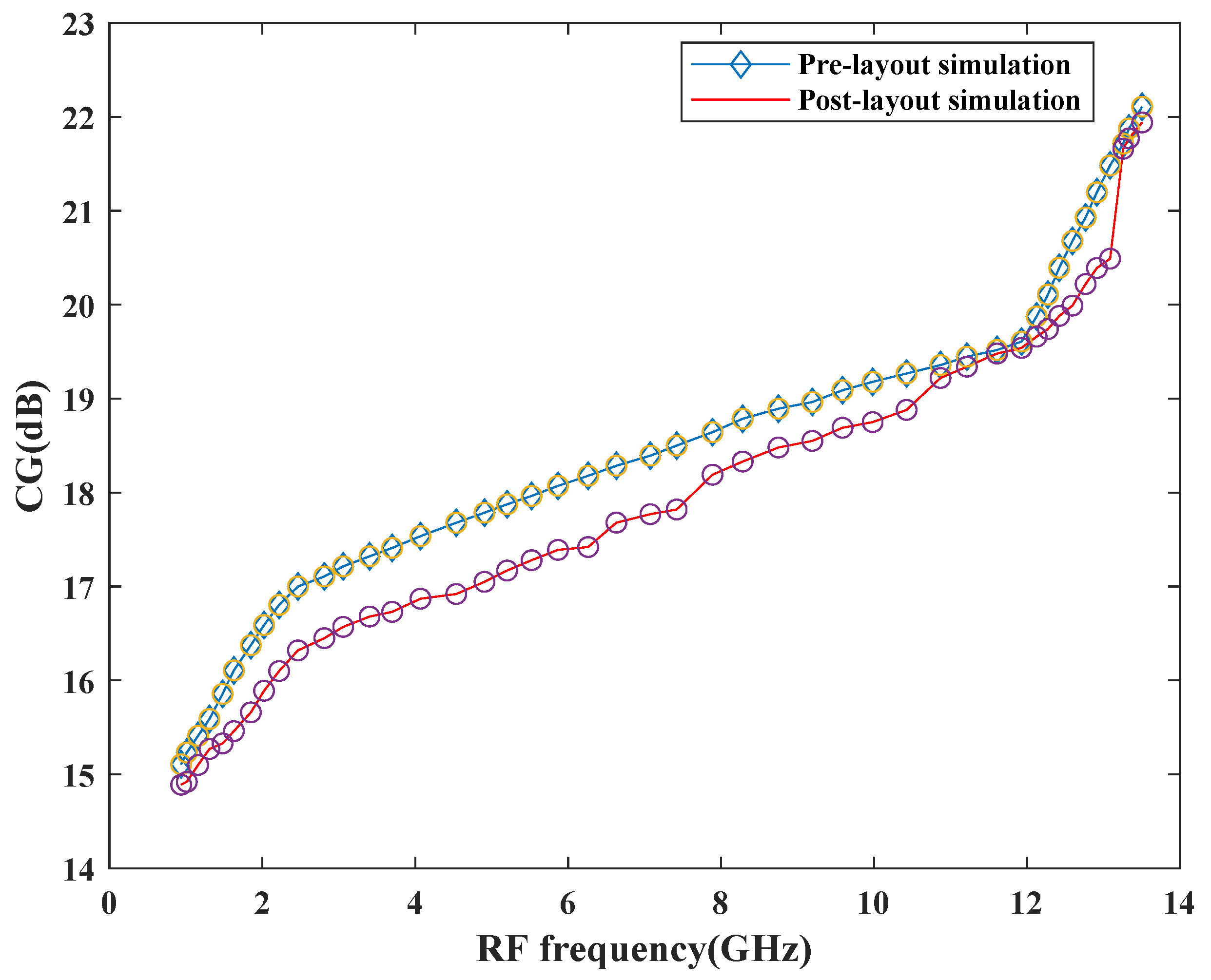

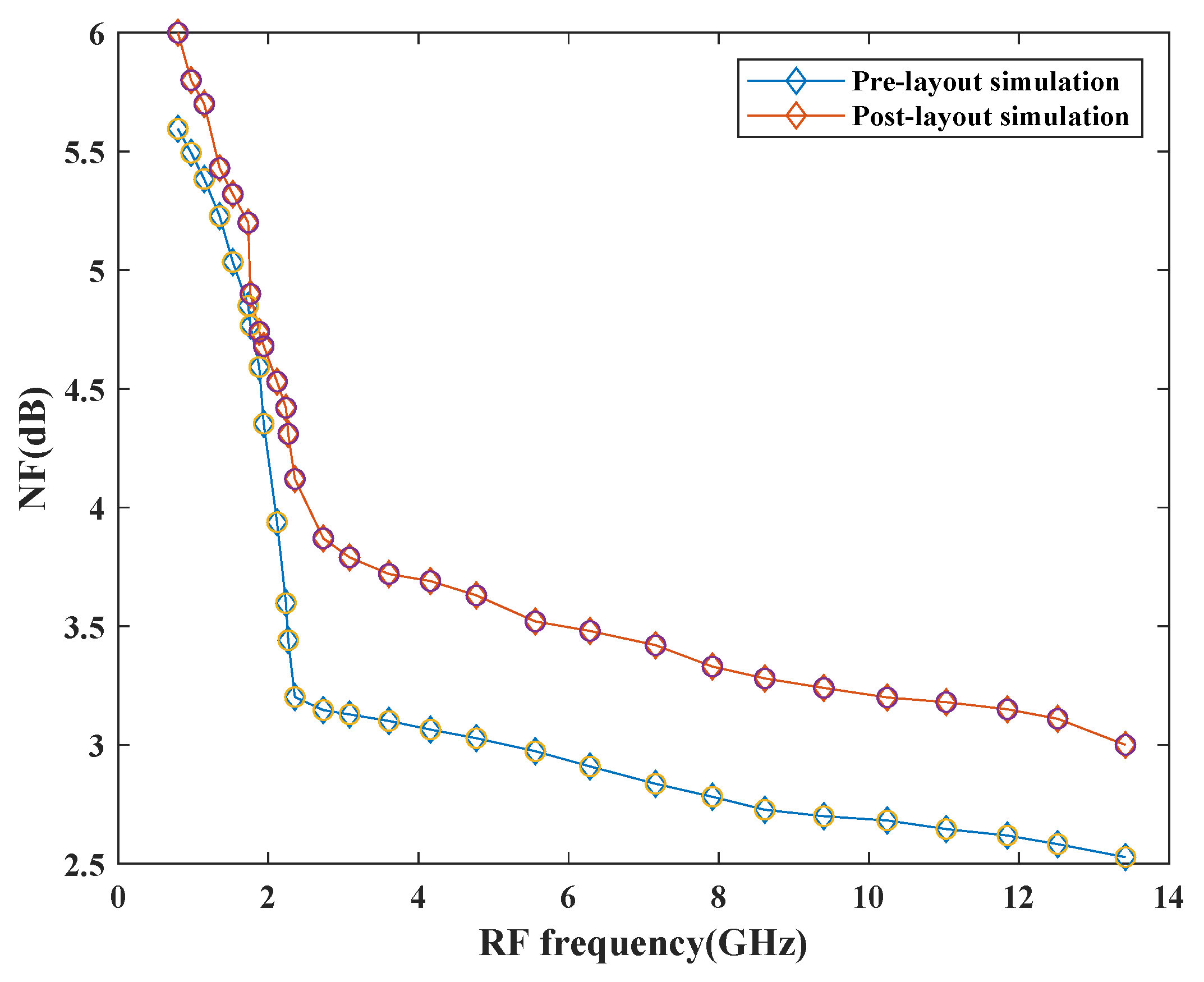

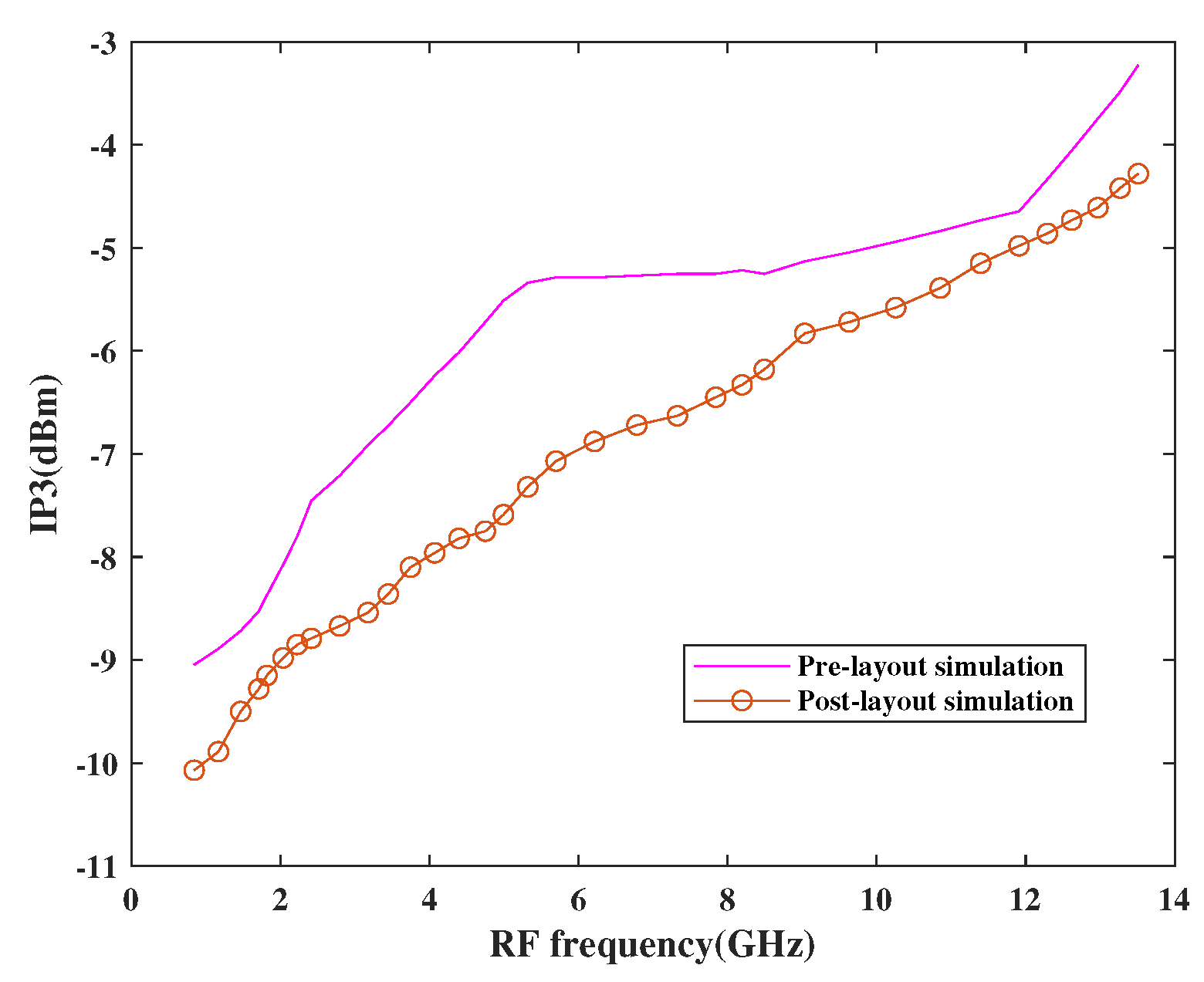

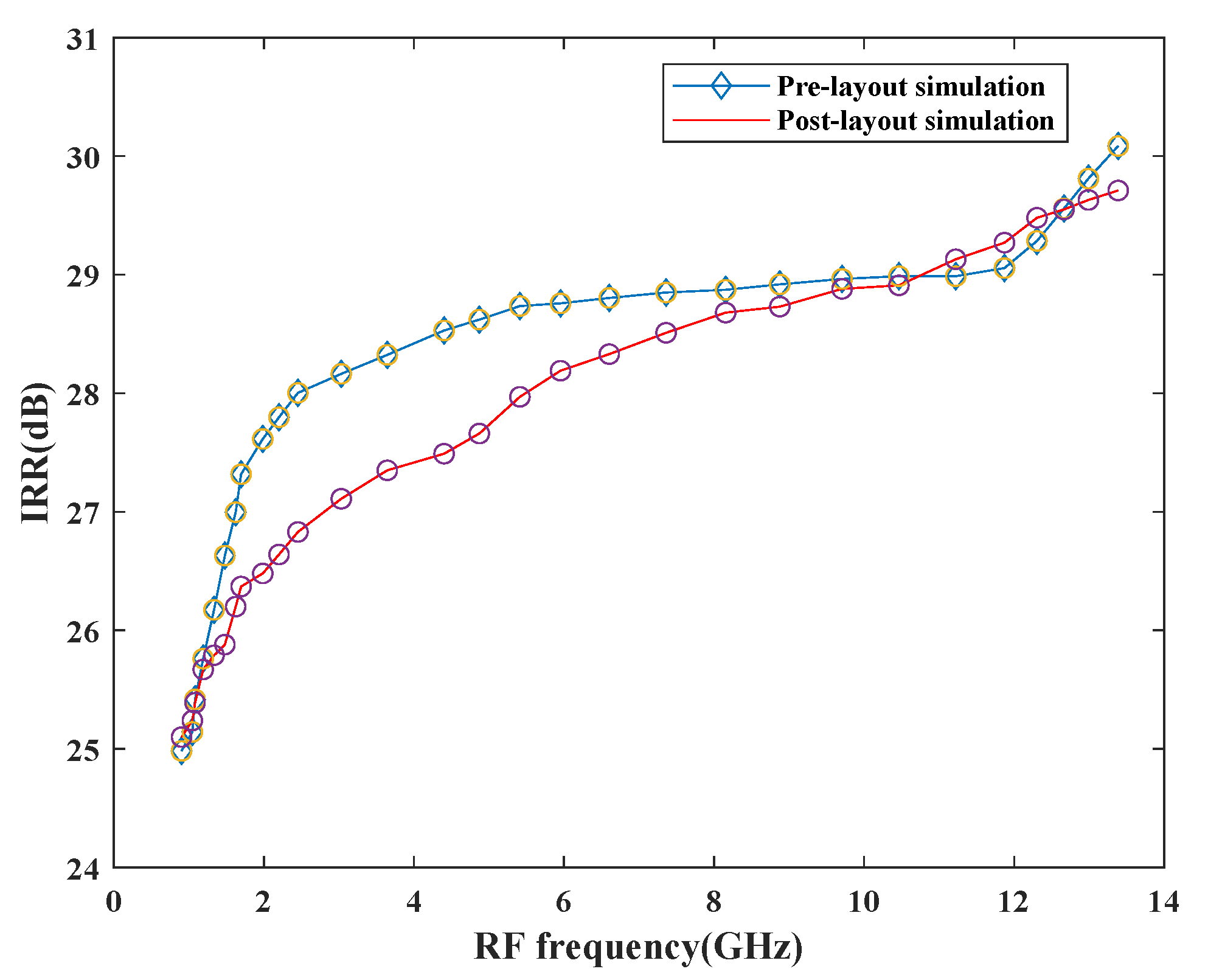

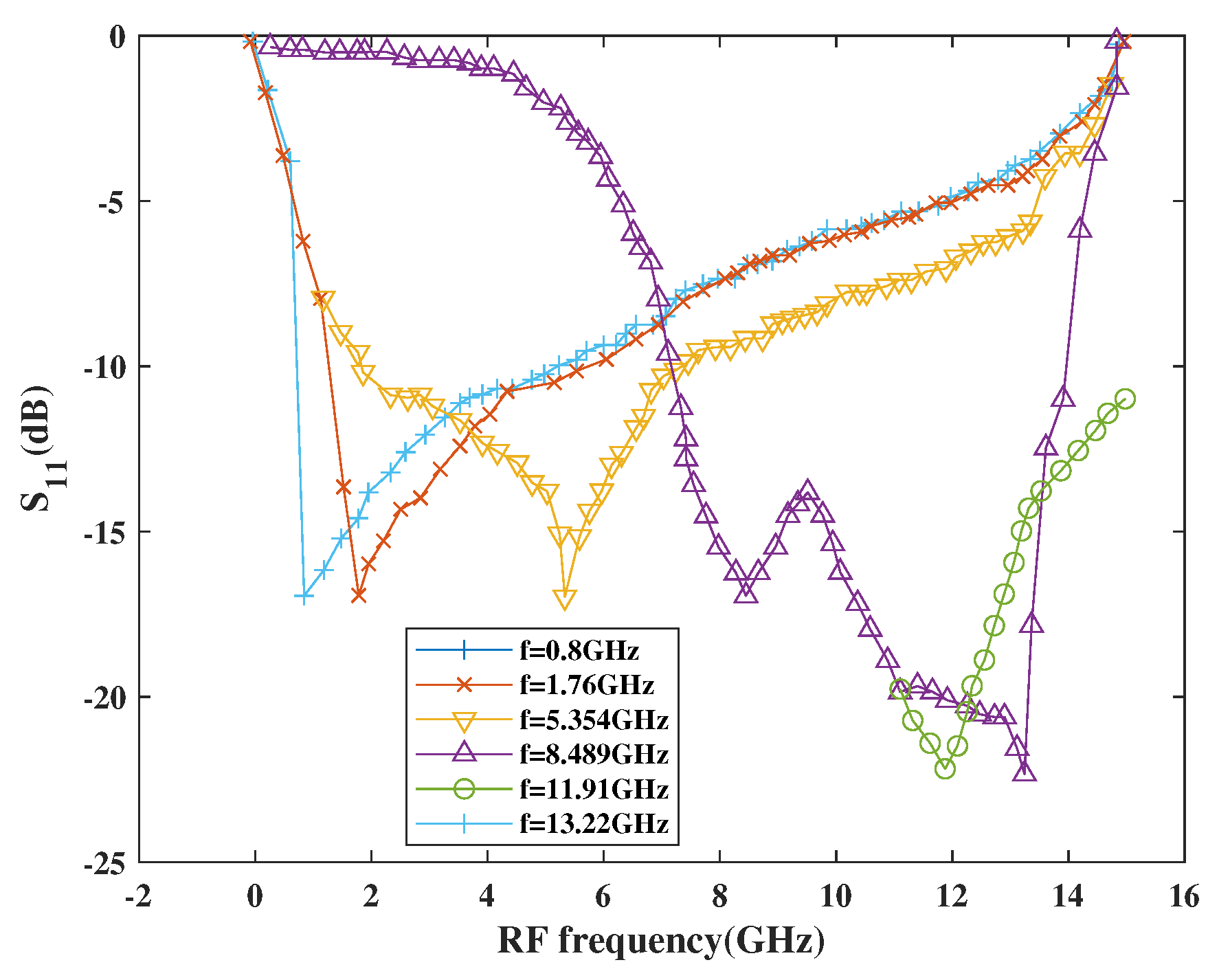

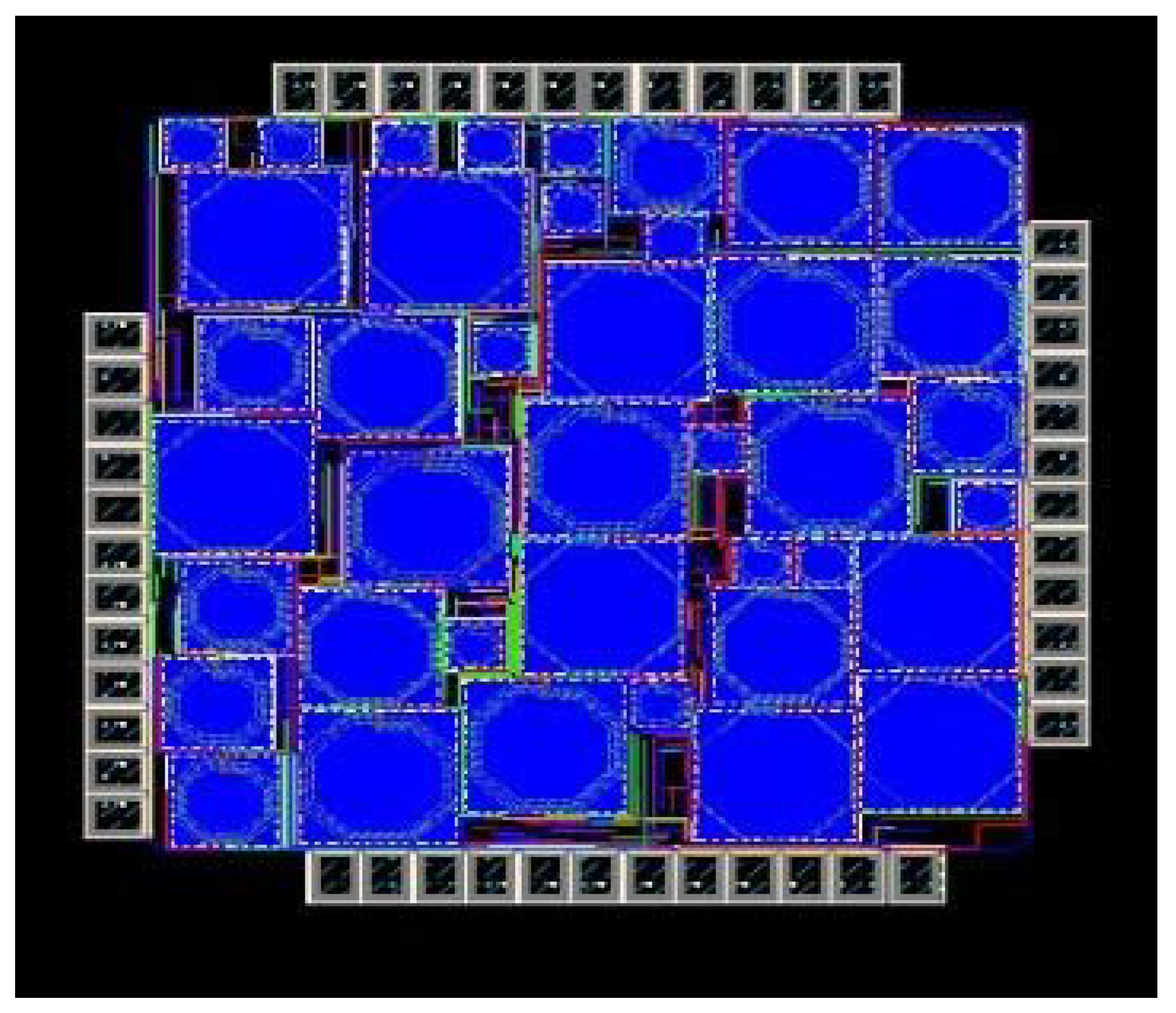

5. Results and Discussion

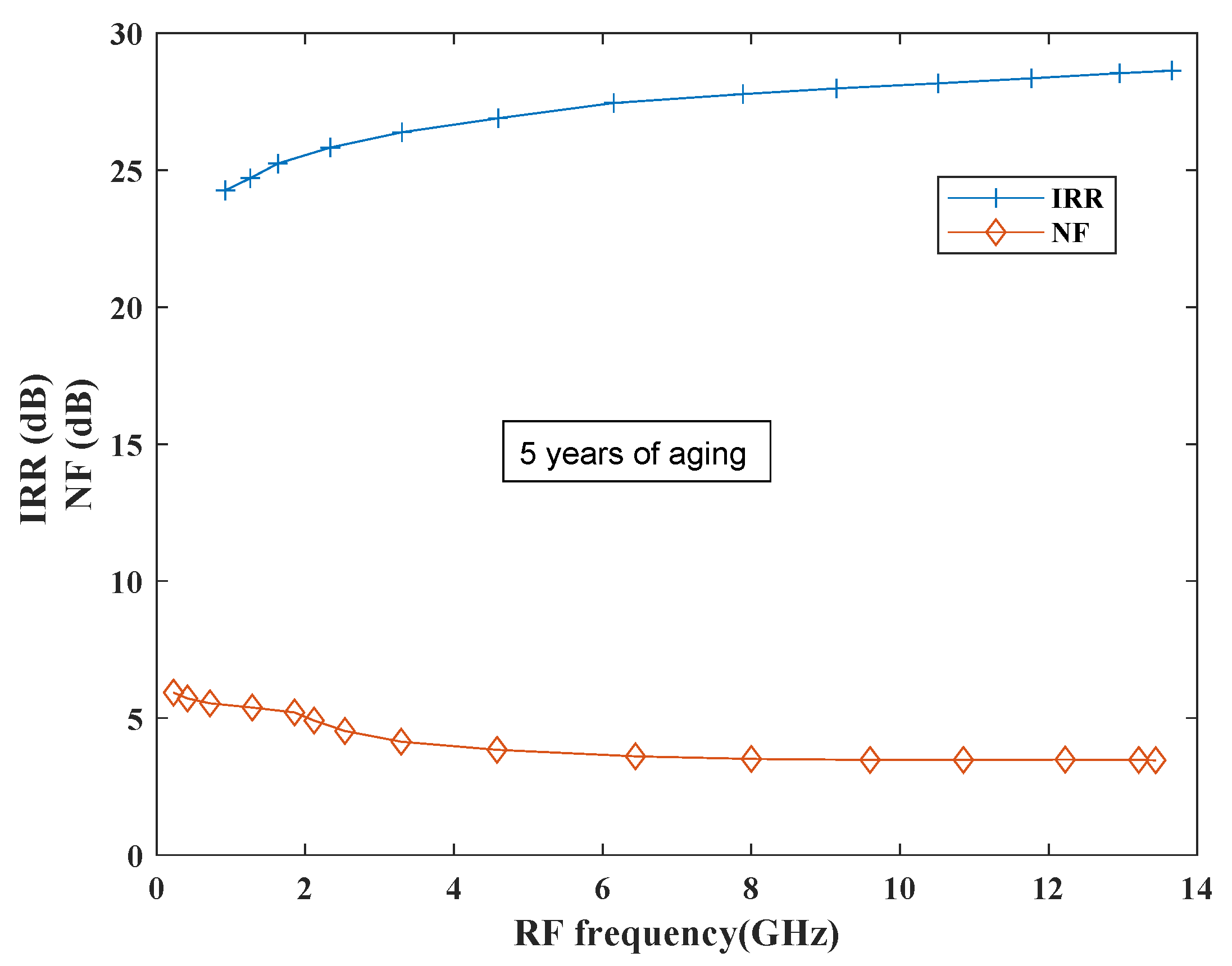

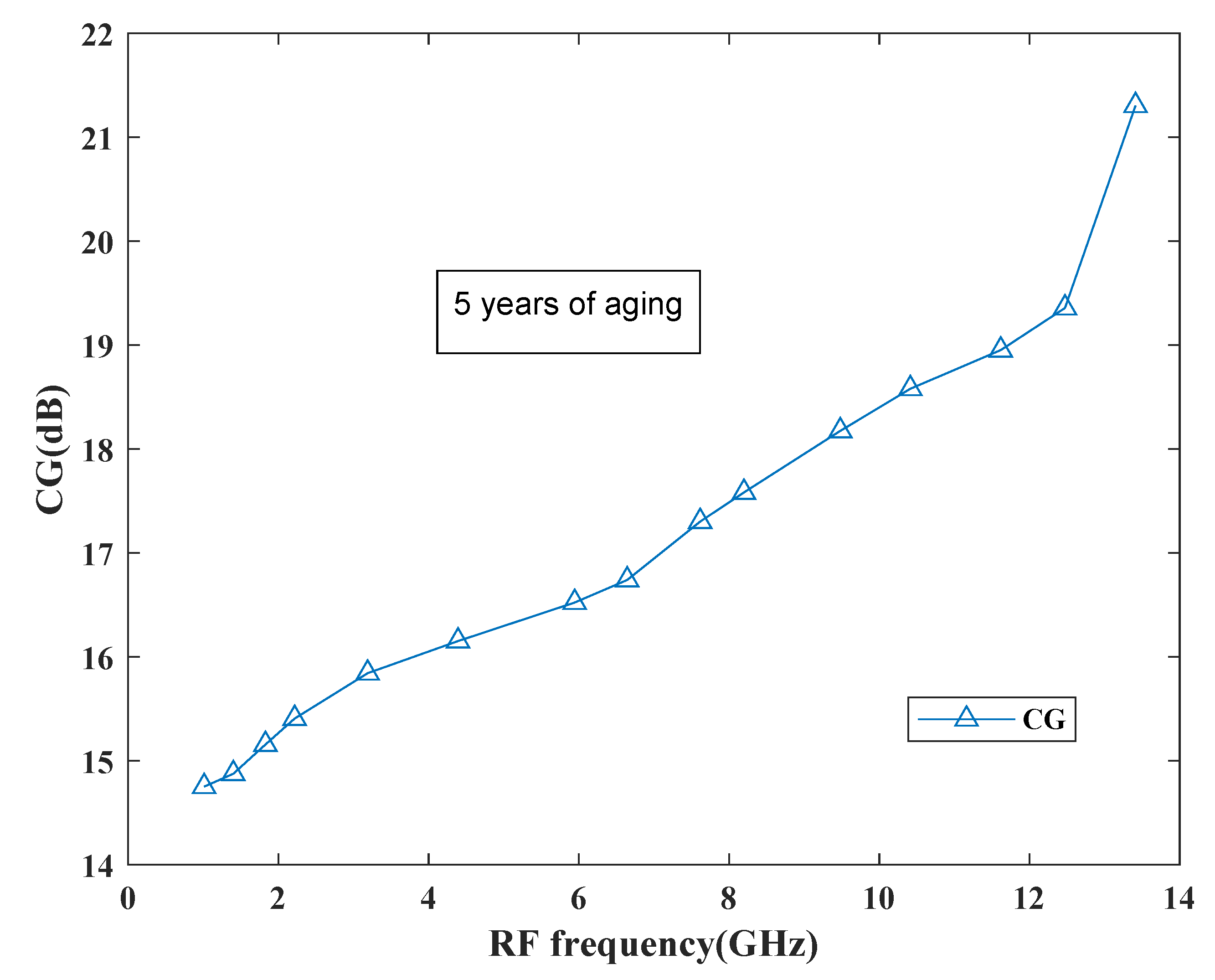

6. Design Reliability

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Brandolini, M.; Rossi, P.; Manstretta, D.; Svelto, F. Toward multistandard mobile terminals - fully integrated receivers requirements and architectures. IEEE Trans. Microw. Theory Tech. 2005, 53, 1026–1038. [Google Scholar] [CrossRef]

- Karanicolas, A.N. A 2.7 V 900 MHz CMOS LNA and mixer. In Proceedings of the 1996 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 1996; pp. 50–51. [Google Scholar]

- Vahidfar, M.B.; Shoaei, O.; Svelto, F. A high dynamic range multi-standard CMOS mixer for GSM, UMTS and IEEE802.11b-g-a applications. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 15–17 June 2008; pp. 193–196. [Google Scholar]

- Bao, K.; Fan, X.; Li, W.; Wang, Z. A wideband current-commutating passive mixer for multi-standard receivers in a 0.18 um CMOS. J. Semicond. 2013, 34, 1–3. [Google Scholar] [CrossRef]

- Wu, C.; Lin, Y. Design of down-conversion mixer with gm-boosted stage combining low phase noise oscillator. In Proceedings of the International Symposium on Signals, Systems and Electronics, Nanjing, China, 17–20 September 2010; Volume 2, pp. 1–4. [Google Scholar]

- Kim, C.; Jang, Y.K.; Yoo, H.J. System Level Design of Multi-standard Receiver Using Reconfigurable RF Block. J. Semicond. Technol. Sci. 2004, 4, 174–181. [Google Scholar]

- Akeela, R.; Dezfouli, B. Software-defined Radios: Architecture, state-of-the-art, and challenges. Comput. Commun. 2018, 128, 106–125. [Google Scholar] [CrossRef]

- Chen, Y.; Yan, N.; Xu, J.; Chen, Q.; Sun, J. Low power, high linearity multi-mode downconversion mixer for SDR. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems, Beijing, China, 19–23 May 2013; pp. 737–740. [Google Scholar]

- Liu, X.; Zhang, X. Multiband Spectrum Access: Great Promises for Future Cognitive Radio Networks. IEEE Trans. Ind. Inform. 2020, 16, 5379–5388. [Google Scholar] [CrossRef]

- Kalathil, D.M.; Jain, R. Spectrum Sharing through Contracts for Cognitive Radios. IEEE Trans. Mob. Comput. 2013, 12, 1999–2011. [Google Scholar] [CrossRef]

- Hattab, G.; Ibnkahla, M. Multiband Spectrum Access: Great Promises for Future Cognitive Radio Networks. Proc. IEEE 2014, 102, 282–306. [Google Scholar] [CrossRef]

- Djoumessi, E.E.; Wu, K. White Space Communication Technologies; Cambridge University Press: Cambridge, UK, 2014. [Google Scholar]

- Davis, M.; Davis, C. Sampling Mixer for Software Defined Radio Applications using 0.18 um RF CMOS Technology. Undergraduate Thesis, Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, 2013. [Google Scholar]

- Asad, B.Z.J. Low-Noise 24 GHz 0.15 um GaAs pHEMT Gilbert Cell Mixer for Intelligent Transportation System Radar Receiver. Master of Applied Science Thesis, Ottawa-Carleton Institute for Electrical and Computer Engineering, Electrical and Computer Engineering, Ottawa, ON, Canada, 2014. [Google Scholar]

- Zumbahlen, H. Linear Circuit Design Handbook; Newnes/Elsevier: Wilmington, MA, USA, 2008. [Google Scholar]

- Siddiqi, A.A. Design Methodology and investigation of GHz range CMOS RF mixers. Master of Engineering Thesis, Carleton University, Ottawa, ON, Canada, 2000. [Google Scholar]

- Arun, J.; Ezra, K.; Nithin, M.; Ravi, S. Design and Analysis of Double Balanced Gilbert Cell CMOS Mixer for Heterodyne receivers. Int. J. Appl. Eng. Res. 2013, 8, 2413–2416. [Google Scholar]

- Hu, X. RF CMOS Tunable Gilbert Mixer with Wide Tuning Frequency and Controllable Bandwidth: Design Sythesis and Verification. Master of Science Thesis, Department of Electrical Engineering, Wright State University, Dayton, OH, USA, 2017. [Google Scholar]

- Piccinni, G.; Avitabile, G.; Coviello, G.; Talarico, C. Gilbert cell mixer design based on a novel systematic approach for nanoscale technologies. In Proceedings of the 2017 IEEE 18th Wireless and Microwave Technology Conference, Cocoa Beach, FL, USA, 24–25 April 2017; pp. 1–4. [Google Scholar]

- Liu, B.; Fan, F.; Zhang, H.; Zeng, C. A wideband down conversion mixer with dual cross-coupled loops for software defined radio. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems, Lisbon, Portugal, 24–27 May 2015; pp. 990–993. [Google Scholar]

- Mehta, S.; Li, X.J.; Aneja, A. A Low Noise Image-Rejection Gilbert Mixer for Software Defined Radios. In Proceedings of the 2020 IEEE International Conference on Electronics, Computing and Communication Technologies, Bangalore, India, 2–4 July 2020; pp. 1–6. [Google Scholar]

- Chrisben Gladson, S.; Bhaskar, M. A low power high-performance area efficient RF front-end exploiting body effect for 2.4 GHz IEEE 802.15.4 applications. AEU-Int. J. Electron. Commun. 2018, 96, 81–92. [Google Scholar] [CrossRef]

- Huang, W.H.; Huang, I.Y.; Tseng, Y.S.; Hsieh, C.H.; Wang, C.C. A 19.38dBm OIP3 gm-boosted up-conversion CMOS mixer for 5–6GHz application. Microelectron. J. 2017, 60, 38–44. [Google Scholar] [CrossRef]

- Tomar, V.S.; Bhatia, V. Low Cost and Power Software Defined Radio Using Raspberry Pi for Disaster Effected Regions. Procedia Comput. Sci. 2015, 58, 401–407. [Google Scholar] [CrossRef]

- Hampel, S.K.; Schmitz, O.; Tiebout, M.; Rolfes, I. Inductorless Low-Voltage and Low-Power Wideband Mixer for Multistandard Receivers. IEEE Trans. Microw. Theory Tech. 2010, 58, 1384–1390. [Google Scholar] [CrossRef]

- Vidojkovic, V.; Tang, J.V.D.; Leeuwenburgh, A.; Roermund, A.V. Mixer topology selection for a 1.8–2.5 GHz multi-standard front-end in 0.18 um CMOS. In Proceedings of the 2003 International Symposium on Circuits and Systems, Bangkok, Thailand, 25–28 May 2003; Volume 2, pp. II301–II303. [Google Scholar]

- Vahidfar, M.B.; Shoaei, O. A CMOS high IIP2 mixer for multi-standard receivers. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 656–659. [Google Scholar]

- Kitsunezuka, M.; Hori, S.; Maeda, T. A Widely-Tunable Reconfigurable CMOS Analog Baseband IC for Software-Defined Radio. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 66–595. [Google Scholar]

- Peng, Y.; Zhang, L.; Fu, J.; Wang, Y. Analysis and Design of a Broadband SiGe HBT Image-Reject Mixer Integrating Quadrature Signal Generator. IEEE Trans. Microw. Theory Tech. 2016, 64, 688–698. [Google Scholar] [CrossRef]

- El-Nozahi, M.; Sanchez-Sinencio, E.; Entesari, K. A CMOS Low-Noise Amplifier With Reconfigurable Input Matching Network. IEEE Trans. Microw. Theory Tech. 2009, 57, 1054–1062. [Google Scholar] [CrossRef]

- Othman, A.; Barrak, R.; Mabrouk, M. A tunable RF filter for multistandard GSM/UMTS/WiFi/LTE receiver. In Proceedings of the 2014 Mediterranean Microwave Symposium, Marrakech, Morocco, 12–14 December 2014; pp. 1–5. [Google Scholar]

- Lee, J.; Yun, T. High-gain mixer using cascode current bleeding and gm-boosting techniques. Microw. Opt. Technol. Lett. 2016, 59, 1–5. [Google Scholar] [CrossRef]

- Raja, R.; Venkataramani, B. A Current Injection Folded-Switch Mixer for Direct Conversion Receiver. In Proceedings of the International Conference on Communication Systems, Haryana, India, 18–20 October 2013; B K Birla Institute of Engineering and Technology: Haryana, India, 2013; pp. 36–44. [Google Scholar]

- Wei, B.; Dai, Y.; Lu, Y.; Zhang, X.; Liu, H. A Sub 1V High-Gain Low-Noise CMOS Downconversion Folded Mixer for 2.4 GHz ISM Band Applications. In Proceedings of the 2008 International Symposium on Intelligent Information Technology Application Workshops, Shanghai, China, 21–22 December 2008; pp. 689–692. [Google Scholar]

- Wei, H.; Hsiao, C. A 1 V bulk-controlled gm-boosted CMOS mixer for LTE-A applications. In Proceedings of the 2013 IEEE 2nd Global Conference on Consumer Electronics, Tokyo, Japan, 1–4 October 2013; pp. 239–242. [Google Scholar]

- Vahidfar, M.B.; Shoaei, O.; Hassanzadeh, M.R. CMOS mixer enhanced for multi-standard receivers. In Proceedings of the 2007 50th Midwest Symposium on Circuits and Systems, Montreal, QC, Canada, 5–8 August 2007; pp. 1010–1013. [Google Scholar]

- Yan, J.; Lim, K.M.; Gu, J.; Wang, K.; Lim, W.M.; Ma, K.; Yeo, K.S. A double-quadrature down-conversion mixer in 0.18 um SiGe BiCMOS process. In Proceedings of the 2011 International SoC Design Conference, Jeju, Korea, 17–18 November 2011; pp. 246–249. [Google Scholar]

- Zhang, C. Reconfigurable RF Front End Components for Multi-Radio Platform Applications. Doctor of Philosophy Thesis, Electrical Engineering, University of Tennessee-Knoxville, Knoxville, TN, USA, 2009. [Google Scholar]

- Kim, J.H.; Jang, Y.K.; Yoo, H.J. Design of reconfigurable RF front-end for multi-standard receiver using switchable passive networks. Analog Integr. Circuits Signal Process. 2007, 50, 81–88. [Google Scholar] [CrossRef]

- Hu, B.; Yu, X.; He, L. A Gm-boosted and current peaking wideband merged LNA and mixer. In Proceedings of the 2010 IEEE International Conference on Ultra-Wideband, Nanjing, China, 20–23 September 2010; Volume 1, pp. 1–4. [Google Scholar]

- Carusone, T.C.; Johns, D.A.; Martin, K.W. Analog Integrated Circuit Design; Wiley: Hoboken, NJ, USA, 2012. [Google Scholar]

- Tang, S.L. A new impedance matching method of CMOS mixer with common-source input stage. In Proceedings of the 2005 6th International Conference on ASIC, Shanghai, China, 24–27 October 2005; Volume 1, pp. 512–515. [Google Scholar]

- Zhiqun, L.; Zhigong, W.; Wei, C.; Li, Z. Image rejection low noise amplifier for WLAN 802.11a application. In Proceedings of the 2005 Asia-Pacific Microwave Conference Proceedings, Suzhou, China, 4–7 December 2005; Volume 5, pp. 1–4. [Google Scholar]

- Long, J.R. A low-voltage 5.1–5.8-GHz image-reject downconverter RF IC. IEEE J. Solid-State Circuits 2000, 35, 1320–1328. [Google Scholar] [CrossRef]

- Heijningen, M.V.; Hoogland, J.A.; Hek, A.P.D.; Vliet, F.E.V. 6–12 GHz double-balanced image-reject mixer MMIC in 0.25 um AlGaN/GaN technology. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; pp. 65–68. [Google Scholar]

- Razavi, B. RF Microelectronics; Pearson Education: Boston, MA, USA, 2012. [Google Scholar]

- Heydari, P. An analysis of high-frequency noise in RF active CMOS mixers. Analog Integr. Circuits Signal Process. 2006, 48, 199–209. [Google Scholar] [CrossRef]

- Yadav, V.S.; Chaturvedi, A. 2.4 GHz active CMOS mixer for Bluetooth and Zigbee receiver systems. In Proceedings of the International Conference on Recent Advances and Innovations in Engineering, Jaipur, Rajasthan, India, 9–11 May 2014; pp. 1–6. [Google Scholar]

- Chen, J.; Lin, Z. 2.4 GHz High IIP3 and Low-Noise Down-conversion Mixer. In Proceedings of the 2006 IEEE Asia Pacific Conference on Circuits and Systems, Singapore, 4–7 December 2006; pp. 37–40. [Google Scholar]

- Motieifar, A.; Pour, Z.A.; Bridges, G.; Shafai, C.; Shafai, L. An ultra wideband mixer with integrated impedance-matching circuit. In Proceedings of the 2006 12th International Symposium on Antenna Technology and Applied Electromagnetics and Canadian Radio Sciences Conference, Montreal, QC, Canada, 17–19 July 2006; pp. 1–4. [Google Scholar]

- Tedjini-Bailiche, S.A.; Trabelsi, M.; Slimane, A.; Belaroussi, M.T.; Haddad, F.; Bourdel, S. Ultra low power and high gain switched CMOS gm-boosted current reused mixer for wireless multi-standard applications. Microelectron. J. 2014, 45, 1575–1582. [Google Scholar] [CrossRef]

- Liang, K.; Chang, H.; Chan, Y. A 0.5–7.5 GHz Ultra Low-Voltage Low-Power Mixer Using Bulk-Injection Method by 0.18- um CMOS Technology. IEEE Microw. Wirel. Comp. Lett. 2007, 17, 531–533. [Google Scholar] [CrossRef]

- Wu, C.; Hsieh, H.; Lai, L.; Lu, L. A 3–5 GHz Frequency-Tunable Receiver Frontend for Multiband Applications. IEEE Microw. Wirel. Comp. Lett. 2008, 18, 638–640. [Google Scholar] [CrossRef]

- Ho, S.S.K.; Saavedra, C.E. A CMOS Broadband Low-Noise Mixer With Noise Cancellation. IEEE Trans. Microw. Theory Tech. 2010, 58, 1126–1132. [Google Scholar] [CrossRef]

- Lin, Y.; Lan, K.; Wang, C.; Chi, C.; Lu, S. 6.3 mW 94 GHz CMOS Down-Conversion Mixer With 11.6 dB Gain and 54 dB LO-RF Isolation. IEEE Microw. Wirel. Comp. Lett. 2016, 26, 604–606. [Google Scholar] [CrossRef]

- Zhu, F.; Wang, K.; Wu, K. A Reconfigurable Low-Voltage and Low-Power Millimeter-Wave Dual-Band Mixer in 65-nm CMOS. IEEE Access 2019, 7, 33359–33368. [Google Scholar] [CrossRef]

- Na, D.; Kim, T.W. A 1.2 V, 0.87–3.7 GHz Wideband Low-Noise Mixer Using a Current Mirror for Multiband Application. IEEE Microw. Wirel. Comp. Lett. 2012, 22, 91–93. [Google Scholar] [CrossRef]

- Mahajan, D.; Ruparelia, V. Reliability Simulation and Analysis of Important RF Circuits Using Cadence Relxpert. In Proceedings of the 2018 IEEE International Conference on Electronics, Computing and Communication Technologies, Bangalore, India, 16–17 March 2018; pp. 1–6. [Google Scholar]

| Ref. | Tech. | Area (mm2) | Freq. (GHz) | S21 (dB) | NF (dB) | IRR (dB) | IP3 (dBm) | S11 (dB) |

|---|---|---|---|---|---|---|---|---|

| This work | SiGe 8HP | 1.8 | 0.9–13.5 | 15.1–22.1 | 2.5–5.6 | 24.9–30.2 | −3.28–9.05 | −17.14–22.7 |

| [42] | 0.25 um | Nil | 0.9 | 5 | 8 | 30 | 1 | −15 |

| [8] | 0.065 um | 0.19 | 0.9, 1.8–2.5 | 9.2–13 | 13.6–18.3 | Nil | ≥10.8 | Nil |

| [48] | 0.18 um | Nil | 2.42–2.48 | 10.73 | Nil | Nil | −7.31 | Nil |

| [49] | 0.18 um | Nil | 2.4 | 9.3 | 7.4 | Nil | 8 | Nil |

| [26] | 0.18 um | Nil | 2.4 | 17 | 11 | Nil | 1 | Nil |

| [34] | 0.18 um | Nil | 2.44 | 18.6 | 7.15 | Nil | −8.1 | Nil |

| [50] | 0.18 um | <1 | 3.1–10.6 | ≥10 | 10 | Nil | 4 | −25 |

| [5] | 0.18 um | 1.4 | 5.1 | 18 | 13.2 | Nil | −5.85 | −14.5 |

| [44] | SiGe | 0.9 | 5.1–5.8 | 14 | 6.8 | 36 | −5.5 | −11 |

| [32] | 0.13 um | 0.85 | 7.2–8.4 | 23.8 | 4.3 | 30 | −10.5 | Nil |

| [51] | 0.18 um | 0.11 | 1.8–2.4 | 23–26 | 16–20 | Nil | −2 | Nil |

| [52] | 0.18 um | 0.61 | 0.5–7.5 | 5.7 | 15 | Nil | −5.7 | Nil |

| [53] | 0.18 um | 1.14 | 3–5 | 19.8–20.6 | 7.7–8.7 | Nil | >−6 | −10.5–15.2 |

| [25] | 0.065 um | 0.21 | 1–10.5 | 10–14.5 | 6.5–10 | Nil | Nil | −20 |

| [54] | 0.13 um | 0.31 | 1–5.5 | 17.5 | 3.9 | Nil | 0.84 | <−8.8 |

| [55] | 0.09 um | 0.57 | 80–110 | 4.1–11.6 | 15.8–18.1 | Nil | 3 | −8.7–22 |

| [56] | 0.065 um | 0.5 | 17–43 | −0.1 ± 1.5 | 12.4 | Nil | 3.4 | Nil |

| [57] | 0.13 um | 0.13 | 0.87–3.7 | 13.5–14 | 2.9–6.5 | Nil | −10–13 | Nil |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mehta, S.; Li, X.-J.; Donelli, M. Design and Analysis of a Reconfigurable Gilbert Mixer for Software-Defined Radios. Sensors 2021, 21, 2711. https://doi.org/10.3390/s21082711

Mehta S, Li X-J, Donelli M. Design and Analysis of a Reconfigurable Gilbert Mixer for Software-Defined Radios. Sensors. 2021; 21(8):2711. https://doi.org/10.3390/s21082711

Chicago/Turabian StyleMehta, Shilpa, Xue-Jun Li, and Massimo Donelli. 2021. "Design and Analysis of a Reconfigurable Gilbert Mixer for Software-Defined Radios" Sensors 21, no. 8: 2711. https://doi.org/10.3390/s21082711

APA StyleMehta, S., Li, X.-J., & Donelli, M. (2021). Design and Analysis of a Reconfigurable Gilbert Mixer for Software-Defined Radios. Sensors, 21(8), 2711. https://doi.org/10.3390/s21082711