An Ultrafast Active Quenching Active Reset Circuit with 50% SPAD Afterpulsing Reduction in a 28 nm FD-SOI CMOS Technology Using Body Biasing Technique

Abstract

1. Introduction

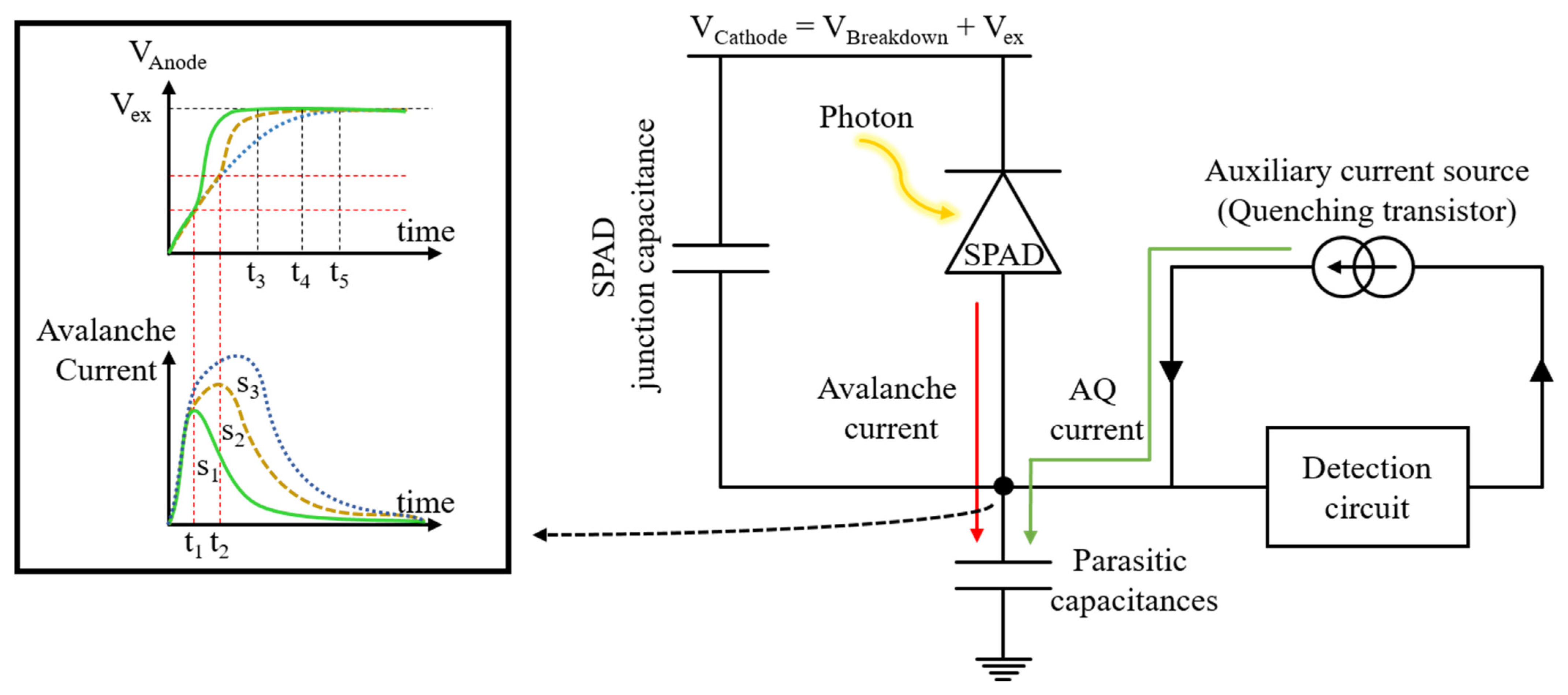

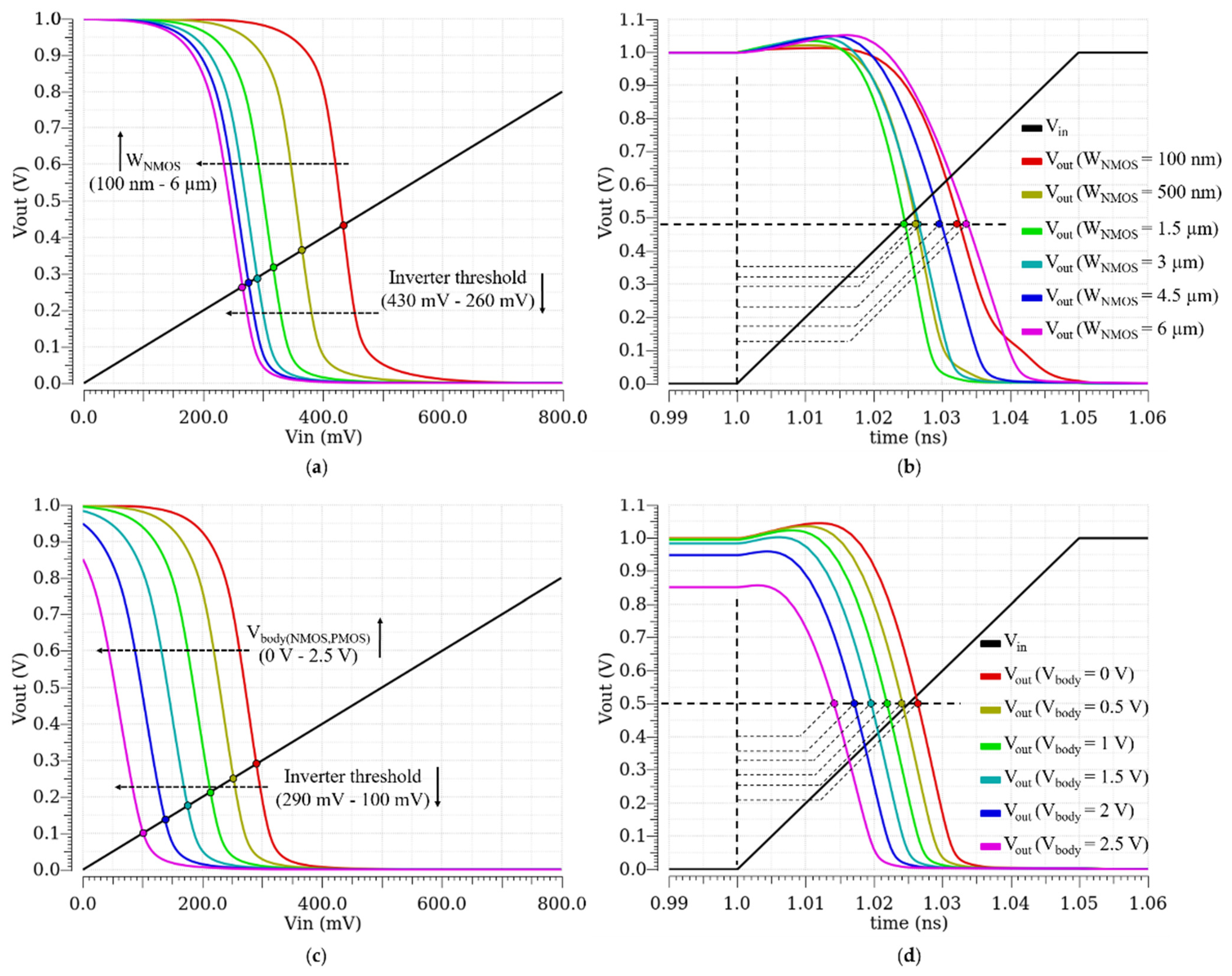

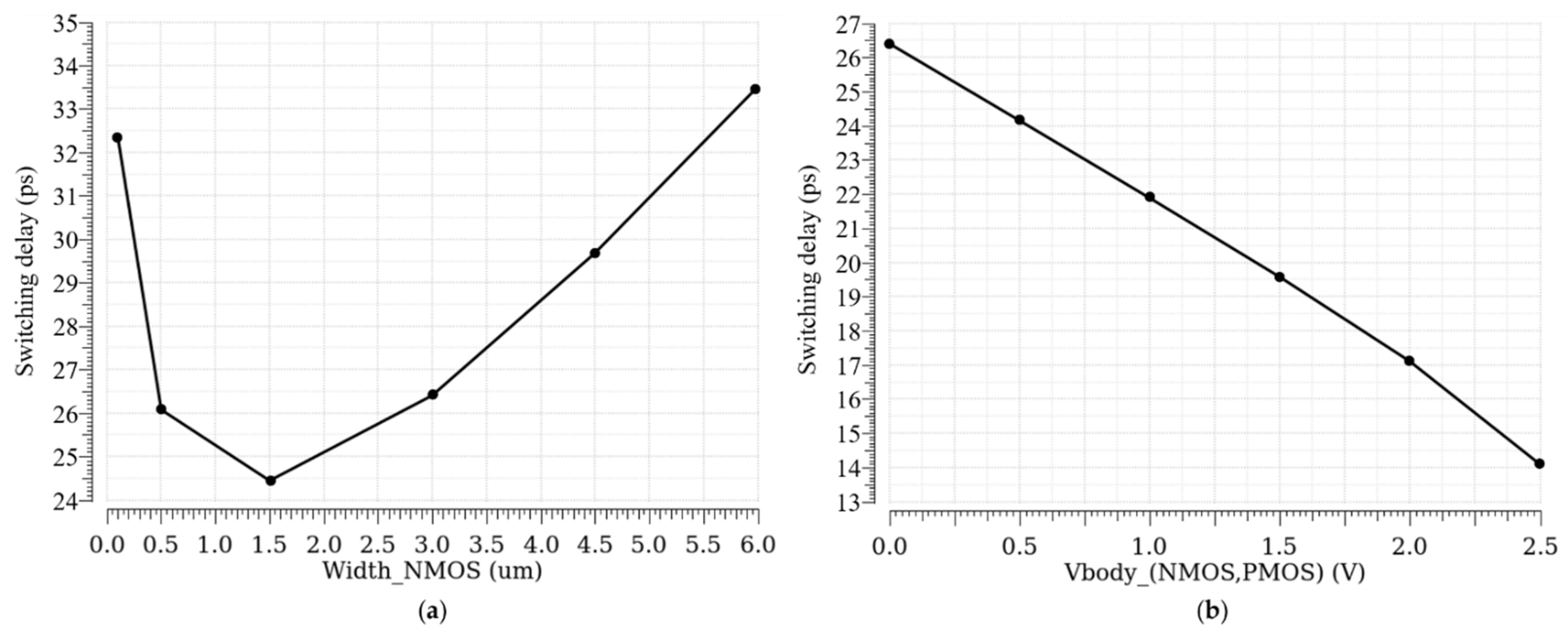

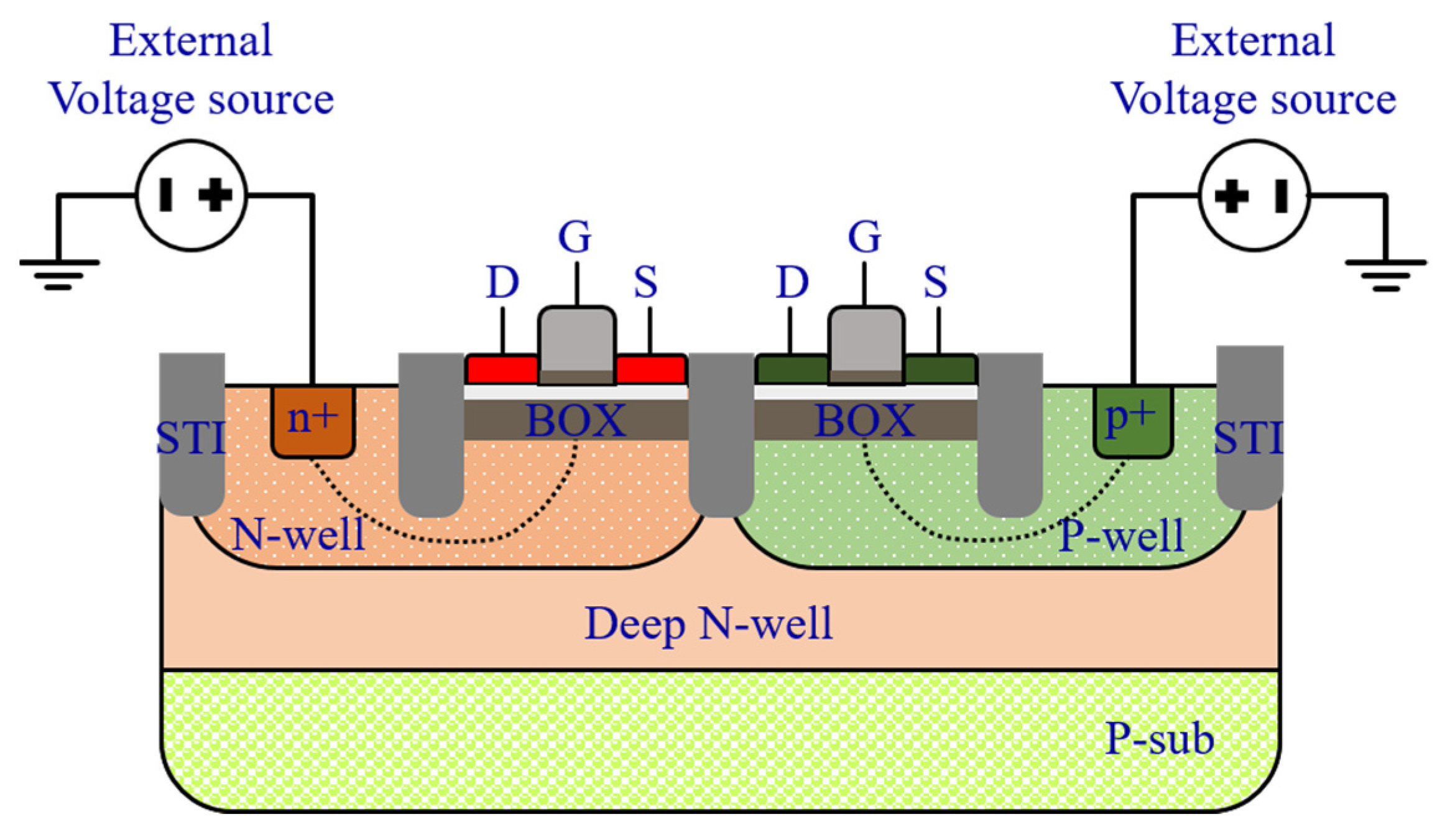

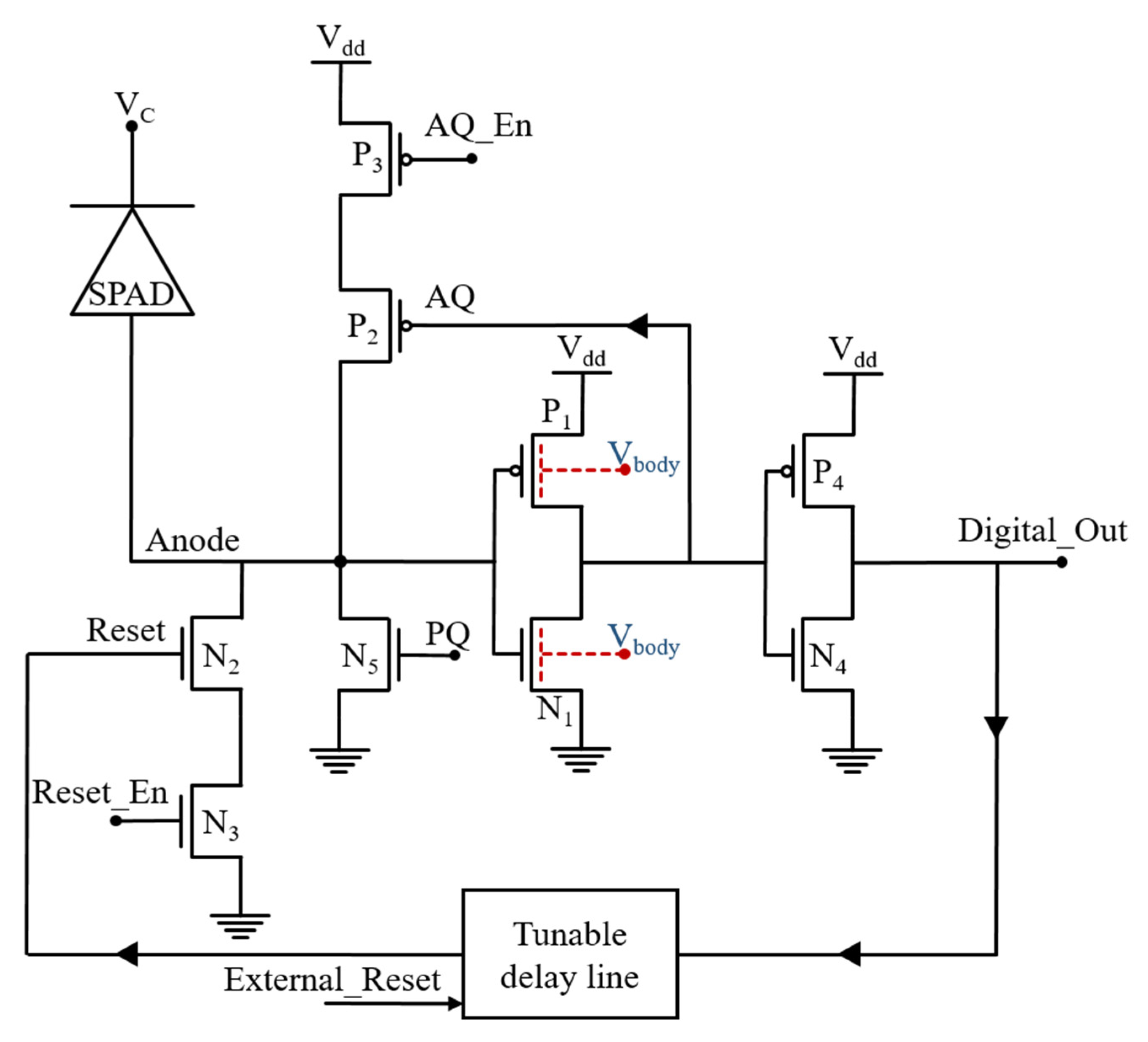

2. Fast Avalanche Detection

3. The AQAR Circuit Based on the Body Biased Inverter

4. Results

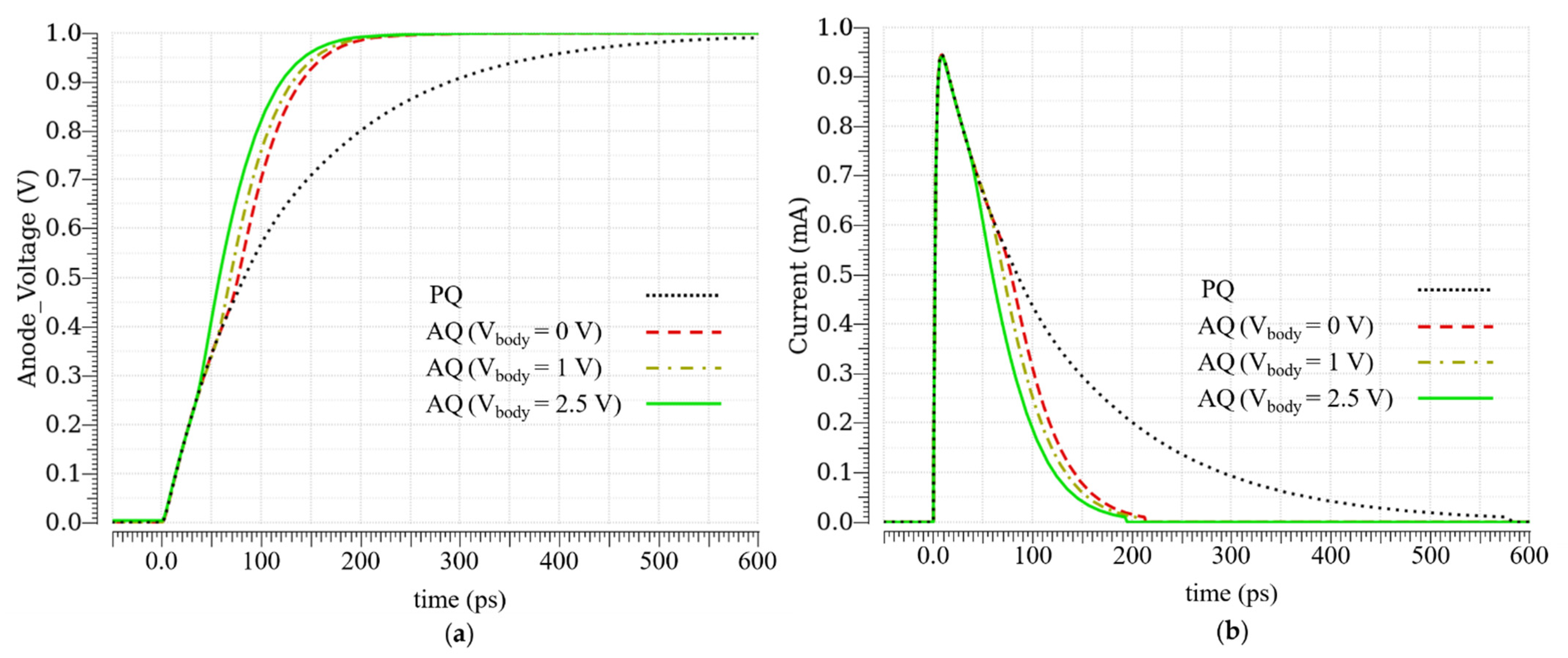

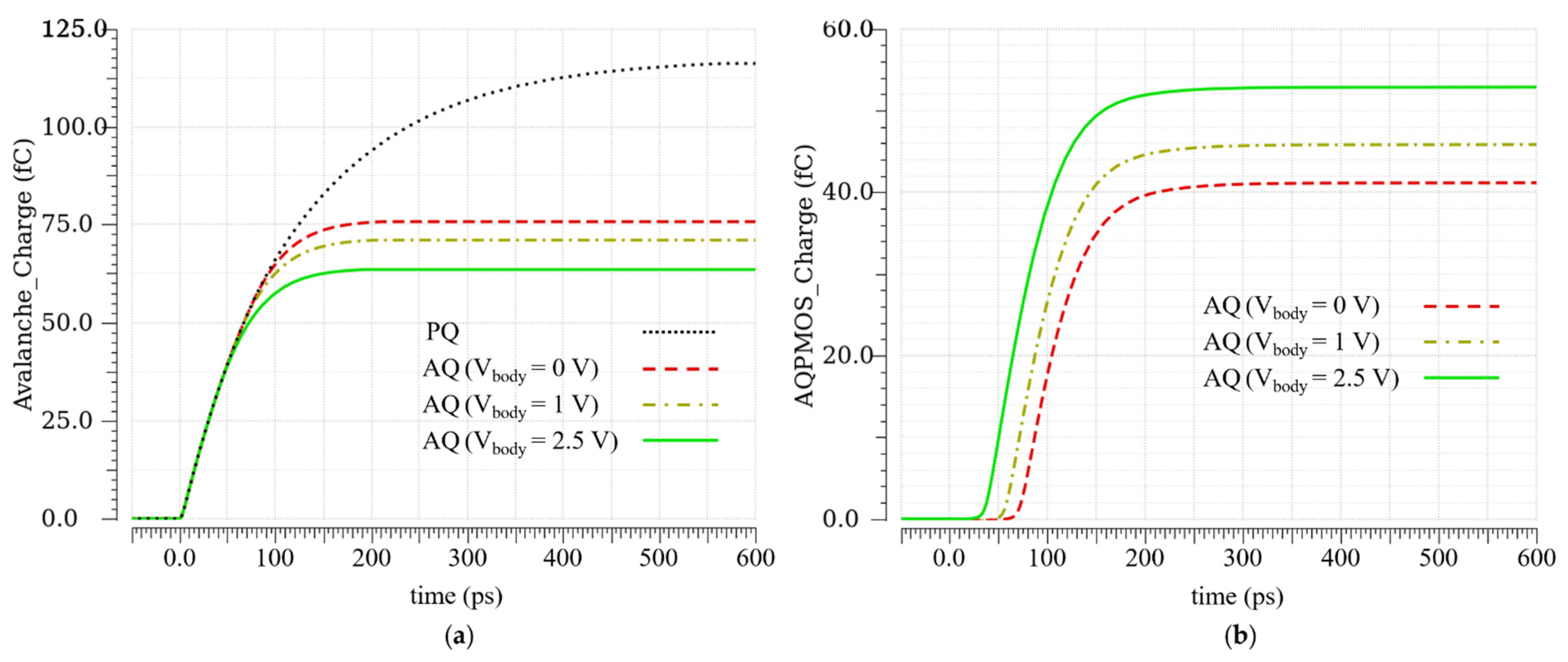

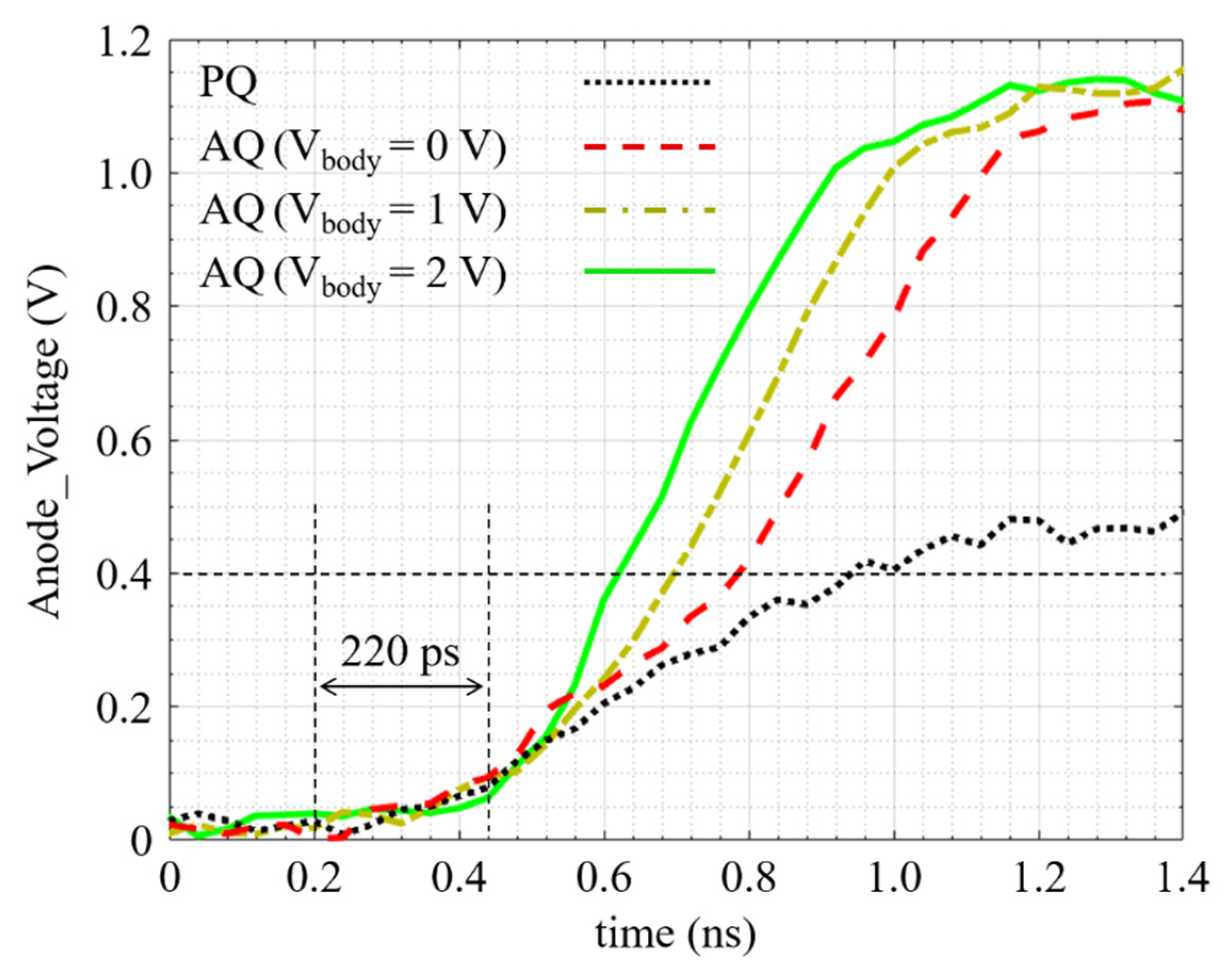

4.1. Post Layout Simulation Results

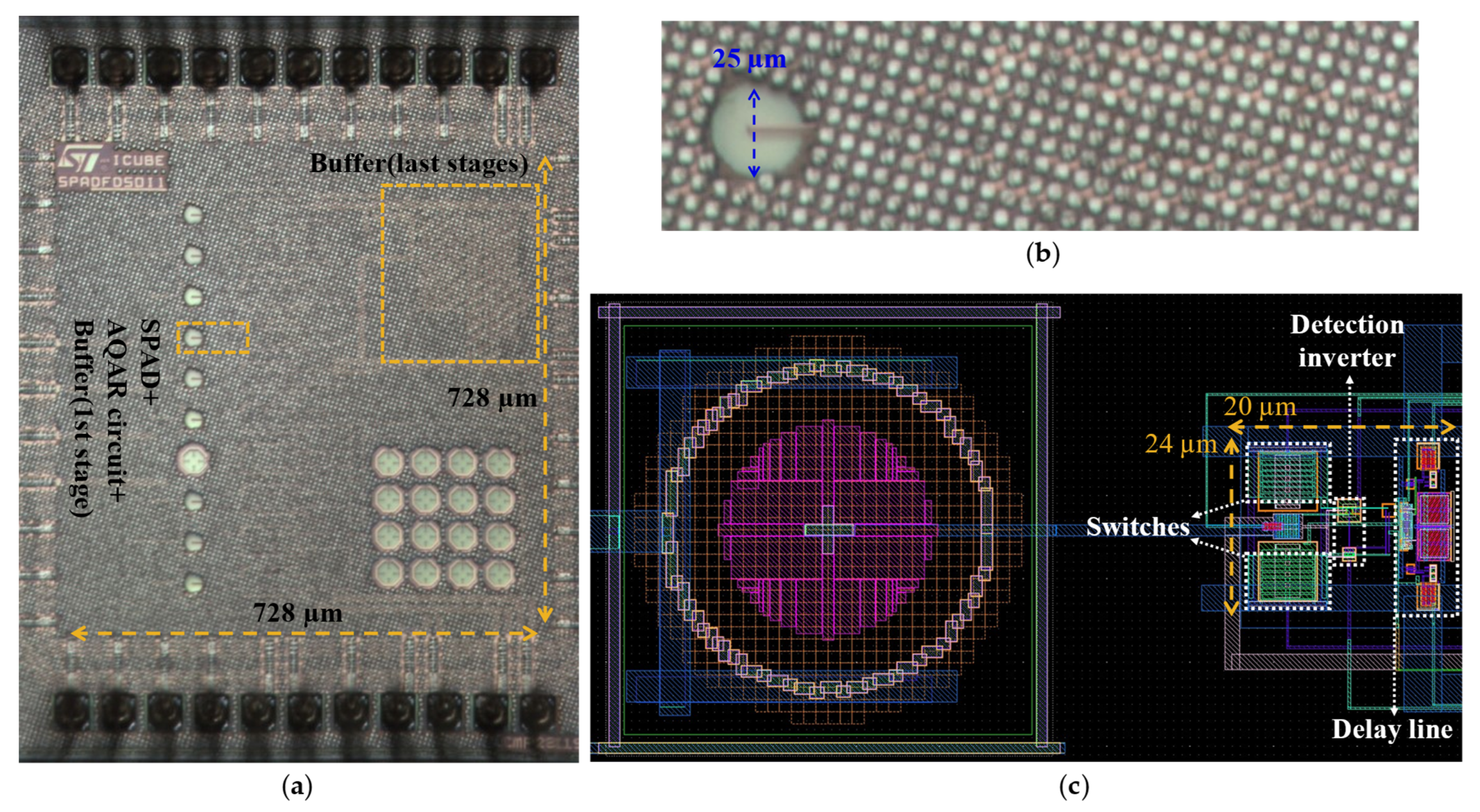

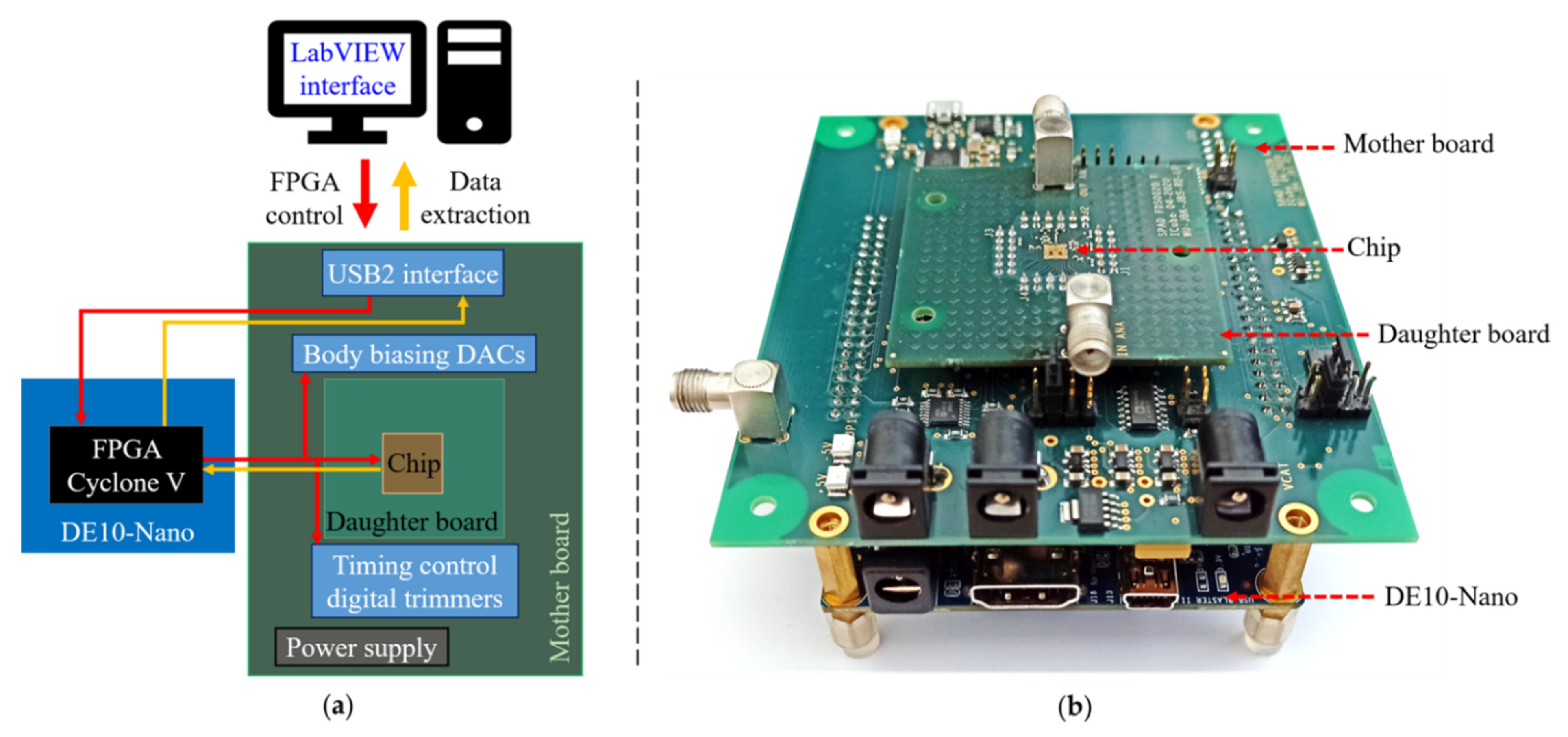

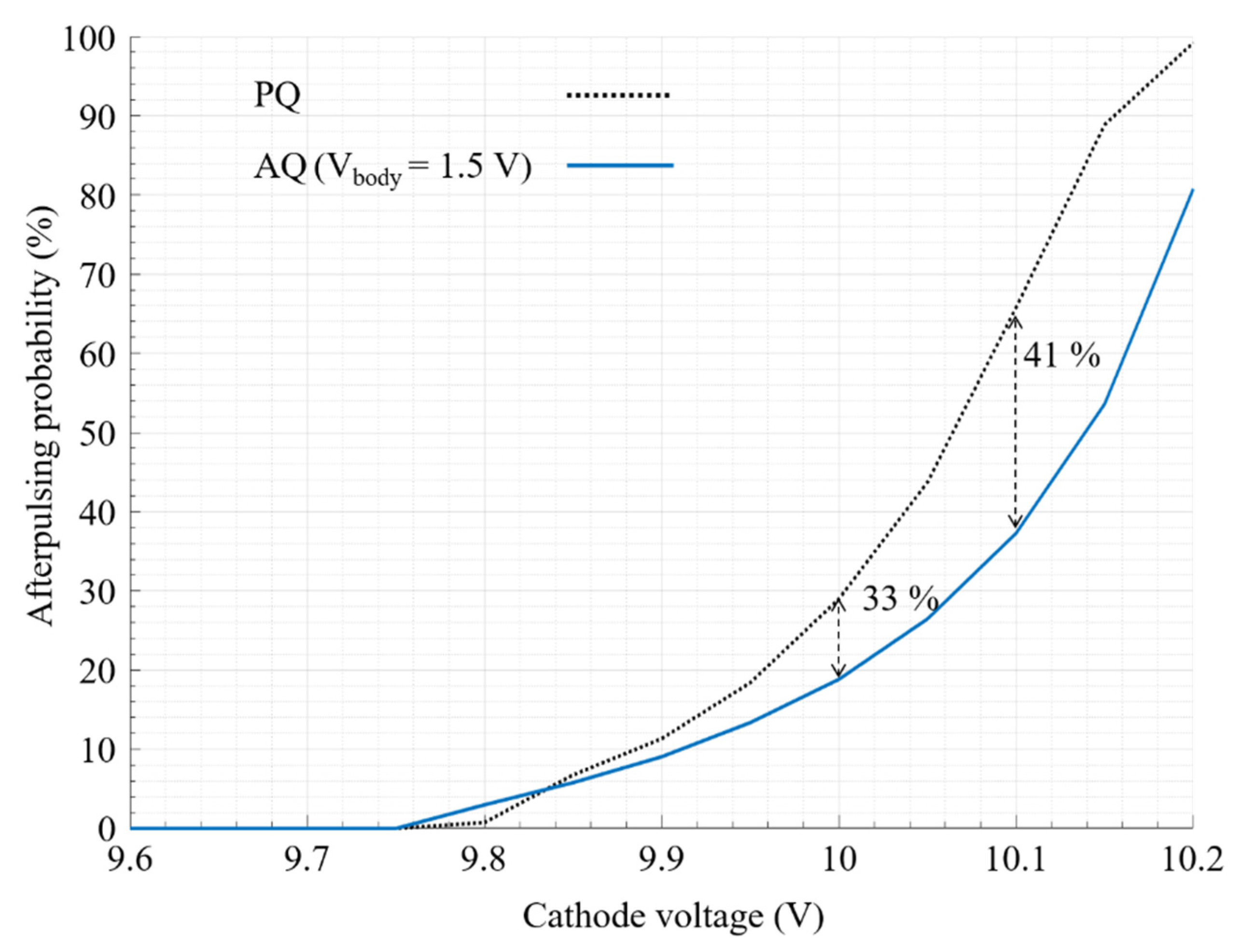

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lee, M.-J.; Ximenes, A.R.; Padmanabhan, P.; Wang, T.-J.; Huang, K.-C.; Yamashita, Y.; Yaung, D.-N.; Charbon, E. High-Performance Back-Illuminated Three-Dimensional Stacked Single-Photon Avalanche Diode Implemented in 45-Nm CMOS Technology. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–9. [Google Scholar] [CrossRef]

- Zhang, C.; Lindner, S.; Antolović, I.M.; Mata Pavia, J.; Wolf, M.; Charbon, E. A 30-Frames/s, $252\times144$ SPAD Flash LiDAR With 1728 Dual-Clock 48.8-Ps TDCs, and Pixel-Wise Integrated Histogramming. IEEE J. Solid State Circuits 2019, 54, 1137–1151. [Google Scholar] [CrossRef]

- Pavia, J.M.; Scandini, M.; Lindner, S.; Wolf, M.; Charbon, E. A 1 × 400 Backside-Illuminated SPAD Sensor With 49.7 Ps Resolution, 30 PJ/Sample TDCs Fabricated in 3D CMOS Technology for Near-Infrared Optical Tomography. IEEE J. Solid State Circuits 2015, 50, 2406–2418. [Google Scholar] [CrossRef]

- Zappa, F.; Tisa, S.; Tosi, A.; Cova, S. Principles and Features of Single-Photon Avalanche Diode Arrays. Sens. Actuators A Phys. 2007, 140, 103–112. [Google Scholar] [CrossRef]

- Gallivanoni, A.; Rech, I.; Ghioni, M. Progress in Quenching Circuits for Single Photon Avalanche Diodes. IEEE Trans. Nucl. Sci. 2010, 57, 3815–3826. [Google Scholar] [CrossRef]

- Moreno-García, M.; Pancheri, L.; Perenzoni, M.; del Río, R.; Guerra Vinuesa, Ó.; Rodríguez-Vázquez, Á. Characterization-Based Modeling of Retriggering and Afterpulsing for Passively Quenched CMOS SPADs. IEEE Sens. J. 2019, 19, 5700–5709. [Google Scholar] [CrossRef]

- Palubiak, D.P.; Li, Z.; Deen, M.J. Afterpulsing Characteristics of Free-Running and Time-Gated Single-Photon Avalanche Diodes in 130-Nm CMOS. IEEE Trans. Electron. Devices 2015, 62, 3727–3733. [Google Scholar] [CrossRef]

- Lakeh, M.D.; Kammerer, J.-B.; Uhring, W.; Schell, J.-B.; Calmon, F. An Ultrafast Active Quenching Circuit for SPAD in CMOS 28nm FDSOI Technology. In Proceedings of the 2020 IEEE Sensors, Rotterdam, The Netherlands, 25–28 October 2020; pp. 1–4. [Google Scholar]

- Guerrieri, F.; Tisa, S.; Tosi, A.; Zappa, F. Two-Dimensional SPAD Imaging Camera for Photon Counting. IEEE Photonics J. 2010, 2, 759–774. [Google Scholar] [CrossRef]

- El-Desouki, M.M.; Palubiak, D.; Deen, M.J.; Fang, Q.; Marinov, O. A Novel, High-Dynamic-Range, High-Speed, and High-Sensitivity CMOS Imager Using Time-Domain Single-Photon Counting and Avalanche Photodiodes. IEEE Sens. J. 2011, 11, 1078–1083. [Google Scholar] [CrossRef]

- Cova, S.; Lacaita, A.; Ripamonti, G. Trapping Phenomena in Avalanche Photodiodes on Nanosecond Scale. IEEE Electron Device Lett. 1991, 12, 685–687. [Google Scholar] [CrossRef]

- Ghioni, M.; Giudice, A.; Cova, S.; Zappa, F. High-Rate Quantum Key Distribution at Short Wavelength: Performance Analysis and Evaluation of Silicon Single Photon Avalanche Diodes. J. Mod. Opt. 2003, 50, 2251–2269. [Google Scholar] [CrossRef]

- Cova, S.; Ghioni, M.; Lacaita, A.; Samori, C.; Zappa, F. Avalanche Photodiodes and Quenching Circuits for Single-Photon Detection. Appl. Opt. 1996, 35, 1956–1976. [Google Scholar] [CrossRef]

- Wayne, M.A.; Restelli, A.; Bienfang, J.C.; Kwiat, P.G. Afterpulse Reduction Through Prompt Quenching in Silicon Reach-Through Single-Photon Avalanche Diodes. J. Lightwave Technol. 2014, 32, 4097–4103. [Google Scholar] [CrossRef]

- Acerbi, F.; Frera, A.D.; Tosi, A.; Zappa, F. Fast Active Quenching Circuit for Reducing Avalanche Charge and Afterpulsing in InGaAs/InP Single-Photon Avalanche Diode. IEEE J. Quantum Electron. 2013, 49, 563–569. [Google Scholar] [CrossRef]

- Enne, R.; Steindl, B.; Hofbauer, M.; Zimmermann, H. Fast Cascoded Quenching Circuit for Decreasing Afterpulsing Effects in 0.35- μ m CMOS. IEEE Solid-State Circuits Lett. 2018, 1, 62–65. [Google Scholar] [CrossRef]

- Bae, W. CMOS Inverter as Analog Circuit: An Overview. J. Low Power Electron. Appl. 2019, 9, 26. [Google Scholar] [CrossRef]

- Cathelin, A. Fully Depleted Silicon on Insulator Devices CMOS: The 28 nm Node Is the Perfect Technology for Analog, RF, MmW, and Mixed-Signal System-on-Chip Integration. IEEE Solid State Circuits Mag. 2017, 9, 18–26. [Google Scholar] [CrossRef]

- Dalla Mora, A.; Tosi, A.; Tisa, S.; Zappa, F. Single-Photon Avalanche Diode Model for Circuit Simulations. IEEE Photonics Technol. Lett. 2007, 19, 1922–1924. [Google Scholar] [CrossRef]

- Chaves de Albuquerque, T.; Issartel, D.; Clerc, R.; Pittet, P.; Cellier, R.; Golanski, D.; Jouan, S.; Cathelin, A.; Calmon, F. Indirect Avalanche Event Detection of Single Photon Avalanche Diode Implemented in CMOS FDSOI Technology. Solid-State Electron. 2020, 163, 107636. [Google Scholar] [CrossRef]

- Bronzi, D.; Tisa, S.; Villa, F.; Bellisai, S.; Tosi, A.; Zappa, F. Fast Sensing and Quenching of CMOS SPADs for Minimal Afterpulsing Effects. IEEE Photonics Technol. Lett. 2013, 25, 776–779. [Google Scholar] [CrossRef]

- Xu, Y.; Lu, J.; Wu, Z. A Compact High-Speed Active Quenching and Recharging Circuit for SPAD Detectors. IEEE Photonics J. 2020, 12, 1–8. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dolatpoor Lakeh, M.; Kammerer, J.-B.; Aguénounon, E.; Issartel, D.; Schell, J.-B.; Rink, S.; Cathelin, A.; Calmon, F.; Uhring, W. An Ultrafast Active Quenching Active Reset Circuit with 50% SPAD Afterpulsing Reduction in a 28 nm FD-SOI CMOS Technology Using Body Biasing Technique. Sensors 2021, 21, 4014. https://doi.org/10.3390/s21124014

Dolatpoor Lakeh M, Kammerer J-B, Aguénounon E, Issartel D, Schell J-B, Rink S, Cathelin A, Calmon F, Uhring W. An Ultrafast Active Quenching Active Reset Circuit with 50% SPAD Afterpulsing Reduction in a 28 nm FD-SOI CMOS Technology Using Body Biasing Technique. Sensors. 2021; 21(12):4014. https://doi.org/10.3390/s21124014

Chicago/Turabian StyleDolatpoor Lakeh, Mohammadreza, Jean-Baptiste Kammerer, Enagnon Aguénounon, Dylan Issartel, Jean-Baptiste Schell, Sven Rink, Andreia Cathelin, Francis Calmon, and Wilfried Uhring. 2021. "An Ultrafast Active Quenching Active Reset Circuit with 50% SPAD Afterpulsing Reduction in a 28 nm FD-SOI CMOS Technology Using Body Biasing Technique" Sensors 21, no. 12: 4014. https://doi.org/10.3390/s21124014

APA StyleDolatpoor Lakeh, M., Kammerer, J.-B., Aguénounon, E., Issartel, D., Schell, J.-B., Rink, S., Cathelin, A., Calmon, F., & Uhring, W. (2021). An Ultrafast Active Quenching Active Reset Circuit with 50% SPAD Afterpulsing Reduction in a 28 nm FD-SOI CMOS Technology Using Body Biasing Technique. Sensors, 21(12), 4014. https://doi.org/10.3390/s21124014