1. Intoroduction

Precision instrumentation systems, such as optical receivers [

1], electrical sensors [

2,

3,

4,

5], emerging biosensors [

6,

7,

8] photodetectors [

9,

10,

11], and other current-output measurement systems, often contain a transimpedance amplifier (TIA). An operational amplifier (op-amp) with negative feedback is typically used in a TIA. The most typical TIA topology is a resistive feedback TIA (RF-TIA), which is simple and easy to analyze as the feedback resistor directly matches the transimpedance gain. In [

3,

4,

6,

7,

12,

13,

14,

15], a capacitive feedback TIA (CF-TIA) has been proposed to reduce the thermal noise generated by the feedback resistor, as well as overcome difficulties in the integration of high resistance in complementary metal-oxide-semiconductor (CMOS) chips.

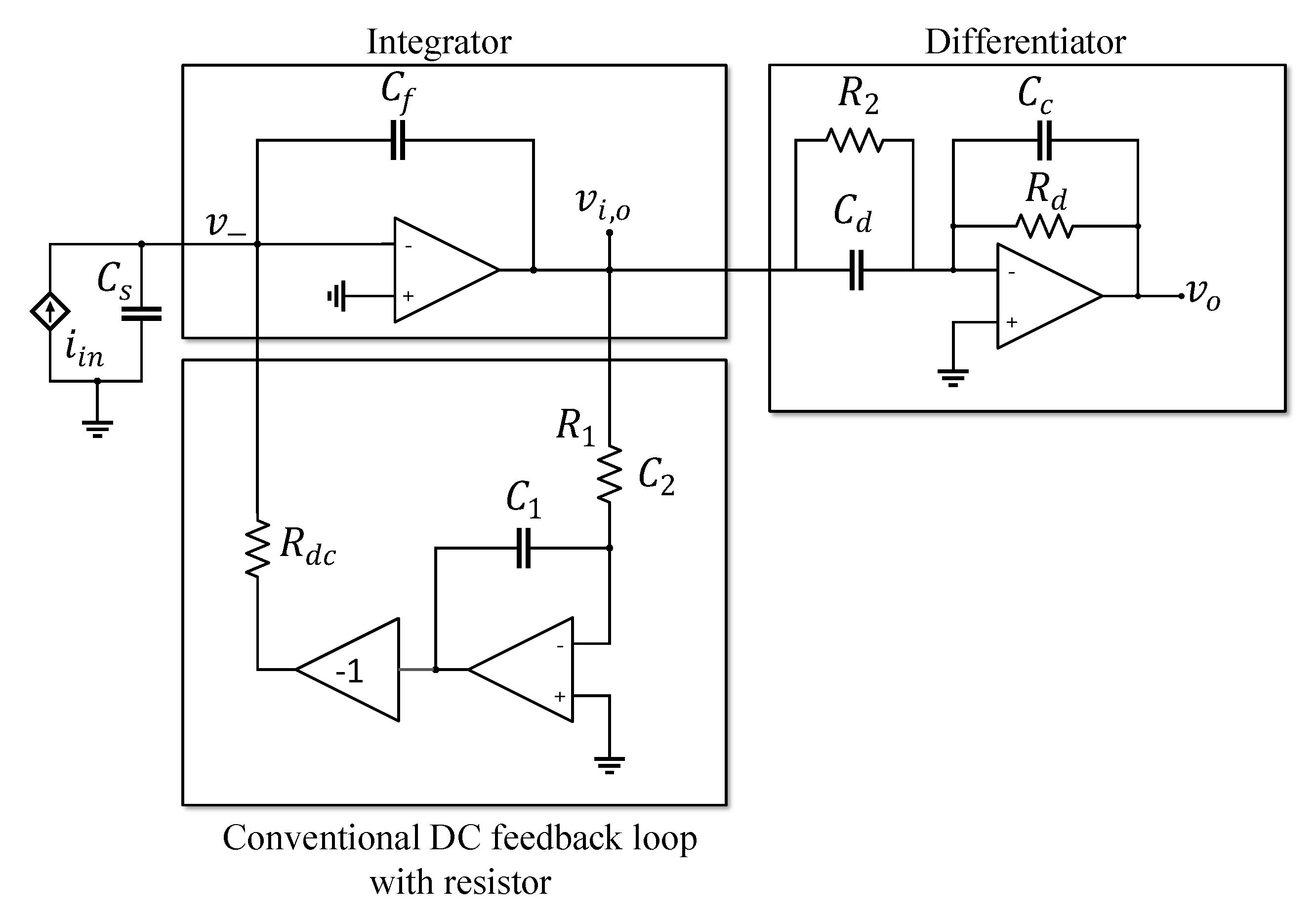

The basic topology of the CF-TIA is composed of an integrator and a cascaded differentiator, as shown in

Figure 1. The DC feedback loop is typically inserted in the first stage integrator. It provides a DC path to prevent saturation of the integrator’s feedback capacitor

and simultaneously to bias the op-amp. The conventional DC feedback loop consists of an non-inverting integrator to filter the DC components on the feedback path and a resistor

to drain the DC components from the input node. Although a high value of

is preferred to reduce the thermal noise currents of

, it limits the maximum allowable DC input with the output voltage range of the op-amp, as in [

6,

7]. The voltage drop across

with the DC input should be less than the op-amp output voltage range which is usually slightly less than the op-amp supply voltage. The higher the allowable DC input, the lower the value of

.

In some applications such as optical sensors, the DC input varies according to the amount of background light. While the normal DC input from the ambient light is typically low, the maximum feasible value of the DC input can be fairly high when intense light is directly incident on the sensors. The TIA has to sense the weak target signal on top of the expected maximum value of the DC input in the worst case scenario. However, to allow for high DC input, the value of should be very low, causing the thermal noise to increase significantly. To make matters worse, increased thermal noise is always present even at normal or low DC inputs, degrading overall system performance. In this study, to overcome the shortcomings of the conventional CF-TIA, a new topology that replaces with the transistor in the feedback loop is introduced. The method of discharging DC inputs using the transistor in the DC feedback loop is one of the widely used methods in various circuits, but it has not yet been used and analyzed for CF-TIA. With the transistor, the high DC can flow with a much smaller voltage drop across the base-emitter (gate-drain) compared to the significant voltage drop that occurs when a resistor is used. The thermal noise of the resistor is then replaced by the shot noise of the transistor.

Actually, when assuming a constant DC input, the shot noise is larger than the thermal noise. However, if the DC dynamic range, i.e., the range from the minimum to maximum DC, is significant, the proposed topology has the benefits in the overall noise. The shot noise of the proposed topology varies with the amount of the DC input. In normal cases, DC inputs are much less than the maximum value, so the proposed topology can exhibit lower noise than conventional topology that always shows the worst thermal noise to cope with maximum DC inputs. The advantage in terms of the noise is more distinct compared to the CMOS implementation of the conventional CF-TIA where the thermal noise and shot noise coexist for the pseudo-resistor [

6,

7]. For the CMOS implementation, the proposed topology shows the lower noise than the conventional topology by the amount of thermal noise even for the maximum DC input.

The proposed circuit includes a method for compensating for the adverse effect of the parasitic capacitance of the transistor on system stability. The overall frequency response and design parameters, such as the cut-off frequency and attenuation ratio associated with the system stability, are presented and analyzed for the proposed topology. Moreover, the inclusion of an additional capacitor to the DC feedback loop for ensuring system stability regardless of the DC input value is discussed. Through simulations and experiments, the proposed CF-TIA scheme is validated. In this study, the circuit is implemented with discrete components, but the frequency response model and stability analysis presented are generalized to be applicable to all CF-TIA applications and CMOS chip designs.

2. CF-TIA with DC Feedback Path Using Transistor

This section investigates and analyzes the proposed CF-TIA using a transistor in the DC feedback loop shown in

Figure 2. The transistor

serves as a variable current sink that pulls the average DC input

from the signal path under a steady state condition. Note that the high current can flow from the collector (drain) to the emitter (gate) with only a low base-emitter (gate-drain) voltage.

First, the fundamental performance of the CF-TIA is presented. The achievable bandwidth of the CF-TIA or the upper cutoff frequency,

, is limited by the gain-bandwidth product of the op-amp

and the ratio between

and

as follows [

6,

7]:

where

is the total capacitance at the TIA input including the sensor capacitance

, the input capacitance of the op-amp

(encapsulating the differential and common mode capacitance), the base-collector (gate-drain) parasitic capacitance of the transistor

, and the capacitor

to compensate the effect of

.

Following this, the overall flat gain of the generic CF-TIA can be described as follows:

where

and

constitute the second differentiator,

is the input current, and

is the output voltage of the CF-TIA. Because the gain of the differentiator increases with the frequency until it is rolled off by the open-loop gain of the op-amp, the product of

and

is constrained as follows:

Note that while both a bipolar junction transistor (BJT) and a field-effect transistor (FET) can be used as

, the FET shows a higher parasitic capacitance

than that of the BJT, resulting in a reduced bandwidth as in (

1). Thus, we use the BJT for

here. Then, in order for

to be in an active mode, the appropriate emitter voltage

must be set such that the collector-emitter voltage is greater than 0.7 V. Moreover, to compensate for the influence of

on system stability, the inverting amplifier

whose overall gain is

, and the capacitor

are inserted between the collector and the base of

.

A detailed analysis of the frequency response of the proposed CF-TIA is presented in next. Applying Kirchhoff’s current law at the negative input node of the integrator gives [

16]:

where

is the output voltage of the first stage integrator,

is the open-loop gain of the op-amp,

is the transconductance of

,

is the DC input,

is the thermal voltage (approximately 25 mV at a room temperature of 259 K),

and

constitutes the integrator in the DC feedback loop, and

. In (

4), (a) follows from substituting

as

, and the approximation (b) follows from that

is exceedingly high within the system bandwidth.

By rewriting (

4) to the transimpedance gain form, the transfer function of the integrator

is obtained as follows:

Rewriting (

5) to a standard form of the transfer function of a second-order bandpass filter with a center frequency

and a damping ratio

yields:

where

,

Now, we obtain the upper and lower cut-off frequencies,

and

of

. From the fact that

is the geometric mean of

and

, and from (

5), followings are derived:

When the wide passband is assumed as

,

. Thus,

and

can be expressed as follows:

Moreover, from the assumption of wide passband by

,

is proved, expressed as

From the expressions for

and

in (

5), it can be observed that both

and

ensure the circuit stability. In the absence of

and

,

becomes negative, resulting in two positive real poles in

. If the system has any poles with a positive real part, the part of outputs diverges without a bound, causing system instability. The value of

is preferred to be negligibly small relative to the total input capacitance in order to maximize the achievable bandwidth as in (

1).

In terms of stability,

is preferred to be high, so that makes the system free of gain peaking as

, even with the high

. Note that we assume that the stability is determined based on a condition of a maximally flat response (Butterworth response), which is

. However,

is limited by the condition that the first pole frequency of

should be placed above

. Note that

varies with

, and the case when

exceeds the system bandwidth

is not taken into account. The aforementioned discussion suggests the following conditions:

By cascading the differentiator to the integrator, the overall CF-TIA transfer function,

, is derived by multiplying

by the differentiator transfer function as follows:

where

is used to stabilize the differentiator as

, and

is placed parallel to

in order to generate a zero in

at

in (

9) such that

. Then, the flat gain of

is multiplied by

, and the decrease in

beyond

is compensated by the increase in

with the introduced zero. The resulting

becomes the bandpass filter transfer function, whose lower cutoff frequency

is equal to

.

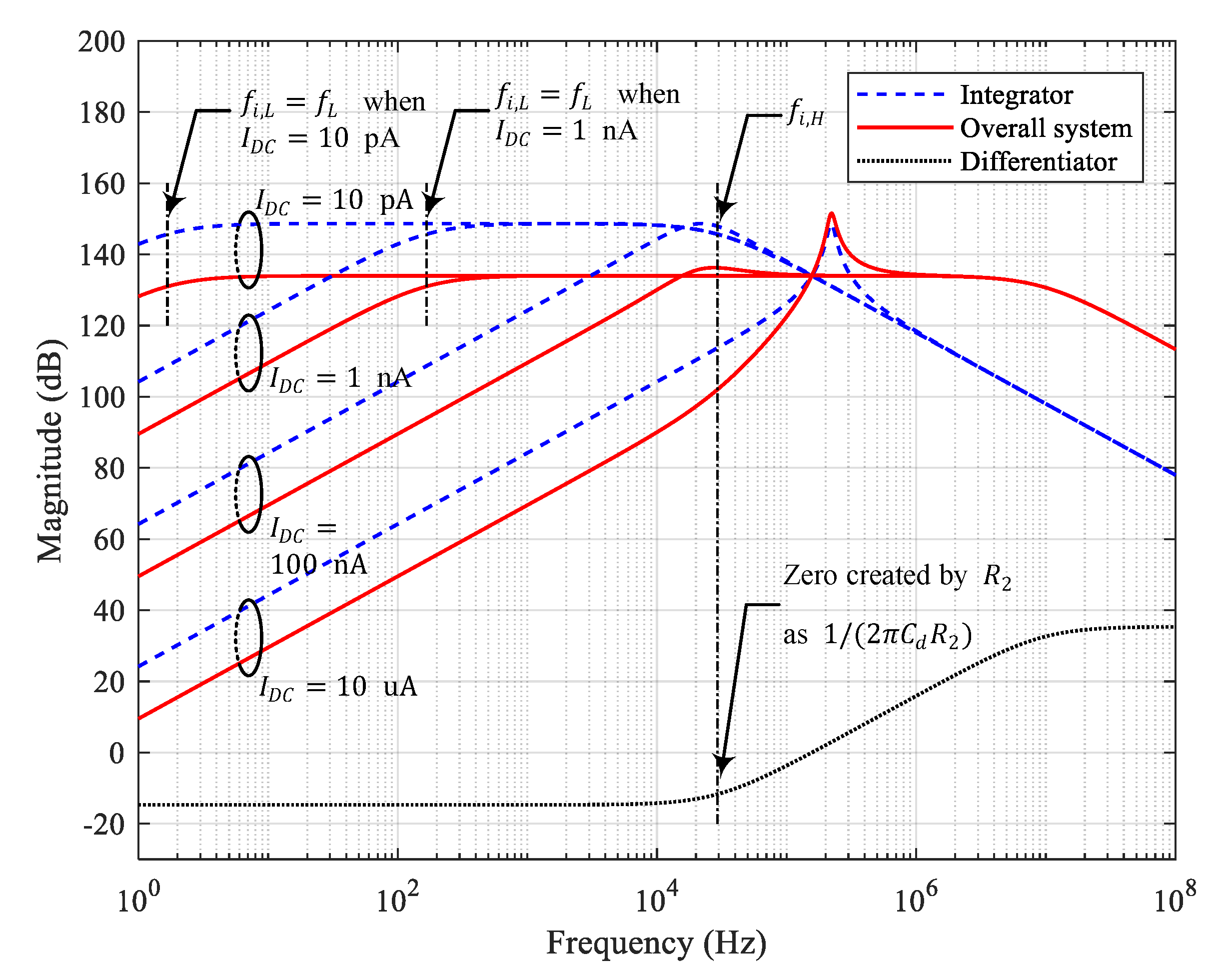

and

are shown in

Figure 3 for increasing

from 10 pA to 10 uA. Note that as

increases,

decreases. Eventually, a gain peaking occurs, as shown for

uA in

Figure 3.

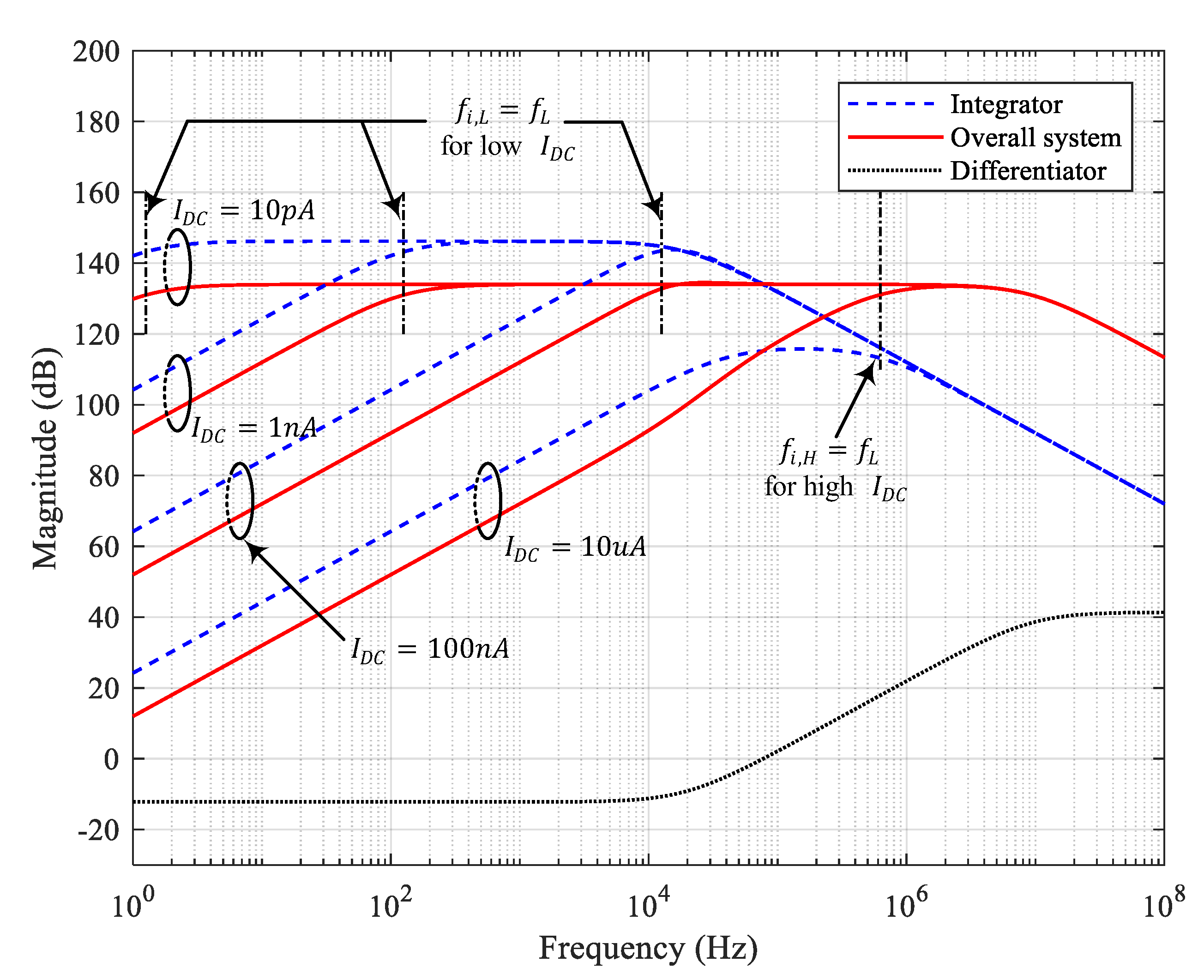

We can include the additional capacitor

parallel to

to ensure stability, regardless of the

value. In the presence of

, following the approaches in (

4) and (

5) gives

as

where

is the parameter that controls the value of

and system stability, such that

. The design parameters are then described as follows:

Then, the upper and lower frequencies of

are expressed in two cases depending on the amount of

. The first case is for a low

with

, and

The second case is for a high

with

, and

Notably,

is placed to generate a zero in

at

of (

16) as previously discussed.

Eventually, multiplying

of (

12) to

of (

13) renders

to the bandpass filter frequency response whose lower cutoff frequency is expressed as follows:

Note that the inclusion of

reduces the overall flat gain magnitude by a factor of

. To achieve the same flat gain magnitude that is exhibited when

is not included, either

or

should be multiplied by

. From the arithmetic-geometric mean inequality,

of (

14) has a lower bound of the following:

where equality holds when

. For

, the stability is always ensured by

, regardless of the

value, as in

Figure 4.

Noise performance analysis is presented in the remaining part of this section. The input-referred noise model is commonly used in noise analysis for comparing input signals and noise levels. In this topology, instead of the thermal noise of the resistor, the current noise of the transistor,

, is added to the typical root mean square (RMS) value of the input-referred noise expression of [

17] as follows:

where

is the inverting-input current noise of the op-amp, and

is the differential voltage noise of the op-amp. The noise

is the shot noise of

, where

and

q is the electron charge. Note that a flicker noise can be significant when implementing circuits with CMOS technology or using MOSFET instead of BJT in

. However, the flicker noise can be made negligible when assuming the broad range of signal bandwidth and using a non-minimal MOSFET area [

4].

The proposed CF-TIA shows better overall noise performance compared to that of the conventional CF-TIA when the dynamic range of is wide. For example, assume that the dynamic range of is 30 dB from 100 nA (normal ) to 100 uA (the expected maxima value of ). Because of the maximum , of the conventional CF-TIA is constrained to 50 kΩ where the supply voltage is 5 V. The maximum output voltage of the op-amp is assumed to be same as the supply voltage. Then, the thermal noise current of becomes 1 pA/ where k () is the Boltzmann constant and T (=300 K) is the absolute temperature.

This thermal noise current always exists even in normal degrading the overall noise performance. However, in the proposed CF-TIA, thermal noise current of the resistor is eliminated and the shot noise of a normal (=100 nA) becomes 0.17 pA , which is much lower than the thermal noise current of 1 pA/.

Furthermore, the noise of the proposed circuit is always less than that of the conventional CF-TIA implemented with CMOS, as in [

6,

7], in which the thermal noise and shot noise currents coexist. If the conventional CF-TIA is implemented with CMOS technology, the feedback resistor is implemented as a pseudo resistor with MOS devices. Therefore, the input-referred noise expression of conventional CMOS CF-TIA includes not only the thermal noise of feedback resistor, but also the shot noise of the MOS [

7]. However, (

20) has only the shot noise term without the thermal noise term.

Note that here

is associated with the noise contribution of the input capacitance term, the third term in (

20). Both the influence on the total noise and the overall system stability should be considered together when determining

.

3. SIMULATION and EXPERIMENT

The presented circuits were implemented and simulated using PSpice to verify the presented analyses of the transfer functions and design parameters. A photograph of the realized circuit is presented in

Figure 5. All the circuits were built using the same op-amp (OPA657, Texas Instruments). OPA657 has wideband and low-noise characteristics, and its

is 1.6 GHz,

is 75 dB at room temperature, and

of 5.2 pF. It is to be noted that

is not a trimmed parameter and can vary by the maximum

due to the process variation for any op-amp [

18]. Consequently, even though the datasheet specifies the

to be 1.6 GHz, I have considered

to be 1.28 GHz, about

of this typical value in order to account for process variations.

Note that to compare the simulation, experiment, and analytic results, all values of the discrete components were set equivalently as the assumed values in the analytical example shown in

Figure 4. Several variables were set by considering the laser position sensor application and its practical implementation. For the laser position sensor QP154-Q (First Sensor),

is assumed to be 20 pF. Taking the lowest value of the practical discrete capacitor,

is set to 0.2 pF. By using MMBT5179 NPN transistor (On Semiconductor) with low parasitic capacitance,

is set to 1 pF. The

value has an upper limit of approximately 1 nF because of the capacitive loading effect at the OPA657 output. In addition,

Figure 6 shows an example of the implementation of

for the simulation and experiment.

and

render the amplifier AC coupled to prevent

from being saturated with DC components. Given the aforementioned assumptions, the maximum achievable bandwidth was calculated as 9.3 MHz using (

1), and overall flat gain magnitude was determined to be

from (

2).

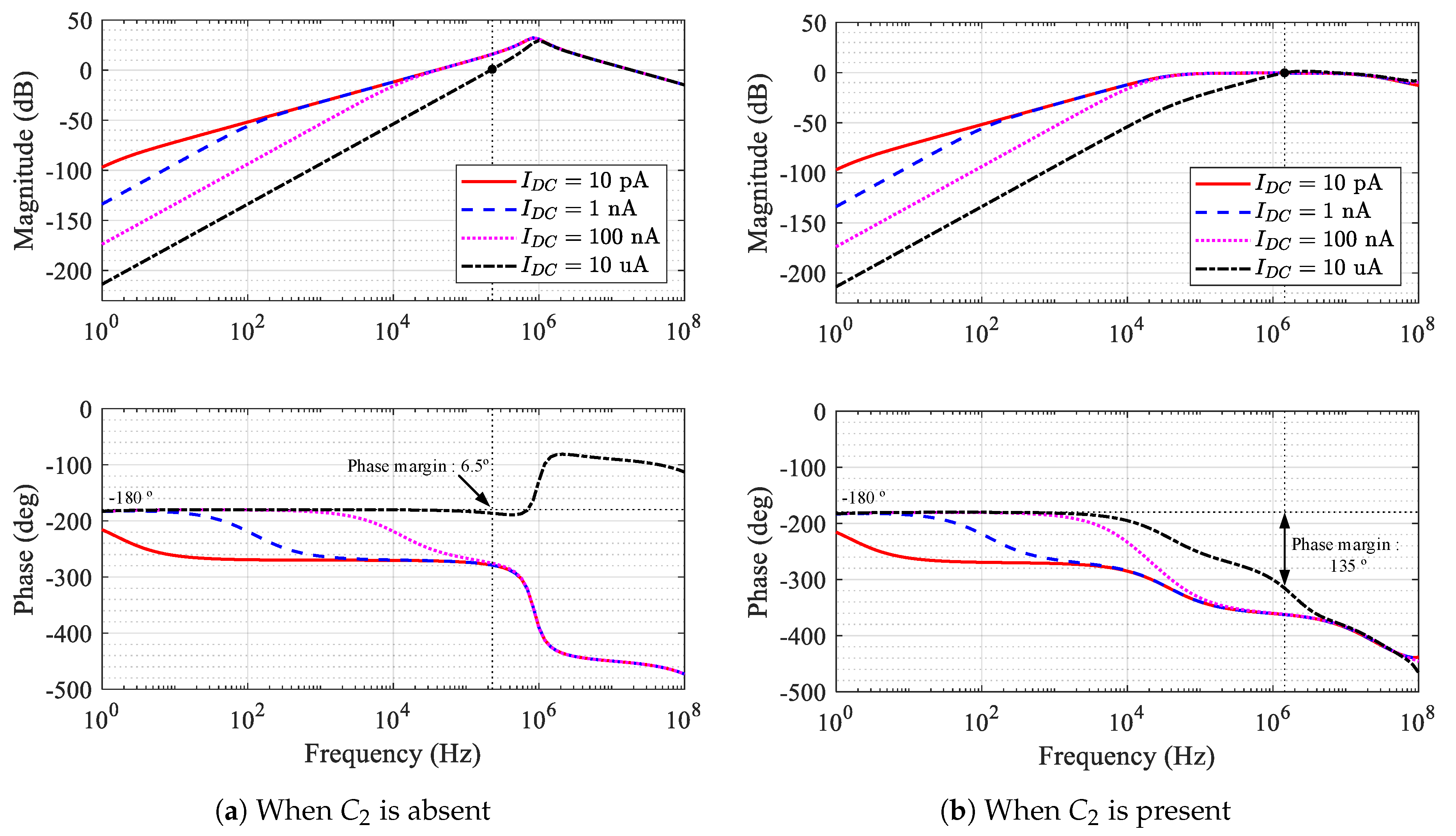

To assess the stability, the magnitude and phase of the loop gain were obtained through simulation, and plotted in

Figure 7.

Figure 7 shows the magnitude and phase of the loop gain of the integrator, depending on the presence or absence of

. For low

, although the phase at low frequencies is about −180°, the stability is ensured by a high gain margin. At high frequencies, the phase drops from −180°, resulting in a very high phase margin at the gain crossover point where the magnitude of the loop gain reaches unity-gain (0 dB). However, as

increases, the point at which the phase begins to drop increases significantly. Eventually, for

10 uA in

Figure 7a, the phase margin is meager at 6.5°, causing the system to become unstable. This result is consistent with the analysis result shown in

Figure 3, where the gain peaking occurs with

uA. In the presence of

, the zero is added before the gain crossover frequency. Thus, we can ensure enough phase margin with

. For

10 uA in

Figure 7b, the phase margin becomes 135°. This result is also consistent with the analysis result shown in

Figure 4, where the gain peaking is prevented on the presence of

with

uA.

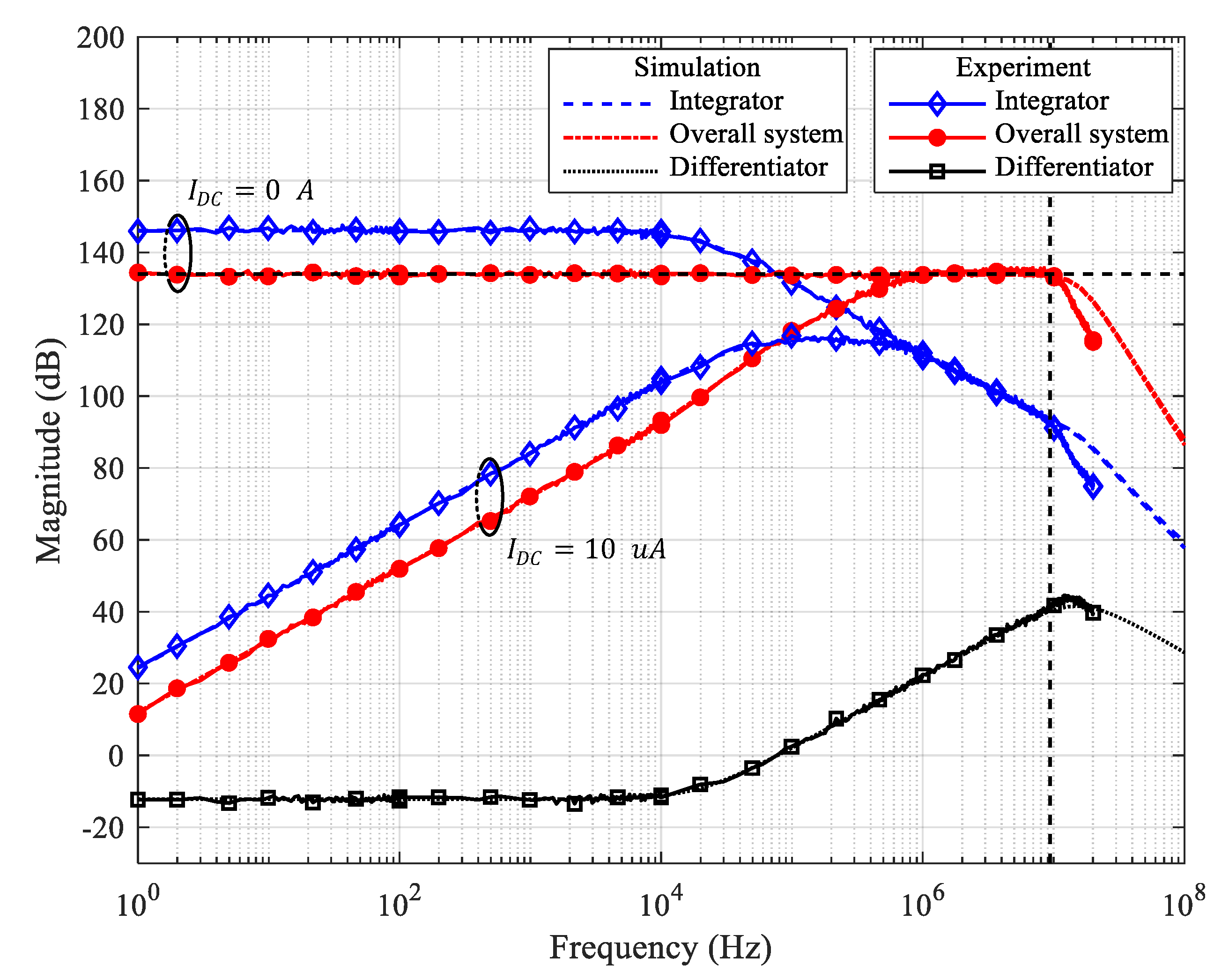

The frequency responses of the simulation and results of the experiment are shown in

Figure 8. The experimental results strongly agree with the simulation results as well as the analytical results of

Figure 4. The only difference is that the experimental results start to roll off at about

, slightly lower than the roll-off point of simulation results. There can be several reasons why this roll-off point in the measurement results is lower than that in the simulation results, such as additional input capacitance in the PCB layout and variations in the parameters of the circuit components. The major reason appears that the

of the op-amp used in the actual implementation is less than the ideal values recorded in the datasheet or the simulation model parameters due to the process variation [

16].