Thermal Drift Investigation of an SOI-Based MEMS Capacitive Sensor with an Asymmetric Structure

Abstract

:1. Introduction

2. Thermal Effect Analysis of an Asymmetric Structure

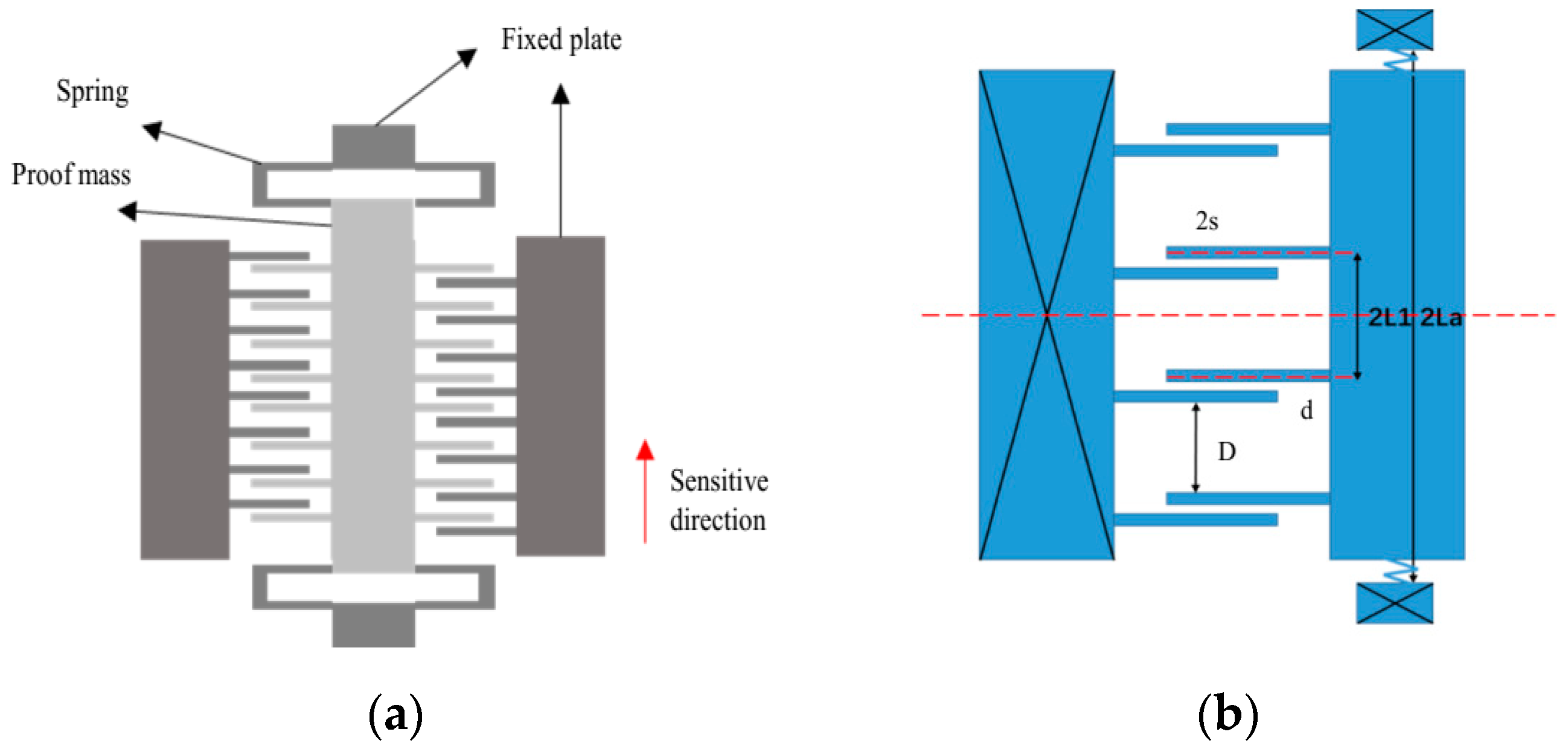

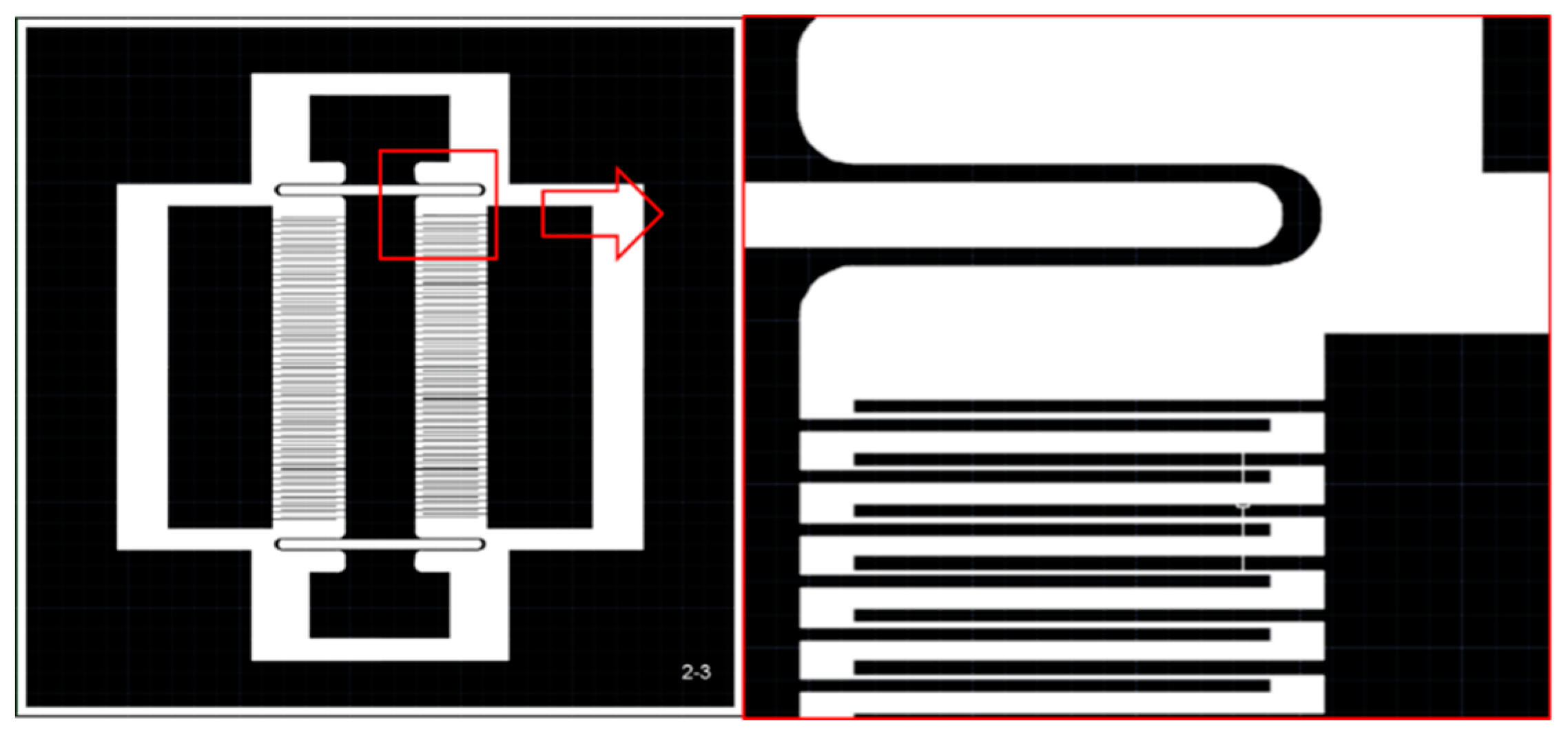

2.1. An Asymmetric Structure Model and Detection Principle

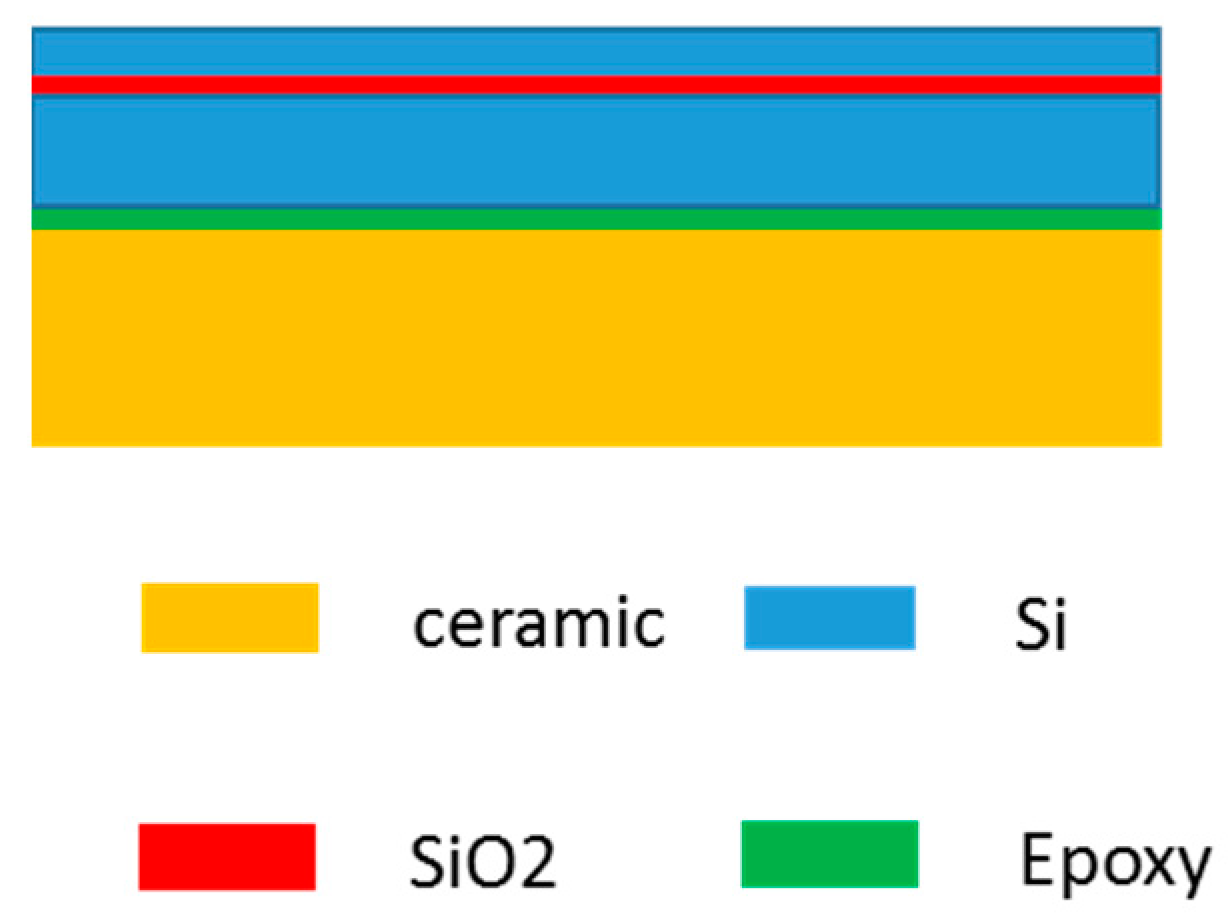

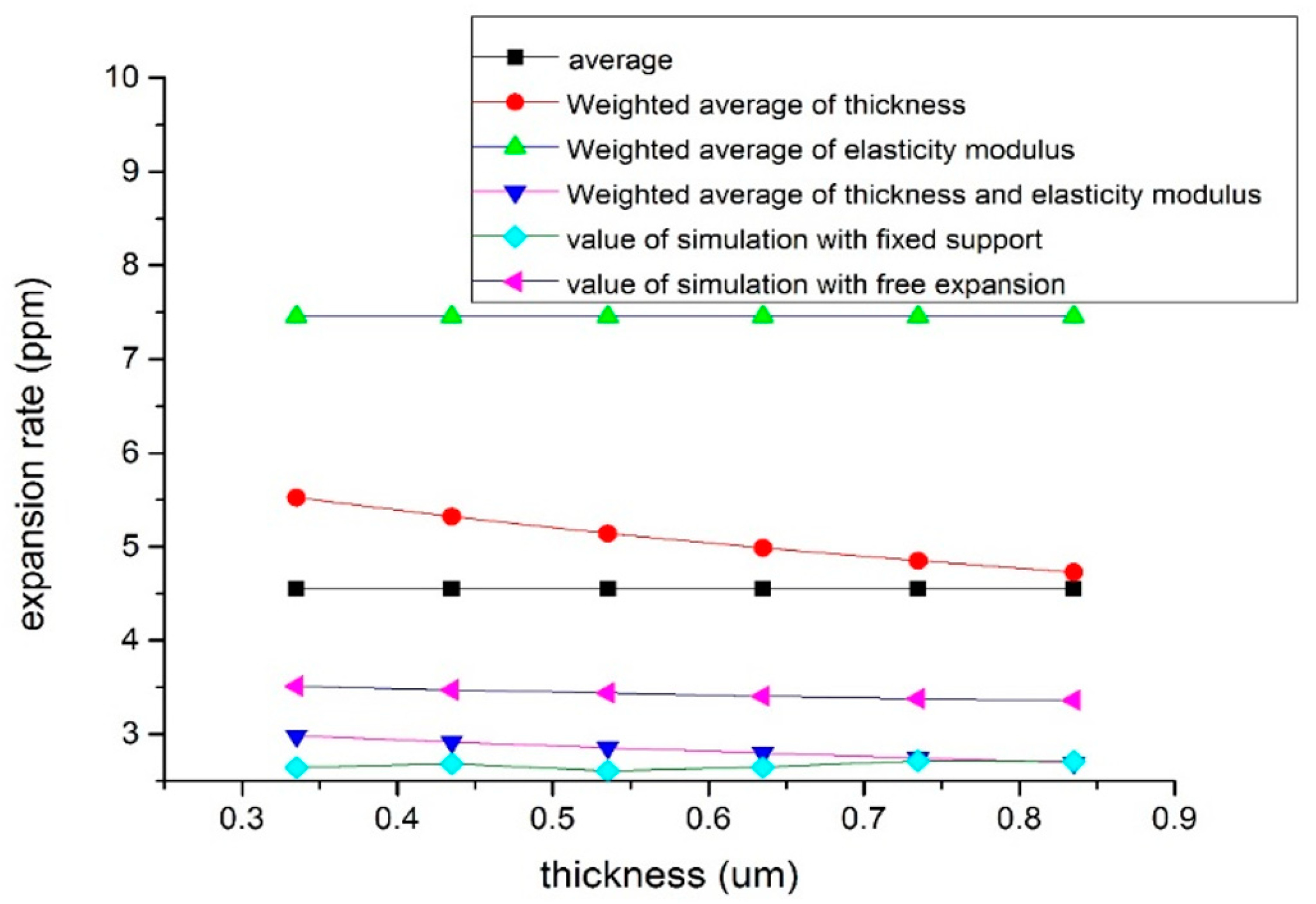

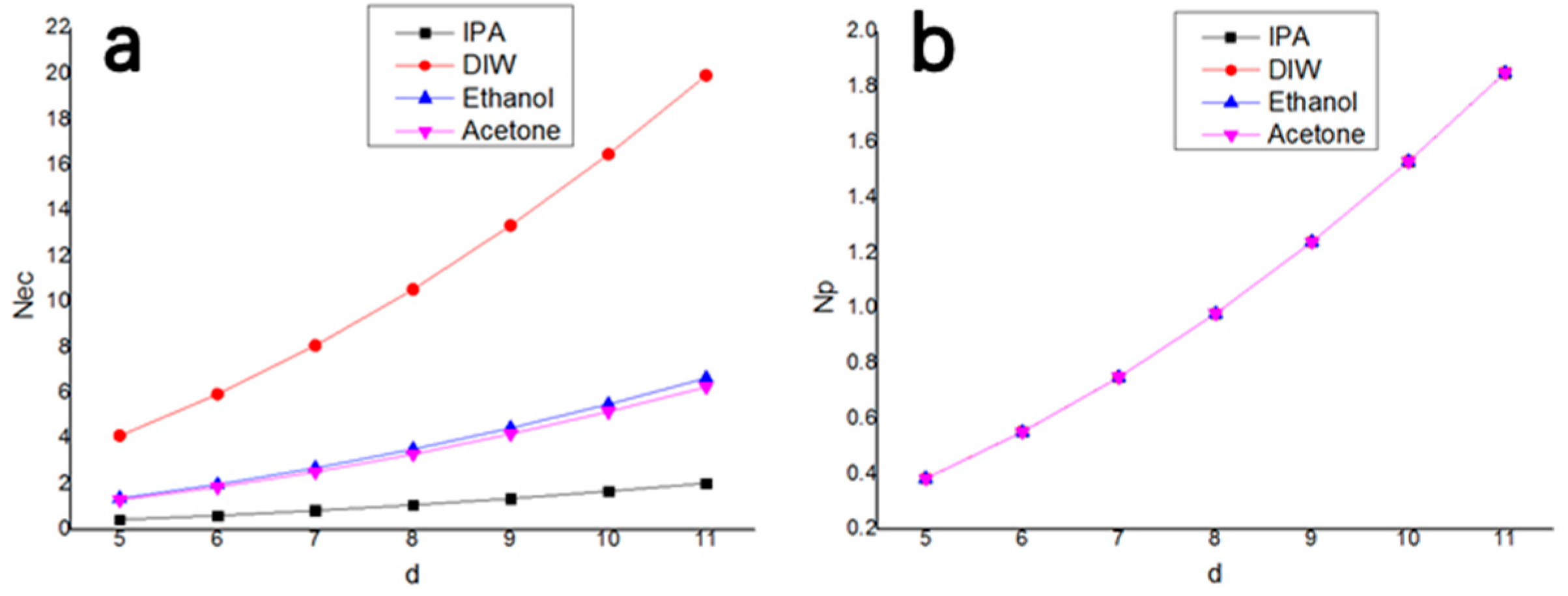

2.2. Analysis of Equivalent CTE

2.3. Analytical Formulas for TDB and TDSF of Asymmetric Structure

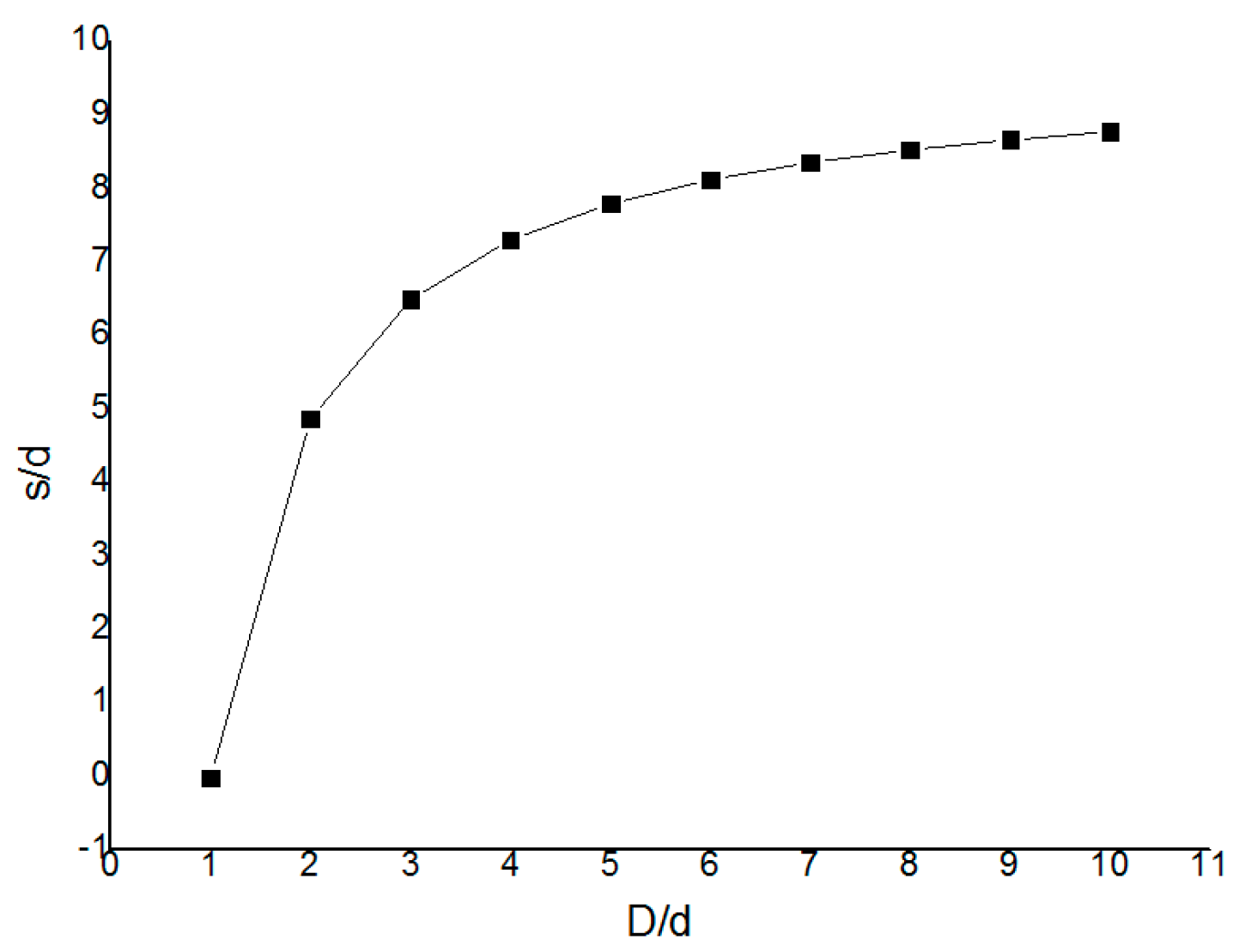

2.4. Optimal Dimensions for Asymmetric Structure

3. Experiment

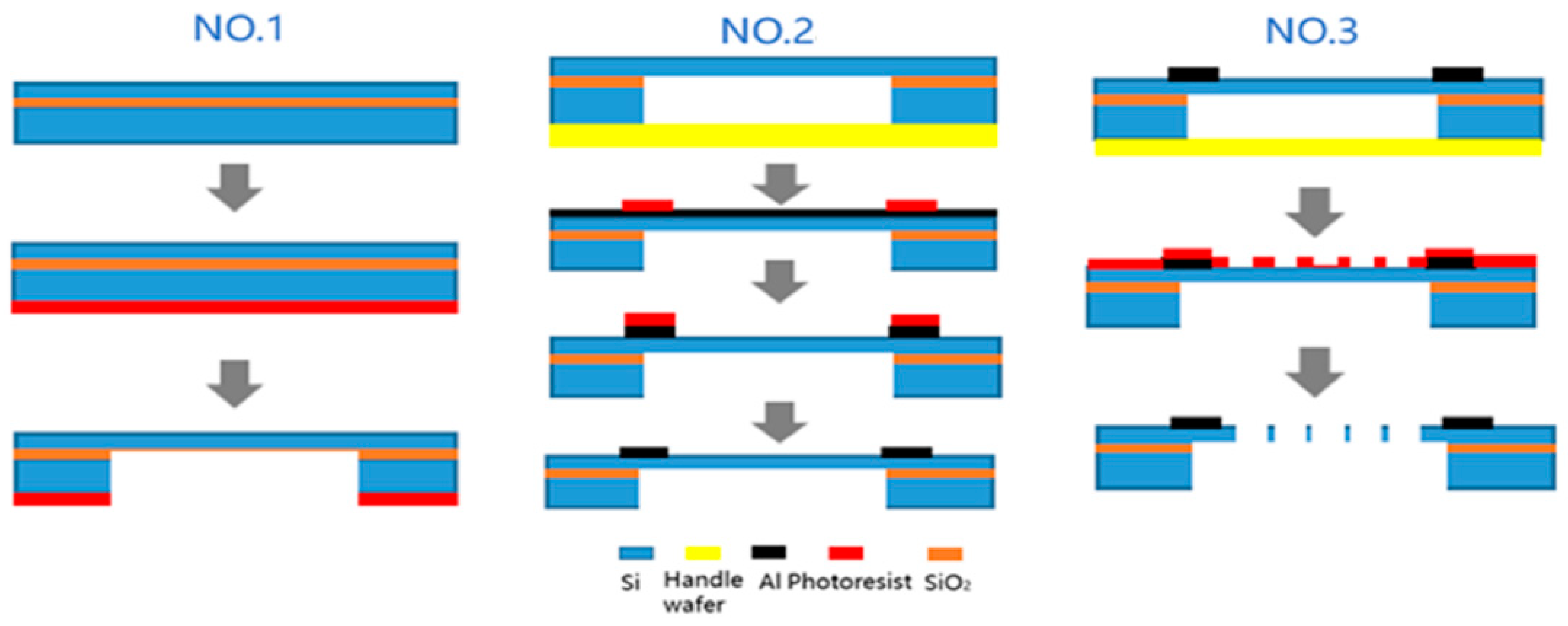

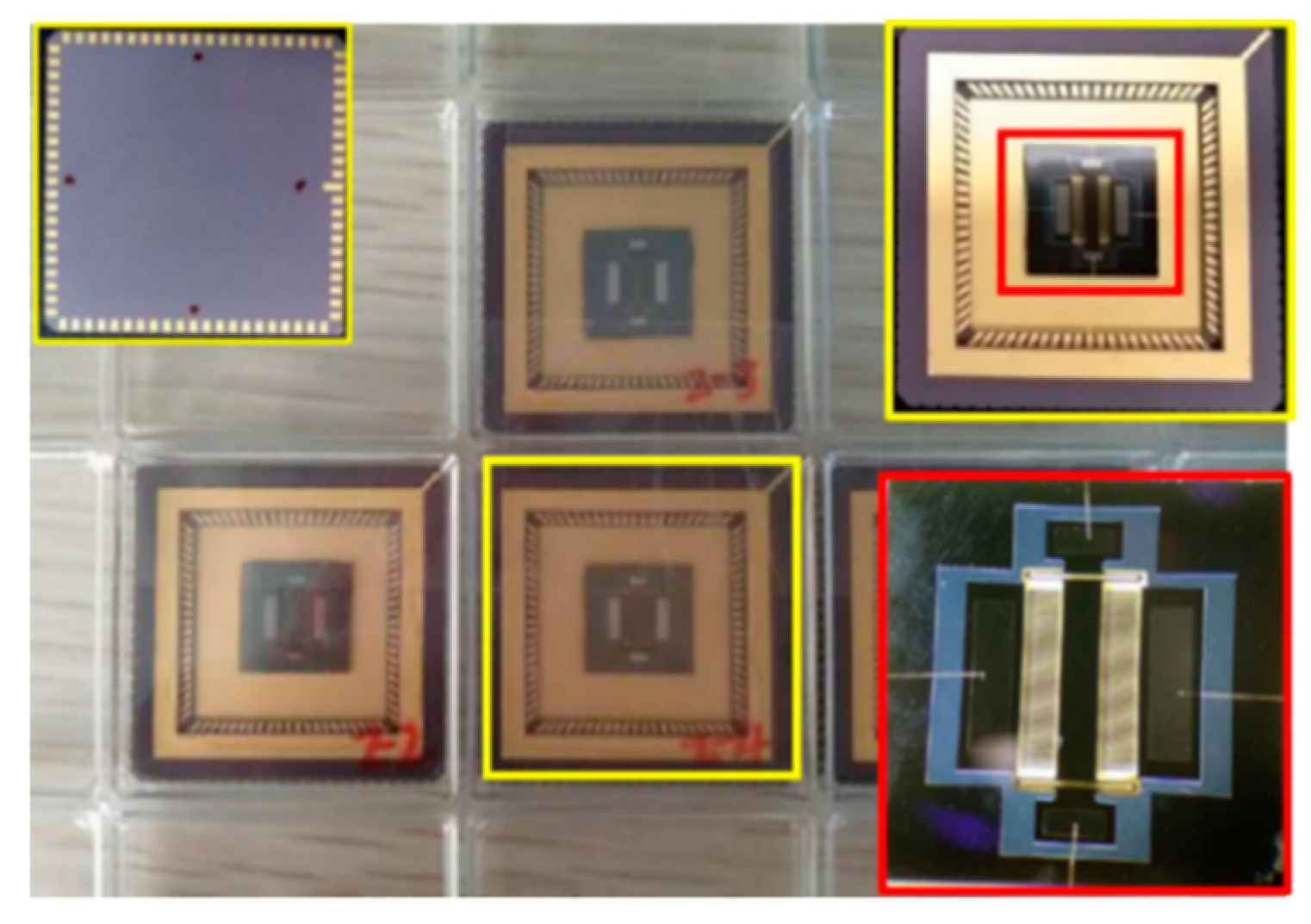

3.1. Fabrication Process

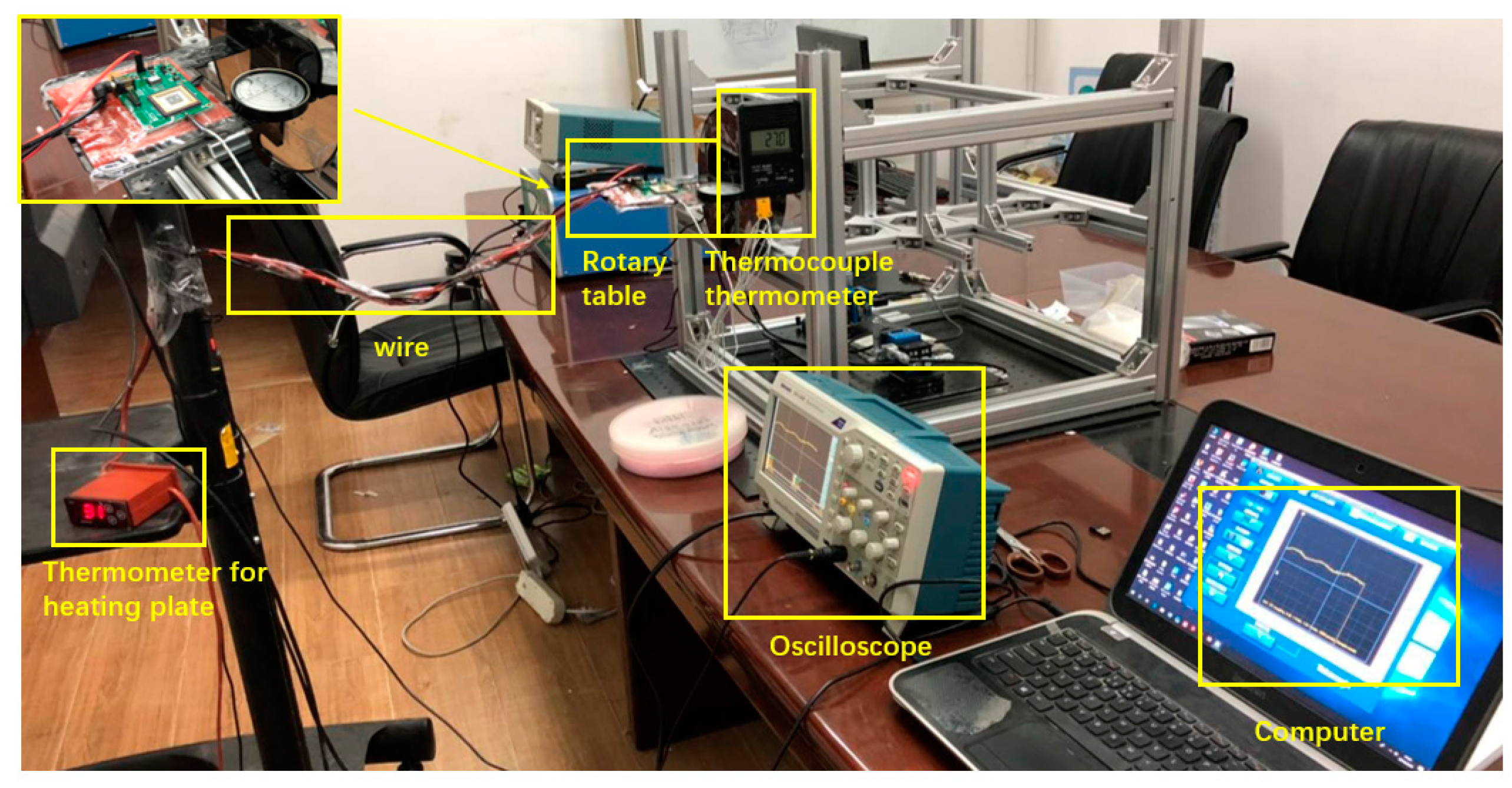

3.2. Testing Process

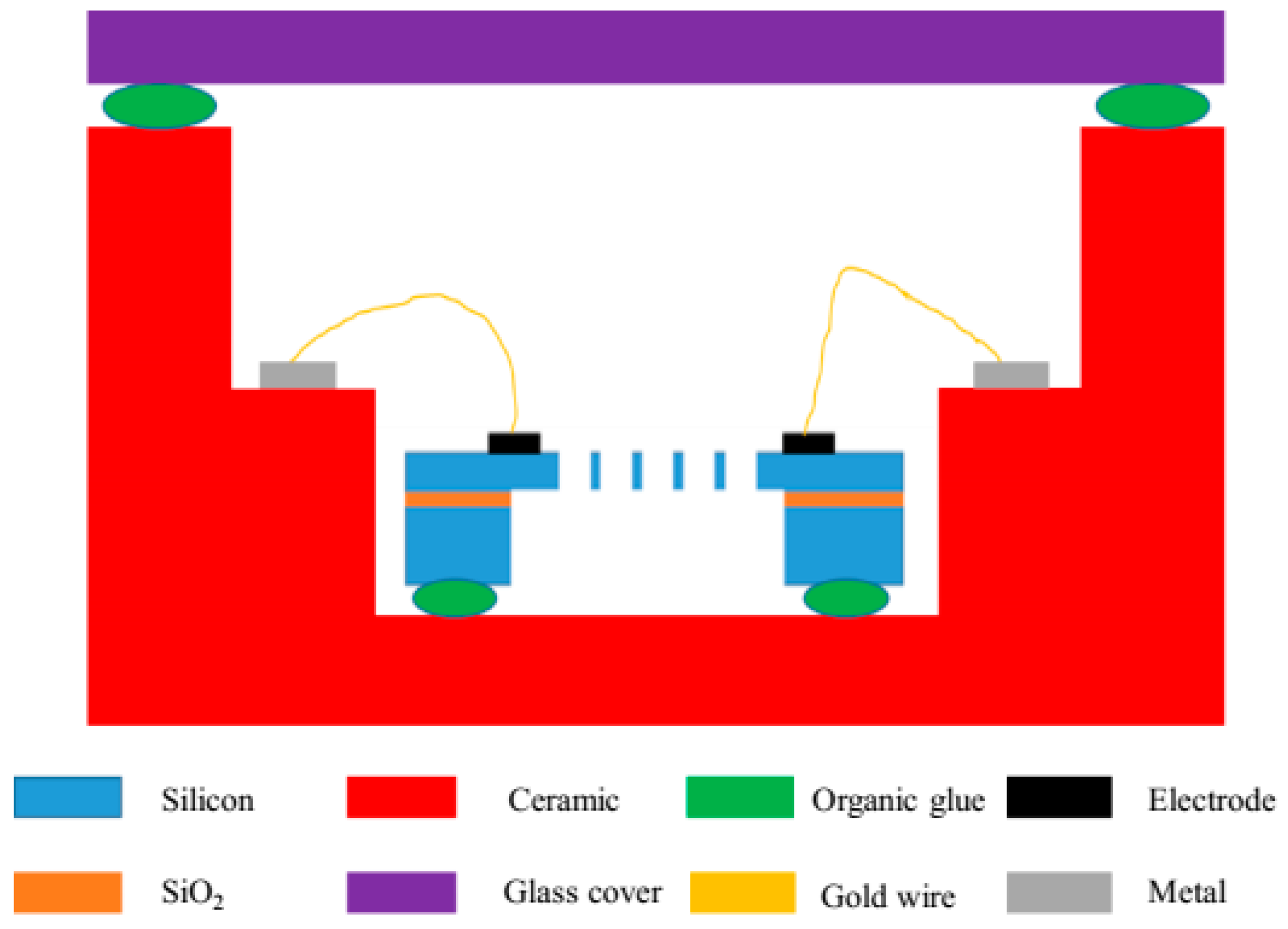

3.3. Package Method and Circuit Design

- (1)

- Tape casting and cutting;

- (2)

- Framing via punching, hole filling, and screen printing;

- (3)

- Lamination, snapping, block shaping, and co-firing;

- (4)

- Ni-plating and Au-plating.

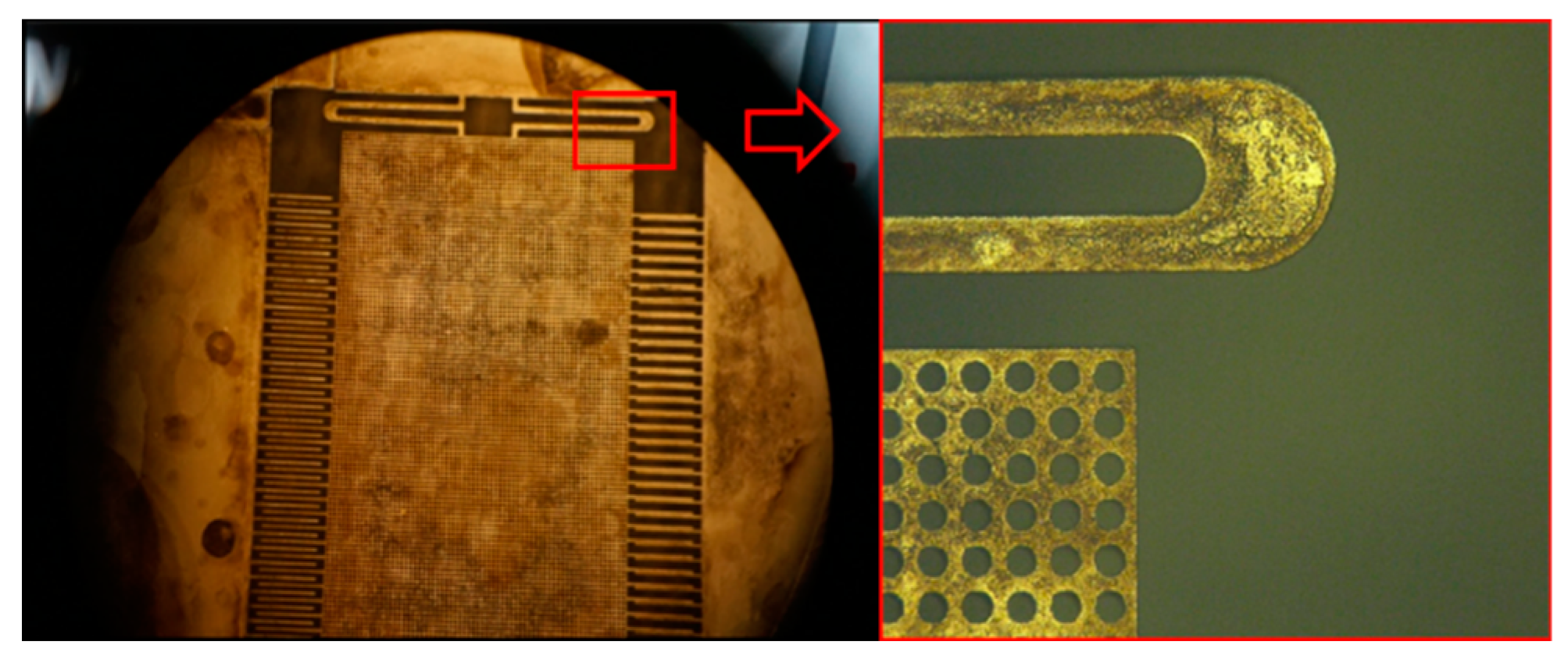

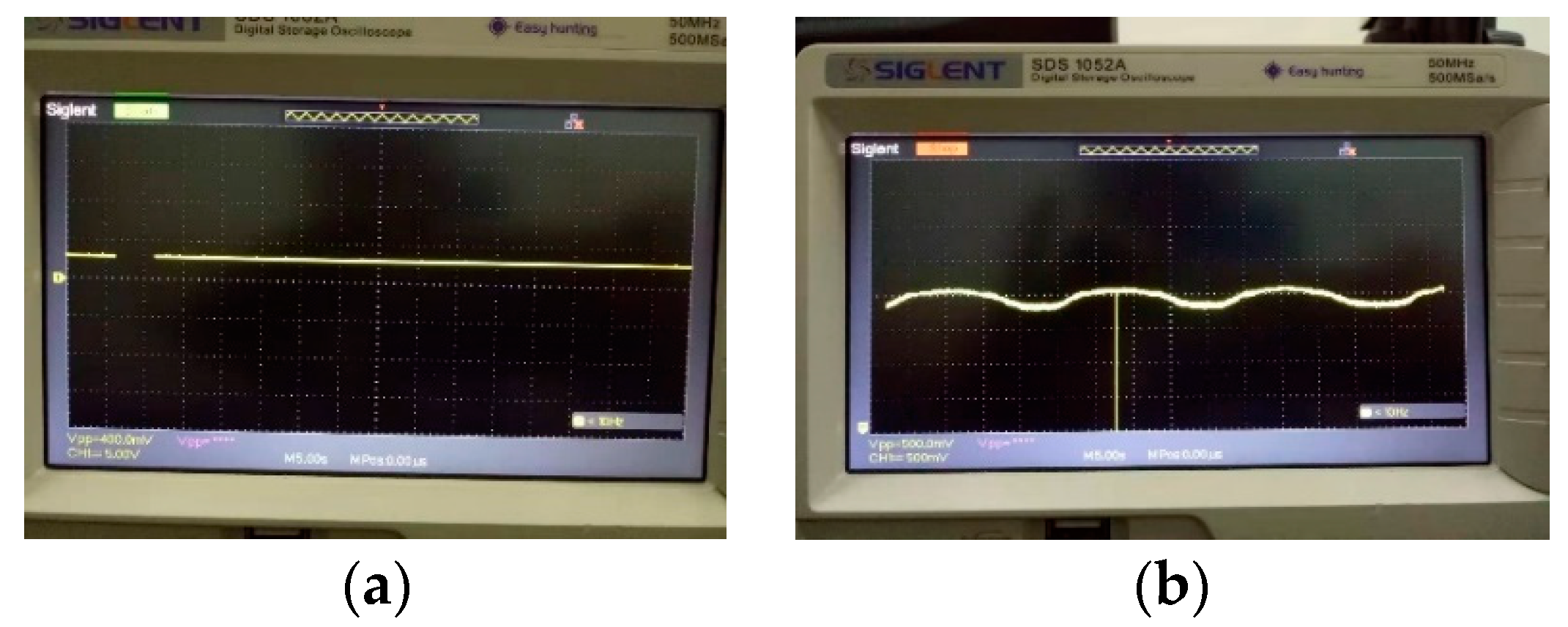

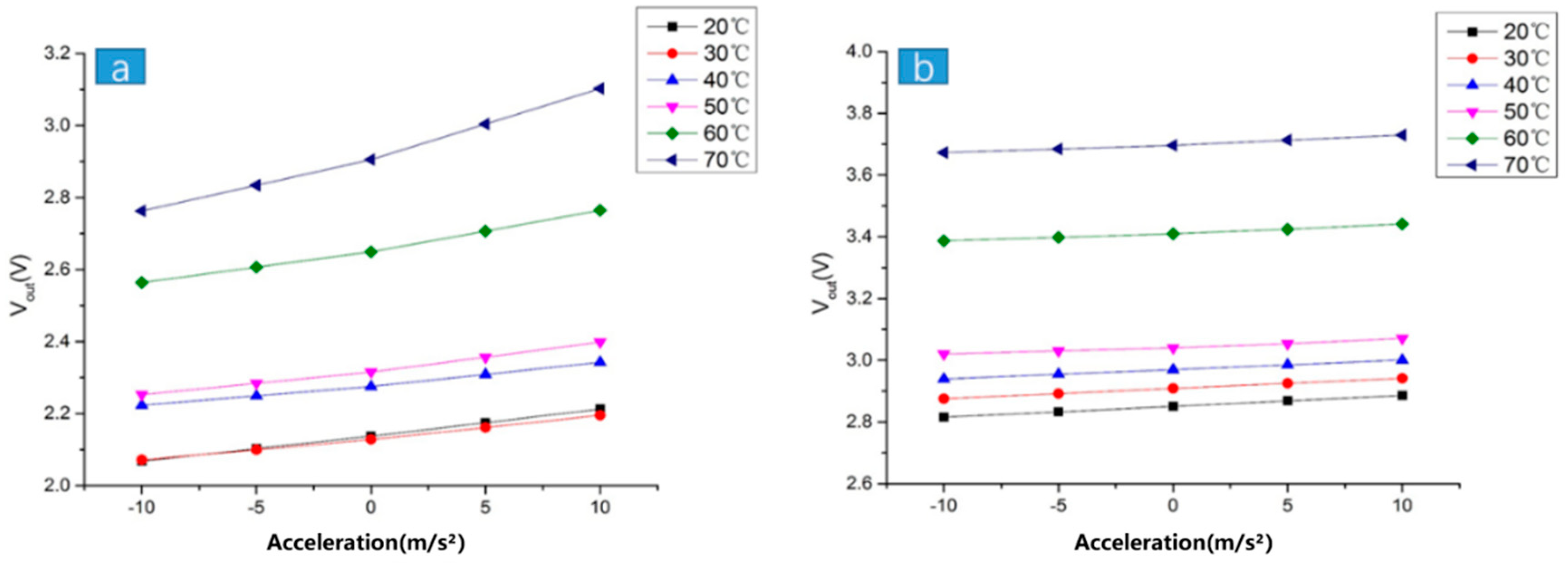

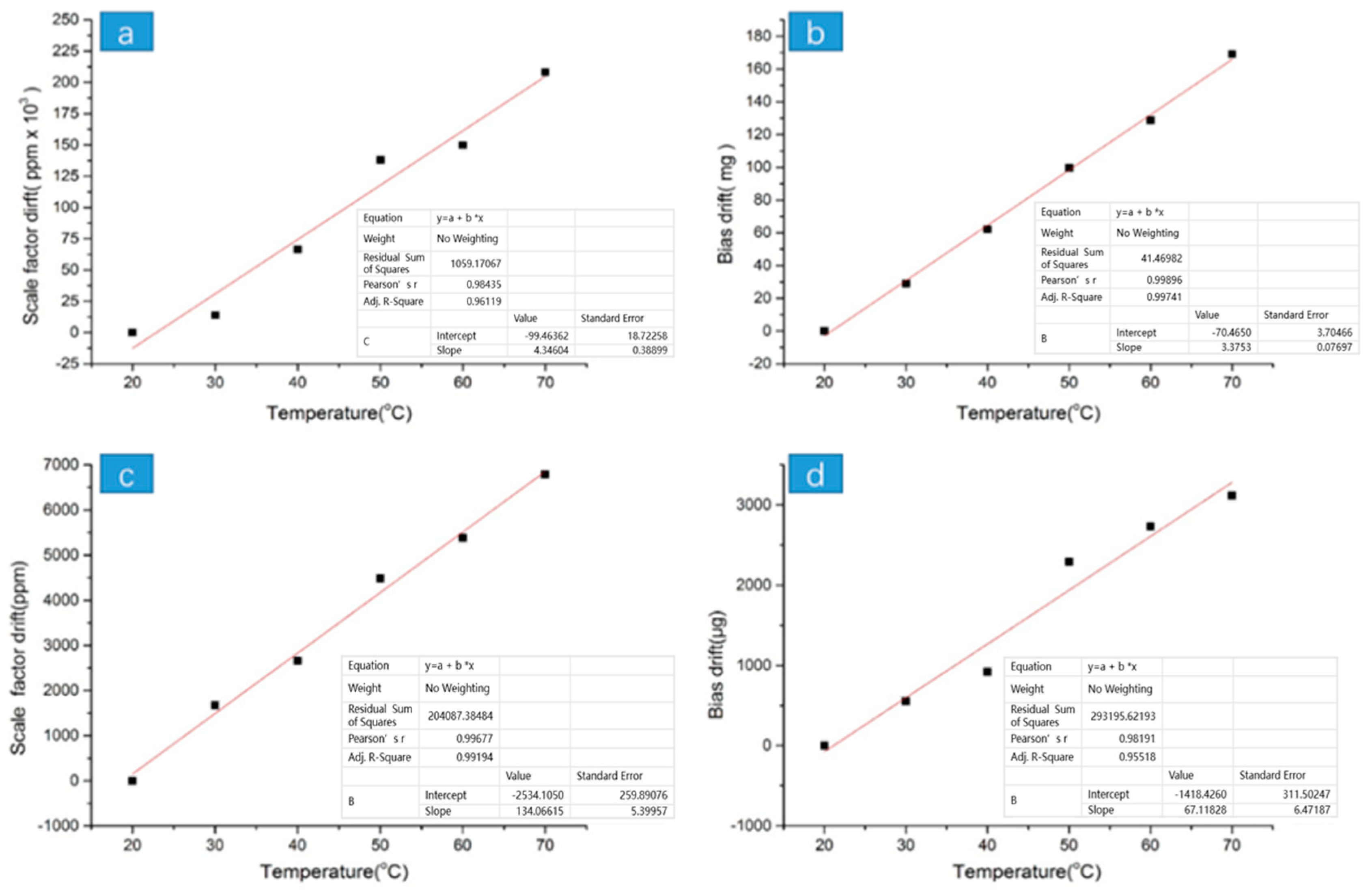

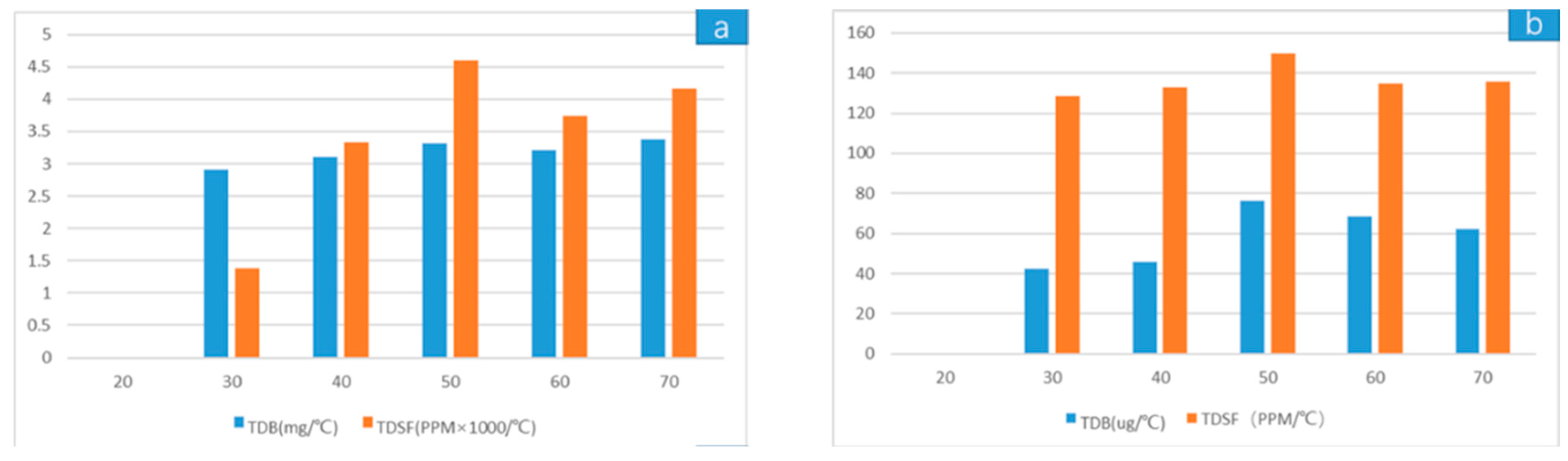

3.4. Experimental Device and Result

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Sethuramalingam, T.K.; Vimala Juliet, A. Design of MEMS based capacitive accelerometer. In Proceedings of the 2nd International Conference on Mechanical Electrical Technology (ICMET), Singapore, 10–12 September 2010; pp. 565–568. [Google Scholar] [CrossRef]

- Kun, L. Road Map of Micro Electro Mechanical System (MEMS) at US and MEMS Activities at LSU/CAMD; Academic Report 2002.7; Center for Advanced Microstructures and Devices Louisiana State University: Baton Rouge, LA, USA, 2002. [Google Scholar]

- Jiang, X.S.; Wang, F.Y.; Kraft, M.; Boser, B.E. An integrated surface micromachined capacitive lateral accelerometer with 2 μg/ resolution. In Proceedings of the Solid-State Sensor, Actuator and Microsystems Workshop, Hilton Head Island, SC, USA, 2–6 June 2002. [Google Scholar]

- Yazdi, N.; Najafi, K. An all-silicon single-wafer micro-g accelerometer with a combined surface and bulk micromachining process. J. Microelectro-Mech. Syst. 2000, 9, 544–550. [Google Scholar] [CrossRef]

- Monajemi, P.; Ayazi, F. Design optimization and implementation of a microgravity capacitive HARPSS accelerometer. IEEE Sens. J. 2006, 6, 39–46. [Google Scholar] [CrossRef]

- Aydin, O.; Akin, T. A bulk micromachined fully-differential MEMS accelerometer with interdigitated fingers. In Proceedings of the Sensors, 2012 IEEE, Taipei, Taiwan, 28–31 October 2012. [Google Scholar]

- Zwahlen, P.; Dong, Y.; Nguyen, A.M.; Rudolf, F.; Stauffer, J.M.; Ullah, P.; Ragot, V. Breakthrough in high performance inertial navigation grade Sigma-Delta MEMS accelerometer. In Proceedings of the 2012 IEEE/ION, Position Location and Navigation Symposium (PLANS), Myrtle Beach, SC, USA, 23–26 April 2012; pp. 15–19. [Google Scholar]

- Liu, M.; Chi, B.; Liu, Y.; Dong, J. A closed-loop MEMS accelerometer with capacitive sensing interface ASIC. Int. J. Electron. 2013, 100, 21–35. [Google Scholar] [CrossRef]

- Leland, P.R. Mechanical-thermal noise in MEMS gyroscopes. IEEE Sens. J. 2005, 5, 493–500. [Google Scholar] [CrossRef]

- Tang, Q.J.; Wang, X.J.; Yang, Q.P.; Liu, C.Z. Static temperature analysis and compensation of MEMS gyroscopes. Int. J. Metrol. Qual. Eng. 2013, 4, 209–214. [Google Scholar] [CrossRef]

- Annovazzi-Lodi, V.; Merlo, S. Mechanical–thermal noise in micromachined gyros. Microelectron. J. 1999, 30, 1227–1230. [Google Scholar] [CrossRef]

- Tan, S.S.; Liu, C.Y.; Yeh, L.K.; Chiu, Y.H.; Hsu, K.Y.J. Design of low-noise CMOS MEMS accelerometer with techniques for thermal stability and stable DC biasing. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–22 September 2010; IEEE: Piscataway, NJ, USA, 2010. [Google Scholar]

- Dong, Y.; Zwahlen, P.; Nguyen, A.M.; Frosio, R.; Rudolf, F. Ultra-high precision MEMS accelerometer. In Proceedings of the IEEE Conference on Solid-State Sensors, Actuators and Microsystems, Beijing, China, 5–9 June 2011; pp. 695–698. [Google Scholar]

- Wei, T.A.; Khosla, P.K.; Riviere, C.N. Nonlinear regression model of a Low-g MEMS accelerometer. IEEE Sens. J. 2007, 7, 81–88. [Google Scholar]

- Li, B.; Lu, D.; Wang, W. Micromachined accelerometer with area-changed capacitance. Mechatronics 2001, 11, 811–819. [Google Scholar] [CrossRef]

- Dai, G.; Li, M.; He, X.; Du, L.; Shao, B.; Su, W. Thermal drift analysis using a multiphysics model of bulk silicon MEMS capacitive accelerometer. Sens. Actuators A Phys. 2011, 172, 369–378. [Google Scholar] [CrossRef]

- Bahari, J.; Feng, R.; Leung, A.M. Robust MEMS gyroscope based on thermal principles. J. Microelectromech. Syst. 2014, 15, 100–116. [Google Scholar] [CrossRef]

- He, J.; Xie, J.; He, X.; Du, L.; Zhou, W. Analytical study and compensation for temperature drifts of a bulk silicon MEMS capacitive accelerometer. Sens. Actuators A Phys. 2016, 239, 174–184. [Google Scholar] [CrossRef]

- He, J.; Zhou, W.; Yu, H.; He, X.; Peng, P. Structural designing of a MEMS capacitive accelerometer for low temperature coefficient and high linearity. Sensors 2018, 18, 643. [Google Scholar] [CrossRef] [PubMed]

- Schröder, S.; Nafari, A.; Persson, K.; Westby, E.; Fischer, A.C.; Stemme, G.; Niklaus, F.; Haasl, S. Stress-minimized packaging of inertial sensors using wire bonding. In Proceedings of the IEEE Transducers & Eurosensors XXVII: The, International Conference on Solid-State Sensors, Actuators and Microsystems, Barcelona, Spain, 16–20 June 2013; pp. 1962–1965. [Google Scholar]

- Zhang, Y.; Gao, C.; Meng, F.; Hao, Y. A SOI sandwich differential capacitance accelerometer with low-stress package. In Proceedings of the IEEE International Conference on Nano/micro Engineered and Molecular Systems, Waikiki Beach, HI, USA, 13–16 April 2014; pp. 341–345. [Google Scholar]

- Geisberger, A.; Schroeder, S.; Dixon, J.; Suzuki, Y.; Makwana, J.; Qureshi, S. A high aspect ratio MEMS process with surface micromachined polysilicon for high accuracy inertial sensing. In Proceedings of the IEEE Transducers & Eurosensors Xxvii: The, International Conference on Solid-State Sensors, Actuators and Microsystems, Barcelona, Spain, 16–20 June 2013; pp. 18–21. [Google Scholar]

- Ko, H. Highly programmable temperature compensated readout circuit for capacitive micro accelerometer. Sens. Actuators A Phys. 2010, 158, 72–83. [Google Scholar] [CrossRef]

- Falconi, C.; Fratini, M. CMOS microsystems temperature control. Sens. Actuators B Chem. 2008, 129, 59–66. [Google Scholar] [CrossRef]

- Raccurt, O.; Tardif, F.; d’Avitaya, F.A.; Vareine, T. Influence of liquid surface tension on stiction of SOI MEMS. J. Micromech. Microeng. 2004, 14, 1083–1090. [Google Scholar] [CrossRef]

- Xu, T.; Tao, Z.; Tan, X.; Li, H. The control method of surface morphology and etch rates for silicon etch process with extremely deep and high aspect ratio. In Proceedings of the Asme International Conference on Micro/Nanoscale Heat and Mass Transfer, Singapore, 4–6 January 2016; p. V002T07A005. [Google Scholar]

- Tan, X.; Tao, Z.; Yu, M.; Wu, H.; Li, H. Anti-reflectance investigation of a micro-nano hybrid structure fabricated by dry/wet etching methods. Sci. Rep. 2018, 8, 7863. [Google Scholar]

- Tan, X.; Tao, Z.; Yu, M.; Wu, H.; Li, H. Anti-reflectance optimization of secondary nanostructured black silicon grown on micro-structured arrays. Micromachines 2018, 9, 385. [Google Scholar] [CrossRef] [PubMed]

| Materials | Silicon | Ceramic | Epoxy | SiO2 |

|---|---|---|---|---|

| Elasticity modulus () | 190 | 400 | 2.5 | 170 |

| Thickness () | 335~835 | 1000 | 4 | 1 |

| CTE (ppm/°C) | 2.6 | 6.5 | 60 | 0.8 |

| Poisson’s ratio | 0.28 | 0.22 | 0.38 | 0.16 |

| Property | Value | Units | Property | Value | Units |

|---|---|---|---|---|---|

| Folded beam width () | 15 | Width of the proof mass () | 2100 | ||

| Folded beam length () | 1000 | Length of the proof mass () | 6020 | ||

| Folded beam height () | 35 | Height of the proof mass () | 35 | ||

| Narrow capacitive gap () | 10 | Width of the electrode () | 30 | ||

| Wide capacitive gap () | 50 | Length of the electrode () | 900 | ||

| Length of the chip () | 10000 | Height of the electrode () | 35 | ||

| Width of the chip () | 10000 | Number of fixed electrodes | 28 | - |

| Process Number | Process step | Operation |

|---|---|---|

| NO.1 | Wafer Cleaning | Clean and dry the SOI wafer |

| Photoresist coating | AZ4620, 3000 rpm, 50 s | |

| Pre-baking | 95 °C, 60 min | |

| Exposure | TSK, 13 s | |

| Development | AZ400k: H2O = 1:3, 2 min | |

| Post-baking | 95 °C, 30 min | |

| Etching | Etch protection ratio is 8:5–9:5, 300 μm | |

| Removal of photoresist | Piranha | |

| Removal of SiO2 | HF | |

| NO.2 | Handle wafer | 500 μm wafer at the bottom of SOI |

| Sputtering | Direct target sputtering, Al, 300 s + 600 s | |

| Photoresist coating | S1813, 3000 rpm, 50 s, remove handle wafer | |

| Pre-baking | 115 °C, 30 min | |

| Exposure | BSK, 3 s | |

| Development | NMD-3, 2 min | |

| Post-baking | 115 °C, 15 min | |

| Corrosion | HF: Deionized water = 1:10, ≤1 min | |

| Removal of photoresist | Acetone, ultrasonic | |

| NO.3 | Photoresist coating | S1813, 3000 rpm, 50 s, remove handle wafer |

| Pre-baking | 115 °C, 30 min | |

| Exposure | BSK, 3 s | |

| Development | NMD-3, 2 min | |

| Exposure | BSK, 3 s | |

| Development | NMD-3, 2 min | |

| Etching | Etch protection ratio is 8:5, 25 μm | |

| Removal of photoresist | Acetone |

| Vref-Up | Vref-Bottom | Vref-Left | Vref-Right |

|---|---|---|---|

| 2.280928 | 2.280896 | 2.280768 | 2.280640 |

| Range | 0.000288 | Relative error | 0.012632% |

| TDB | TDSF | |||||

|---|---|---|---|---|---|---|

| Absolute Value | Absolute Stability | Relative Stability | Absolute Value | Absolute Stability | Relative Stability | |

| Before packaging | 3 mg/°C | 0.47 mg/°C | 14.93% | 3000 ppm/°C | 3210 ppm/°C | 93.20% |

| After packaging | 60 μg/°C | 33.69 μg/°C | 57.016% | 140 ppm/°C | 20.97 ppm/°C | 15.38% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, H.; Zhai, Y.; Tao, Z.; Gui, Y.; Tan, X. Thermal Drift Investigation of an SOI-Based MEMS Capacitive Sensor with an Asymmetric Structure. Sensors 2019, 19, 3522. https://doi.org/10.3390/s19163522

Li H, Zhai Y, Tao Z, Gui Y, Tan X. Thermal Drift Investigation of an SOI-Based MEMS Capacitive Sensor with an Asymmetric Structure. Sensors. 2019; 19(16):3522. https://doi.org/10.3390/s19163522

Chicago/Turabian StyleLi, Haiwang, Yanxin Zhai, Zhi Tao, Yingxuan Gui, and Xiao Tan. 2019. "Thermal Drift Investigation of an SOI-Based MEMS Capacitive Sensor with an Asymmetric Structure" Sensors 19, no. 16: 3522. https://doi.org/10.3390/s19163522

APA StyleLi, H., Zhai, Y., Tao, Z., Gui, Y., & Tan, X. (2019). Thermal Drift Investigation of an SOI-Based MEMS Capacitive Sensor with an Asymmetric Structure. Sensors, 19(16), 3522. https://doi.org/10.3390/s19163522