Fabrication Technology and Characteristics of a Magnetic Sensitive Transistor with nc-Si:H/c-Si Heterojunction

Abstract

:1. Introduction

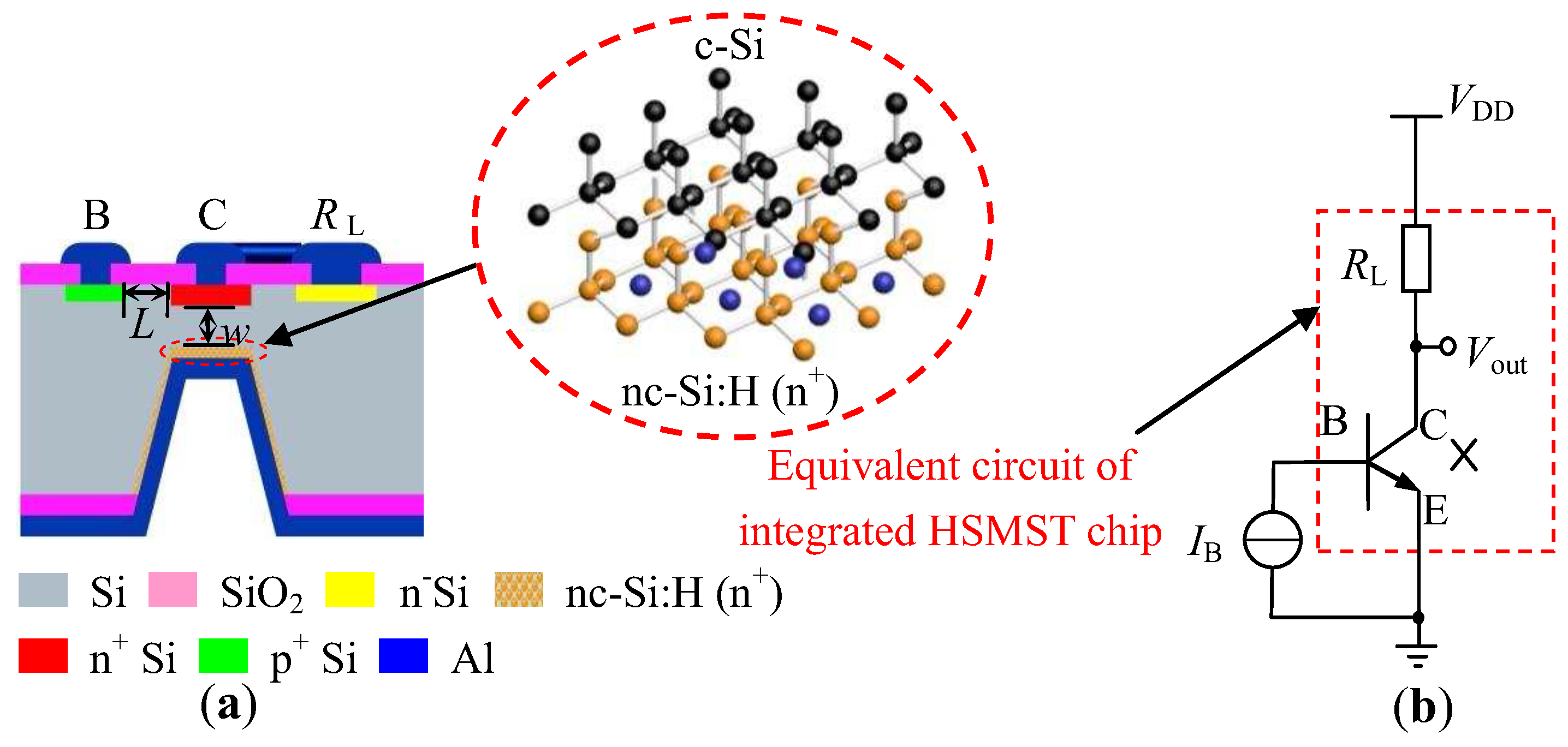

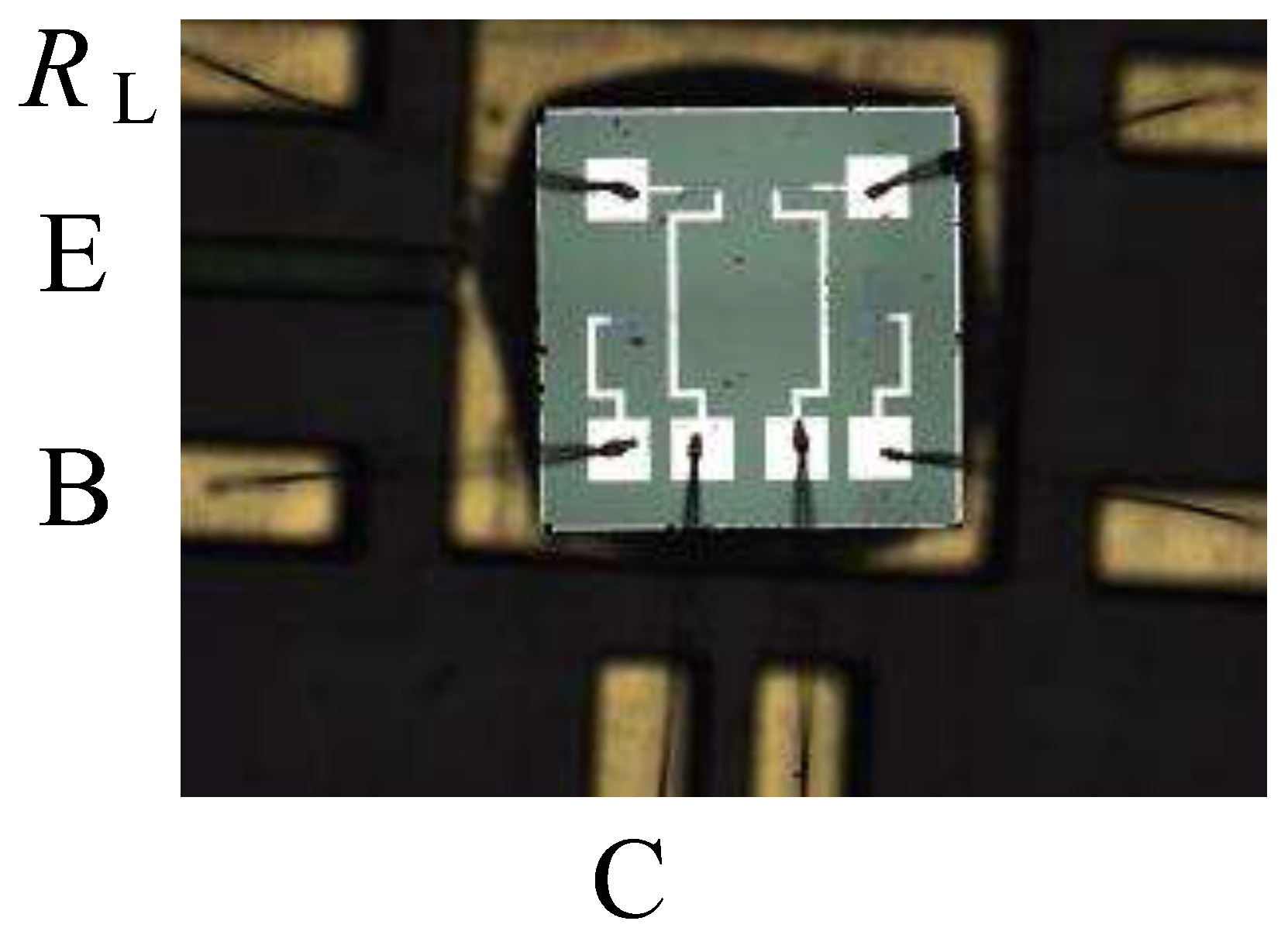

2. Basic Structure and Operating Principle

2.1. Basic Structure

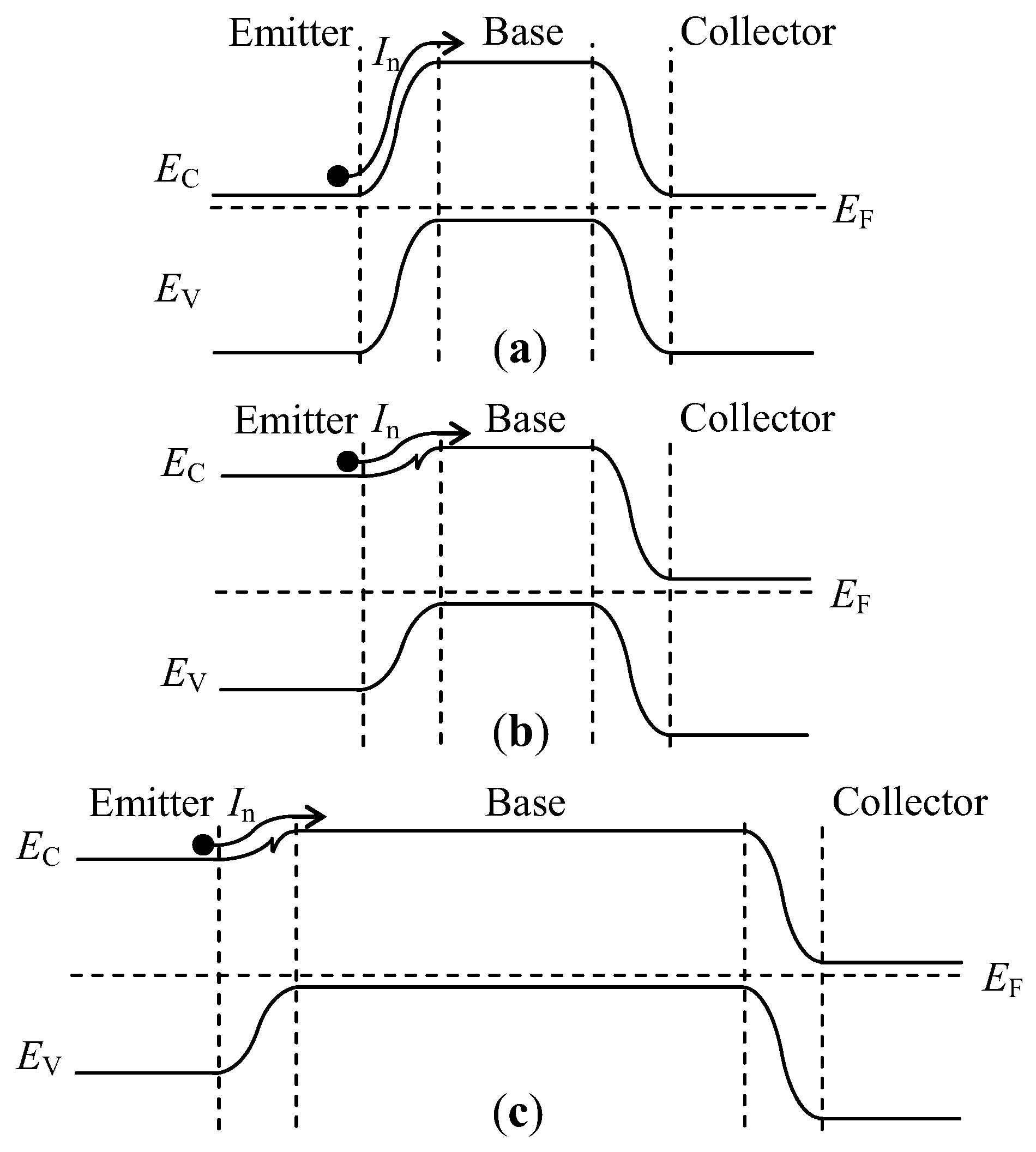

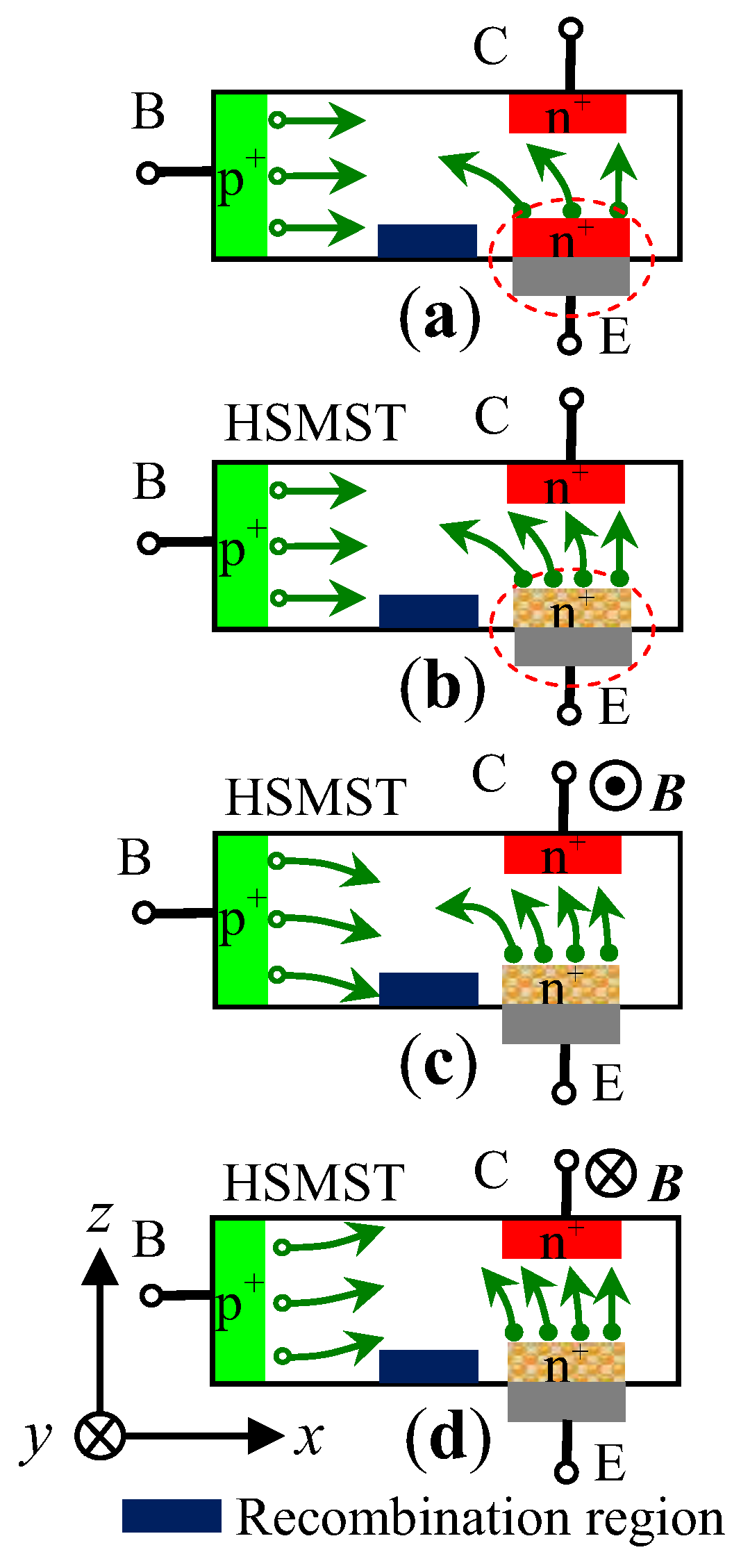

2.2. Operating Principle

2.2.1. Heterojunction Transistor

2.2.2. Magnetic Sensitivity

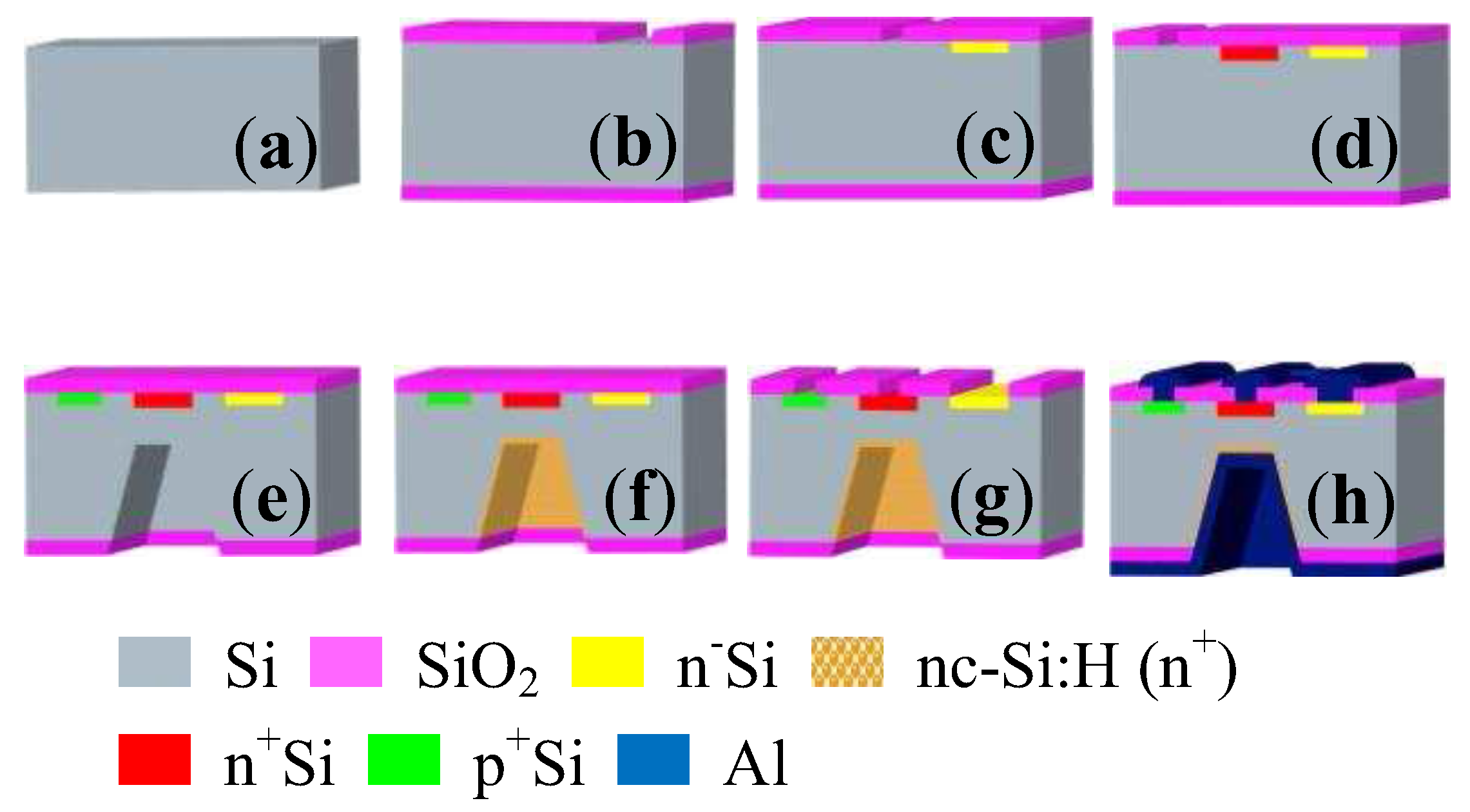

3. Fabrication Technology

4. Results and Discussion

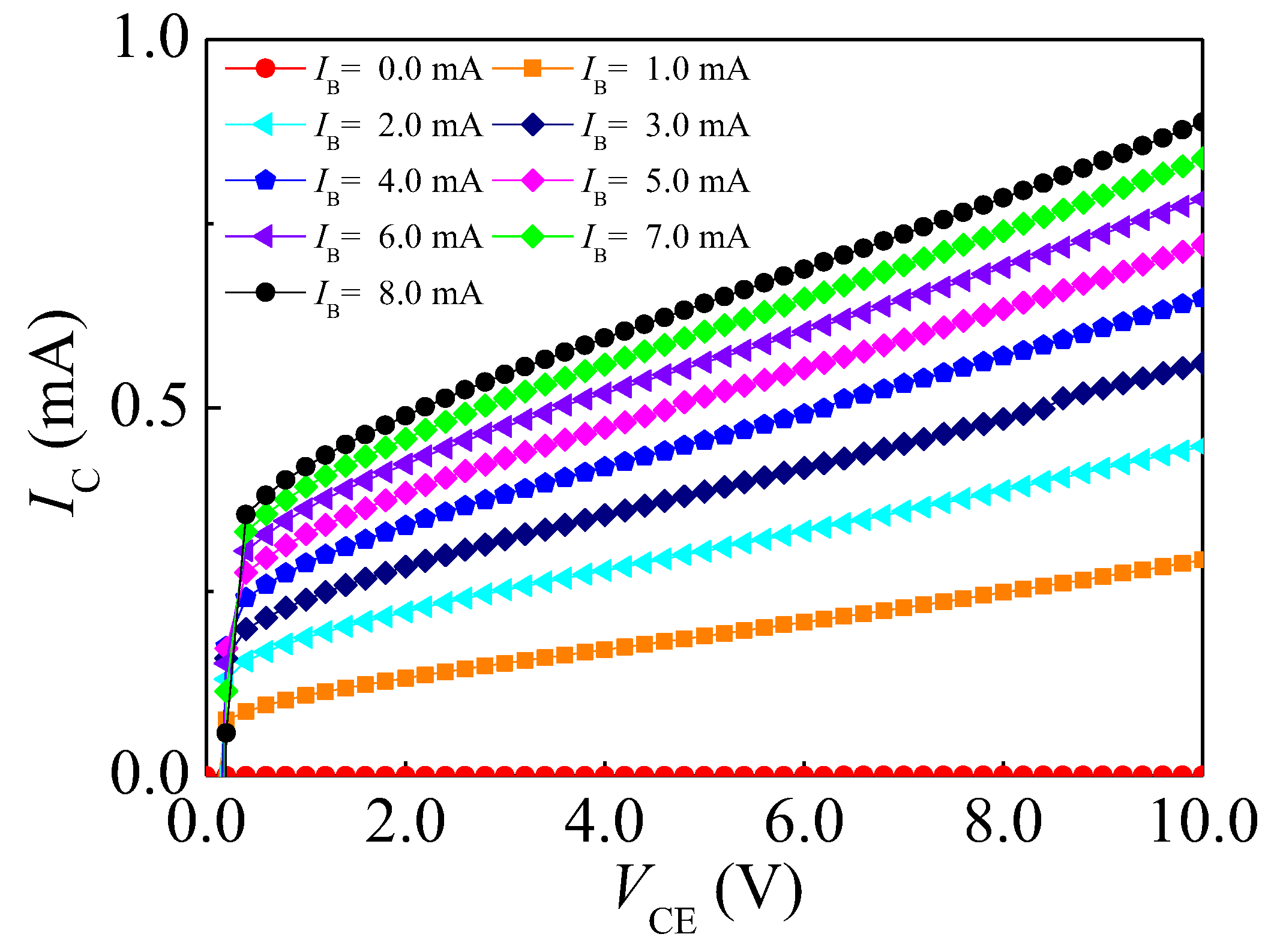

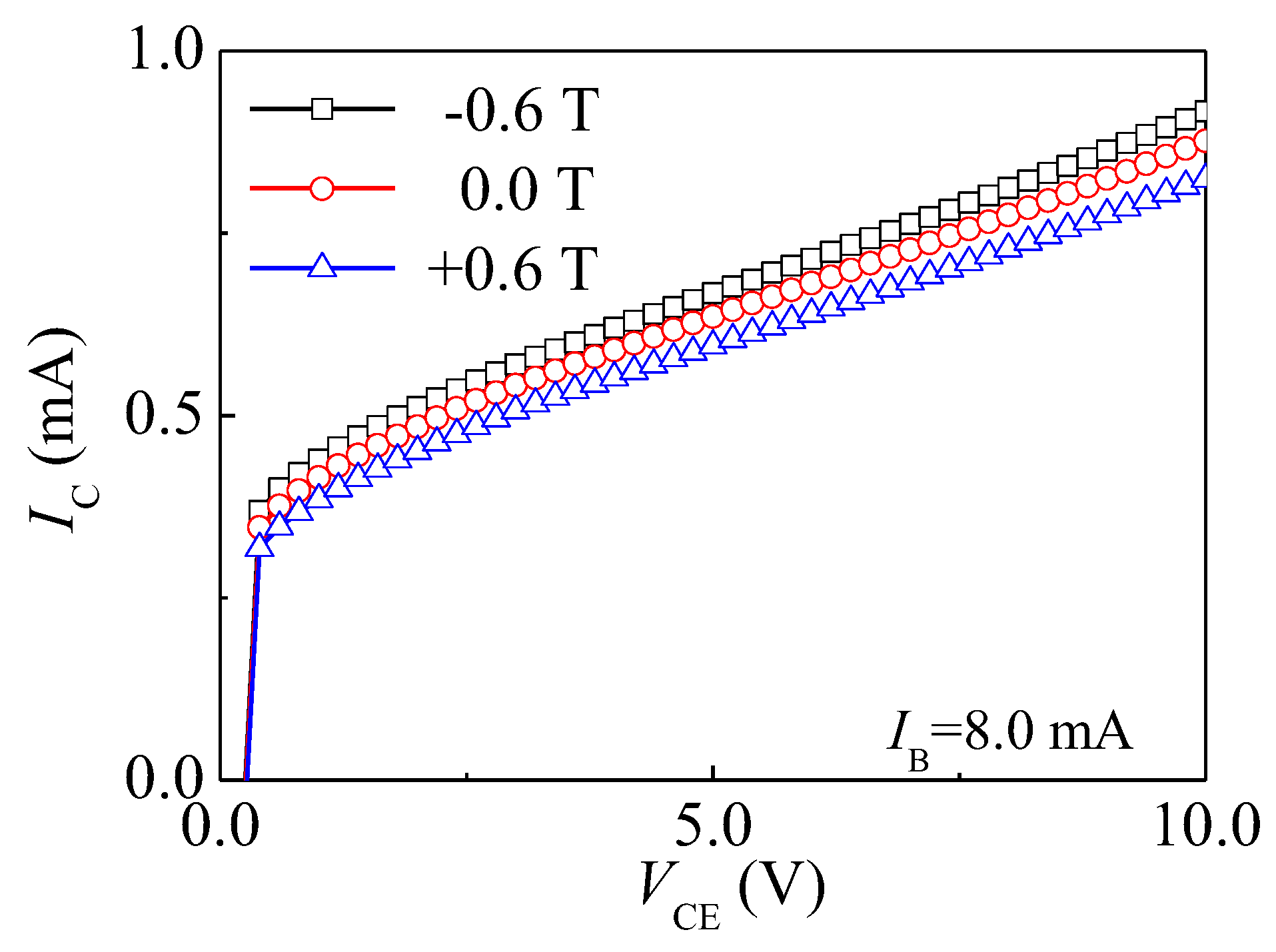

4.1. I–V Characteristics

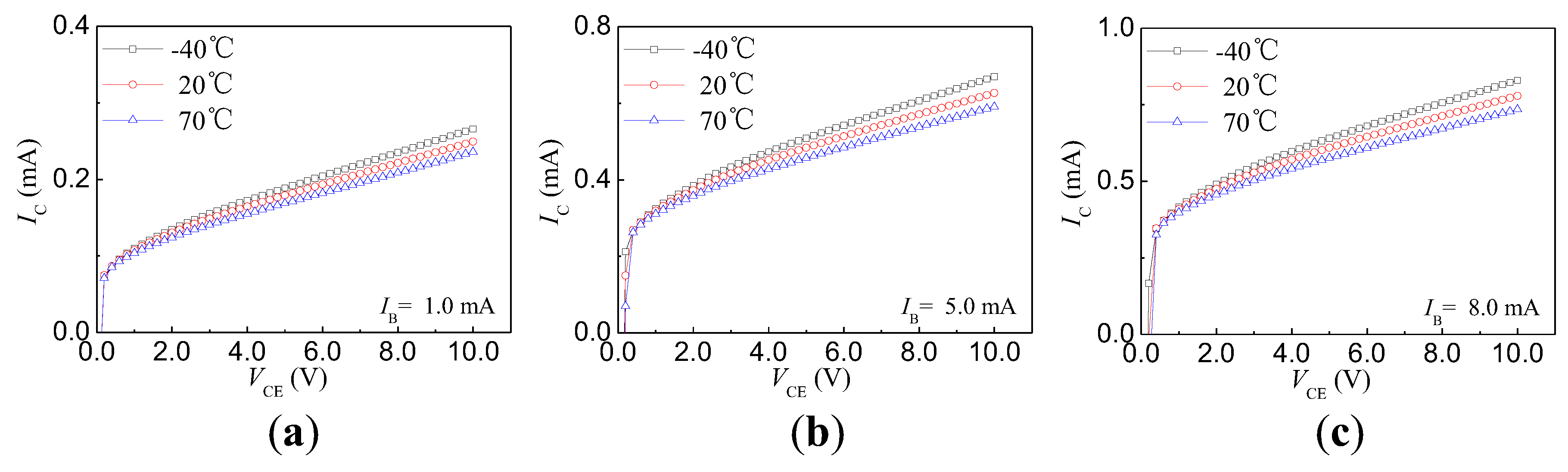

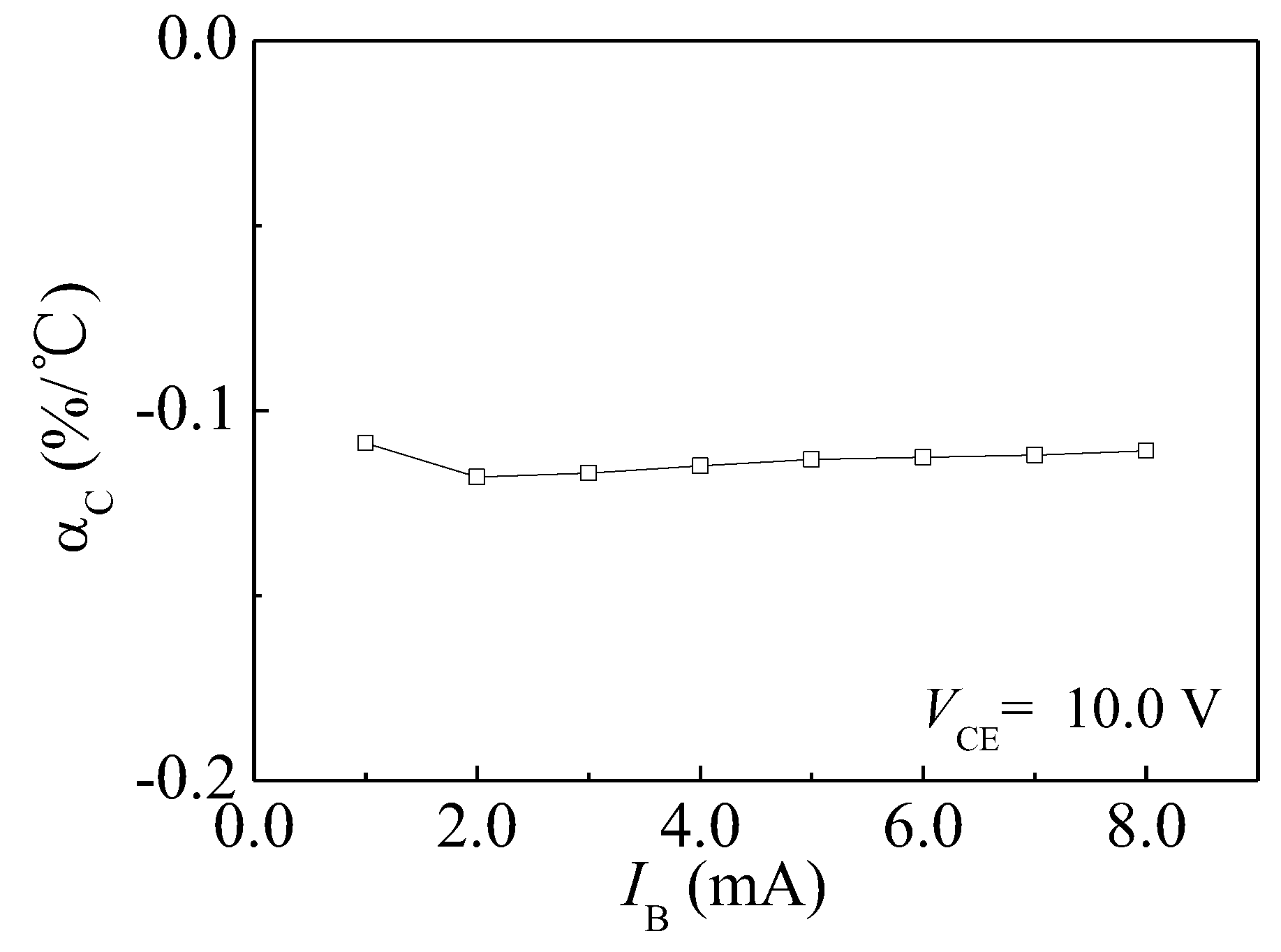

4.2. Temperature Characteristics

4.3. Magnetic Sensitivity Characteristics

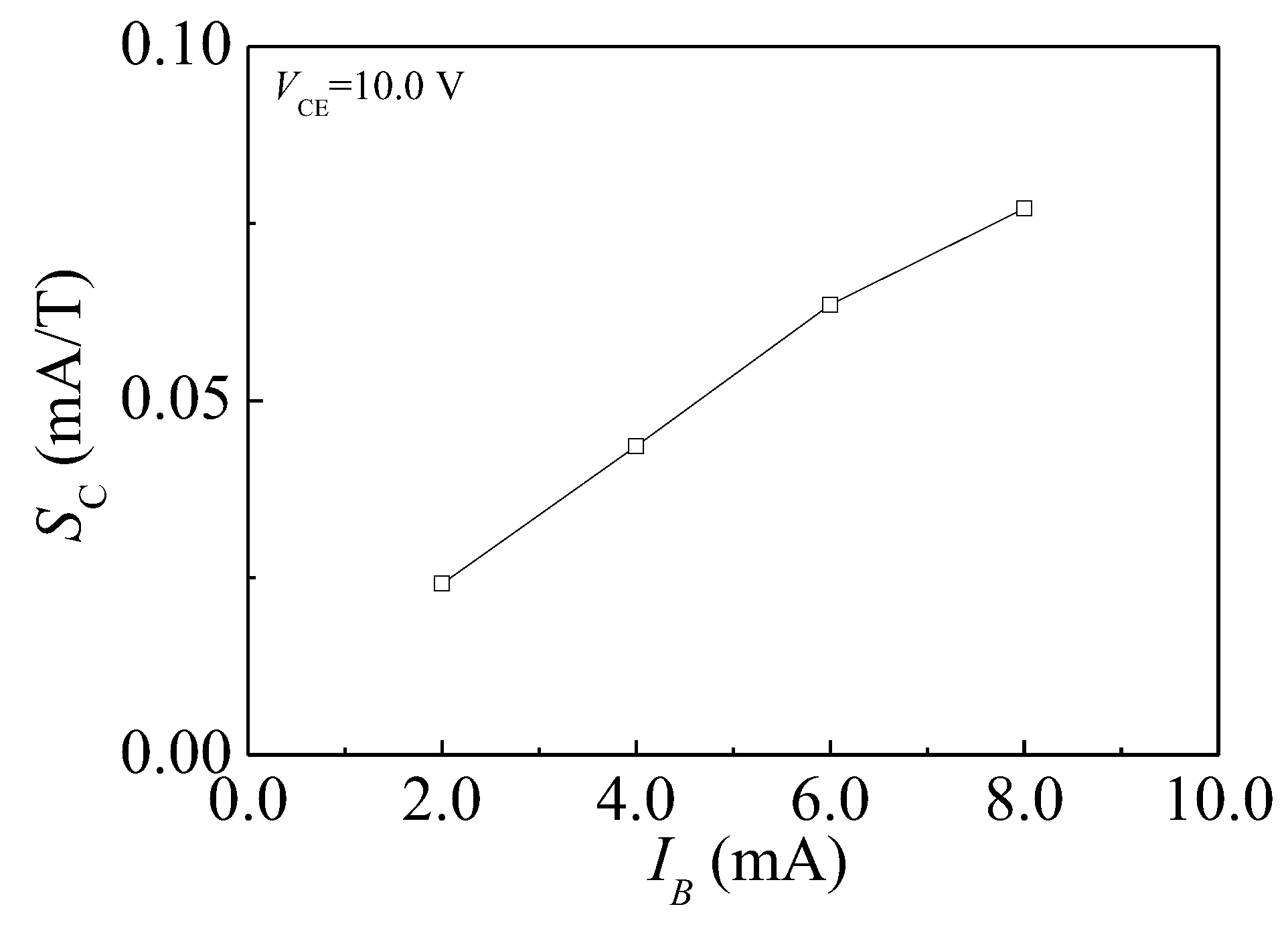

4.3.1. Current Magnetic Sensitivity

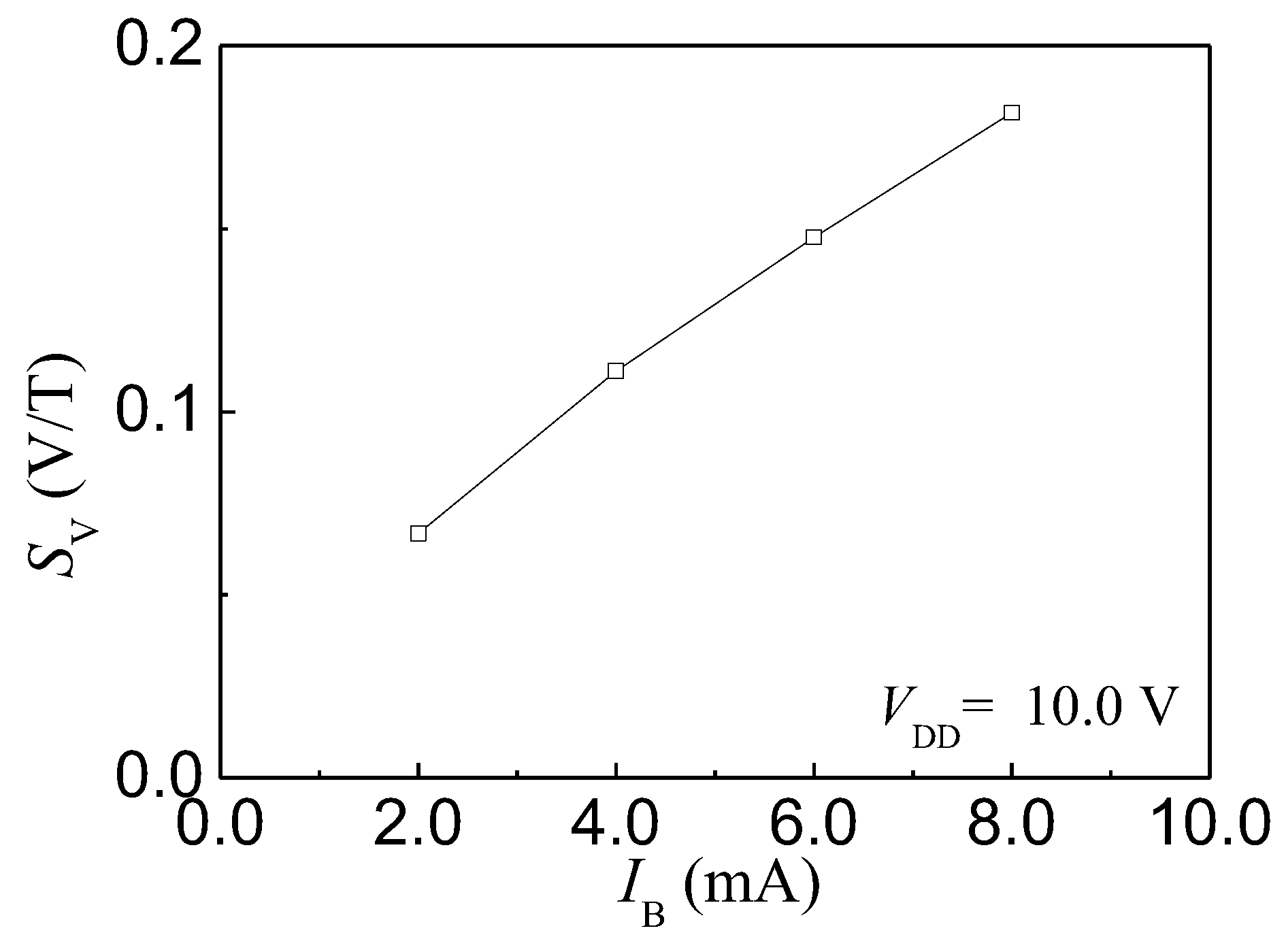

4.3.2. Voltage Magnetic Sensitivity

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Tsai, J.H.; Lour, W.S.; Chao, Y.T. An InP/InGaAs metamorphic δ-doped heterojunction bipolar transistor with high current gain and low offset voltage. Thin Solid Films 2012, 521, 172–175. [Google Scholar] [CrossRef]

- Narang, V.B.; Shukla, S.R. Quantitative analysis of dc characteristics of Ga0.5In0.5P/GaAs heterojunction bipolar devices. J. Vac. Sci. Technol. B 2013, 31, 061201. [Google Scholar] [CrossRef]

- Saha, U.; Imteaz, F.; Saleque, O.P. Numerical simulation of silicon-germanium heterojunction bipolar transistor (HBT) in silvaco/atlas and analysis of HBT base transit time to achieve faster operation. In Proceedings of the 2015 International Conference on Electrical Engineering and Information Communication Technology (ICEEICT), Dhaka, Bangladesh, 21–23 May 2015; pp. 1–4.

- Kim, S.M.; Ha, J.; Kim, J.B. Ideal pn diode current equation for organic heterojunction using a buffer layer: Derivation and numerical study. Braz. J. Phys. 2016, 46, 170–174. [Google Scholar] [CrossRef]

- Huang, T.H.; Wu, M.C. Efficient light output power for InGaP/GaAs heterojunction bipolar transistors incorporated with InGaAs quantum wells. Solid State Electron. 2016, 121, 12–15. [Google Scholar] [CrossRef]

- Kennedy, J.; Leveneur, J.; Williams, G.V.M. Fabrication of surface magnetic nanoclusters using low energy ion implantation and electron beam annealing. Nanotechnology 2011, 22, 115602. [Google Scholar] [CrossRef] [PubMed]

- Leveneur, J.; Kennedy, J.; Williams, G.V.M. Large room temperature magnetoresistance in ion beam synthesized surface Fe nanoclusters on SiO2. Appl. Phys. Lett. 2011, 98, 053111. [Google Scholar] [CrossRef]

- Lai, S.W.; Kuo, T.C.; Kiang, J.F. CMOS-MEMS single-axis magnetic-field sensor for measuring geomagnetic field disturbance. In Proceedings of the 2010 5th International Microsystems Packaging Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, 20–22 October 2010; pp. 1–4.

- Osberger, L.; Frick, V.; Hébrard, L. High resolution shallow vertical Hall sensor operated with four-phase bi-current spinning current. Sens. Actuators A Phys. 2016, 244, 270–276. [Google Scholar] [CrossRef]

- Lozanova, S.; Noykov, S.; Ivanov, A. Temperature and 3D magnetic field measurement using the same sensing zone. Sens. Actuators A Phys. 2016, 242, 27–31. [Google Scholar] [CrossRef]

- Wang, D.Y.; Kuo, K.M.; Chien, C.W. A complementary magnetic field sensor using magnetic tunnel junction. In Proceedings of the 2015 International Symposium on VLSI Technology, Systems and Applications, Hsinchu, Taiwan, 27–29 April 2015; pp. 1–2.

- Gkotsis, P.; Lara-Castro, M.; López-Huerta, F. Mechanical characterization and modelling of Lorentz force based MEMS magnetic field sensors. Solid State Electron. 2015, 112, 68–77. [Google Scholar] [CrossRef]

- Zhao, X.F.; Wen, D.Z.; Li, G. Fabrication and characteristics of an nc-Si/c-Si heterojunction MOSFETs pressure sensor. Sensors 2012, 12, 6369–6379. [Google Scholar] [CrossRef] [PubMed]

- Zhao, X.F.; Wen, D.Z.; Zhuang, C.C. High sensitivity magnetic field sensors based on nano-polysilicon thin-film transistors. Chin. Phys. Lett. 2012, 29, 118501. [Google Scholar] [CrossRef]

- Zhao, X.F.; Wen, D.Z. Fabrication and characteristics of the nc-Si/c-Si heterojunction MAGFET. J. Semicond. 2009, 30, 114002. [Google Scholar]

- Neugroschel, A. Emitter injection efficiency in heterojunction bipolar transistors. Solid State Electron. 1987, 30, 1171–1173. [Google Scholar] [CrossRef]

- Zhao, X.F.; Wen, D.Z.; Pan, D.Y. Differential structure and characteristics of a new-type silicon magnetic sensitivity transistor. Chin. Phys. Lett. 2013, 30, 088501. [Google Scholar] [CrossRef]

© 2017 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, X.; Li, B.; Wen, D. Fabrication Technology and Characteristics of a Magnetic Sensitive Transistor with nc-Si:H/c-Si Heterojunction. Sensors 2017, 17, 212. https://doi.org/10.3390/s17010212

Zhao X, Li B, Wen D. Fabrication Technology and Characteristics of a Magnetic Sensitive Transistor with nc-Si:H/c-Si Heterojunction. Sensors. 2017; 17(1):212. https://doi.org/10.3390/s17010212

Chicago/Turabian StyleZhao, Xiaofeng, Baozeng Li, and Dianzhong Wen. 2017. "Fabrication Technology and Characteristics of a Magnetic Sensitive Transistor with nc-Si:H/c-Si Heterojunction" Sensors 17, no. 1: 212. https://doi.org/10.3390/s17010212

APA StyleZhao, X., Li, B., & Wen, D. (2017). Fabrication Technology and Characteristics of a Magnetic Sensitive Transistor with nc-Si:H/c-Si Heterojunction. Sensors, 17(1), 212. https://doi.org/10.3390/s17010212