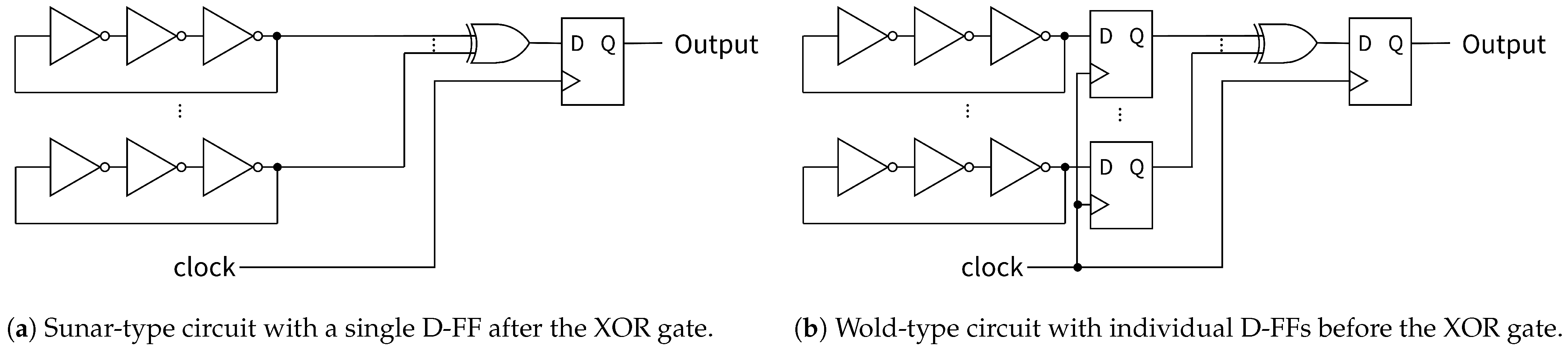

In this session, we describe our previous studies, the XOR gate in the RO-based random number generator and unstable signal inputs to the LUT. Based on these works, the bit occurrence probability of the XOR gate was simulated with and without metastable states.

3.3. XOR Output and Bit Appearance Probability

We considered the effect of the bit distribution from the entropy source on the bit distribution of the XOR gate output in

Section 3.1. There are two primary factors contributing to this phenomenon: First, when threshold voltages

of individual components do not lie exactly between the high and low voltage levels. Second, when the metastable state occurrence introduces biasing in the LUT outputs. For the random number sequence test, statistical randomness tests, including NIST Special Publication 800-22 (NIST SP 800-22), assume a uniform bit distribution. Therefore, achieving a uniform bit distribution is essential for RO-based RNGs. RO-based RNGs generate random numbers based on oscillation signals that include jitter, making it difficult to predict the signals input to the XOR gate. Based on this, this study considers the input signals to the XOR gate as probabilistic events. At this point, we simulate the output bit distribution of the XOR gate using a binomial distribution and confirm the bit distribution of the RO output, the number of ROs, and their relationship.

This validation approach treats the input signals to the XOR operation as stochastic processes. Let the sequence generated from an analog noise source be considered a stochastic process. As an example, let

represent a particular bit, we denote a random sequence of length 2 as

. Here, it is assumed that

is generated after

. When

is dependent on

, the probability of observing this random sequence

is given by

If instead

and

are independent, this expression can be rewritten as

The defining characteristics of true random numbers are non-periodicity and unpredictability. Regarding the bit length

, each bit

of the true random sequence

can be treated as independent. The probability of occurrence for the true random sequence

then becomes

Estimating the probability of each bit appearance in this analog noise source proves challenging. Since each bit’s probability is independent, we can interpret the values obtained during digitization as probabilistically sampled from the population. By collecting l bit samples from the population and estimating the population characteristics, we can derive the probability of occurrence for each bit. The probability of observing 1 can be calculated based on the Hamming weight

of the

l-bit random sequence. Therefore, the bit occurrence probability is estimated as follows:

Fujiwara et al. [

17] calculate the probability of 0 occurrences, but using Equations (

6) and (

7), the probabilities of individual bit appearances can be interpreted as those generated by the RO output. Accordingly, if we conceptualize the analog noise source as an output of an RO circuit, the following holds true:

Equation (

8) shows the probability of inputting a signal to the XOR gate. In the RO-based RNG, multiple ROs are connected with an XOR gate. Here, we assume that each RO input to the XOR has the same probability. Let

be the number of ROs and let

be the iterator for the

j-th RO. Furthermore, let

be the probability of 1 appearing from the

j-th RO. Let

be the input value for an XOR operation. Then, the probability that

k inputs out of

N ROs is 1 as

using a binomial distribution. The probability of 1 from each RO is considered as an independent event. We assume that the appearance probability of 1 from all ROs is the same as follows:

Denoting

as the probability of 1 appearing in the result of the XOR operation, from Equations (

9) and (

10) it follows that

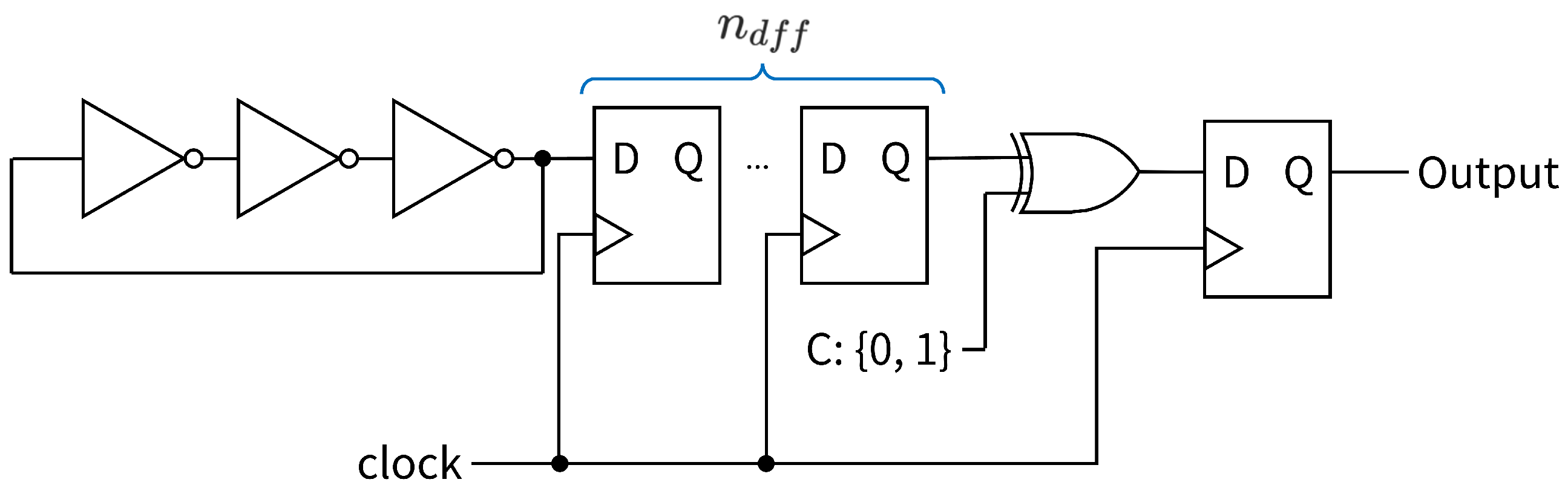

For the simulation, probabilities of 0.642 and 0.587 were used as the probabilities of 1 appearing from RO, as referenced in [

17]. In addition, an ideal probability of 0.500 was incorporated into the simulation. We simulated

with these three probabilities as

based on Equation (

11). The transition of

when

n was set from 1 to 10 is displayed in the graph. The simulation environment is shown in

Table 1.

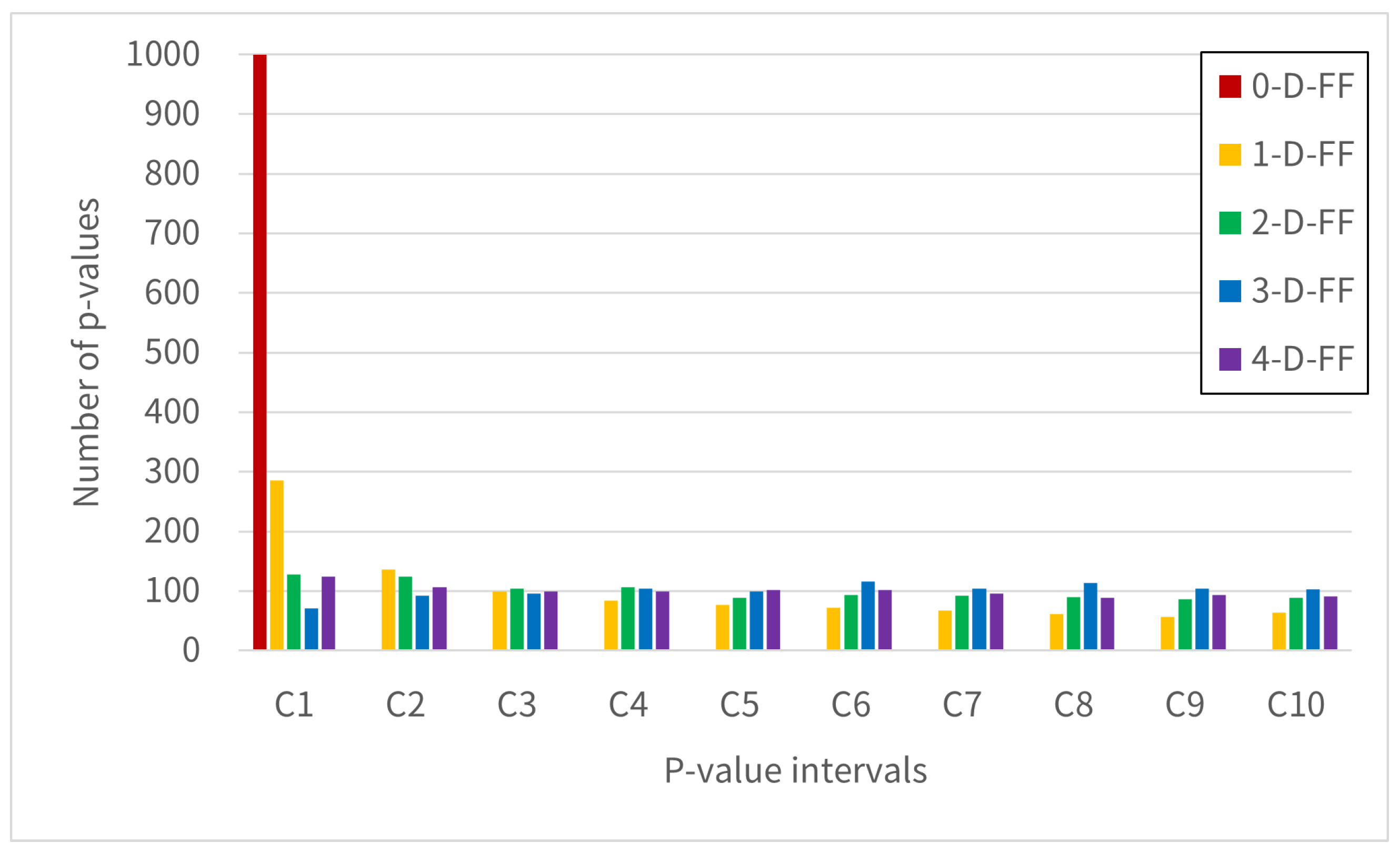

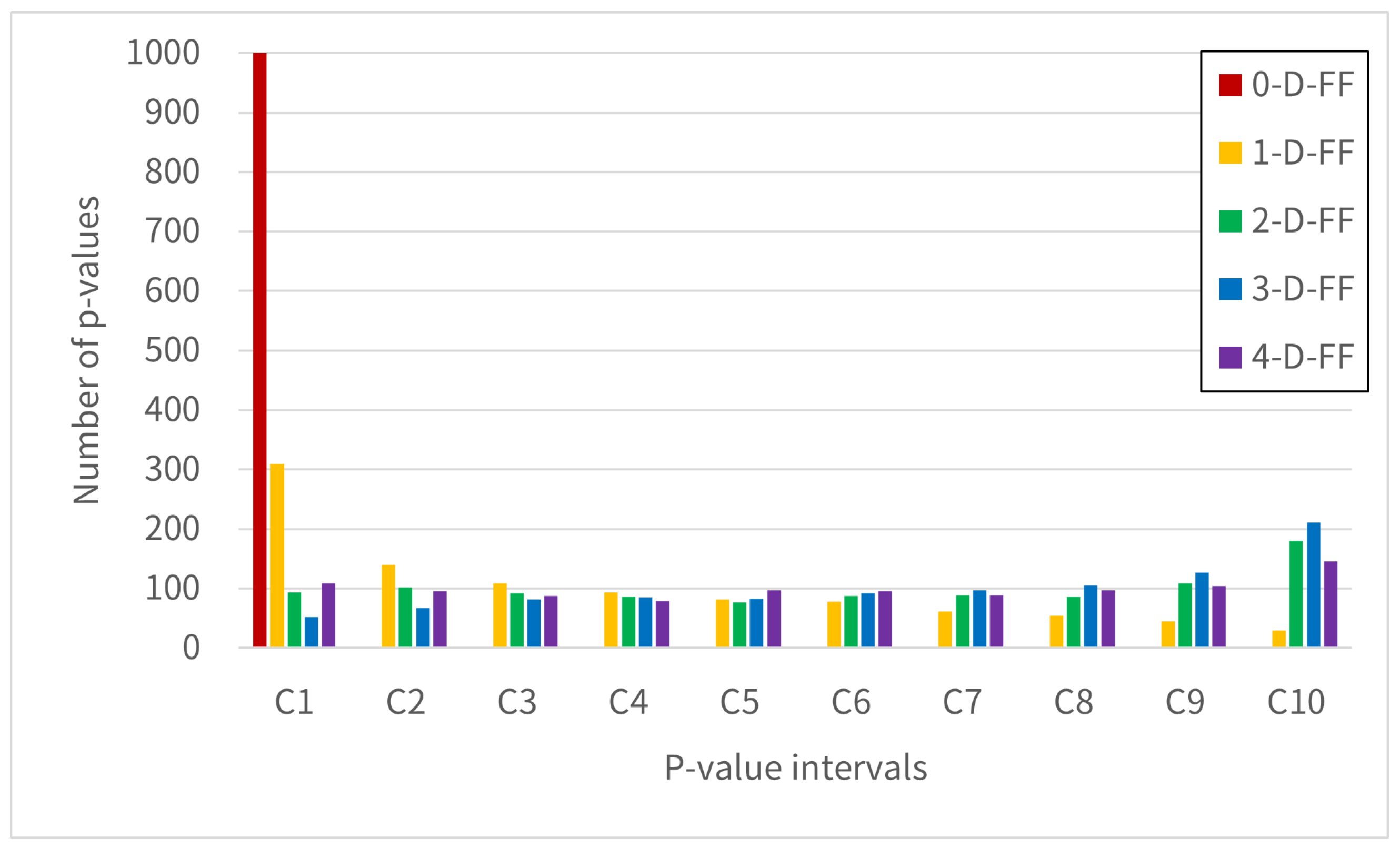

Figure 3 shows the simulation results. As shown in the figure, increasing the number of ROs resulted in the convergence of the probability

to 0.500. Furthermore, as the probability

approaches the ideal value of 0.500, the probability

converges to 0.5 with a smaller number of ROs.

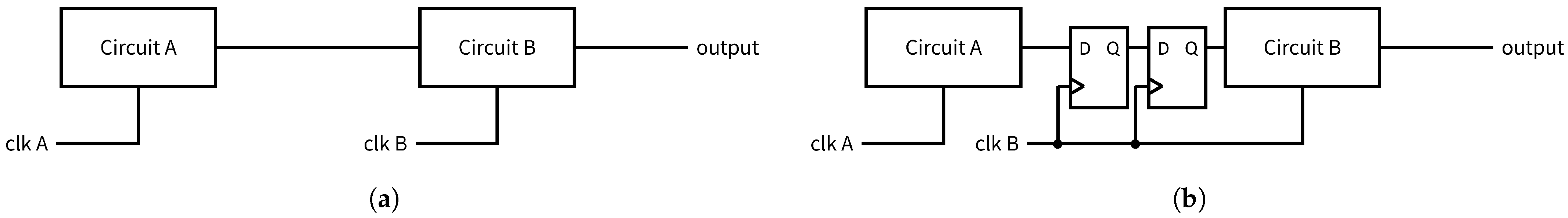

This simulation showed that the bit distribution of the XOR output is expected to become more uniform as the RO output approaches 0.5. Connecting multi-D-FFs to the RO output prevents it from entering the LUT in a metastable state and improves the bit distribution, as discussed in

Section 3.2. Based on these results, we can hypothesize that applying multi-D-FFs to the RO-based RNG affects the bit distribution uniformity of the output random number sequence.

3.4. XOR Output and Metastable State

Previously, we performed a probabilistic simulation of the XOR output when the signals input to the XOR gate were {0, 1}. Here, we conduct a simulation that accounts for signals in metastable states that may occur when sampling asynchronous signals.

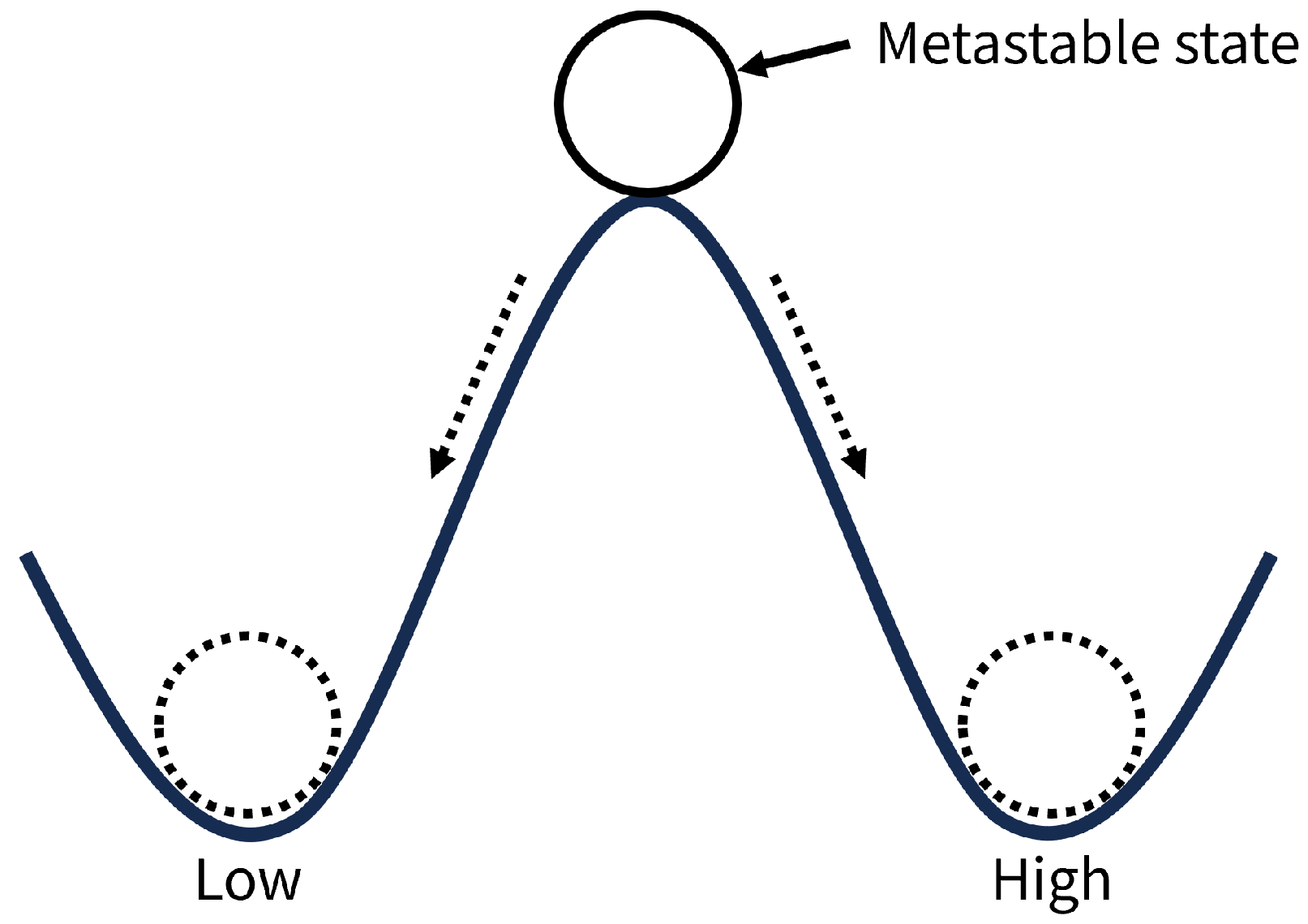

Digital logic typically operates only with {0, 1}, where binary states correspond to high/low voltage levels within the circuit. However, certain voltage values that do not fall within these high/low ranges may occur. We refer to this voltage state as an “intermediate voltage,” which can cause errors in correct computation within the circuit. To prevent such occurrences, it is necessary to implement synchronization circuits or design the circuit architecture with careful attention to timing constraints.

Let

represent the frequency of a particular RO, and let

denote the frequency of the clock on the FPGA board. Here, we define the phase of

as

. Consider sampling

using a D-FF with clock frequency

. When a clock frequency and an RO signal are coprime, we can say that the output phase when sampling

uniformly distributes within

[

20]. If we model

as a sinusoidal waveform, and when the D-FF performs sampling near the points

, this corresponds to being sampled during the setup or hold time at frequency

. In this case, the output of the D-FF will enter a metastable state. Building upon this, we can now analyze the probability of entering a metastable state.

Here we consider two probabilistic events:

- A

Probability of sampling a specific RO oscillation cycle within a given 1-second period for RO signals;

- B

Probability that the sampling occurs near the points within an RO cycle period.

Letting

represent the switching time interval within the RO signal’s period and

denote the complete RO signal period, we can express each probability as follows:

From Equations (

12) and (

13), the probability

of entering a metastable state when synchronizing an RO signal with a D-FF is thus

Next, we examine the probabilities

and

of obtaining 0, 1 when synchronizing an RO signal with a D-FF. From Equations (

12) and (

13), we can derive the following:

Thus, when synchronizing an asynchronous RO signal with the clock via D-FFs, metastable states will occur. The probability of this occurrence can be calculated based on the frequency of the RO signal and its switching time.

Consequently, these three signal patterns—including the metastable state—will now be input to the XOR gate, each occurring with their respective probabilities.

Now, let us consider the output when the three possible inputs (including a metastable state) are applied to the XOR gate. Let XORed denote the output of the 2-input XOR gate with respect to inputs RO1 and RO2. As noted in the literature [

17], the exact behavior of the XOR gate when receiving a metastable signal is unclear. For this analysis, we assume that the presence of even a single metastable input causes output instability, which we designate as M. The resulting truth table is shown in

Table 2.

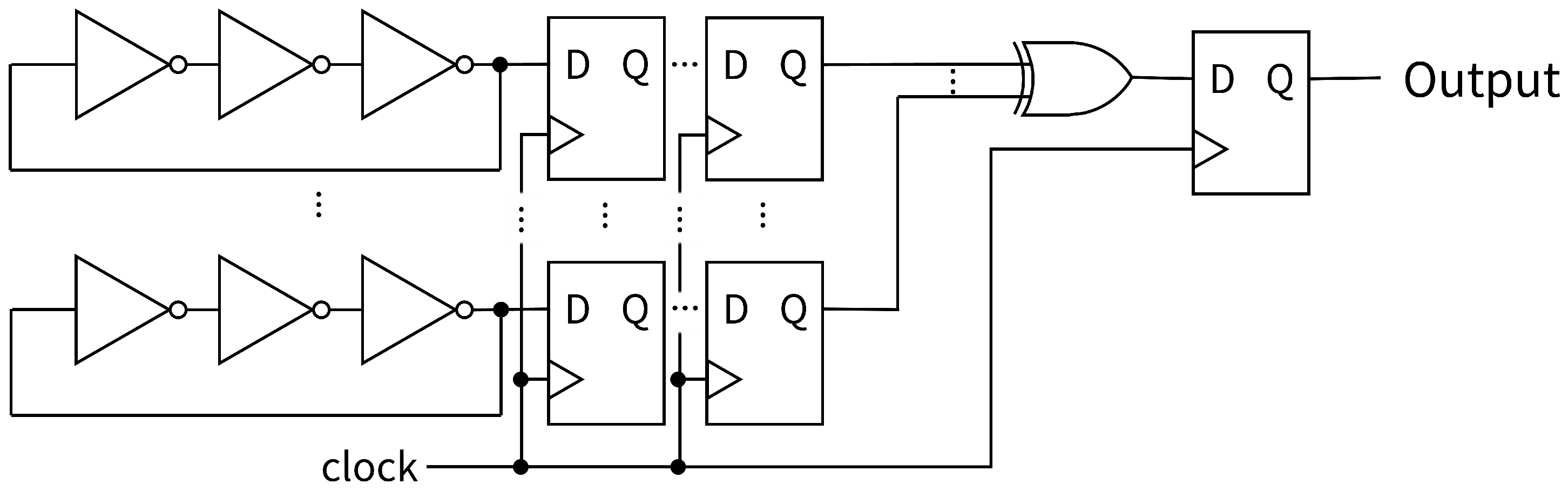

Based on these considerations, we will simulate the probability of each bit state in the XOR gate according to the binomial distribution. As in

Section 3.3, we assume the probabilities of each bit appearing from each RO to be identical. We further assume that both the sequences emerging from each RO and the individual bit appearance probabilities are all statistically independent. The output of the XOR gate in this case can be determined as follows:

Using these results, we will now examine the probabilities when employing N ROs. The outputs of each XOR gate can be represented as follows:

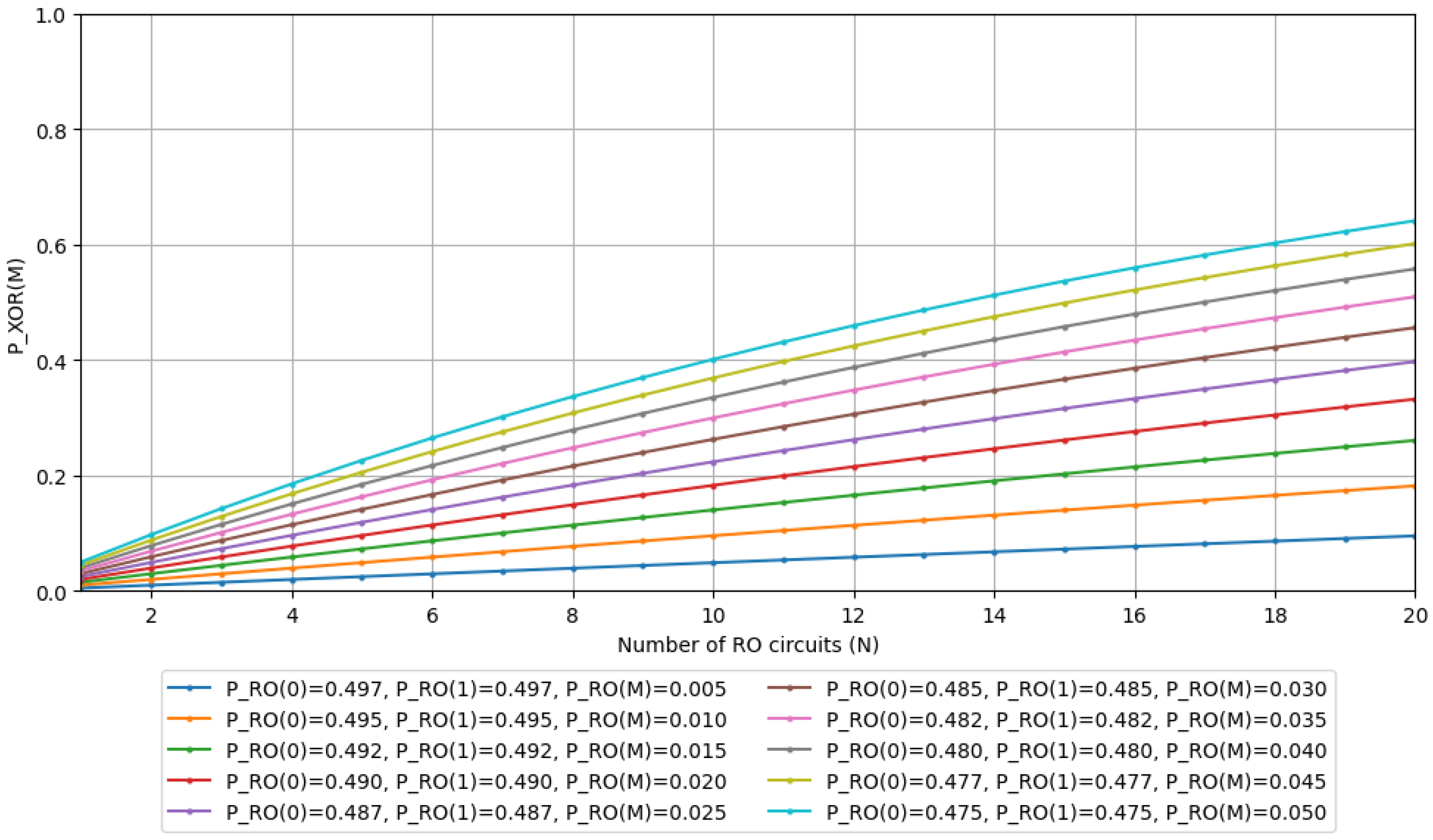

From Equation (

21), we can see that the probability of metastable state occurrence is expected to increase as the number of ROs N increases.

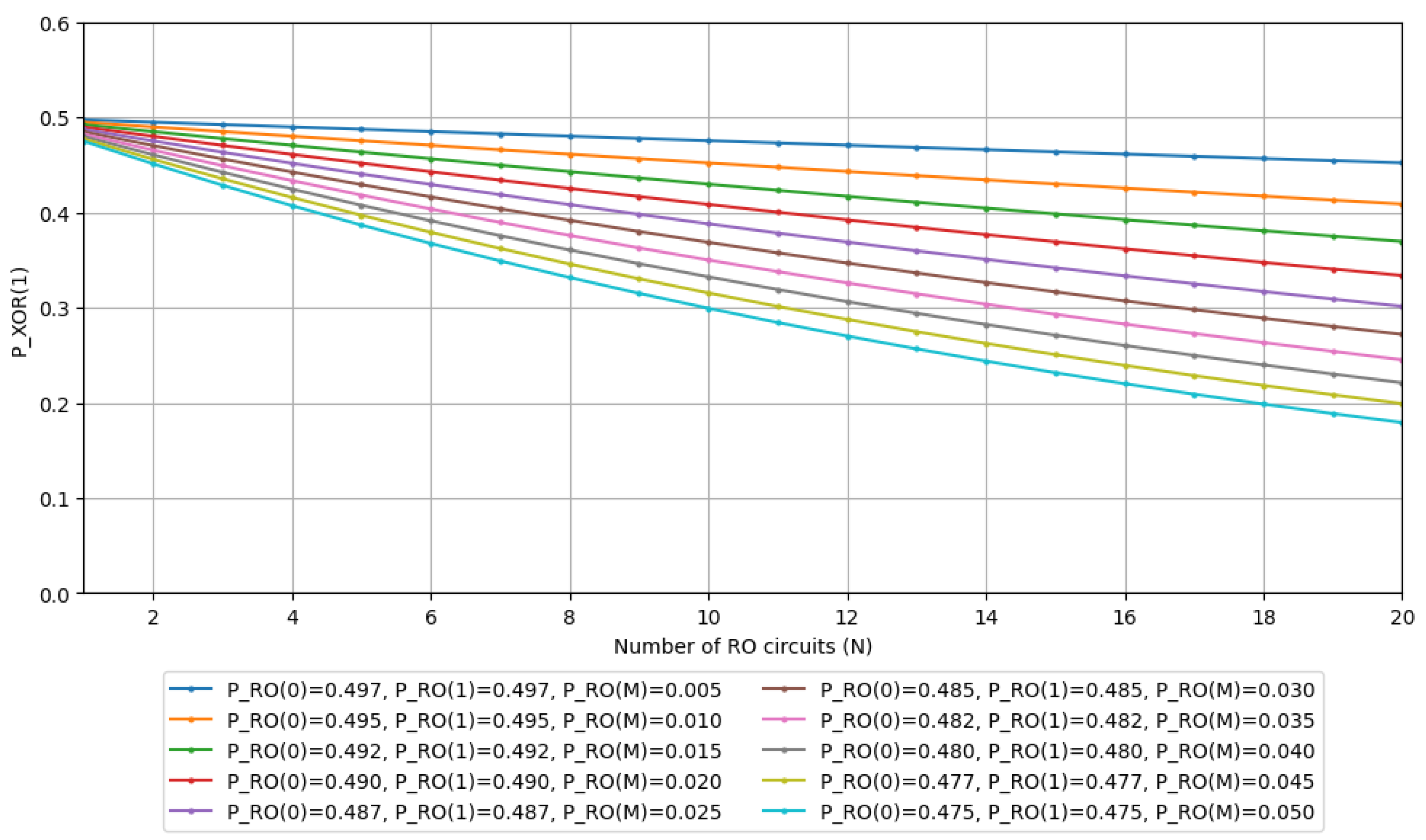

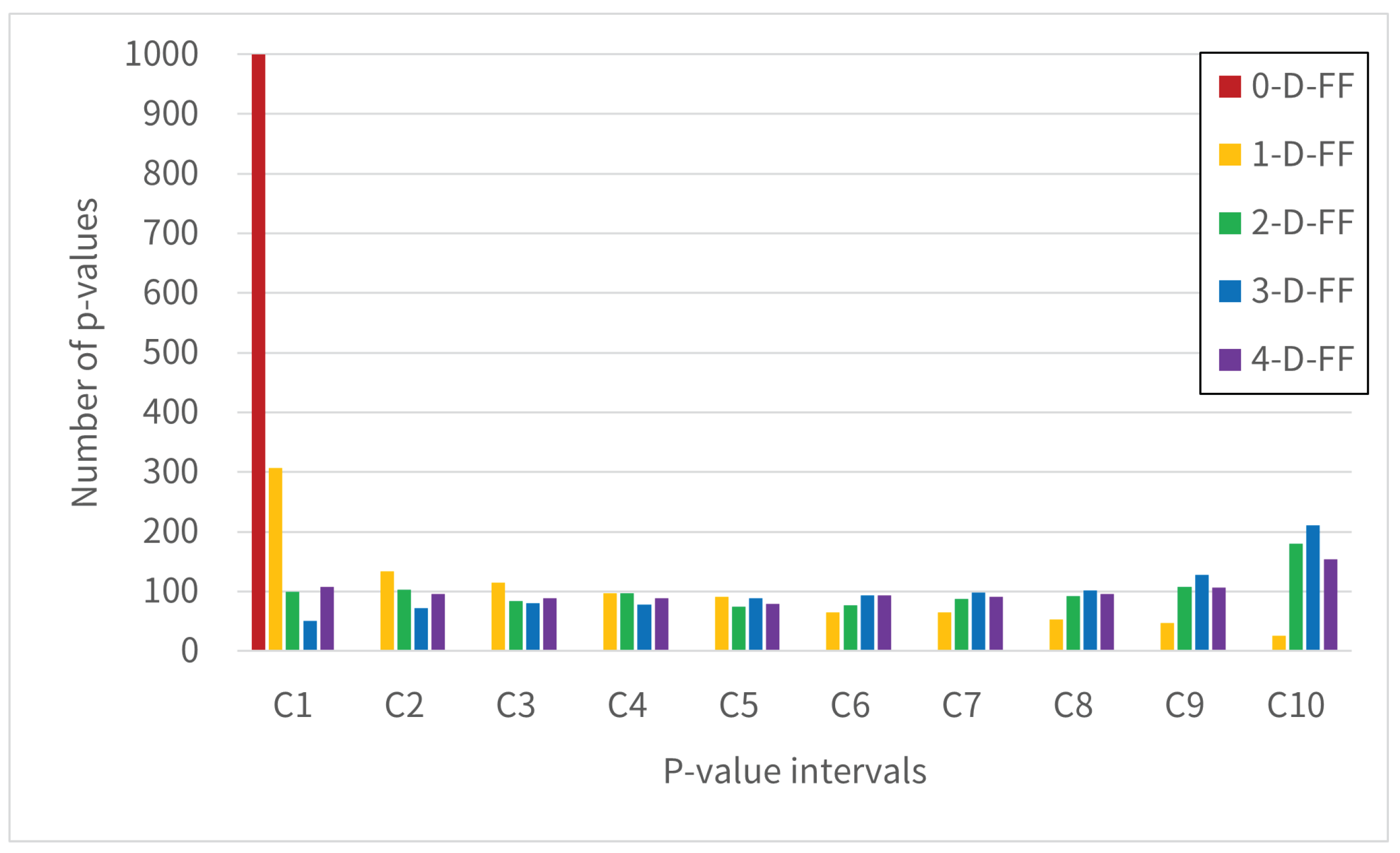

We will now conduct simulations based on Equations (

19)–(

21). The simulation environment is specified in

Table 1. For our test parameters, we set

and observe the trends when varying

. For

, let’s assume a switching delay of

, with RO frequencies

and clock frequency at 100 MHz. These values serve as reference points for calculating the probability of metastable state occurrences, so we will disregard the specific relationship between

and

in this instance. Using the above values and Equation (

14), we obtain

, which we will utilize as simulation parameters. The simulation results for the probabilities of outputs

and

are shown in

Figure 4 and

Figure 5, respectively.

The results clearly show that the probability of metastable state occurrences increases as the number of RO circuits grows. Moreover, when the switching delay

remains constant, the higher the frequency of the RO signals, the greater the increase in metastability occurrence probability. We observe that if an XOR output enters a metastable state and exhibits biased bit distribution, then increasing the number of ROs would predictably lead to increased bias in the bit distribution. These results, along with

Section 3.3, indicate that unless we reduce the likelihood of input signals to XOR gates entering metastable states, we cannot achieve a uniform bit distribution by increasing the number of ROs.

Now, let us consider how to reduce metastable states. Reference [

20] states that when using two D-FFs for synchronization, the probability of metastability occurrence is significantly reduced. This suggests that by connecting two D-FFs after an asynchronous RO, we can effectively suppress the probability

of metastable state occurrences. If we can successfully reduce the probability

of metastable states, then even in the presence of biased bit distribution—as demonstrated in

Section 3.3—increasing the number of ROs would approach a more uniform bit distribution.