Random numbers are widely used in a variety of applications, including statistics, computer programming, video games, numeric analysis, and cryptography, among others [

1,

2,

3]. Random numbers can be obtained from random sequences produced by random number generators (RNGs) [

1]. The quality of an RNG is determined by its ability to produce sequences with good statistical properties, minimal predictability, and uniform digit distribution [

4,

5,

6,

7].

The development of random number generation methods dates back to the 1940s, with contributions from Von Neumann, Metropolis, Ulam, and Lehmer. They pioneered the Monte Carlo simulation method [

8,

9,

10], which was published by N. Metropolis and Stanislaw M. Ulam in 1949 [

9,

11]. The method estimates outcomes in unpredictable events across multiple fields, including sales forecasting, integral approximations, sampling experiments, and artificial intelligence [

12,

13,

14,

15]. The Monte Carlo method is based on sequences of pseudorandom numbers, where a set of results is predicted in an estimated range of values, building a model with possible results [

12,

13,

14,

15]. However, unlike random numbers, pseudorandom numbers are deterministic, meaning their sequences eventually repeat [

6,

7]. Thus, pseudorandom numbers must meet specific statistical criteria to ensure unpredictability, e.g., the random appearance of the length and uniformly distributed bits [

6,

7]. Some applications of pseudorandom sequences include cryptography, financial models, communications, artificial intelligence, etc., [

6,

7,

16,

17].

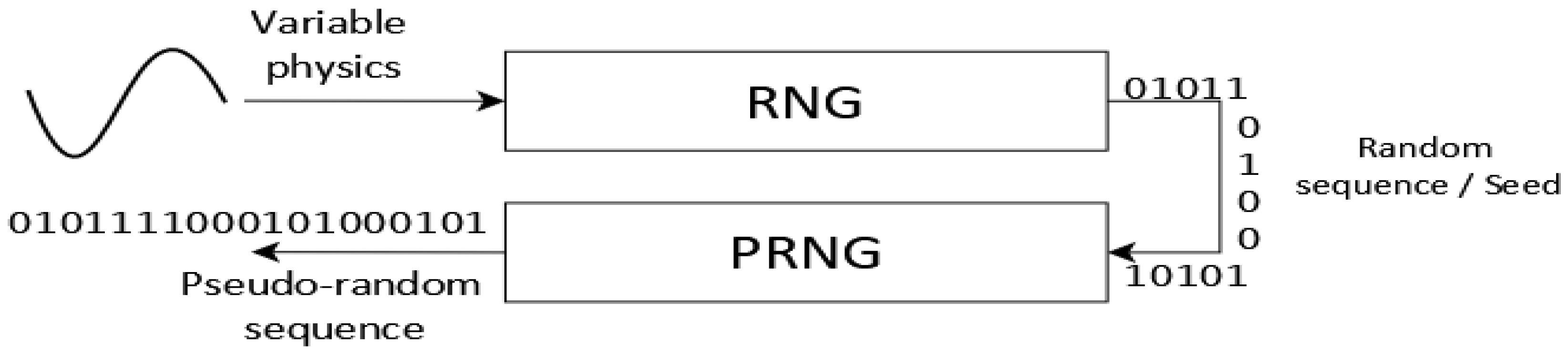

Random Number Generators (RNGs) and Pseudorandom Number Generators (PRNGs)

Various types of random number and pseudorandom number generators (RNGs and PRNGs) have been designed. Examples of RNGs are the QRNG (Quantum Random Generator) and the TRNG (True Random Generator) [

18,

19,

20], which use physical variables, such as electronic noise from electronic circuits, biological signals, and quantum processes (e.g., semiconductors) [

18,

19,

20]. The quality of the generators depends on the concordance between their output properties and those of a process of generating uniform and independent data [

21]. The goal is to ensure that the random number sequences meet the necessary characteristics for various applications, such as generating initial data or seed data for a PRNG, as shown in

Figure 1. From the seed data, the PRNG is initialized to produce a new pseudorandom sequence [

4].

PRNGs use deterministic algorithms to generate sequences, ensuring uniformity and independence [

22]. A common method is the Linear Congruential Generator (LCG) invented by D. H. Lehmer, defined by the recursive relation in Equation (1), where each number is computed as a function of the previous number.

is defined as the seed (

),

a is the constant multiplier (

),

is the active constant (

c > 0), and

m is the modulus (

). According to the recursive relation,

is the remainder when dividing

by the modulus [

22,

23,

24,

25,

26,

27].

Another widely used PRNG method is the Linear Feedback Shift Register (LFSR), which employs storage registers that shift bits in response to clock pulses, generating pseudorandom sequences. Each register cell stores a bit that is shifted one position to the right for each clock pulse [

28,

29,

30,

31,

32,

33]. This component is often used in generators for stream encryption due to the flexibility of hardware implementation. Additionally, the register’s statistical properties [

28,

29,

30,

31,

32,

33] allow it to be used for the design of news generators.

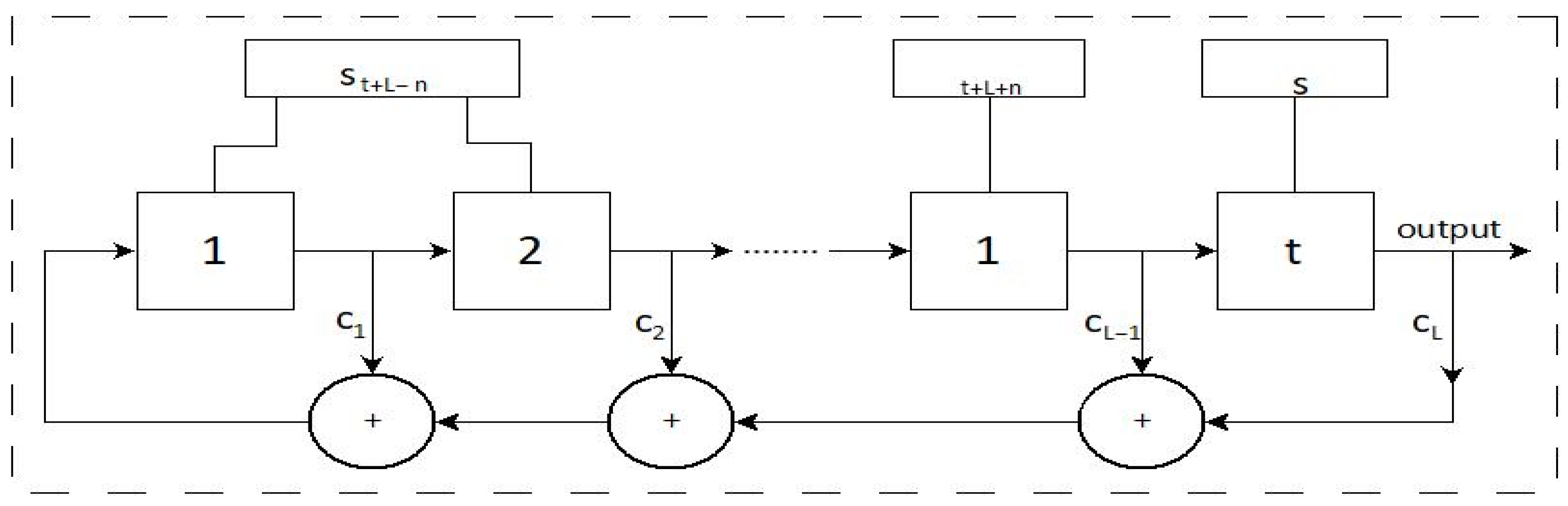

Every time a shift to the right occurs in the LFSR, a cell in the register becomes empty, allowing a new bit to be stored in the vacant position [

28,

29,

30,

31,

32,

33]. Feedback is a linear feedback function, as shown in Equation (2). In an LFSR of length L over

, the system functions as a finite state automaton that generates a semi-infinite sequence of elements of

, denoted

, which satisfies a linear recurrence relation of degree L over

[

28,

29,

30,

31,

32,

33]. The coefficients of L

are elements of

and are referred to as feedback coefficients of the LFSR;

Figure 2 illustrates an LFSR representing this concept [

28].

Some recent PRNG generator designs include the one proposed in [

34], which uses multiple LFSRs to produce 16-bit pseudorandom numbers at 50 kHz and ambient electromagnetic noise to generate the generator seeds [

34]. Thus, the efficiency of LFSRs in the design of pseudorandom number generators for different applications is once again confirmed. Another is proposed by [

35], which consists of a generator called a multi-PRNG. This generator produces multiple pseudorandom number streams. A multi-PRNG is implemented using a field programmable gate array FPGA, based on a chaotic multi-scroll memristive Hopfield neural network (MHNN) [

35]. The objective is to produce multiple spatially dependent PRNG streams from the chaotic multi-scroll system. Each multiple shift produced functions as an independent PRNG [

35].

All random and pseudorandom number generators must be validated through statistical tests to determine whether the sequences they produce exhibit randomness or pseudo-randomness. Examples include the Diehard tests and the NIST statistical tests [

36,

37,

38,

39], which consist of 15 tests proposed by the National Institute of Standards and Technology to evaluate the RNG or PRNG generator sequences. Some of the tests include the Frequency (Monobit) test [

37,

40,

41], which ensures that the sequence contains approximately equal proportions of zeros and ones with uniform a distribution [

37,

40], the Frequency within a Block test, which examine the proportion of ones within M-bits bocks [

37,

40,

42], the Runs test, which evaluates the total number of runs (uninterrupted by identical) in the entire sequence [

37,

40,

43], the Binary Matrix Rank test, which checks the linear dependence between fixed length substrings of the original sequence [

36,

37,

40,

44], the Maurer’s Universal Statistical test, which measures the number of bits between matching patterns to determine whether the sequence can be compressed without losing information [

37,

40,

45], the Linear Complexity test, which assesses whether the sequence is complex enough to be considered random [

37,

40,

46,

47], the Cumulative Sums (Cusums), which analyzes the maximum deviation from zero in a random walk defined by the cumulative sum, where sequence digits are adjusted to −1 and +1 [

37,

40,

48], the Random Excursion test, which determine the number of K visit cycles in a cumulative random walk [

37,

40,

48], and the Random Excursion Variant test, which examines the total number of times a particular state is visited in a sequence [

37,

40,

48]. These statistical tests help validate the quality of RNG and PRNG sequences, ensuring their suitability for cryptographic, simulation, and other applications.

Each test in the suite evaluates pseudo-randomness independently, calculating the

P-value, as shown in

Table 1, where the corresponding equation is observed [

37]. A sequence is considered satisfactory only if the

P-value is greater than 0.01; otherwise, the sequence is deemed completely non-random or non-pseudorandom [

37,

40]. The

P-value is derived from hypothesis testing, assessing whether the observed result is consistent with the assumption of randomness [

37,

40]. Each test follows a hypothesis-testing framework. Under the null hypothesis H0, the sequence is random, while under the alternative hypothesis Ha, the sequence is not random [

37,

40]. Two types of errors can occur during hypothesis tests: type I error, where H0 is rejected (concluding non-randomness) when the sequence is actually random [

37,

40], or type II error, where H0 is accepted (concluding randomness) when the sequence is actually non-random [

37,

40]. For a sequence to pass the test, it must be random enough to accept H0; if it is non-random, H0 is rejected in favor of Ha [

37,

40].

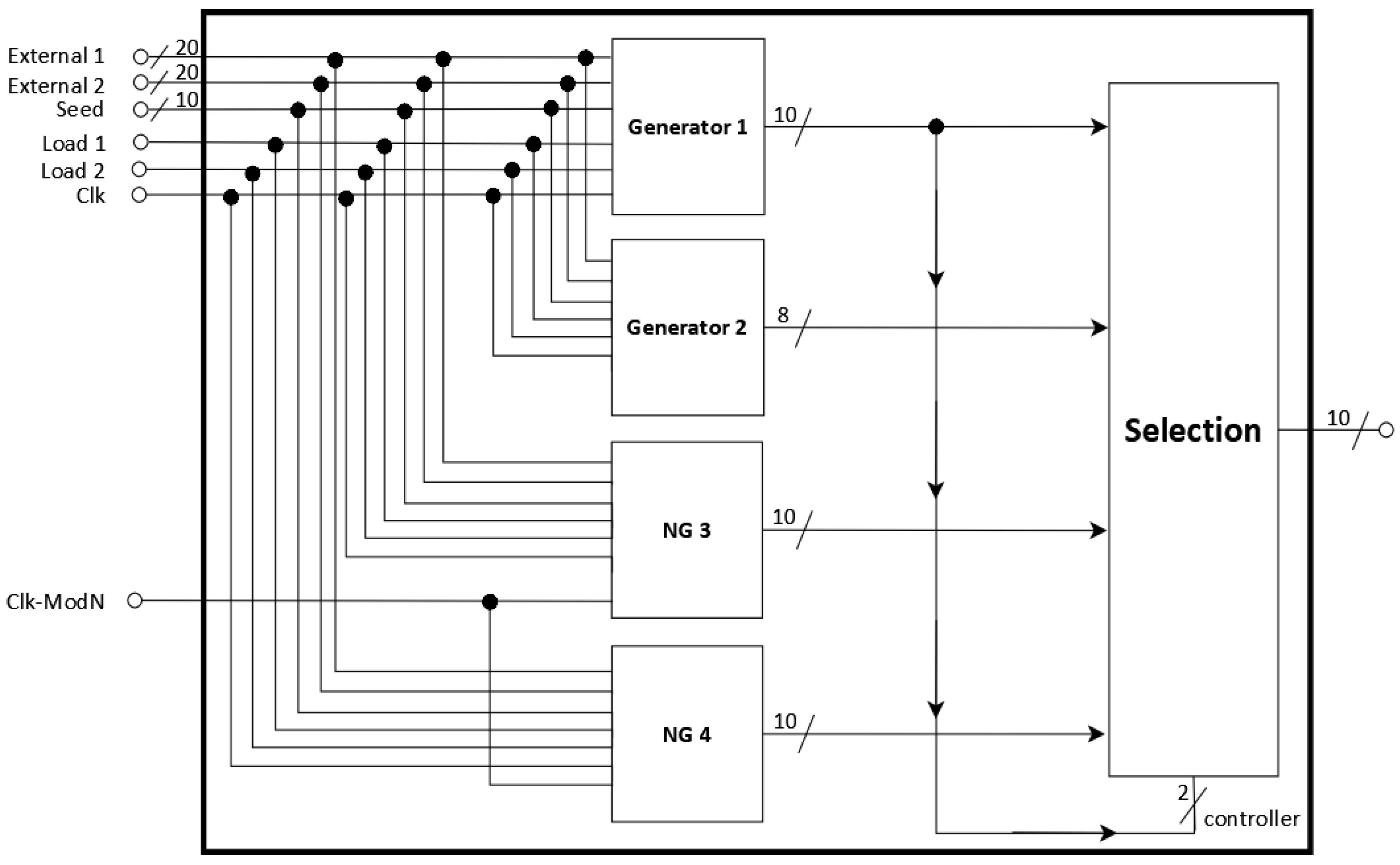

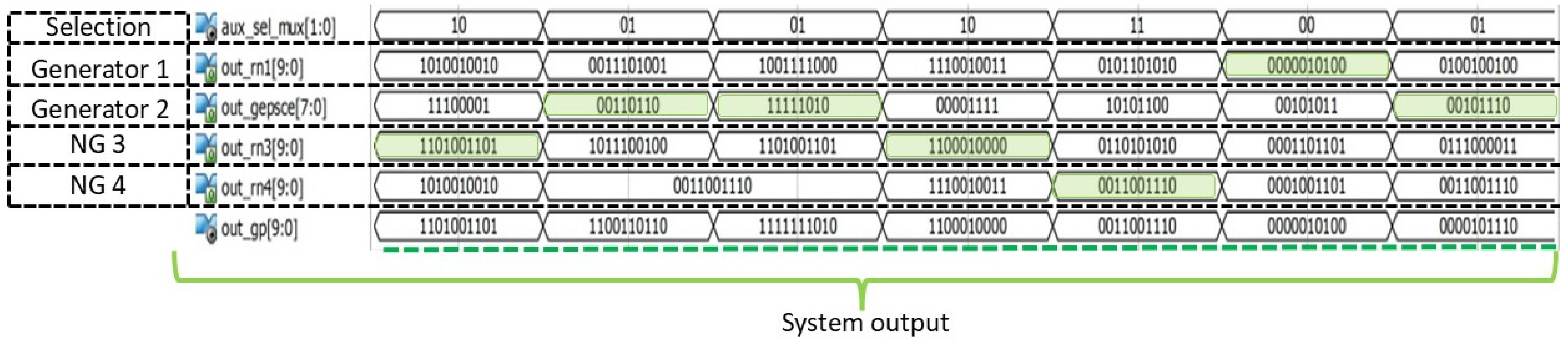

This work presents the design and implementation of a system incorporating PRNG generators and neuro-generators on the

Virtex 7 xc7vx485t-ffg1761 reconfigurable FPGA (Field Programmable Gate Array) device [

40,

49,

50,

51]. The system features four internal PRNG generators with good statistical properties and a uniform bit distribution, which meet the criteria to pass various NIST tests. The system allows for the generation of new pseudorandom sequences by selecting from all internal generators. In addition, a specific generator can be chosen to produce a previously validated sequence. Some of the tests confirming the pseudo-randomness of the generated sequences include the Frequency (Monobit) test, Frequency within a Block test, Linear Complexity test, and Binary Matrix Rank test, among others. The results demonstrate that the generator system is suitable for various applications, such as biological systems, simulations, testing electronic circuits, etc.