Standard-Cell-Based Comparators for Ultra-Low Voltage Applications: Analysis and Comparisons

Abstract

:1. Introduction

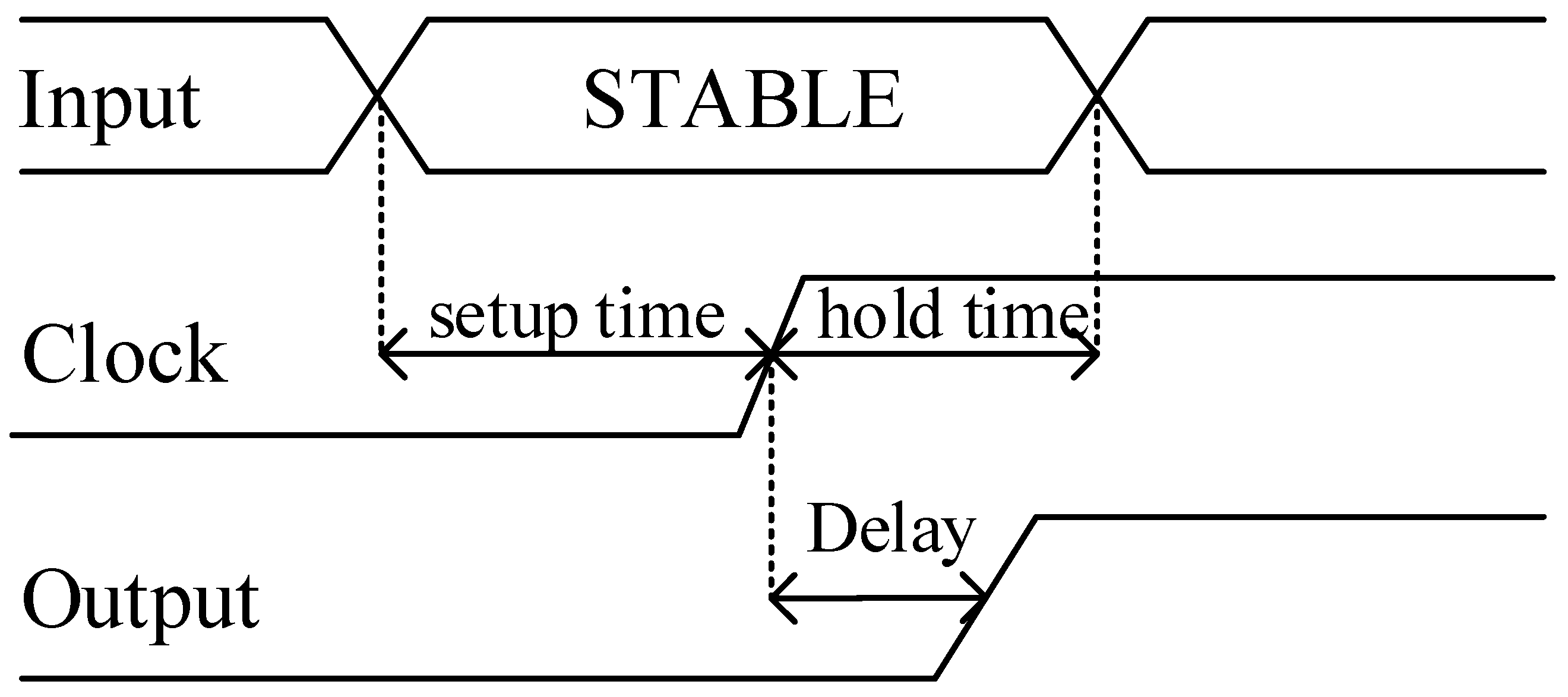

2. Latched Comparators: Performance Parameters and Application Scenarios

2.1. Performance Parameters of the Latched Comparator

2.2. Performance Parameters vs. Latched Comparators Applications

3. A Review of the Main Topologies to Implement Standard-Cell-Based Dynamic Voltage Comparators

4. Simulation Testbench and Figures of Merit

4.1. Testbench Description

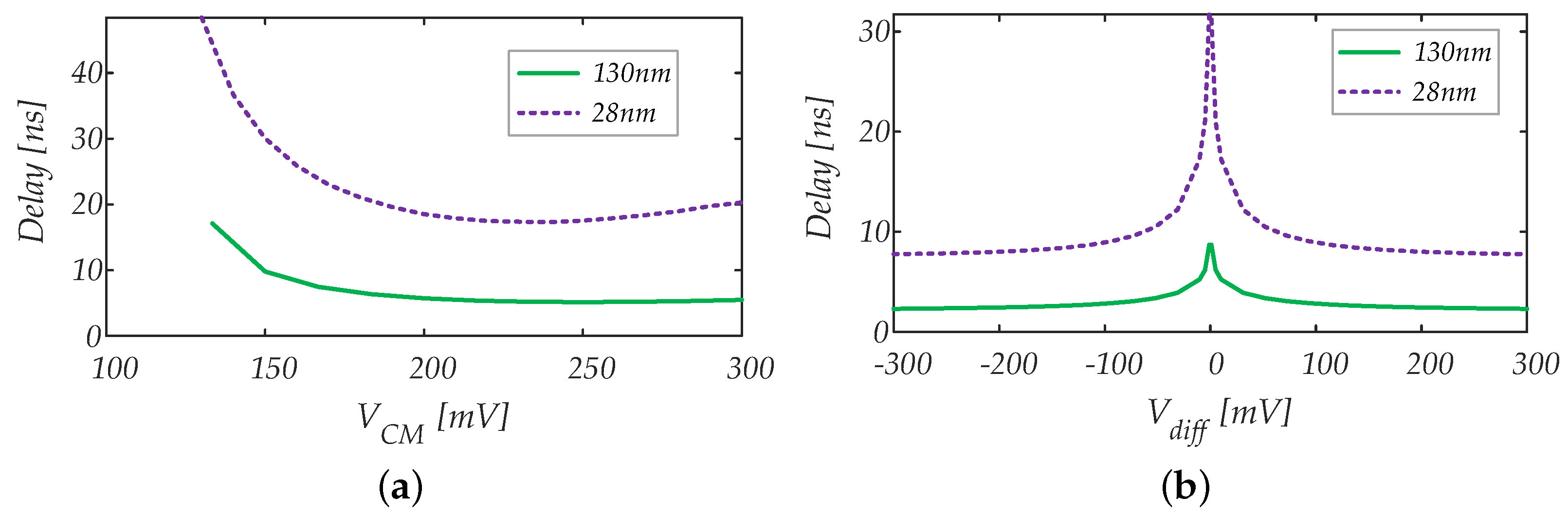

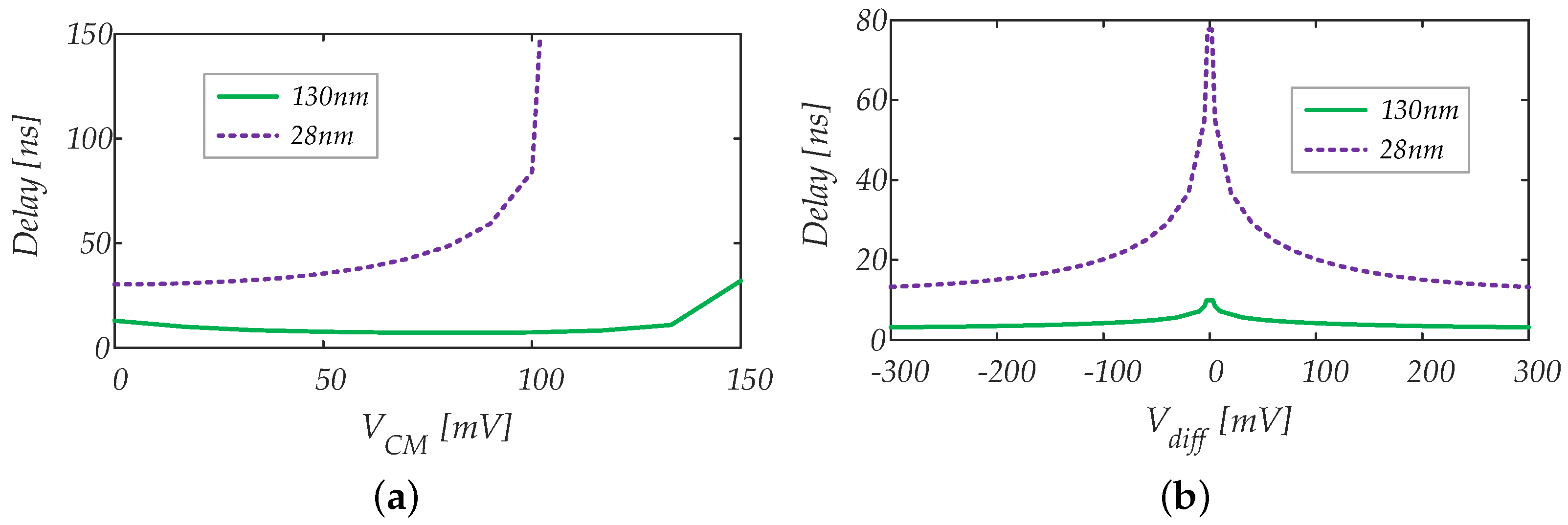

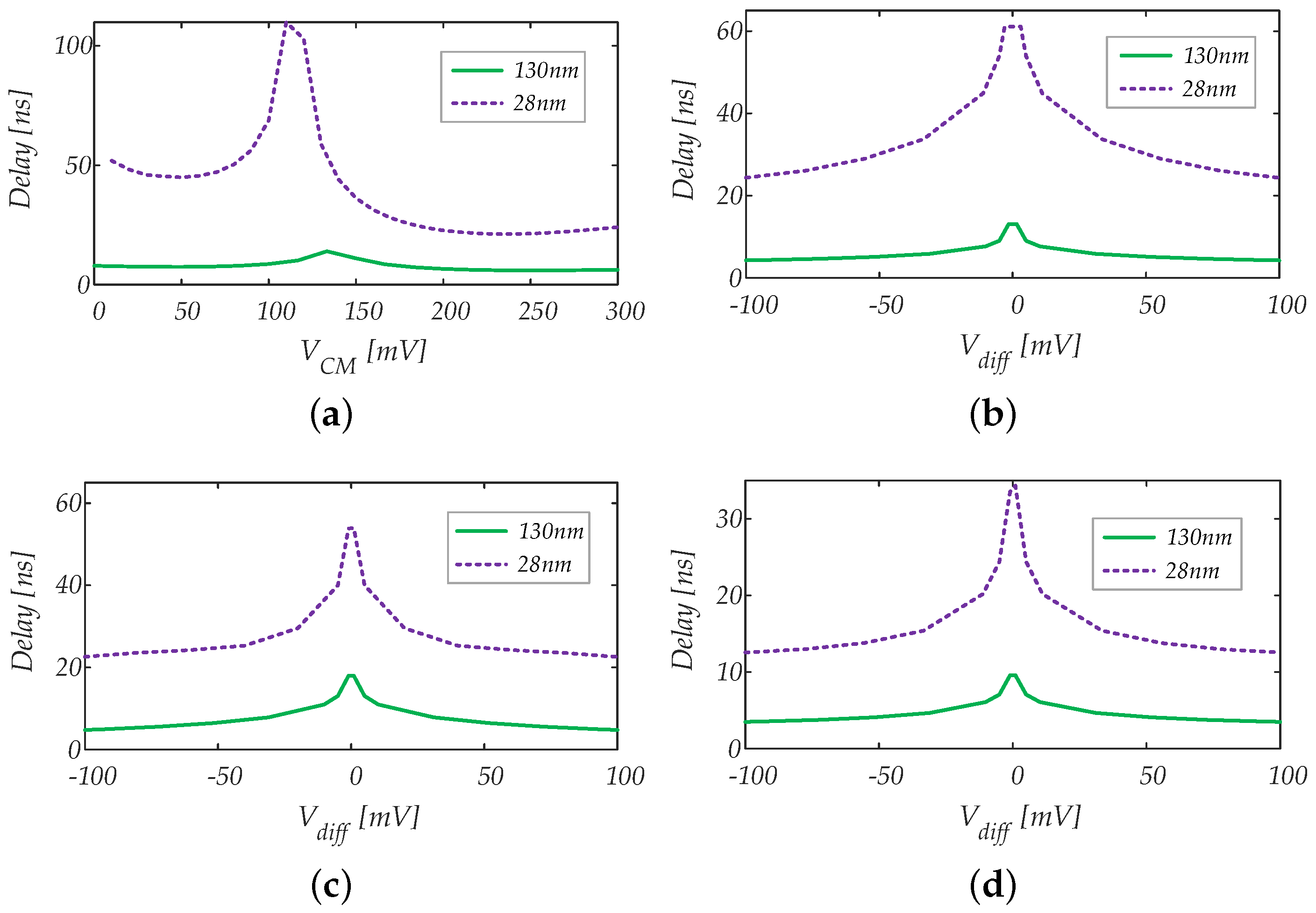

4.1.1. Propagation Delay vs. Input Common Mode Voltage

- Supply voltage V;

- Input common mode varied in the range between 0 and ;

- Differential input signal amplitude of 10 mV;

- Temperature of 27 °C.

4.1.2. Propagation Delay vs. Input Differential Signal Amplitude

- V;

- Input common mode voltage set at , and ;

- Temperature set at 27 °C.

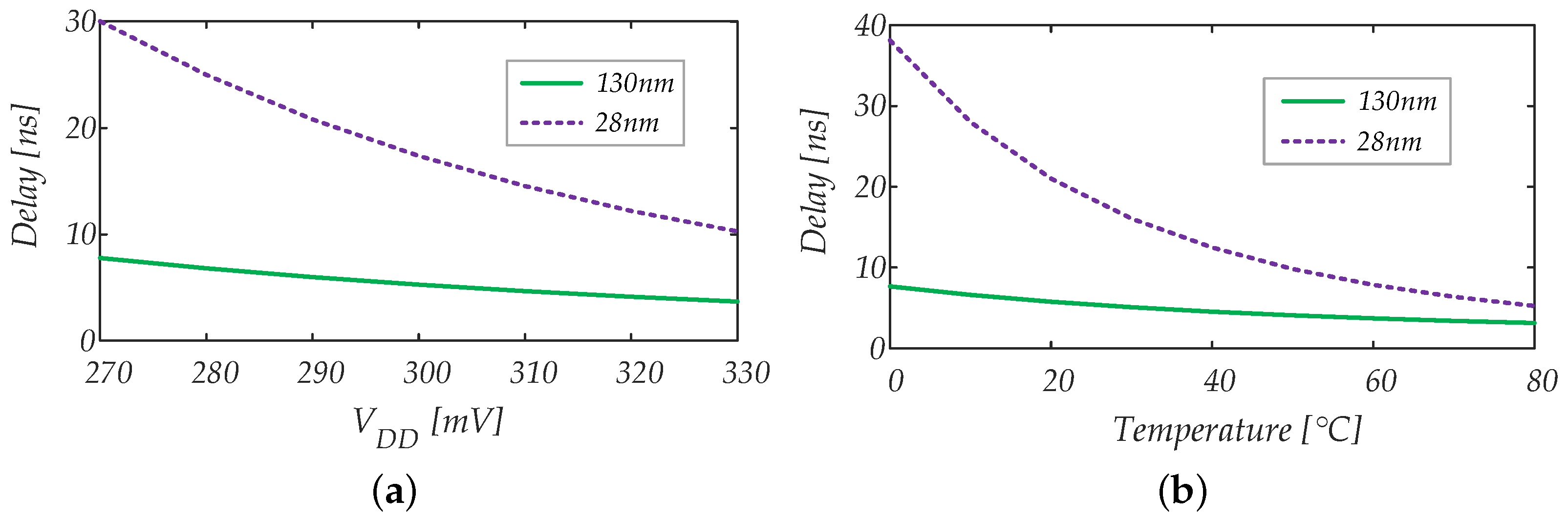

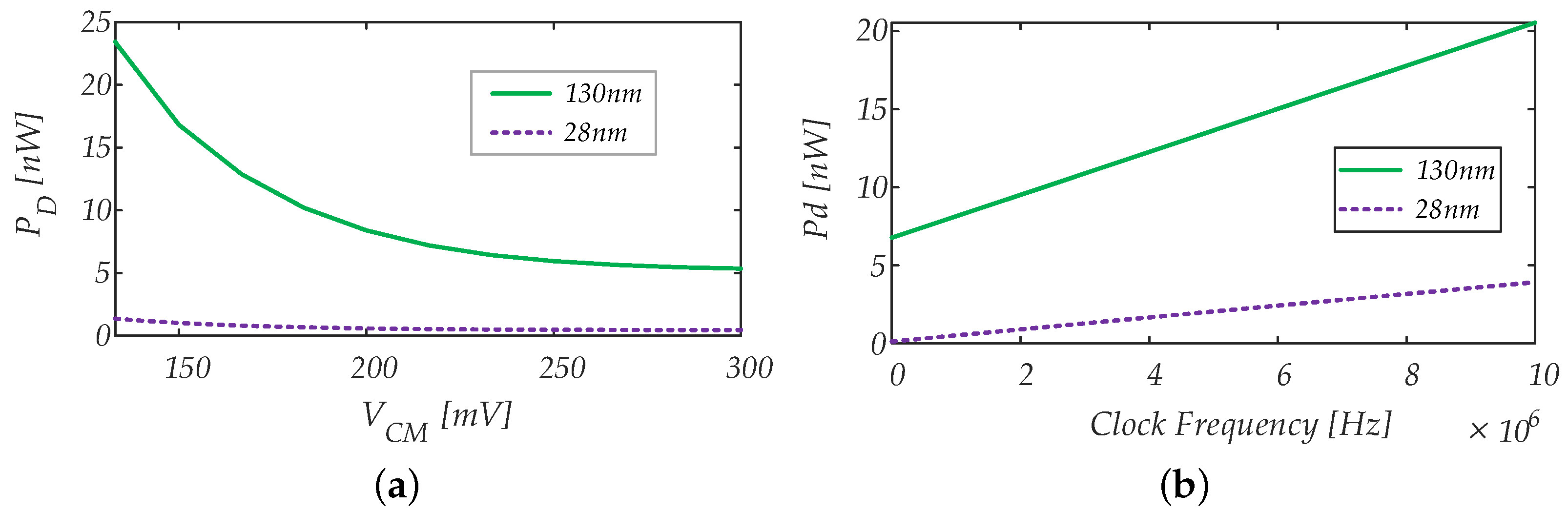

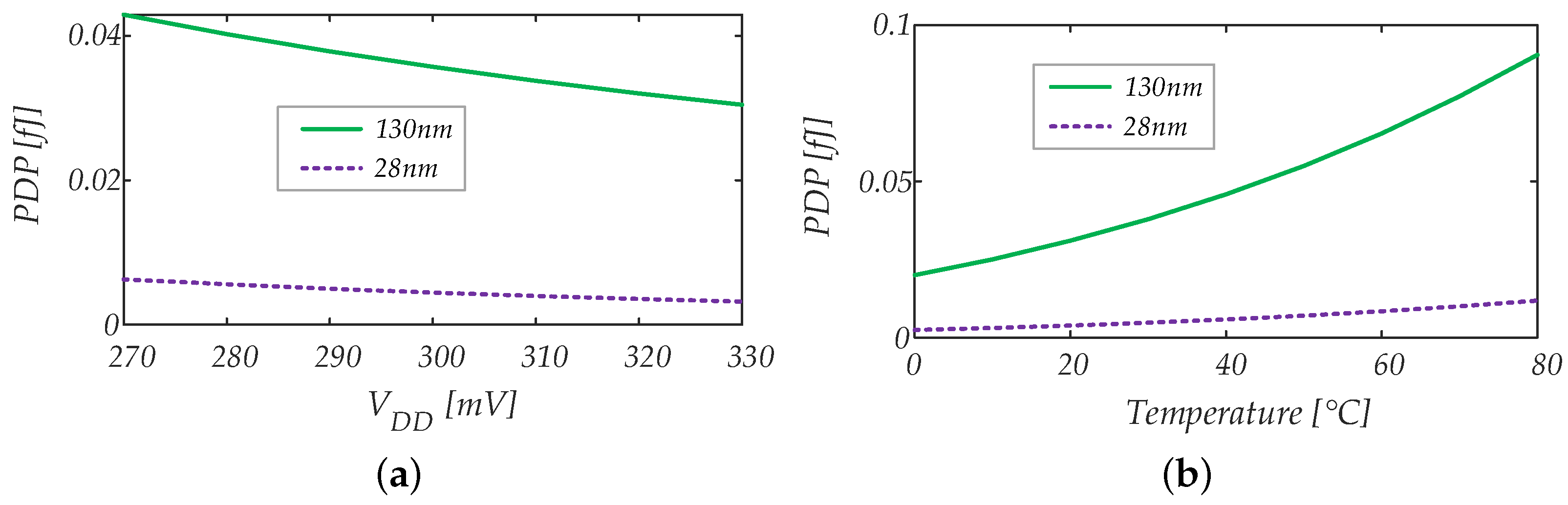

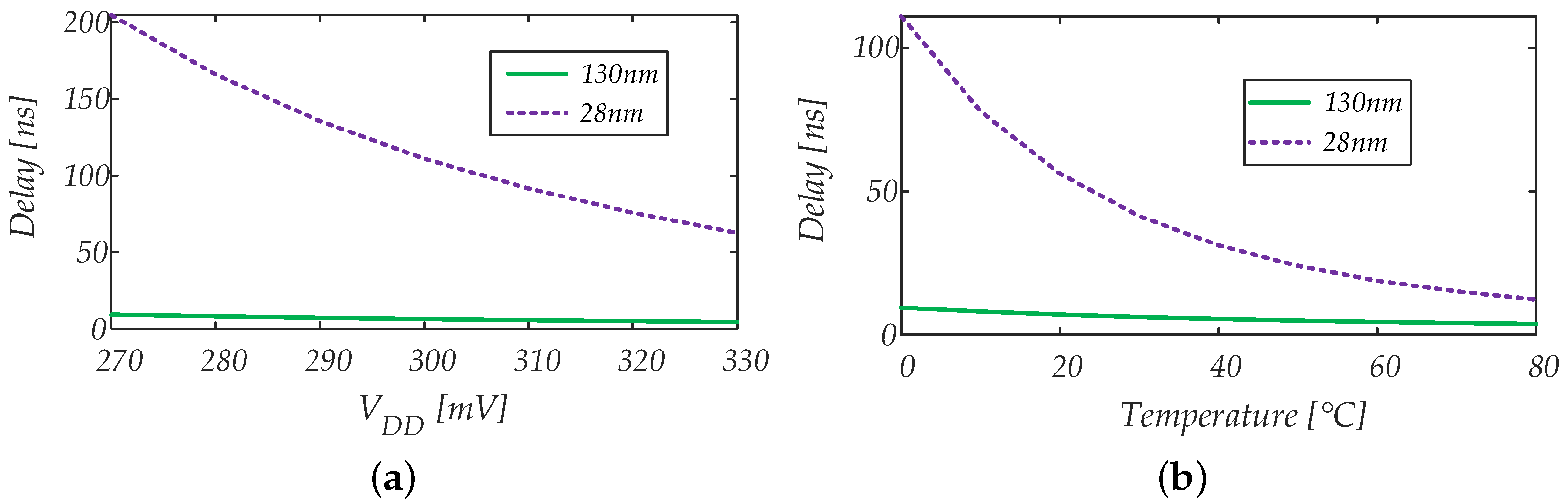

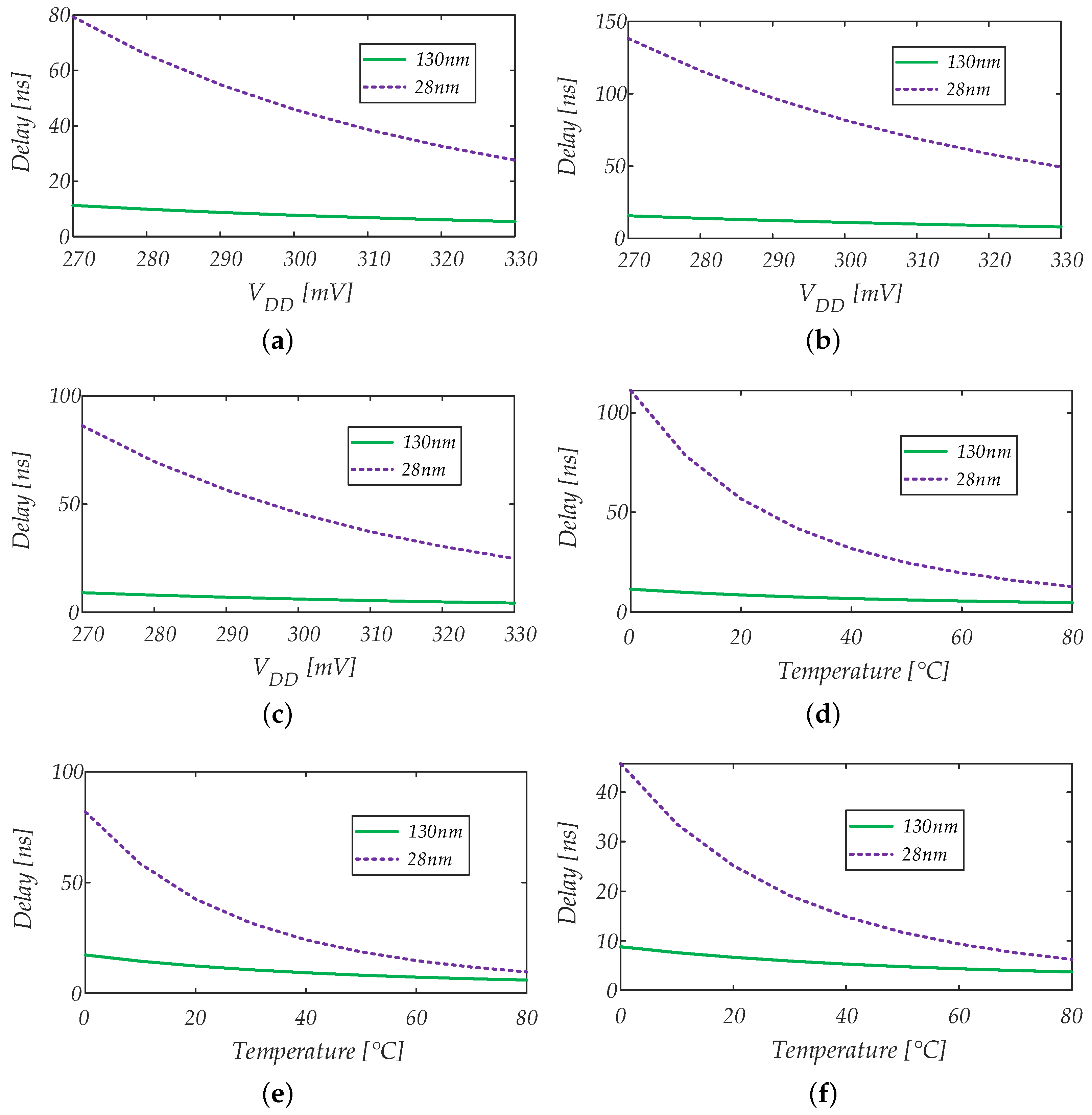

4.1.3. Power Consumption vs. Input Common Mode Voltage, Supply Voltage and Temperature Variations

- V ± 10%;

- A differential input signal amplitude of 10 mV;

- A clock frequency set at 10 Hz and at 10 MHz;

- A temperature varying from 0 to 80 °C.

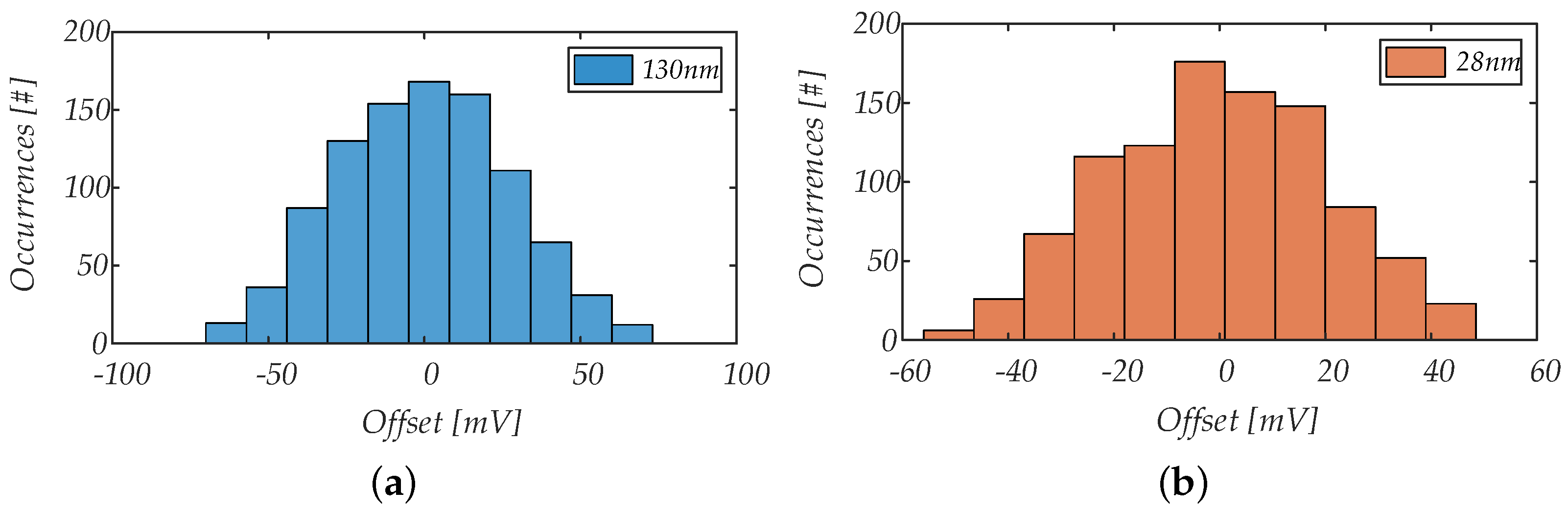

4.1.4. Input Offset Voltage vs. Supply Voltage, Temperature and Mismatch Variations

- = 0.3 V;

- An input signal varying linearly with time in a transient simulation;

- A differential input signal amplitude ranging from −70 mV to +70 mV;

- Monte Carlo simulations using statistical models provided by IC manufacturers are used to account for technology mismatches;

- 1000 Monte Carlo runs have been performed on each topology.

4.2. Figures of Merit Definition

4.3.

4.4. A Universal FoM

5. Simulation Results

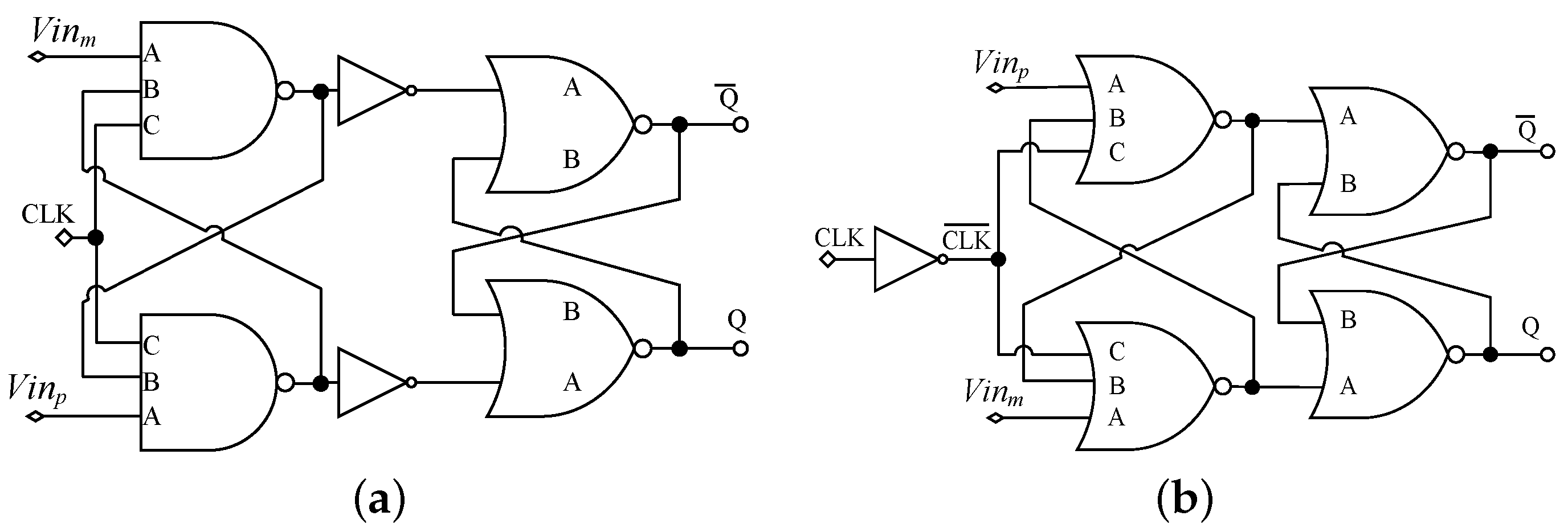

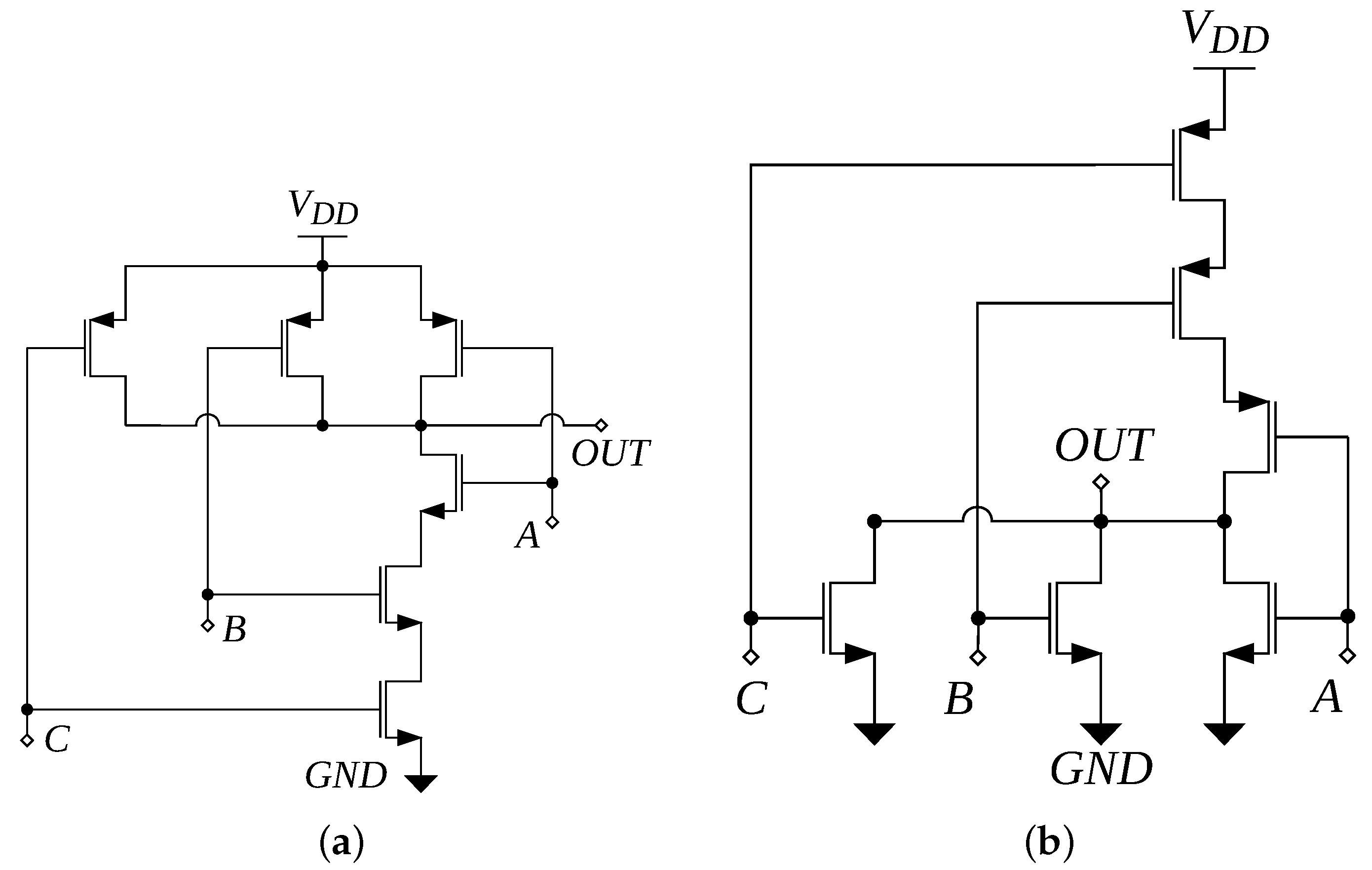

5.1. -Based Comparator

5.1.1. Propagation Delay

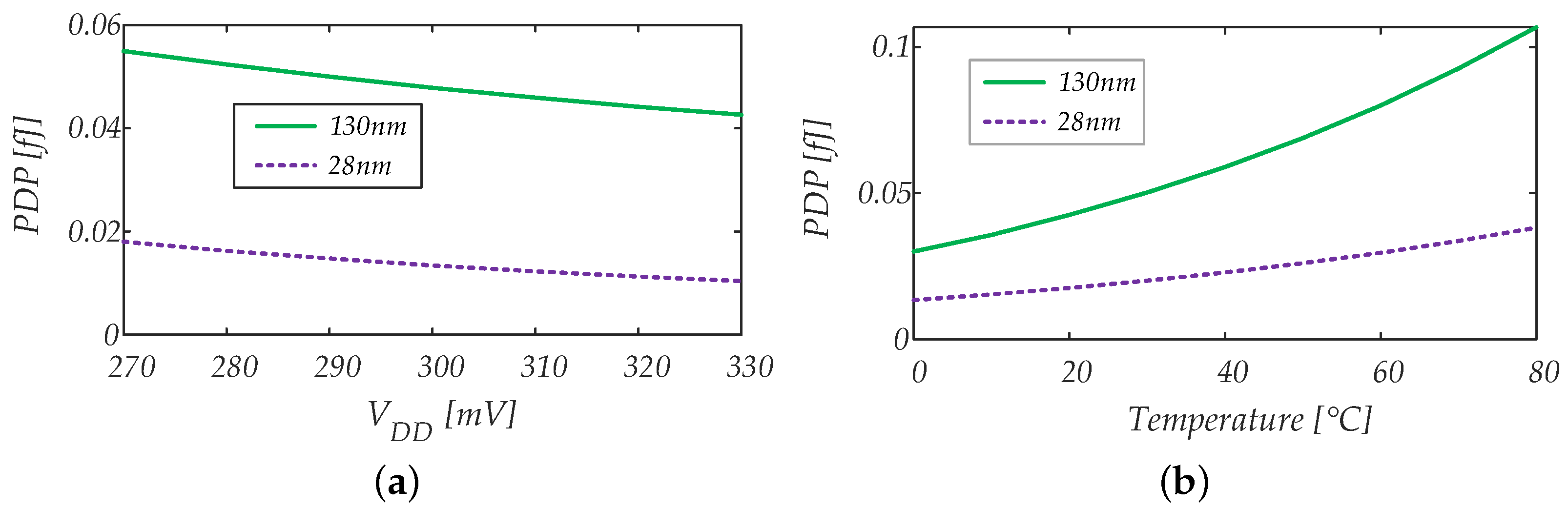

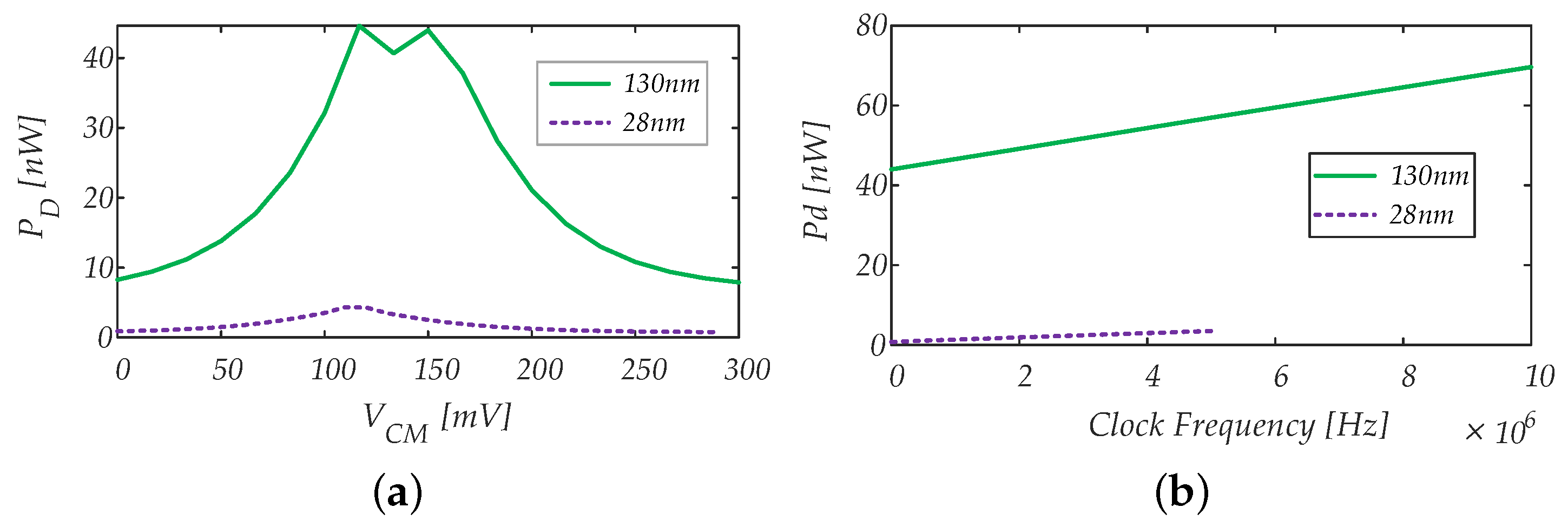

5.1.2. Power Consumption and Power–Delay Product

- The minimum-sized gates in 28 nm exhibit a much lower parasitic capacitance than the minimum-sized gates in 130 nm, thus resulting in much lower dynamic power;

- The transistors of the considered 130 nm technology exhibit a lower threshold voltage compared to the transistors of the considered 28 nm FDSOI technology, and this results in deeper subthreshold operation for the 28 nm transistors at = 0.3 V, resulting in much lower static power consumption for the 28 nm technology.

5.1.3. Offset

5.2. -Based Comparator

5.2.1. Propagation Delay

5.2.2. Power Consumption and Power–Delay Product

5.2.3. Offset

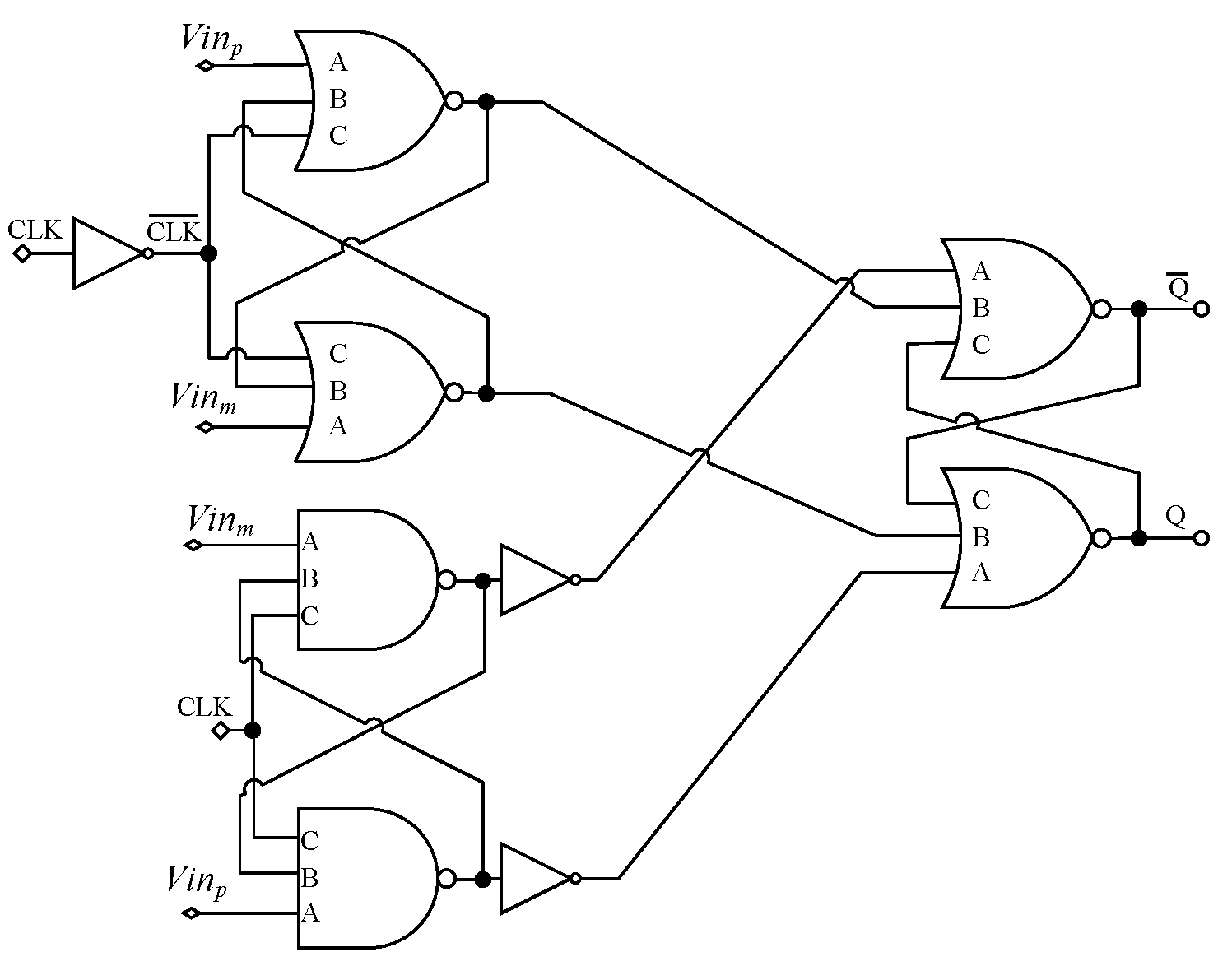

5.3. Rail-to-Rail ICMR Standard-Cell Comparator

5.3.1. Propagation Delay

5.3.2. Power Consumption and Power–Delay Product

5.3.3. Offset

6. Comparison

6.1. Comparison in ULV Conditions

6.2. Comparison at Higher Supply Voltages

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Sumanen, L.; Waltari, M.; Halonen, K.A.I. A 10-bit 200-MS/s CMOS parallel pipeline A/D converter. IEEE J. Solid-State Circuits 2001, 36, 1048–1055. [Google Scholar] [CrossRef]

- Lin, J.; Haroun, B. An embedded 0.8 V/480 /spl mu/W 6b/22 MHz flash ADC in 0.13-/spl mu/m digital CMOS process using a nonlinear double interpolation technique. IEEE J. Solid-State Circuits 2002, 37, 1610–1617. [Google Scholar] [CrossRef]

- Fahmy, A.; Liu, J.; Kim, T.; Maghari, N. An all-digital scalable and reconfigurable wide-input range stochastic ADC using only standard cells. IEEE Trans. Circuits Syst. II 2015, 62, 731–735. [Google Scholar] [CrossRef]

- Kadayinti, N.; Sharma, D.K. Sense amplifier comparator with offset correction for decision feedback equalization based receivers. Microelectron. J. 2017, 70, 27–33. [Google Scholar] [CrossRef]

- Gandhi, P.P.; Devashrayee, N.M. A novel low offset low power CMOS dynamic comparator. Analog. Integr. Circ. Sig. Process. 2018, 96, 147–158. [Google Scholar] [CrossRef]

- Xu, Z.; Ojima, N.; Li, S.; Iizuka, T. An all-standard-cell-based synthesizable SAR ADC with nonlinearity-compensated RDAC. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2021, 29, 2153–2162. [Google Scholar] [CrossRef]

- Weaver, S.; Hershberg, B.; Moon, U.K. Digitally synthesized stochastic flash ADC using only standard digital cells. IEEE Trans. Circ. Syst. I 2014, 61, 84–91. [Google Scholar] [CrossRef]

- Seo, M.J.; Roh, Y.J.; Chang, D.J.; Kim, W.; Kim, Y.D.; Ryu, S.T. A reusable code-based SAR ADC design with CDAC compiler and synthesizable analog building blocks. IEEE Trans. Circuits Syst. II 2018, 65, 1904–1908. [Google Scholar] [CrossRef]

- Park, J.E.; Hwang, Y.H.; Jeong, D.K. A 0.5-V fully synthesizable SAR ADC for on-chip distributed waveform monitors. IEEE Access 2019, 7, 63686–63697. [Google Scholar] [CrossRef]

- Sood, L.; Agarwal, A. A CMOS standard-cell based fully-synthesizable low-dropout regulator for ultra-low power applications. AEU Int. J. Electron. Commun. 2021, 141, 153958. [Google Scholar] [CrossRef]

- Wang, D.; Wang, Z.; Xu, H.; Wang, J.; Zhao, Z.; Zhang, C.; Wang, Z.; Chen, H. A 56-Gbps PAM-4 wireline receiver with 4-tap direct DFE employing dynamic CML comparators in 65 nm CMOS. IEEE Trans. Circ. Syst. I 2022, 69, 1027–1040. [Google Scholar] [CrossRef]

- Kobayashi, T.; Nogami, K.; Shirotori, T.; Fujimoto, Y.; Watanabe, O. A current-mode latch sense amplifier and a static power saving input buffer for low-power architecture. In Proceedings of the 1992 Symposium on VLSI Circuits, Seattle, WA, USA, 4–6 June 1992; IEEE: Piscataway, NJ, USA, 1992; pp. 28–29. [Google Scholar] [CrossRef]

- Montiel-Nelson, J.A.; Navarro, V.; Sosa, J.; Bautista, T. Analysis and optimization of dynamically reconfigurable regenerative comparators for ultra-low power 6-bit TC-ADCs in 90nm CMOS technologies. Microelectron. J. 2014, 45, 1247–1253. [Google Scholar] [CrossRef]

- Razavi, B. The StrongARM latch. IEEE Solid-State Circuits Mag. 2015, 7, 12–17. [Google Scholar] [CrossRef]

- Schinkel, D.; Mensink, E.; Klumperink, E.; van Tuijl, E.; Nauta, B. A double-tail latch-type voltage sense amplifier with 18ps setup+hold time. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2007; IEEE: Piscataway, NJ, USA, 2007; pp. 314–605. [Google Scholar] [CrossRef]

- Babayan-Mashhadi, S.; Lotfi, R. Analysis and design of a low-voltage low-power double-tail comparator. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2014, 22, 343–352. [Google Scholar] [CrossRef]

- Khorami, A.; Sharifkhani, M. A low-power high-speed comparator for precise applications. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2018, 26, 2038–2049. [Google Scholar] [CrossRef]

- Chevella, S.; O’Hare, D.; O’Connell, I. A Low-Power 1-V supply dynamic comparator. IEEE Solid-State Circuits Lett. 2020, 3, 154–157. [Google Scholar] [CrossRef]

- Mehr, I.; Dalton, D. A 500-MSample/s, 6-bit Nyquist-rate ADC for disk-drive read-channel applications. IEEE J. Solid-State Circuits 1999, 34, 912–920. [Google Scholar] [CrossRef]

- Usama, M.; Kwasniewski, T. Design and comparison of CMOS Current Mode Logic latches. In Proceedings of the 2004 IEEE International Symposium on Circuits and Systems (ISCAS), Vancouver, BC, Canada, 23–26 May 2004; IEEE: Piscataway, NJ, USA, 2004; Volume 4, pp. 353–356. [Google Scholar] [CrossRef]

- Goll, B.; Zimmermann, H. Low-power 600 MHz comparator for 0.5 V supply voltage in 0.12 μm CMOS. Electron. Lett. 2007, 43, 388–390. [Google Scholar] [CrossRef]

- Mohtashemi, D.; Green, M.M. A low-power 8-GS/s comparator for high-speed analog-to-digital conversion in 0.13 μm CMOS technology. IEEE Trans. Circuits Syst. II 2019, 66, 557–561. [Google Scholar] [CrossRef]

- Martins, R.; Lourenco, N.; Horta, N. LAYGEN II- Automatic layout generation of analog integrated circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2013, 32, 1641–1654. [Google Scholar] [CrossRef]

- Martins, R.; Lourenço, N.; Canelas, A.; Póvoa, R.; Horta, N. AIDA: Robust layout-aware synthesis of analog ICs including sizing and layout generation. In Proceedings of the 2015 International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Istanbul, Turkey, 7–9 September 2014; IEEE: Piscataway, NJ, USA, 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Maji, K.B.; Kar, R.; Mandal, D.; Ghoshal, S.P. An evolutionary approach based design automation of low power CMOS Two-Stage Comparator and Folded Cascode OTA. AEU Int. J. Electron. Commun. 2016, 70, 398–408. [Google Scholar] [CrossRef]

- Bashir, M.; Abbassi, F.; Misic, M.V.; Sturm, J.; Getnot, H. Performance comparison of BAG and custom generated analog layout for single-tail dynamic comparator. In Proceedings of the 2020 Austrochip Workshop on Microelectronics (Austrochip), Vienna, Austria, 7 October 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 37–41. [Google Scholar] [CrossRef]

- Settaluri, K.; Liu, Z.; Khurana, R.; Mirhaj, A.; Jain, R.; Nikolic, B. Automated design of analog circuits using reinforcement learning. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2022, 41, 2794–2807. [Google Scholar] [CrossRef]

- Patyal, A.; Chen, H.M.; Lin, M.P.H.; Fang, G.Q.; Chen, S.Y.H. Pole-aware analog layout synthesis considering monotonic current flows and wire crossings. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2022, 42, 266–279. [Google Scholar] [CrossRef]

- Newton, S.M.; Kinget, P.R. A 4th-order analog continuous-time filter designed using standard cells and automatic digital logic design tools. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 297–300. [Google Scholar] [CrossRef]

- Liu, J.; Park, B.; Guzman, M.; Fahmy, A.; Kim, T.; Maghari, N. A fully synthesized 77-dB SFDR reprogrammable SRMC filter using digital standard cells. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2018, 26, 1126–1138. [Google Scholar] [CrossRef]

- Liu, Y.; Zhang, B.; Cheng, X.; Han, J.; Zeng, X. A 0.9V all digital synthesizable OPAMP with boosted gain and widened common mode input range. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Centurelli, F.; Giustolisi, G.; Pennisi, S.; Scotti, G. A biasing approach to design ultra-low-power standard-cell-based analog building blocks for nanometer SoCs. IEEE Access 2022, 10, 25892–25900. [Google Scholar] [CrossRef]

- Centurelli, F.; Della Sala, R.; Scotti, G. A standard-cell-based CMFB for fully synthesizable OTAs. J. Low Power Electron. Appl. 2022, 12, 27. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G. Enabling ULV fully synthesizable analog circuits: The BA cell, a standard-cell-based building block for analog design. IEEE Trans. Circuits Syst. II 2022, 69, 4689–4693. [Google Scholar] [CrossRef]

- Toledo, P.; Rubino, R.; Musolino, F.; Crovetti, P. Re-thinking analog integrated circuits in digital terms: A new design concept for the IoT era. IEEE Trans. Circuits Syst. II 2021, 68, 816–822. [Google Scholar] [CrossRef]

- Crovetti, P.S. A digital-based analog differential circuit. IEEE Trans. Circ. Syst. I 2013, 60, 3107–3116. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Design of digital OTAs with operation down to 0.3 V and nW power for direct harvesting. IEEE Trans. Circ. Syst. I 2021, 68, 3693–3706. [Google Scholar] [CrossRef]

- Palumbo, G.; Scotti, G. A novel standard-cell-based implementation of the digital OTA suitable for automatic place and route. J. Low Power Electron. Appl. 2021, 11, 42. [Google Scholar] [CrossRef]

- Unnikrishnan, V.; Vesterbacka, M. Time-mode analog-to-digital conversion using standard cells. IEEE Trans. Circ. Syst. I 2014, 61, 3348–3357. [Google Scholar] [CrossRef]

- Ojima, N.; Xu, Z.; Iizuka, T. A 0.0053-mm2 6-bit fully-standard-cell-based synthesizable SAR ADC in 65 nm CMOS. In Proceedings of the 2019 17th IEEE International New Circuits and Systems Conference (NEWCAS), Munich, Germany, 23–26 June 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation. IEEE Access 2020, 8, 70890–70899. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.S.; Alioto, M. Fully synthesizable low-area digital-to-analog converter with graceful degradation and dynamic power-resolution scaling. IEEE Trans. Circ. Syst. I 2019, 66, 2865–2875. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Standard cell-based ultra-compact DACs in 40-nm CMOS. IEEE Access 2019, 7, 126479–126488. [Google Scholar] [CrossRef]

- Park, Y.; Wentzloff, D.D. An all-digital PLL synthesized from a digital standard cell library in 65nm CMOS. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–21 September 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Deng, W.; Yang, D.; Ueno, T.; Siriburanon, T.; Kondo, S.; Okada, K.; Matsuzawa, A. A fully synthesizable all-digital PLL with interpolative phase coupled oscillator, current-output DAC, and fine-resolution digital varactor using gated edge injection technique. IEEE J. Solid-State Circuits 2015, 50, 68–80. [Google Scholar] [CrossRef]

- Liu, J.; Maghari, N. A fully-synthesizable 0.6 V digital LDO with dual-loop control using digital standard cells. In Proceedings of the 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Vancouver, BC, Canada, 26–29 June 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Akram, M.A.; Hong, W.; Hwang, I.C. Fast transient fully standard-cell-based all digital low-dropout regulator with 99.97% current efficiency. IEEE Trans. Power Electron. 2018, 33, 8011–8019. [Google Scholar] [CrossRef]

- Ojima, N.; Nakura, T.; Iizuka, T.; Asada, K. A synthesizable digital low-dropout regulator based on voltage-to-time conversion. In Proceedings of the 2018 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Verona, Italy, 8–10 October 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 55–58. [Google Scholar] [CrossRef]

- Sood, L.; Agarwal, A. A transient-enhanced low-power standard-cell-based digital LDO. Arab. J. Sci. Eng. 2022, 47, 13943–13953. [Google Scholar] [CrossRef]

- Xu, B.; Li, S.; Sun, N.; Pan, D.Z. A scaling compatible, synthesis friendly VCO-based delta-sigma ADC design and synthesis methodology. In Proceedings of the 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, TX, USA, 18–22 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Li, S.; Xu, B.; Pan, D.Z.; Sun, N. A 60-fJ/step 11-ENOB VCO-based CTDSM synthesized from digital standard cell library. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Fully synthesizable, rail-to-rail dynamic voltage comparator for operation down to 0.3 V. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Li, X.; Zhou, T.; Ji, Y.; Li, Y. A 0.35 V-to-1.0 V synthesizable rail-to-rail dynamic voltage comparator based OAI&AOI logic. Analog. Integr.Circ. Sig. Process. 2020, 104, 351–357. [Google Scholar] [CrossRef]

- Aiello, O.; Toledo, P. Temperature characterization of a fully-synthesizable rail-to-rail dynamic voltage comparator operating down to 0.15-V. In Proceedings of the 2021 19th IEEE International New Circuits and Systems Conference (NEWCAS), Toulon, France, 13–16 June 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Toledo, P.; Alioto, M. Rail-to-rail dynamic voltage comparator scalable down to pW-range power and 0.15-V supply. IEEE Trans. Circuits Syst. II 2021, 68, 2675–2679. [Google Scholar] [CrossRef]

- Zhou, T.; Li, X.; Ji, Y.; Li, Y. A 0.25-1.0 V fully synthesizable three-stage dynamic voltage comparator based XOR & XNOR & NAND & NOR logic. Analog. Integr.Circ. Sig. Process. 2021, 108, 221–228. [Google Scholar] [CrossRef]

- Li, M.; Wang, J.; Cheng, X.; Zeng, X. A fully synthesizable dynamic latched comparator with reduced kickback noise. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 2876–2880. [Google Scholar] [CrossRef]

- Wicht, B.; Nirschl, T.; Schmitt-Landsiedel, D. Yield and speed optimization of a latch-type voltage sense amplifier. IEEE J. Solid-State Circuits 2004, 39, 1148–1158. [Google Scholar] [CrossRef]

- Savani, V.; Devashrayee, N.M. Analysis of power for double-tail current dynamic latch comparator. Analog. Integr.Circ. Sig. Process. 2019, 100, 345–355. [Google Scholar] [CrossRef]

- Xu, H.; Abidi, A.A. Analysis and design of regenerative comparators for low offset and noise. IEEE Trans. Circ. Syst. I 2019, 66, 2817–2830. [Google Scholar] [CrossRef]

- Pelgrom, M.J.M. Comparators. In Analog-to-Digital Conversion; Springer: Cham, Switzerland, 2021; pp. 599–641. [Google Scholar] [CrossRef]

- Veendrick, H.J.M. The behaviour of flip-flops used as synchronizers and prediction of their failure rate. IEEE J. Solid-State Circuits 1980, 15, 169–176. [Google Scholar] [CrossRef]

- Juan-Chico, J.; Bellido, M.J.; Acosta, A.J.; Valencia, M.; Huertas, J.L. Analysis of metastable operation in a CMOS dynamic D-latch. Analog. Integr. Circuits Signal Process. 1997, 14, 143–157. [Google Scholar] [CrossRef]

- Figueiredo, P.M. Comparator metastability in the presence of noise. IEEE Trans. Circ. Syst. I 2013, 60, 1286–1299. [Google Scholar] [CrossRef]

- Razavi, B. The design of a comparator. IEEE Solid-State Circuits Mag. 2020, 12, 8–14. [Google Scholar] [CrossRef]

- He, J.; Zhan, S.; Chen, D.; Geiger, R.L. Analyses of static and dynamic random offset voltages in dynamic comparators. IEEE Trans. Circ. Syst. I 2009, 56, 911–919. [Google Scholar] [CrossRef]

- Nuzzo, P.; De Bernardinis, F.; Terreni, P.; Van der Plas, G. Noise analysis of regenerative comparators for reconfigurable ADC architectures. IEEE Trans. Circ. Syst. I 2008, 55, 1441–1454. [Google Scholar] [CrossRef]

- Kim, J.; Leibowitz, B.S.; Ren, J.; Madden, C.J. Simulation and analysis of random decision errors in clocked comparators. IEEE Trans. Circ. Syst. I 2009, 56, 1844–1857. [Google Scholar] [CrossRef]

- Lei, K.M.; Mak, P.I.; Martins, R.P. Systematic analysis and cancellation of kickback noise in a dynamic latched comparator. Analog. Integr.Circ. Sig. Process. 2013, 77, 277–284. [Google Scholar] [CrossRef]

- Sundstrom, T.; Alvandpour, A. Utilizing process variations for reference generation in a flash ADC. IEEE Trans. Circuits Syst. II 2009, 56, 364–368. [Google Scholar] [CrossRef]

- Weaver, S.; Hershberg, B.; Kurahashi, P.; Knierim, D.; Moon, U.K. Stochastic flash analog-to-digital conversion. IEEE Trans. Circ. Syst. I 2010, 57, 2825–2833. [Google Scholar] [CrossRef]

- Jeon, M.K.; Yoo, W.J.; Kim, C.G.; Yoo, C. A stochastic flash analog-to-digital converter linearized by reference swapping. IEEE Access 2017, 5, 23046–23051. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Urkin, T.; Abramov, E.; Peretz, M.M. Enhanced performance fully-synthesizable ∑Δ ADC for efficient digital voltage-mode control. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padua, Italy, 25–28 June 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–8. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A 0.3 V Rail-to-Rail Three-Stage OTA with High DC Gain and Improved Robustness to PVT Variations. IEEE Access 2023, 11, 19635–19644. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. A 0.3-V 98-dB Rail-to-Rail OTA in 0.18 μm CMOS. IEEE Access 2020, 8, 27459–27467. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F.; Kumngern, M. 0.3-V nanopower biopotential low-pass filter. IEEE Access 2020, 8, 119586–119593. [Google Scholar] [CrossRef]

| Topology | [7]-NAND | [7]-NOR | [52,55] | [7]-NAND | [7]-NOR | [52,55] |

|---|---|---|---|---|---|---|

| Technology node (nm) | 130 | 130 | 130 | 28 | 28 | 28 |

| Area | 36.50 | 27.74 | 60.80 | 3.264 | 2.62 | 5.22 |

| Normalized area | 2160 | 1641 | 3598 | 4163 | 3342 | 6658 |

| 0.3 | 0.3 | 0.3 | 0.3 | 0.3 | 0.3 | |

| Input Common Mode Range (min-max ) | 125–300 | 0–150 | 0–300 | 125–300 | 0–110 | 0–300 |

| Input offset (, ) | −1.1, 24.2 | −1.4, 23.8 | 4.4, 15.7 | −0.4, 19.4 | −2.3, 22.6 | 2.6, 19.6 |

| Delay @ | - | 6.34 | 7.71 | - | 111.0 | 111.26 |

| Delay @ | - | - | 11.01 | - | - | 81.80 |

| Delay @ | 5.27 | - | 6.1 | 38.12 | - | 45.76 |

| @ | - | 7.55 | 20.37 | - | 0.122 | 0.333 |

| @ | - | - | 43.98 | - | - | 0.378 |

| @ | 6.77 | - | 14.45 | 0.063 | - | 0.124 |

| PDP @ | - | 0.048 | 0.156 | - | 0.0134 | 0.0367 |

| PDP @ | - | - | 0.483 | - | - | 0.0309 |

| PDP @ | 0.035 | - | 0.087 | 0.0024 | - | 0.0056 |

| @ best | 2. 82 | 3.808 | 4.553 | 0.155 | 1.009 | 0.365 |

| @ best | 20.41 | 24 | 87 | 1.4 | 4.913 | 5.6 |

| @ best | 4.84 | 7.616 | 4.553 | 0.266 | 2.753 | 0.365 |

| @ best | 10.45 | 12.50 | 16.38 | 1.107 | 9.200 | 2.436 |

| Topology | [7]-NAND | [7]-NOR | [52,55] | [7]-NAND | [7]-NOR | [52,55] | [7]-NAND | [7]-NOR | [52,55] |

|---|---|---|---|---|---|---|---|---|---|

| 0.6 | 0.9 | 1.2 | |||||||

| technology | 130 | 130 | 130 | 130 | 130 | 130 | 130 | 130 | 130 |

| area | 36.50 | 27.74 | 60.80 | 36.50 | 27.74 | 60.80 | 36.50 | 27.74 | 60.80 |

| Area normalized | 2160 | 1641 3 | 598 | 2160 | 1641 | 3598 | 2160 | 1641 | 3598 |

| Input Common Mode Range (min-max ) | 0.26–0.6 | 0–0.3 | 0–0.6 | 0.38–0.9 | 0–0.430 | 0–0.6 | 0.485–1.2 | 0–0.57 | 0–1.2 |

| input offset () | 9.33 | 13.15 | 8.9 | 19.4 | 10 | 15.9 | 9.8 | 22.6 | 19.6 |

| Delay @ | - | 623 | 731 | - | 325 | 350 | - | 266 | 276 |

| Delay @ | - | - | 841 | - | - | 297 | - | - | 207 |

| Delay @ | 468 | - | 554 | 205 | - | 249 | 148 | - | 181 |

| @ | - | 76.6 | 275 | - | 624 | 2495 | - | 3248 | 14,070 |

| @ | - | - | 1743 | - | - | 15,830 | - | - | 55,150 |

| @ | 52.8 | - | 172 | 417 | - | 1508 | 2438 | - | 8973 |

| PDP @ | - | 47.6 | 200 | - | 200 | 871 | - | 861 | 3675 |

| PDP @ | - | - | 1461 | - | - | 4676 | - | - | 11,350 |

| PDP @ | 24.69 | - | 94.7 | 85.4 | - | 375 | 360 | - | 1618 |

| @ best | 0.77 | 2.09 | 2.81 | 5.52 | 6.67 | 19.88 | 11.76 | 64.86 | 105.71 |

| @ best | 27.98 | 47.60 | 189.40 | 148.03 | 300.00 | 1125.00 | 858.00 | 1722.00 | 6472 |

| @ best | 0.68 | 2.09 | 1.40 | 3.19 | 4.44 | 6.63 | 4.93 | 32.43 | 26.43 |

| @ best | 1.46 | 3.42 | 5.05 | 6.88 | 7.30 | 23.83 | 10.66 | 53.23 | 95.08 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Della Sala, R.; Centurelli, F.; Scotti, G.; Palumbo, G. Standard-Cell-Based Comparators for Ultra-Low Voltage Applications: Analysis and Comparisons. Chips 2023, 2, 173-194. https://doi.org/10.3390/chips2030011

Della Sala R, Centurelli F, Scotti G, Palumbo G. Standard-Cell-Based Comparators for Ultra-Low Voltage Applications: Analysis and Comparisons. Chips. 2023; 2(3):173-194. https://doi.org/10.3390/chips2030011

Chicago/Turabian StyleDella Sala, Riccardo, Francesco Centurelli, Giuseppe Scotti, and Gaetano Palumbo. 2023. "Standard-Cell-Based Comparators for Ultra-Low Voltage Applications: Analysis and Comparisons" Chips 2, no. 3: 173-194. https://doi.org/10.3390/chips2030011

APA StyleDella Sala, R., Centurelli, F., Scotti, G., & Palumbo, G. (2023). Standard-Cell-Based Comparators for Ultra-Low Voltage Applications: Analysis and Comparisons. Chips, 2(3), 173-194. https://doi.org/10.3390/chips2030011