Current Density-Voltage (J-V) Characterization of Monolithic Nanolaminate Capacitors †

Abstract

1. Introduction

2. Materials and Methods

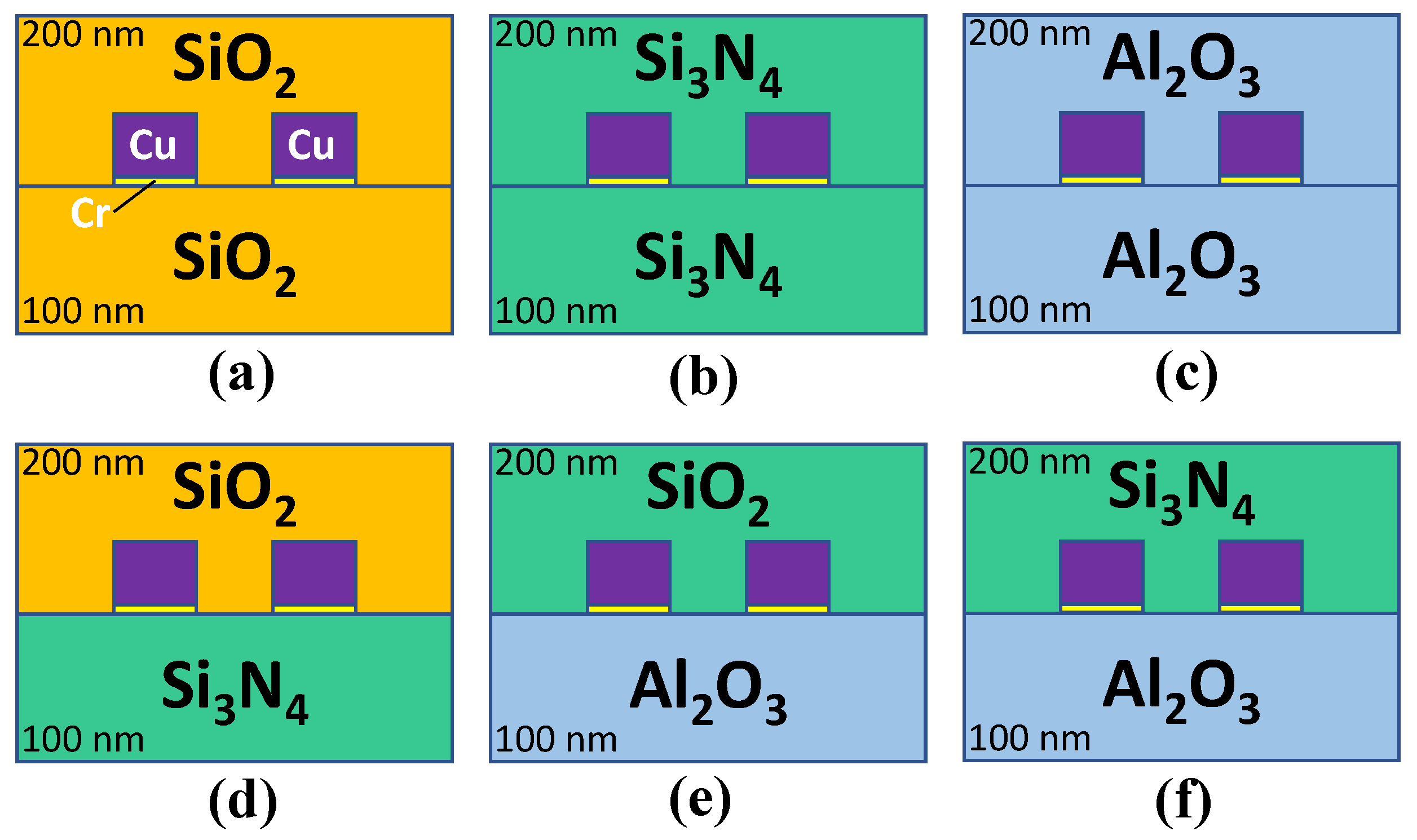

2.1. Overview of Fabrication of PPE and IDE Devices

2.2. Current-Voltage (I-V) Measurements

3. Results

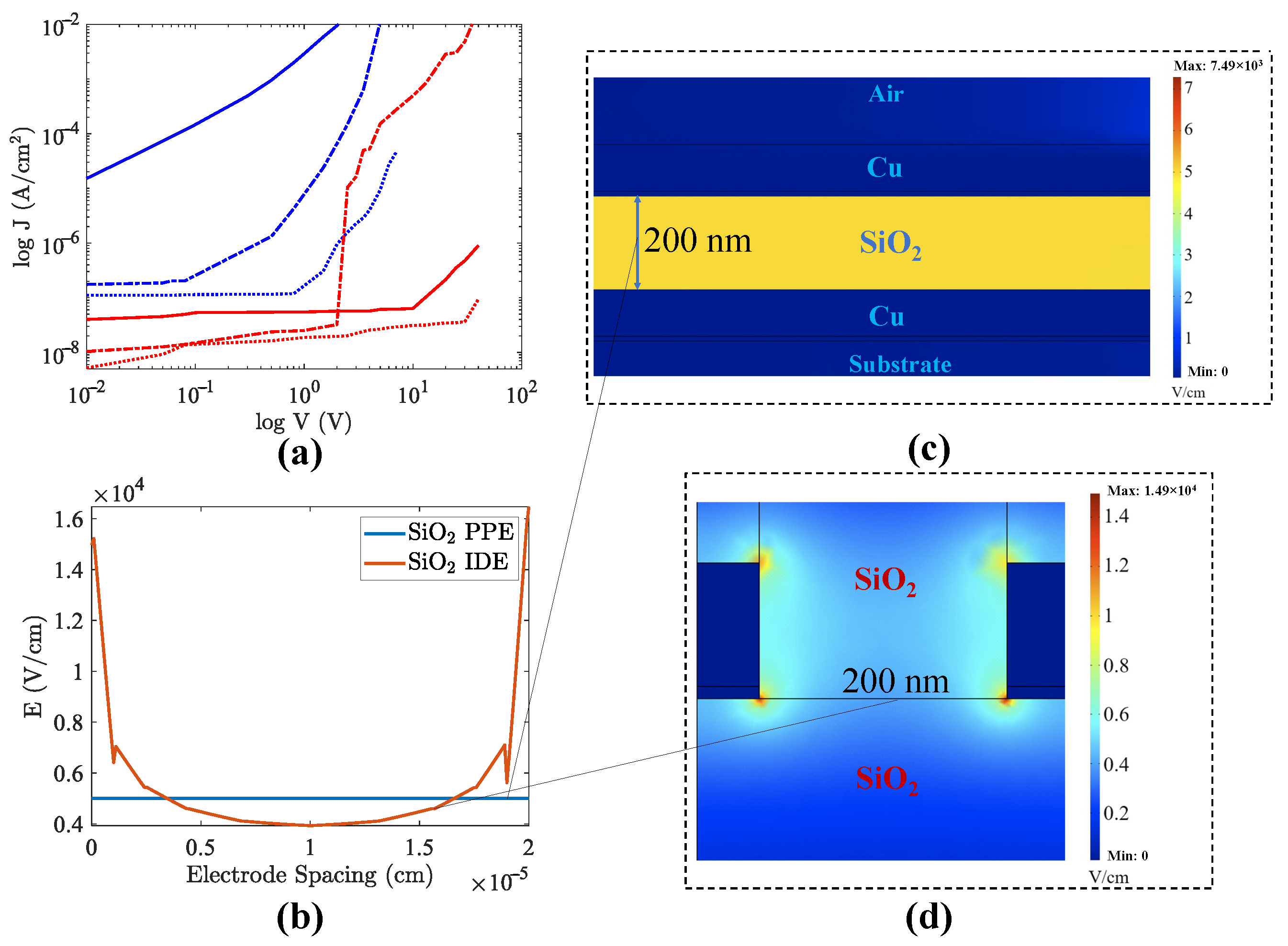

3.1. Homogeneous PPE and IDE Devices

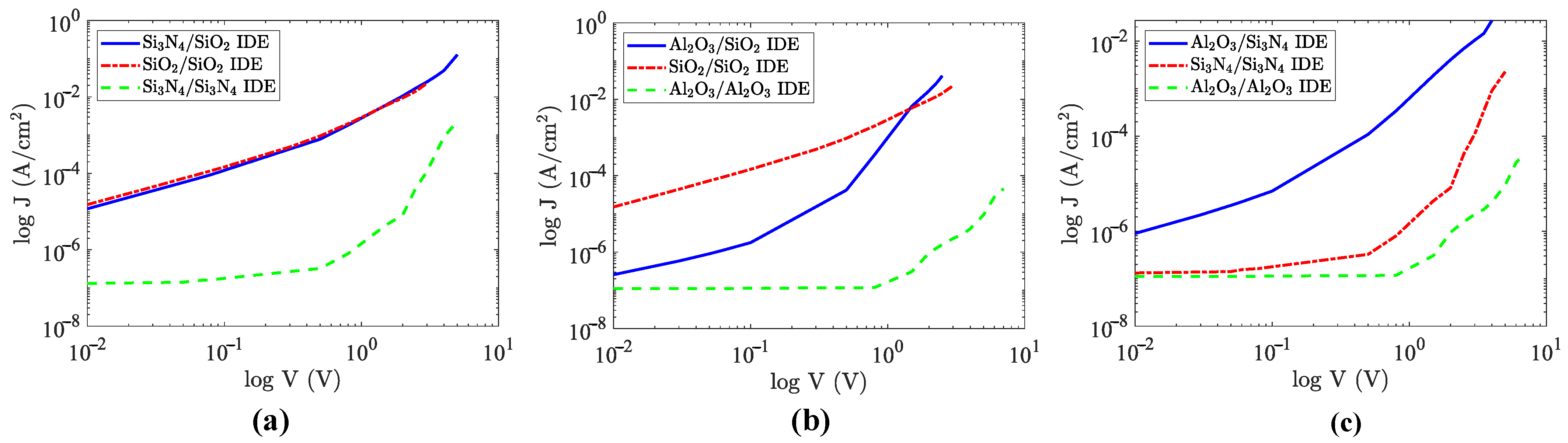

3.2. Homogeneous vs. Heterogeneous Structure in IDE Devices

4. Discussion

Potential Application of Ideal High-Density PPE Devices

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| IDE | Interdigitated Electrode |

| PPE | Parallel Plate Electrode |

| MNES | Multilayer Nanolaminate Energy Storage |

| FEM | Finite Element Method |

| PECVD | Plasma Enhanced Chemical Vapor Deposition |

| PMMA | Polymethylmethacrylate |

| EBL | Electron Beam Lithography |

| MIBK | Methyl Isobutyl Ketone |

| SEM | Scanning Electron Microscope |

References

- Signorelli, R.; Ku, D.C.; Kassakian, J.G.; Schindall, J.E. Electrochemical Double-Layer Capacitors Using Carbon Nanotube Electrode Structures. Proc. IEEE 2009, 97, 1837–1847. [Google Scholar] [CrossRef]

- Wu, Z.S.; Parvez, K.; Feng, X.; Müllen, K. Graphene-Based In-Plane Micro-Supercapacitors with High Power and Energy Densities. Nat. Commun. 2013, 4, 2487. [Google Scholar] [CrossRef] [PubMed]

- Sarkar, A.; Ranjith, R.; Krupanidhi, S.B. Nonlinear Dielectric Behavior in Three-Component Ferroelectric Superlattices. J. Appl. Phys. 2007, 102, 024108. [Google Scholar] [CrossRef]

- Singh, M.P.; Prellier, W. Oxide Superlattices for Mltiferroics: Opportunities, Issues, and Challenges. Philos. Mag. Lett. 2007, 87, 211–222. [Google Scholar] [CrossRef]

- Ang, C.; Yu, Z. High Capacitance-Temperature Sensitivity and “Giant” Dielectric Constant in SrTiO3. Appl. Phys. Lett. 2007, 90, 202903. [Google Scholar] [CrossRef]

- Ducharme, S. An Inside-Out Approach to Storing Electrostatic Energy. ACS Nano 2009, 3, 2447–2450. [Google Scholar] [CrossRef] [PubMed]

- Lee, G.; Lai, B.K.; Phatak, C.; Katiyar, R.S.; Auciello, O. Interface-Controlled High Dielectric Constant Al2O3/TiOx Nanolaminates with Low Loss and Low Leakage Current Density for New Generation Nanodevices. J. Appl. Phys. 2013, 114, 027001. [Google Scholar] [CrossRef]

- Coss, B.E.; Loh, W.Y.; Carlo Floresca, H.; Kim, M.J.; Majhi, P.; Wallace, R.M.; Kim, J.; Jammy, R. Dielectric Dipole Mitigated Schottky Barrier Height Tuning Using Atomic Layer Deposited Aluminum Oxide for Contact Resistance Reduction. Appl. Phys. Lett. 2011, 99, 102108. [Google Scholar] [CrossRef]

- Wu, Y.Q.; Lin, H.C.; Ye, P.D.; Wilk, G.D. Current Transport and Maximum Dielectric Strength of Atomic-Layer-Deposited Ultrathin Al2O3 on GaAs. Appl. Phys. Lett. 2007, 90, 072105. [Google Scholar] [CrossRef]

- Li, J.Y.; Zhang, L.; Ducharme, S. Electric Energy Density of Dielectric Nanocomposites. Appl. Phys. Lett. 2007, 90, 132901. [Google Scholar] [CrossRef]

- Mousavi Karimi, Z. Characterization and Modelling of Anomalous Properties of SiO2, Si3N4, and Al2O3 Nanolaminates. Ph.D. Thesis, Georgia Institute of Technology, Atlanta, GA, USA, 2021. [Google Scholar]

- Santos-Neto, I.S.D.; Carvalho, C.D.; Filho, G.B.A.; Andrade, C.D.S.S.; Santos, G.C.D.O.; Barros, A.K.; Neto, J.V.D.F.; Casas, V.L.P.; Alencar, L.M.R.; Lopes, A.J.O.; et al. Interdigitated Electrode for Electrical Characterization of Commercial Pseudo-Binary Biodiesel–Diesel Blends. Sensors 2021, 21, 7288. [Google Scholar] [CrossRef] [PubMed]

- Bowen, C.R.; Bowles, A.; Drake, S.; Johnson, N.; Mahon, S. Fabrication and Finite Element Modelling of Interdigitated Electrodes. Ferroelectrics 1999, 228, 257–269. [Google Scholar] [CrossRef]

- Mousavi Karimi, Z.; Davis, J.A. Interfacial Permittivity Characterization of Heterogeneous Dielectric Bi-Layers. IEEE Trans. Electron Devices 2022, 69, 1950–1955. [Google Scholar] [CrossRef]

- Mousavi Karimi, Z.; Davis, J.A. Permittivity Characterization of Dielectric Surfaces Using Nanofabricated In-Plane Capacitors. IEEE Trans. Electron Devices 2021, 68, 4033–4038. [Google Scholar] [CrossRef]

- McPherson, J.; Kim, J.; Shanware, A.; Mogul, H.; Rodriguez, J. Proposed Universal Relationship between Dielectric Breakdown and Dielectric Constant. In Proceedings of the Digest. International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; pp. 633–636. [Google Scholar]

- Lin, H.C.; Ye, P.D.; Wilk, G.D. Leakage Current and Breakdown Electric-Field Studies on Ultrathin Atomic-Layer-Deposited Al2O3 on GaAs. Appl. Phys. Lett. 2005, 87, 182904. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mousavi Karimi, Z.; Davis, J.A. Current Density-Voltage (J-V) Characterization of Monolithic Nanolaminate Capacitors. Mater. Proc. 2023, 14, 54. https://doi.org/10.3390/IOCN2023-14590

Mousavi Karimi Z, Davis JA. Current Density-Voltage (J-V) Characterization of Monolithic Nanolaminate Capacitors. Materials Proceedings. 2023; 14(1):54. https://doi.org/10.3390/IOCN2023-14590

Chicago/Turabian StyleMousavi Karimi, Zeinab, and Jeffrey A. Davis. 2023. "Current Density-Voltage (J-V) Characterization of Monolithic Nanolaminate Capacitors" Materials Proceedings 14, no. 1: 54. https://doi.org/10.3390/IOCN2023-14590

APA StyleMousavi Karimi, Z., & Davis, J. A. (2023). Current Density-Voltage (J-V) Characterization of Monolithic Nanolaminate Capacitors. Materials Proceedings, 14(1), 54. https://doi.org/10.3390/IOCN2023-14590