A typical CNTFET structure is mainly composed of carbon nanotubes as conductive channels, a gate, a source, and a drain. The electric field applied through the gate can effectively regulate the transport of charge carriers in the CNT channel. According to the geometric layout of the gate relative to the CNT channel, CNTFET devices can be mainly divided into three mainstream structures: bottom-gate (BG), top-gate (TG), and gate-all-around (GAA). The gate of the BG-CNTFET is located on the substrate below the CNT channel and isolated from the channel by a dielectric layer. The manufacturing process of such devices is relatively simple. However, due to the typically thick gate dielectric layer, the electrostatic control ability of the gate over the channel is relatively limited, making it more commonly used in low-frequency analog circuits [

25]. The TG-CNTFET directly deposits a high-k gate dielectric above the CNT channel, which can significantly enhance gate control capability and increase driving current. Therefore, it is widely used in the design of high-performance logic circuits and carbon–silicon-heterojunction-integrated static random access memory (SRAM) cells [

26]. The GAA-CNTFET has the best electrostatic control capability and excellent suppression performance for short-channel effects. However, its manufacturing process is extremely complex and requires precise alignment technology at the nanoscale. Currently, it is mainly aimed at cutting-edge applications such as ultra-low power nanoelectronic devices and emerging quantum computing units [

27].

Pd is used as the source/drain contact metal, and the gate electrode consists of Ti/Au. Above the local bottom gate, a dielectric stack of Y2O3/HfO2 is deposited, followed by placement of the carbon nanotube channel and subsequent deposition of source/drain metals. In certain regions, the source/drain metal partially overlaps with the gate metal. The channel length is 4 µm, and the channel width is 30 µm. Following device fabrication, a surface electrical modification layer is deposited to electrostatically dope the transistor into n-type. Then, wet etching is applied to remove this modification layer in regions intended to retain p-type contact. Finally, an electron-beam resist passivation layer is deposited over the device.

Directly solving Equation (1), which involves complex transmission probability calculations and high-dimensional energy integration, poses significant challenges in terms of computational efficiency and convergence for mainstream SPICE simulators. Especially when the circuit scale and the number of devices increase, direct calculation will lead to an exponential increase in simulation time, which cannot meet the actual needs of integrated circuit design. Therefore, in order to efficiently and accurately describe the electrical characteristics of the CNTFET in circuit-level simulation, especially its behavior under extreme conditions such as ESD, it is crucial to develop accurate and efficient Compact Models.

2.1. Thermionic Current Modeling

In typical CNTFETs, when the gate voltage is higher than the threshold voltage, its drain current is mainly contributed by the thermionic emission carriers injected from the source and crossing the top of the channel barrier. Based on the widely used Virtual Source (VS) model theoretical framework [

21], the drain current can be expressed as the product of the moving charge density at the virtual source location (i.e., the top of the potential barrier) and the effective injection velocity of charge carriers at that location.

is the effective surface density or line density of moving electrons (or holes) at the virtual source, and

is the average effective velocity of the corresponding charge carriers at the virtual source. The gate voltage controls

by adjusting the height of the channel potential barrier.

depends on the series voltage divider effect of the gate oxide capacitor

and the CNT’s own quantum capacitance

. Due to the quasi-one-dimensional band structure of carbon nanotubes, their density of states (DOS) is relatively low, resulting in a quantum capacitance

of the same magnitude as Cox, which cannot be ignored. Therefore, under strong inversion conditions, the equivalent gate capacitance

of the channel cannot be simply approximated as Cox and needs to be calculated through a series model.

is the equivalent quantum capacitance used to approximate the one-dimensional quantum capacitance effect under strong gate bias conditions. In compact models,

is often expressed using empirical or semi-empirical formulas:

Among them,

is the bandgap of carbon nanotubes,

is the Boltzmann constant, T is the absolute temperature, and parameters

and

are empirical fitting parameters. Their values need to be calibrated with experimental data to ensure the accuracy of the model under different diameters, temperatures, and bias conditions.

mainly reflects the maximum quantum capacitance of one-dimensional channels limited by the low density of states, while

can characterize a residual constant term or a non-ideal effect of quantum capacitance under high electric fields. Through

, we can approximately assume that under strong inversion conditions, the channel charge density

generated by the virtual source satisfies

is the gate source voltage, and is the threshold voltage. is an effective barrier modulation term, which is mainly used to describe the Drain-Induced Barrier Lowering (DIBL) effect caused by the drain source voltage . When increases, the barrier of the drain decreases, manifested as a decrease in the effective threshold voltage with the increase of . In (6), we describe this effect using the DIBL coefficient . It reflects the electrostatic shielding and the gate’s ability to control the channel. It is usually extracted from the rate of change in the threshold voltage with in the device’s output characteristic.

The above charge model, based on a linear capacitor (Equation (5)), is mainly effective in a strong inversion region. In the subthreshold region, the carrier concentration varies exponentially with gate voltage, and the thermionic current also follows an exponential law. In order to uniformly describe the process from subthreshold to strong inversion, a smoothing function is introduced to continuously describe the electron density at the virtual source, as well as the thermoelectric coefficient

and subthreshold slope factor

, so that the electron density model at the virtual source can be represented as

When

is much greater than 0, the device is a strong inversion region; when

, the device recovers to a linear capacitor model; when

is less than 0, then

Equation (8) clearly presents the characteristic of subthreshold current increasing exponentially with gate voltage. By calibrating the subthreshold factor , Equation (7) can accurately fit the I-V characteristics obtained from experimental data, achieving a smooth and continuous transition between weak and strong inversion regions.

In a short-channel CNTFET, due to significant suppression of carrier scattering, the injected carriers from the source can be largely regarded as quasi-ballistic transport.

is the initial effective velocity at which these charge carriers are injected into the channel. According to the widely used virtual source model,

is influenced by both the intrinsic ballistic limit velocity of carbon nanotubes and the scattering events within the channel (characterized by the equivalent mean free path

). By approximating through empirical formulas, we can obtain

is gate length, is equivalent mean free path, and is defined as the theoretical upper carrier velocity in CNTs under a fully ballistic transport ceiling ().

To describe the smooth transition of the drain current

from the linear to the saturation region, it is necessary to introduce a dependence on

. Combining Equations (2), (7), and (9), and considering the current saturation effect, a complete expression for the drain current is constructed as shown in Equation (10). In the unsaturated region, the current increases with the increase of

; when

is large enough, the electric field distribution near the virtual source tends to saturate, and the current also saturates accordingly. Finally, by introducing the low field effective mobility

and empirical smoothing parameter

to regulate the steepness of the transition from linear to saturation region, the following form of current equation can be obtained:

We modeled and simulated the current characteristics dominated by the ballistic transport of the CNTFET within the normal operating voltage range, and the simulation results are shown in

Figure 2. The main parameter settings used in the model are listed in

Table 1. This model, through reasonable physical approximation and parameter extraction, can effectively describe the DC characteristics of the CNTFET under normal operating voltage (0 V~2 V) while ensuring computational efficiency.

2.2. Tunneling Current Modeling

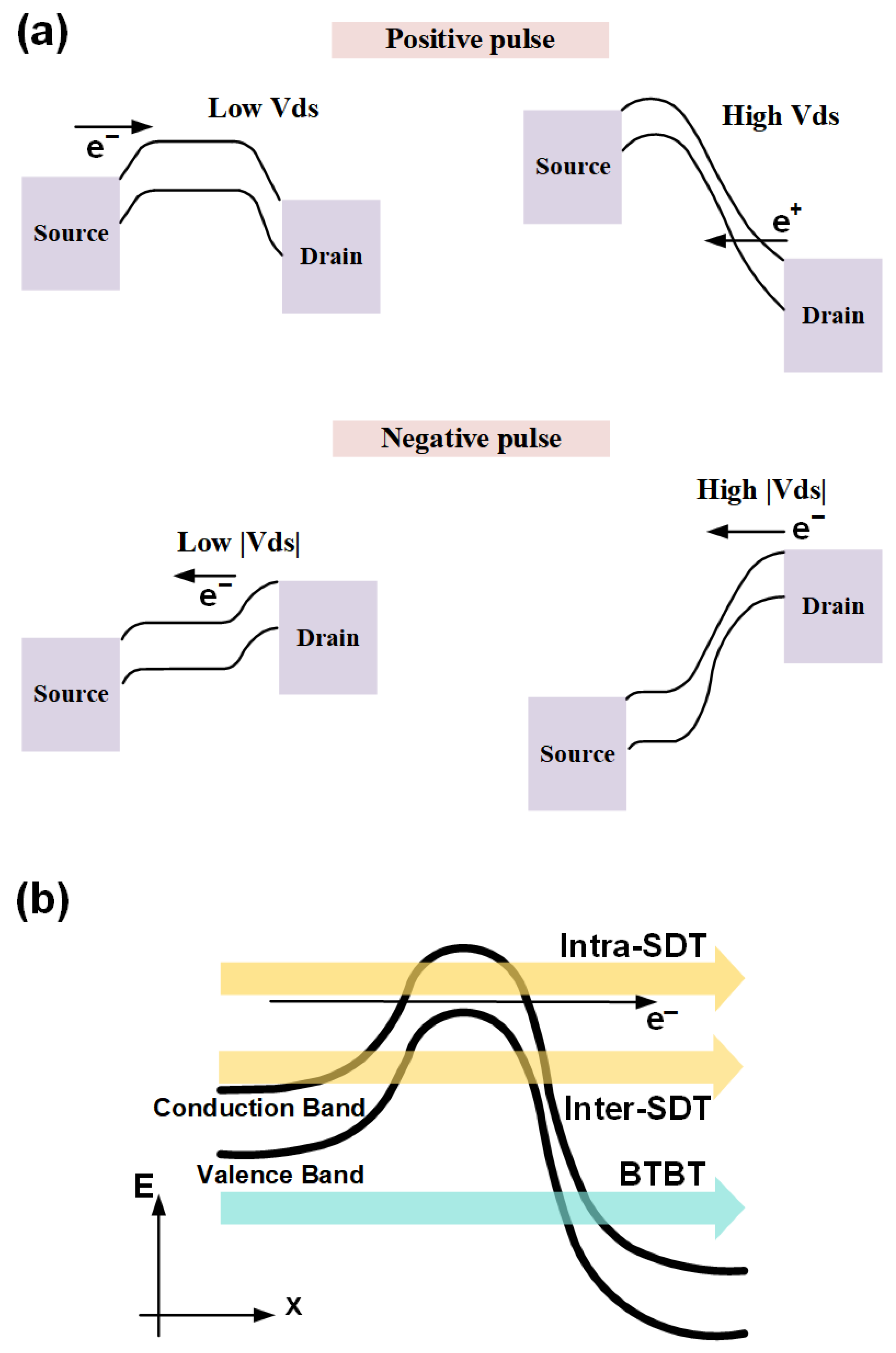

Compared to traditional silicon-based MOSFET devices, the CNTFET, with its unique quasi-one-dimensional nanostructure and superior ballistic transport characteristics, can effectively suppress short-channel effects, providing the possibility for achieving shorter effective gate lengths and faster switching speeds. However, when small-sized CNTFETs are subjected to external transient high voltage impacts, an extremely strong electric field will be formed inside the device, resulting in a significant incline of the band and severe deformation of the potential barrier (as shown in

Figure 3).

In this case, the probability of carriers in CNTFET-forming leakage current through a quantum tunneling mechanism will far exceed that of the device at normal operating voltage. Therefore, using only the thermionic current model cannot accurately describe the complex operating behavior of the device under high field strength and high bias conditions, such as ESD. In order to accurately describe the working characteristics and failure mechanism of CNTFET in ESD events, we must accurately model the tunneling leakage current of CNTFET. We divide the leakage current in CNTFET into two categories: Source–Drain Tunneling (SDT) and Band–Band Tunneling (BTBT), as shown in

Figure 3.

Source–drain tunneling refers to the leakage current formed by electrons or holes directly penetrating the channel barrier between the source and drain. Due to the quasi one-dimensional channels of carbon nanotubes, the potential barrier shape between the source and drain can be approximated by a simplified trapezoidal/triangular potential barrier. For one-dimensional potential barriers, the transmittance given by the Wentzel–Kramers–Brillouin method (WKB) is generally in the form of [

30]:

is the energy distribution of the potential barrier between source and drain,

is the effective mass of the carrier,

is the incident energy level of the particle, and x

1 and x

2 are the classical inflection points of the tunneling potential barrier. Assuming x

1 and x

2 are the barrier heights at the source and drain, respectively, when V

ds is high, the barrier height linearly decreases from x

1 at the source to

at the drain, which can be approximated as a trapezoidal barrier. Integrating Equation (11) under this linear potential barrier yields an analytical approximation of the tunneling emissivity:

When

Vds is large enough that

approaches 0, the shape of the potential barrier transforms into a triangle, and its transmittance is determined only by the height of the potential barrier at the source. At this point, Equation (12) can be further simplified as

is the equivalent barrier width. It can be seen that the tunneling transmittance is exponentially correlated with the barrier height

and inversely proportional to

Vds. Combine various constants and pre-factors into a fitting parameter

, and we finally obtain a compact model explicit expression for SDT leakage current:

represents the height of the potential barrier at the source (which can be estimated by the deviation between gate voltage and threshold voltage, for example, approximately in the subthreshold region), is the exponential factor of tunneling current on the height of the potential barrier, and is the fitting coefficient related to material and geometric parameters (reflecting the influence of barrier width, effective mass of the active region, etc., on tunneling probability). is the current amplitude fitting parameter (reflecting the overall scale of carrier density and transmission probability at the source). Parameters , , and can be extracted by fitting with the I-V characteristics of experiments or numerical simulations. The above model formula is simple in form and can be easily incorporated into the traditional leakage current model dominated by thermionic emission.

In an N-type CNTFET, when a high drain-source voltage is applied, the energy bands of the source and drain may overlap. When the highest energy level of the valence band of the drain (or near the drain region of the channel) exceeds the lowest energy level of the source conduction band, a BTBT current is generated from the drain valence band to the source conduction band. This process is driven by a strong transverse electric field, particularly evident in one-dimensional CNT band structures.

Due to the fact that the bandgap

of CNT is determined by the tube diameter and does not significantly change with bias voltage, the transverse electric field at high bias voltage causes the barrier width (

) to decrease with increasing V

ds, where F (

) is the approximate electric field strength, and L

eff is the effective barrier length. Therefore, as

Vds further increases, the tunneling barrier becomes thinner, the tunneling probability significantly increases, and BTBT current is formed. Under the above approximation, the tunneling probability of electrons (or holes) in a single energy level within the barrier can be approximated by WKB as follows:

is the front exponential term, which is proportional to CNT diameter and density, carrier effective state density, Fermi velocity, etc. It reflects the available energy and channel cross-sectional area of the conduction and valence band; is related to the tunneling barrier characteristics and usually increases with Eg and effective mass. is a power exponent, which is related to the shape of the potential barrier and nonlinear effects. For an ideal triangular potential barrier, = 1, but in practical devices, > 1; V0 is the threshold voltage of BTBT, corresponding to Vds when the conduction band and valence band are perfectly aligned and overlap. Therefore, when Vds < V0, the model is invalid, and . When Vds > V0, the current increases exponentially. This formula has a compact structure and can be directly used for circuit simulation, avoiding the WKB integration process. Only parameters such as need to be determined through experiments or simulations.

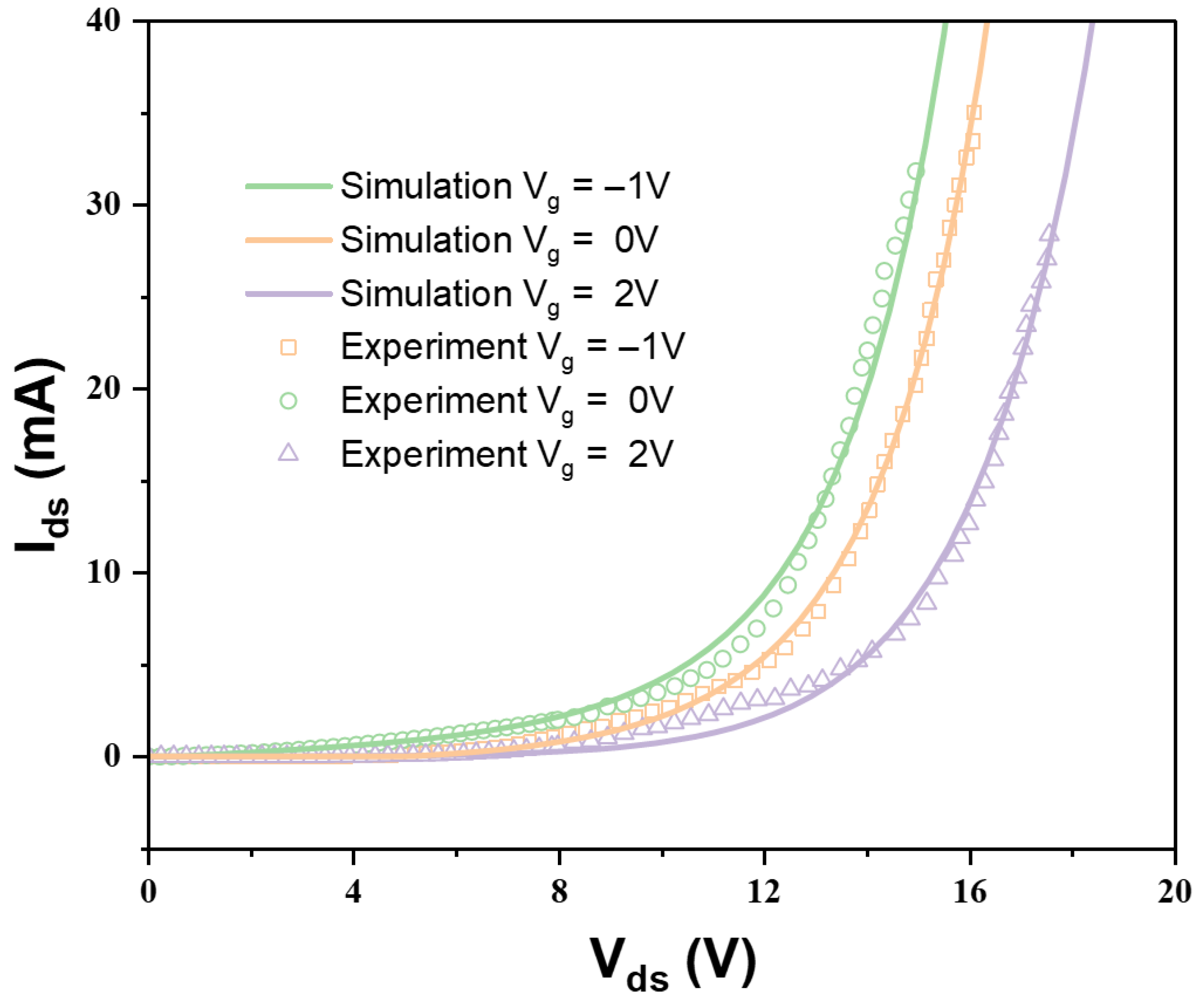

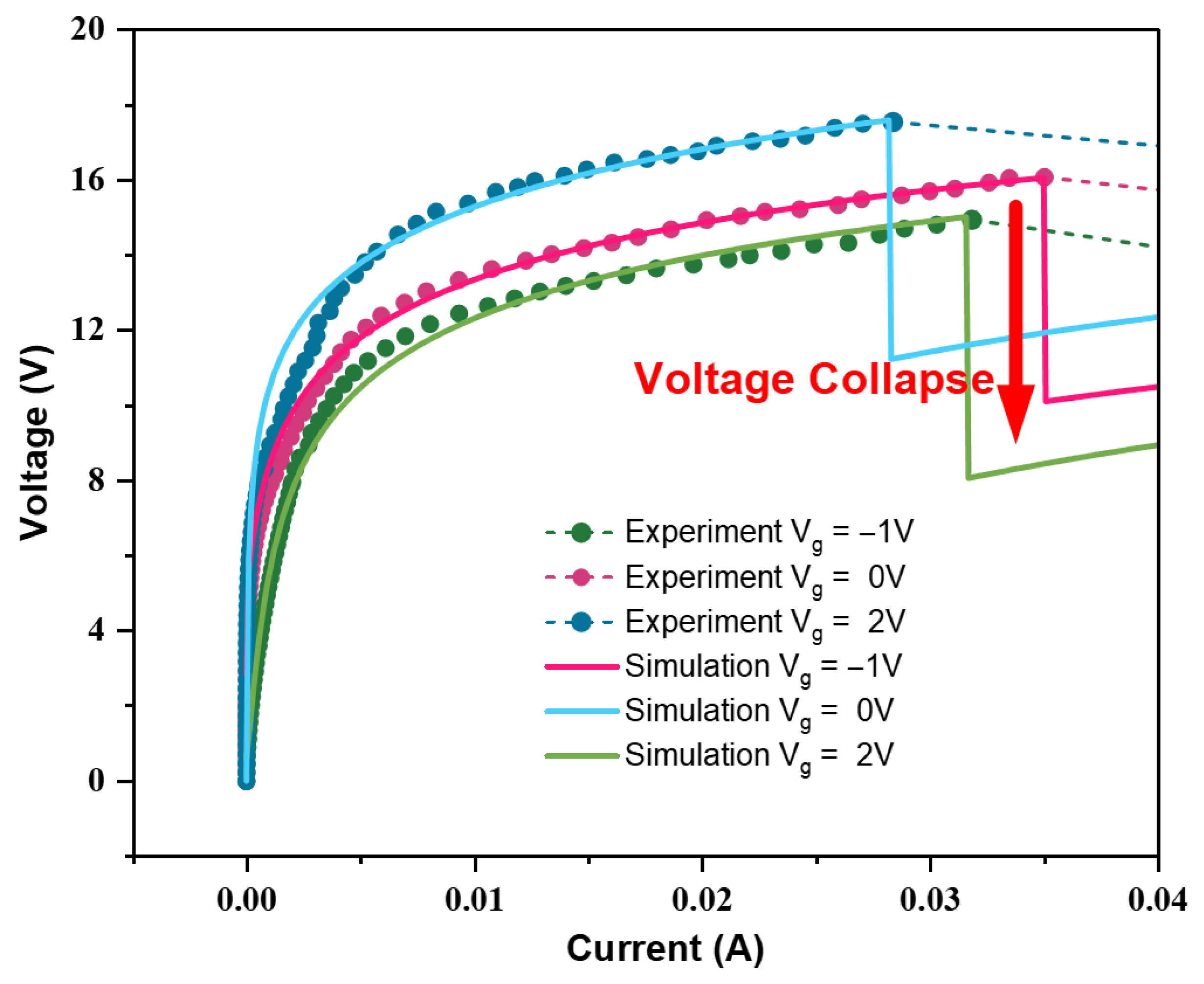

A test is conducted on CNTFET: three gate voltage states, V

g = −1 V, 0 V, and 2 V, are selected, with the source grounded (V

Source = 0 V). A stepwise ESD test voltage V

ds is applied to the drain, and I

ds is recorded at each voltage to obtain the I

ds vs. V

ds characteristic as shown in

Figure 4. To avoid parasitic effects and drift caused by instantaneous overheating, current compliance values and fixed integration times are set during the testing process.

Based on the theoretical model of tunneling current mentioned above, we modeled and numerically simulated the tunneling behavior in the high V

ds region under three gate bias conditions consistent with the experiment. The simulation results are shown in solid lines in the same coordinate system. The model, with its main parameter settings summarized in

Table 1, starts from the height/thickness of the barrier controlled by the gate voltage, and uniformly describes the reduction in the barrier and the increase in the penetration probability under the increase of V

ds; all parameters are calibrated within the same framework and maintain consistency throughout the entire voltage range. As shown in

Figure 4, the established model can clearly demonstrate the regulation law and magnitude of gate voltage on tunneling current: in low voltage region, the currents are close to zero; As V

ds increases, I

ds rapidly increases and shows a clear gating sequence—when V

g = −1 V, the potential barrier decreases and the tunneling probability increases, so I

ds is the highest at the same V

ds; V

g = 0 V, followed by the positive gate bias V

g = 2 V, which raises the potential barrier, suppresses tunneling, and minimizes I

ds. The overall agreement between the model and the measured data is good, and it can simultaneously reproduce the exponential rise pattern of the experiment and the relative relationship between the three gate voltages. The slight deviation at the high voltage may be related to self-heating, field dependence of contact barriers, or series resistance. The above results verify the model’s ability to describe the tunneling conductivity of CNTFET under ESD conditions, providing a reliable basis for subsequent reliability evaluation and circuit-level simulation.

Table 1.

Model parameter definitions and values.

Table 1.

Model parameter definitions and values.

| Parameter | Description | Value |

|---|

| W | Gate width | 30 |

| L | Gate length | 4 |

| CNT bandgap | 0.75 |

| Quantum-capacitance effective coefficient | 0.087 |

| Quantum-capacitance offset | 0.150 |

| Threshold voltage | 0.42 |

| DIBL coefficient | 0.02 |

| Subthreshold slope factor | 1.15 |

| Equivalent mean free path | 90 |

| Low field effective mobility | 1.31 × 102 |

| Fitting parameters | 1.73 |

| Height of potential barrier at source | 0.28 |

| SDT pre-exponential amplitude | 3.0 × 10−13 |

| SDT exponential slope factor | 33.6 |

| Fitting parameters | 1.10 |

| BTBT pre-exponential amplitude | 2.0 × 10−13 |

| BTBT exponential slope factor | 7.1 × 108 |

| Fitting parameters | 1.25 |

| BTBT threshold voltage | 5 |

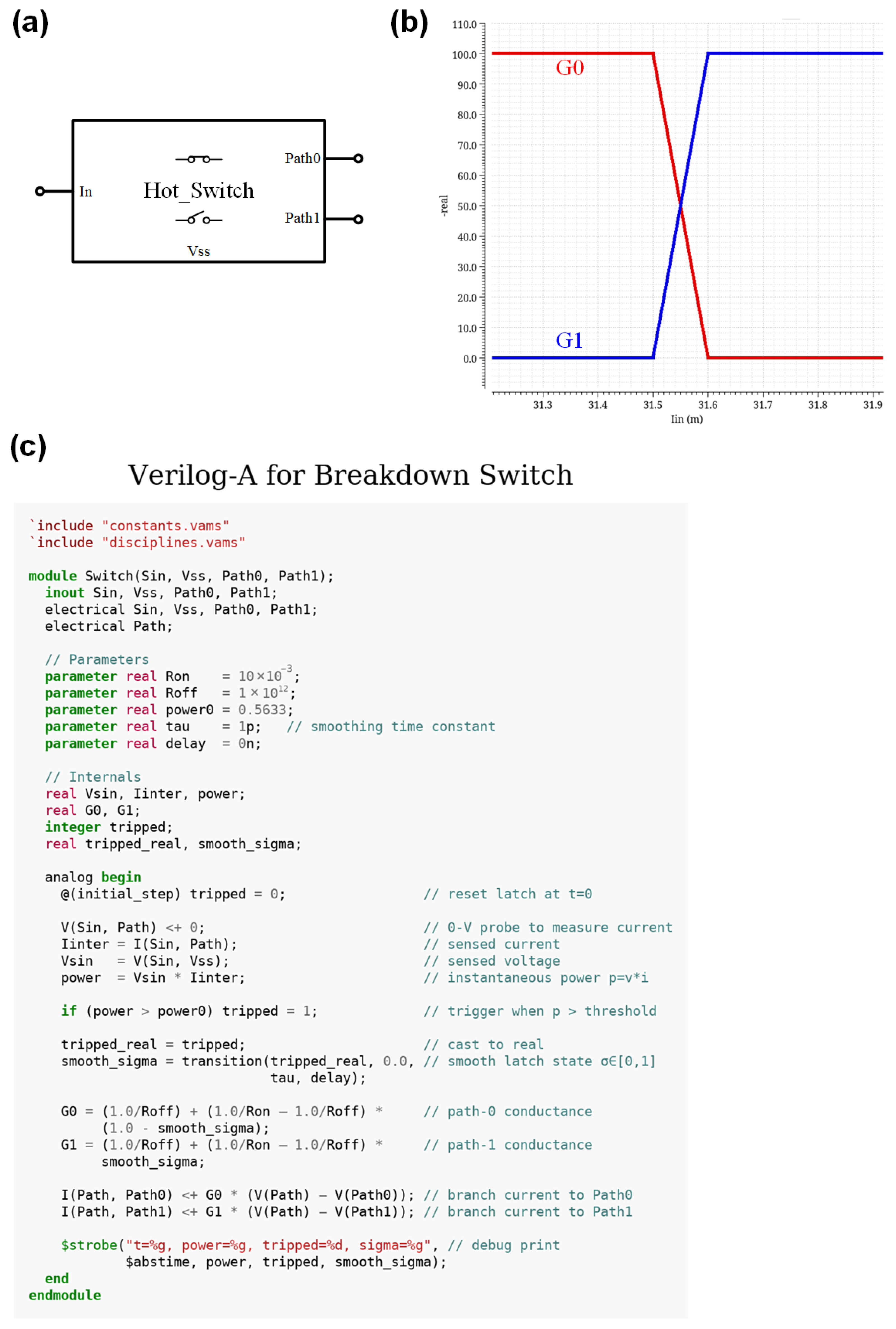

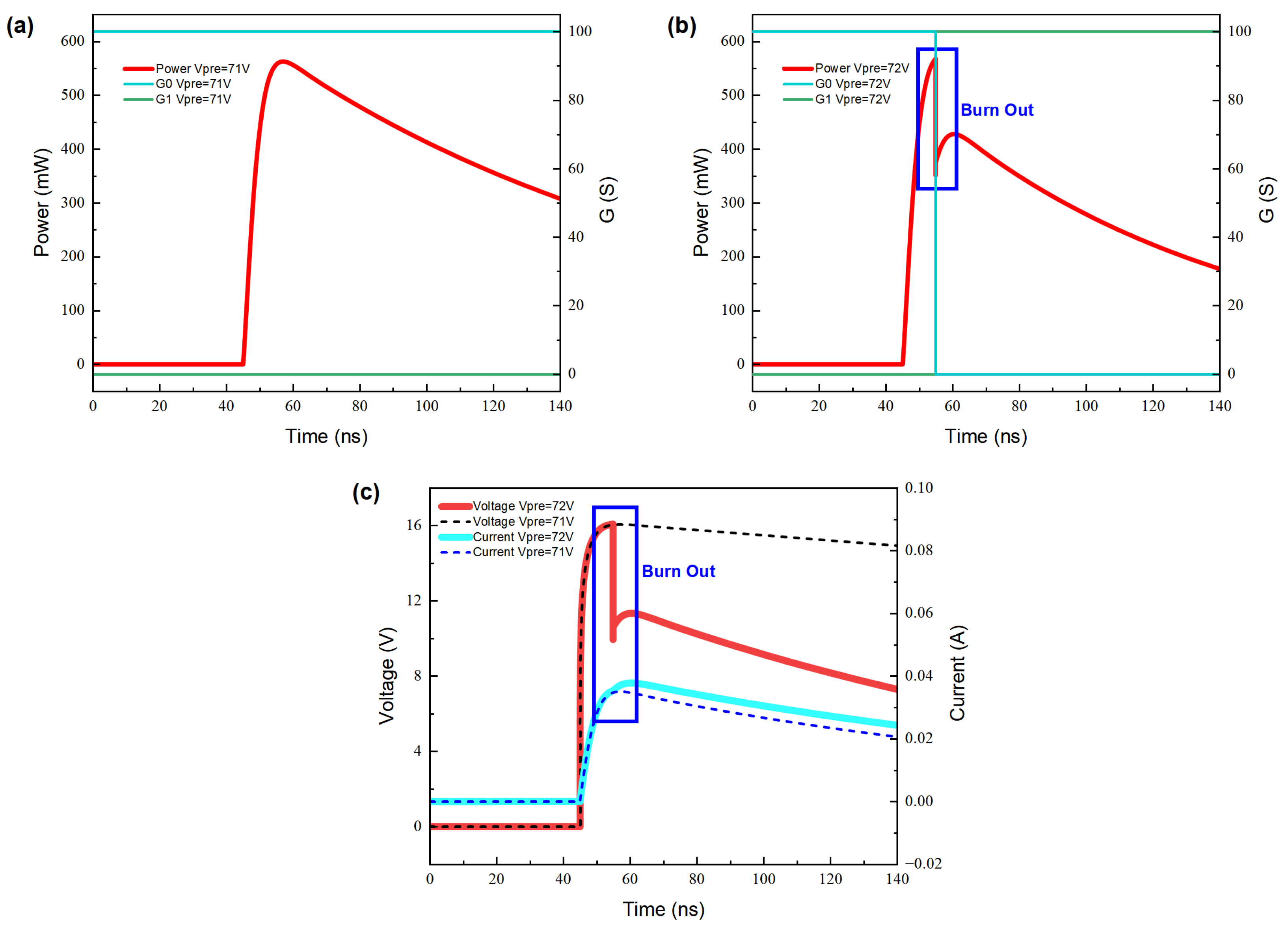

2.3. Thermal Breakdown

In ESD events, the transient high current experienced by CNTFET devices can lead to significant Joule heating effects. When the power consumption of the device exceeds its thermal tolerance limit, the CNTFET will undergo irreversible thermal damage, ultimately leading to permanent failure. In order to accurately describe this critical failure mechanism in a compact model, this paper constructs a specialized thermal breakdown module. According to Duan et al.’s study [

13], the failure process of CNTFET under ESD stress exhibits a clear three-stage characteristic, with thermal failure being the dominant mechanism for the final failure of the device. When the instantaneous power consumption of the device exceeds the critical threshold P0, the temperature inside the carbon nanotube channel rises sharply, causing C-C bond breakage and channel damage, and the device transitions from a conductive state to a high-resistance state.

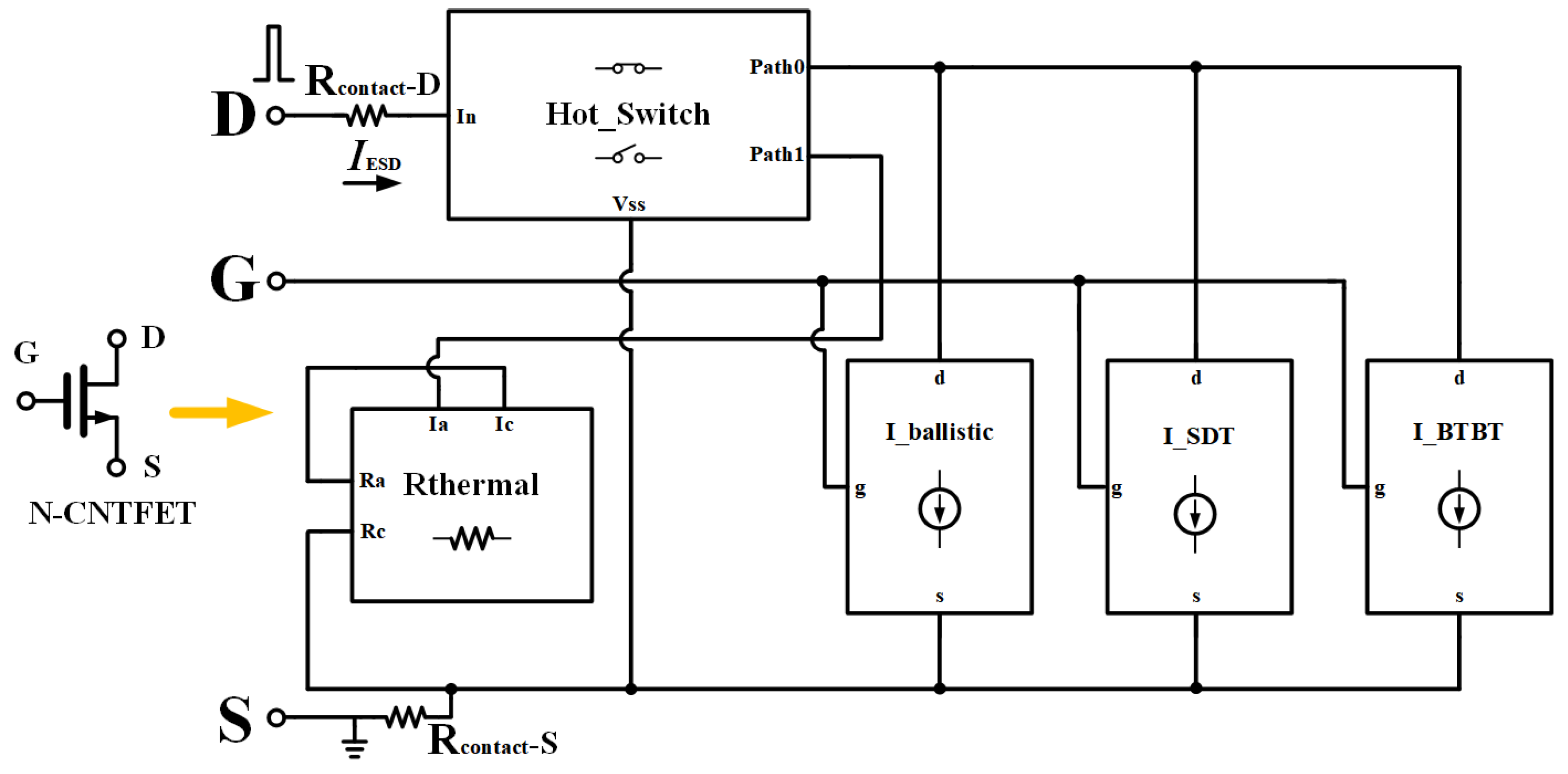

The hot-switch behavioral module judges based on the power consumption and the set threshold. When the instantaneous power consumption exceeds the preset threshold power0, the device quickly transitions from a conducting state to a high-resistance state and introduces a parallel low resistance breakdown path to simulate the thermal breakdown phenomenon; see

Figure 5.

From electrical measurements at the breakdown point during ESD testing of the LBG-CNTFET, we extract the resistance. By incorporating the Rthermal module into the aforementioned model, we simulate the low-resistance path formed after device breakdown. The proposed ESD hybrid model of CNTFET is shown in

Figure 6.

We use DC scanning current to simulate the current model established earlier by adding a thermal breakdown switch. The simulation results are shown in

Figure 7. The points are test data, and the three curves represent simulation data corresponding to simulation results under different gate voltages. When the power consumption of the circuit approaches the test value, the thermal breakdown switch is quickly triggered, instantly setting the original current path to a high resistance path and connecting a low resistance path in parallel to simulate the thermal breakdown process. From the simulation results, it can be seen that as the power consumption reaches the critical value, the current path undergoes significant changes, reflecting the failure process of CNTFET devices caused by thermal effects under ESD events. Especially when the power consumption exceeds the threshold, the voltage of the device drops sharply, exhibiting a hysteresis-like characteristic, which is consistent with the phenomenon observed in actual testing. By comparing simulation and test data, the effectiveness and accuracy of the established model in describing the thermal breakdown process of CNTFET can be verified.

Overall, our model is compact and data-calibrated, so it can cover the full bias window needed for device sweeps and ESD co-simulation without resorting to Non-Equilibrium Green’s Function (NEGF). In thermionic current, we use a Landauer/virtual-source core: current is written at a virtual source with an inversion-charge term, contact/series resistances are de-embedded at the terminals, and a smooth transition links linear and velocity-limited behavior. In tunneling current, we add explicit high-field leakage using WKB-type SDT and BTBT expressions; the onset voltage is tied to drain-side band overlap, and the fitted parameter captures the gate control that enables or suppresses BTBT in LBG CNFET. For thermal breakdown, the electrical core is coupled to a behavioral hot-switch that triggers once a calibrated power threshold is reached.

However, this compact approach has limits: simplified tunneling barriers may miss detailed phonon-assisted pathways far from the fitted window, and the behavioral thermal switch compresses spatially non-uniform heating and stochastic damage into a single power/energy threshold, so it cannot perfectly capture device-to-device variability, duty-cycle effects, or multi-pulse endurance seen in CNT breakdown studies; ultra-short (<1 ns) or long DC stresses may require full transient electro-thermal or NEGF-based analysis.