Abstract

In this work the harmonic injection active anti-islanding technique that has been recently proposed in reference Voglitsis et al. (2018) published in Trans. Power Electron. is generalized under the prospect of a high penetration level of distributed energy resource (DER) installations. Towards this direction, the theoretical limitation for the penetration level of such schemes is investigated and a firm theoretical background is presented that takes into account the installation parameters, as well as the penetration level at the installation common coupling point. Furthermore, a substantial feature which indicates the upgrade-ability of each installation is studied. Finally, extensive simulations and experiments verify the theoretical analysis.

1. Introduction

The global cumulative capacity of distributed energy resources (DERs) has grown at almost an exponential rate over the past decade, pushed by strong feed-in policies and declining DER prices [1]. Nowadays, worldwide expectations for renewable energy sources are still increasing, with PVs and wind parks being the predominant representatives of the DERs energy market share. Regarding PV-technology, the majority of PV installations consists of low power residential applications that are connected into the low voltage grid network. An indicative example is the renewable energy market share of Germany, where 70% of installed PVs are connected to the low voltage grid [1].

Until recently, for these installations, the guidelines concerning the integration of PVs were relatively modest, including only few basic demands for the PV installation, requiring the THDi of the inverter output injected current to be less than 5%, while the DPF needed to be close to unity. Therefore, the common (and cost effective) practice concerning the control of these systems has involved two main tasks: to track the maximum power from the PV-panel (by applying an MPPT control); and to inject a current waveform with a low THDi and unity DPF (e.g., by synchronizing with the utility voltage through a PLL). On the other hand, the power production of these installations typically varies between 0.1 and 10 kW, being characterized by low PL levels thus far. However, the continually rising share of renewable energy sources is currently pushing towards innovative solutions that will allow higher levels of renewable sources to be integrated into the low (and medium) voltage networks. A sign of this direction comes from the new IEEE 1547-2018 standard, which states that new DERs should be, among other capabilities, able to provide ancillary services into the grid.

Another major issue associated with interconnected DERs towards the upcoming PL growth is the facilitation of unintentional islanding detection. Undoubtedly, protection against this undesirable condition is of significant importance for the proper operation, safety, and reliability of the electrical system. Several recommendations and directives have been published on this subject aiming to protect maintenance personnel and the electric equipment of interconnected DERs. For example, the California Electric Public Utilities Commission (CPUC) Rule 21 describes the interconnecting, operating, and metering requirements for new generation facilities emphasizing, among other things, the importance of robust anti-islanding protection features. Furthermore, the foremost standardization institutions require a disconnection ability from the utility grid within a timeframe of 2 s., such as the IEEE Std. 1547, IEC Std. 62116, UL Std. 1741, and the former IEEE Std. 929-2000.

Until recently, passive anti-islanding protection schemes (i.e., by means of under/over voltage/frequency) were the common practice for small scale DERs (like residential PVs). However, in the anticipation of their power increase and high penetration level, those schemes are expected to end up suffering from large NDZs. Therefore, more sophisticated communication or active based anti-islanding techniques are required to meet the above mentioned standards.

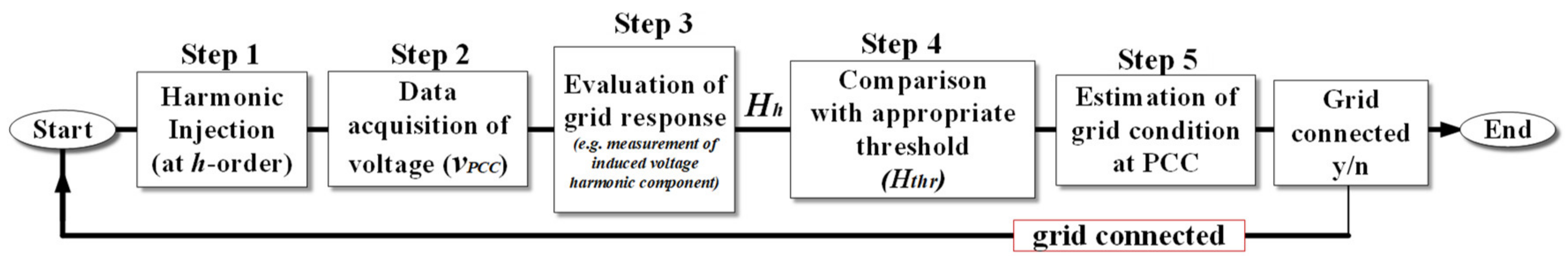

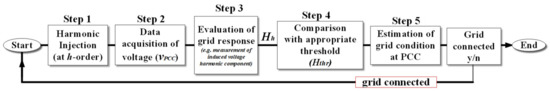

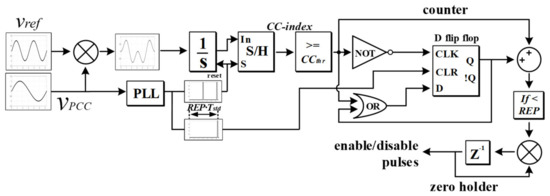

An active based anti-islanding scheme which is dedicated for implementation under high penetration levels of DERs, has been proposed in reference [2]. According to that scheme, anti-islanding detection can be based on the injection of the 2nd harmonic current component, achieving both low NDZ and low FDZ and without affecting the power quality at the PCC. While the abovementioned work considers the high penetration levels of DERs, the rather significant cancelling effect that comes from the operation of multiple grid-tied inverters that inject the same order harmonic current was not be taken into consideration. This effect was thoroughly analyzed in the current work and it is consistent with any harmonic injection base scheme that is described by the following formula and the structure shown in Figure 1:

Figure 1.

Generic description of the harmonic injection based anti-islanding techniques.

The equation above describes anti-islanding techniques that periodically inject a low current harmonic component, and estimate the grid condition at PCC (grid-tied or islanded) based on the evaluation parameter, Hh, and a predefined threshold value (Hthr). Normally Hh is based on Equation (1), while typically the condition Hh > Hthr indicates the islanded-operation of the installation. Grid response is usually evaluated through a DFT algorithm, as in references [2,3,4], by other means such as through cross-correlation, as in references [2,5,6], or through a Goertzel algorithm, as in reference [7]. A comprehensive comparative review on the above methods can be found in reference [8]. Various PL values have been used, while the effect of the anti-islanding schemes on the quality of the delivered power has also been studied. However, in reference [8], the PL level values were achieved by adjusting the power of a single grid-tied inverter along with the internal impedance of the grid transformer. As such, the concept of multiple inverters was not achieved in that work.

In the current work, the anti-islanding protection technique that has been proposed in reference [2] is modified, in order to take into account the effect of parallel operation of multiple DER-inverters that are connected to the same node. This problem has been also stated in reference [9], where a solution based on an external accumulator was proposed. In this work, a different solution is proposed that prolongs the harmonic injection in order to achieve a required overlap among the injected harmonic components of inverters. The modified technique that is proposed in this work is very simple and does not require an external accumulator, which are the main reasons not to use the technique discussed in reference [9]. On the other hand, the proposed modified technique has some limitations (particularly for a large number of inverters), because of the harmonic regulations of grid-tied inverters. Those limitations are discussed in more detail in Section 3.4. The effectiveness of the proposed technique is verified through extensive simulations as well as experimental results, which are presented in Section 4 and Section 5, respectively. Finally, Section 6 concludes the paper.

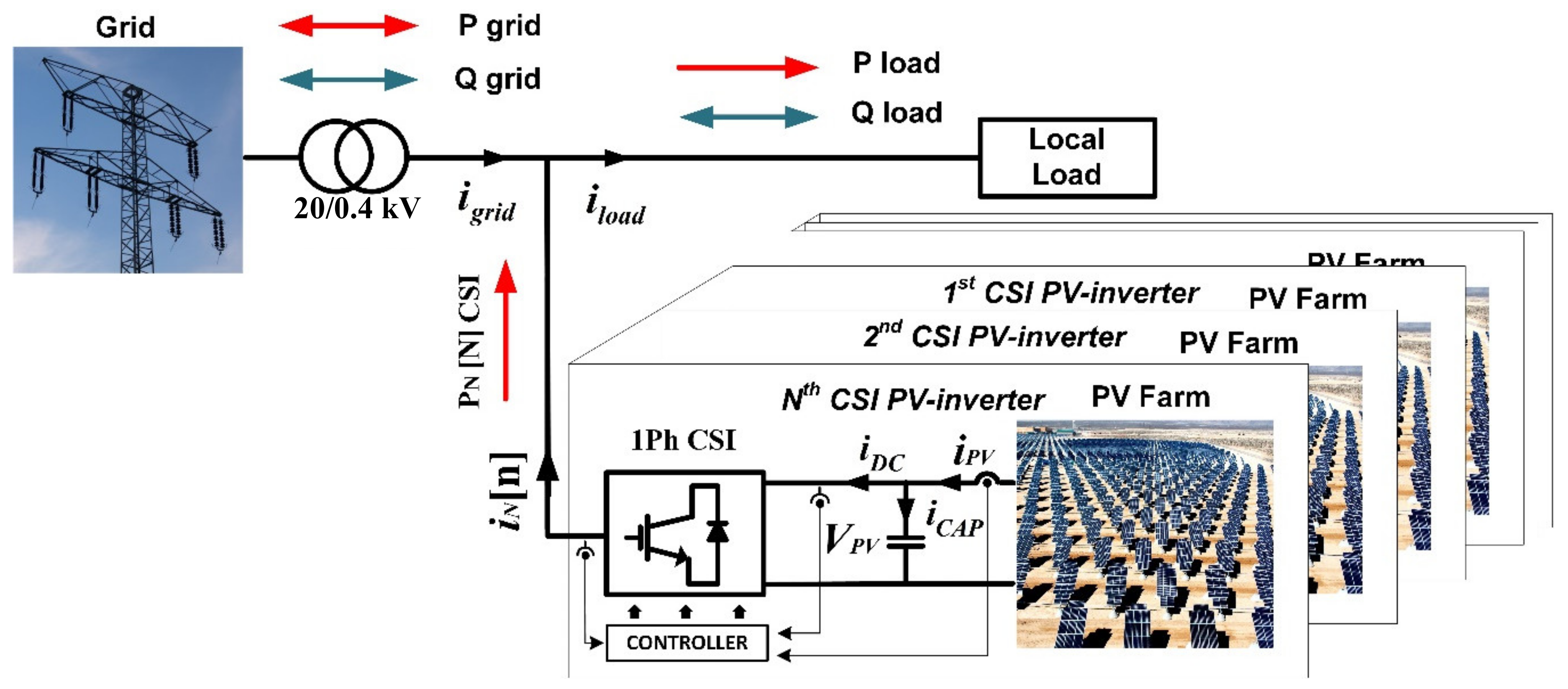

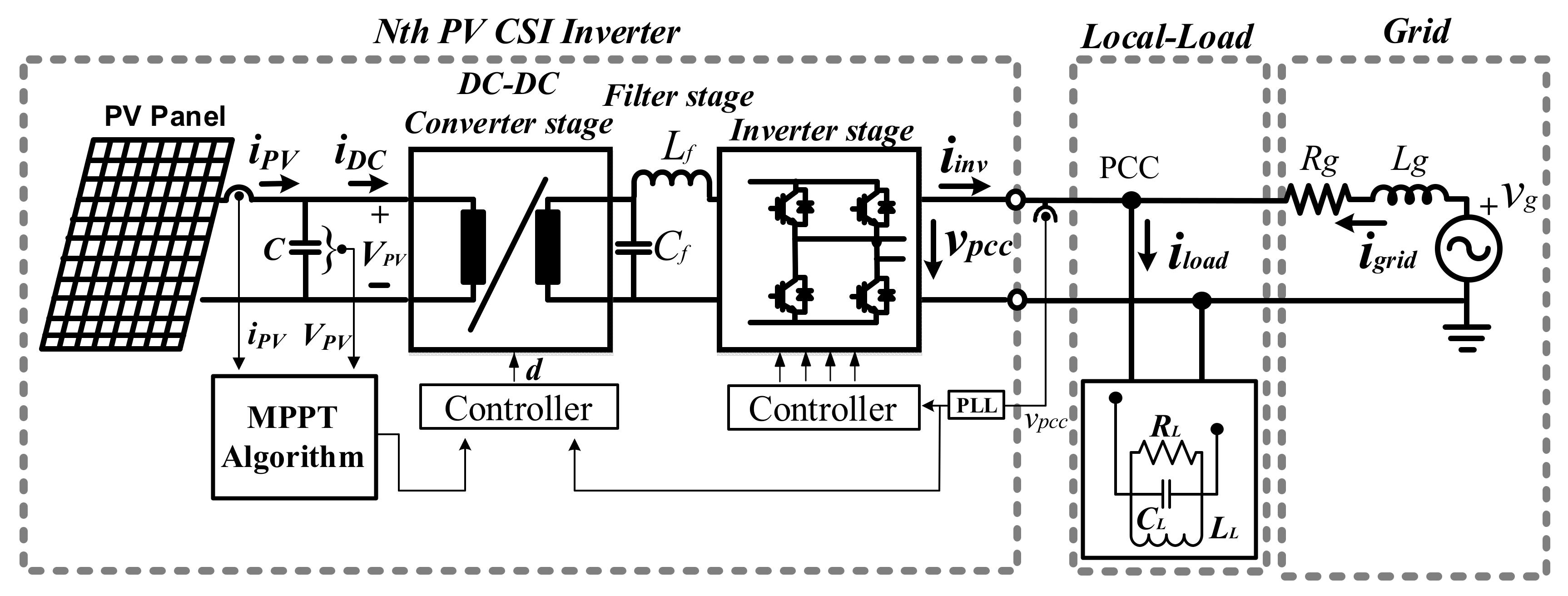

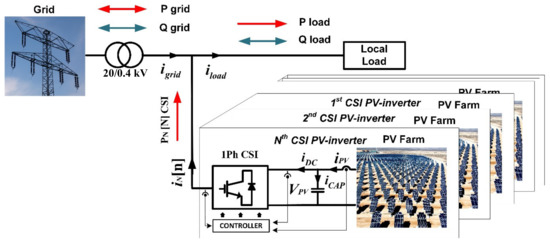

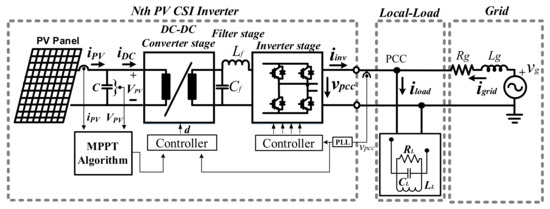

2. Description of System Under Study

The general description of the system under study is illustrated in Figure 2. PV-generators have been considered in this scheme, which are the predominant DER for low-voltage networks nowadays [2]. The power flow of each subsystem is also illustrated in Figure 2. It is noted that according to the new version of IEEE 1547-2018 [10], DER-generators should provide ancillary services to the grid and be capable of reactive power flow operation [1,11,12]. Finally, Figure 3 depicts the equivalent electrical diagram of a typical PV grid-tied CSI [13,14], which is an attractive configuration for low-power (typically below 500 W) PV-microinverters [3]. The topology consists of two stages. The inverter stage of the topology operates in line frequency with a very simple control and very low switching losses. On the other hand, the dc-dc converter stage operates in a high switching frequency driven by a maximum power point tracking (MPPT) algorithm. The utility grid and an RLC load (local-load) are also illustrated in Figure 3, forming the recommended circuit based on the IEEE 929-2000 [15] and IEEE 1547.1-2005 [16] for assessing the anti-islanding features of grid-tied inverters. The resistance Rg and inductance Lg (also shown in Figure 3), represent the power-line and power-transformer equivalent impedance.

Figure 2.

Schematic diagram of the system under study, where PV-distributed energy resources (DER) generators have been used.

Figure 3.

Electrical diagram of a PV-based DER-CSI.

3. Proposed Modification and Description of the Anti-Islanding Technique in reference [2]

3.1. Description of the Anti-Islanding Technique That Has Been Proposed in reference [2]

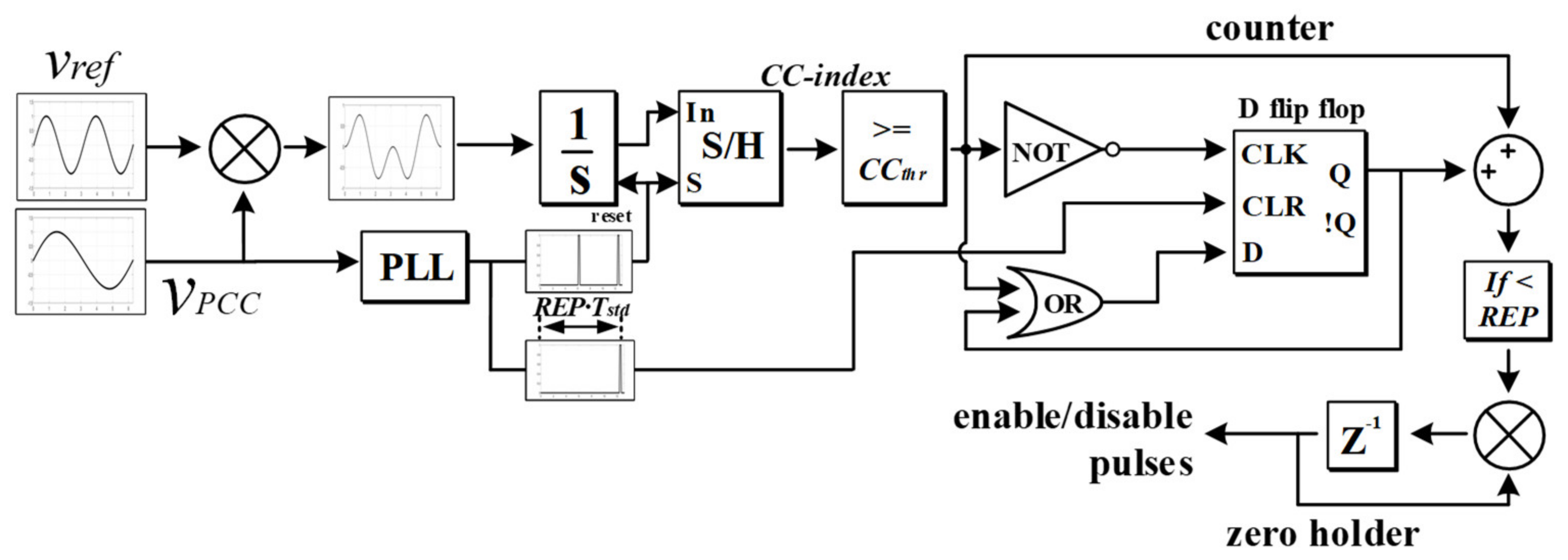

The anti-islanding technique that has been proposed in reference [2] is a harmonic-injection-based technique which is based on the cross-correlation algorithm to generate the evaluation index in Equation (1). It injects a harmonic current component with twice the base frequency aiming to distort the PCC voltage, which correlates with a reference signal (that also has twice the base frequency). The correlated value is compared against a threshold value to identify a potential islanding condition. The correlated signal is periodically stored through the sample and hold subsystem of Figure 4, and is compared against CCthr every TStd seconds. An islanding condition is detected only when the correlated value surpasses CCthr REP consecutive times (typically REP = 2), adding a countermeasure against false tripping of the inverter. Finally, when an islanding condition is identified, the inverter operation is ceased and locked-in, through the D flip-flop and zero-hold circuit of Figure 4.

Figure 4.

The anti-islanding technique that has been proposed in reference [2].

3.2. Description of the Issue That Arises by the Parallel Operation of Multiple Grid-Tied Inverters

Regarding the harmonic injection-based techniques, the induced harmonic voltage component that is induced by each inverter is compromised, as synchronous injection (injection at same time-intervals) among the inverters cannot be reassured. As such, the anti-islanding detection is jeopardized, risking being unable to detect an islanding incident. To better explain this problem, we will use some key equations coming from the operation of a single inverter. We will start by uing the active power of a single inverter, operating in a load-matching condition (keep in mind that in (2) Ptot is referring to the total power of a single-inverter):

Based on the anti-islanding technique used in reference [2], the induced harmonic component of the PCC voltage, which is provoked by a single inverter under load-matching conditions is given by (“i” was assigned for the islanded or grid mode of operation):

The CCindex in the islanded and in the grid-tied operation can be approximated (assuming a relatively large S-value) by [2]:

Please note that TCC should be an integer multiple of Tb, otherwise the calculated CCindex will deviate from the theoretical value in Equation (4). When considering Equation (4), a threshold can be set—as in reference [2]—that is based on the load-matching condition of a single inverter:

Now let us assume that N current-source inverters (of PN [n] nominal power each) that utilize the anti-islanding technique in reference [2], as well as M other DER-inverters (that may or may not utilize the anti-islanding technique) of a total nominal power PMtot that might be potentially installed are connected to the same PCC, and that Ptot = PMtot + PNtot. According to the analysis that is conducted in reference [9], the magnitude of the induced voltage that is caused by each inverter of the N-subgroup can be expressed by the following equation:

whereas the induced harmonic voltage that is generated by the synchronous (simultaneously) harmonic injection of l-inverters (assuming that the N-subgroup consists of inverters of the same type) is given by [9]:

Therefore, the CCindex that is calculated by (3) for a single inverter of nominal power Ptot, is reduced by a factor of when multiple inverters are connected to the same PCC under the load-matching condition. Evidently, the initial selection of CCthr, which has been made considering only a single grid-tied inverter, might fail to detect the islanding operation under multiple inverters, as the CCindex might fall below the initial CCthr -value during the islanded operation. Therefore, only a limited power upgrade (PMtot) is permitted for each installation, the value of which can be calculated by the following expression (assuming identical Gain and K values for each inverter) [9]:

According to reference [9], the upgrade factor of a given installation can be given by the following equation:

Evidently, UF provides an important feature of DER-installations that should be taken into account for the evaluation of the harmonic-based anti-islanding techniques (this factor will be even more significant in the near future when the penetration level of DERs is expected to be significantly increased). Using Equation (7) and Equation (8), we can either improve UF by increasing the number of overlapped inverters or by adjusting the CCislmin/CCthr ratio. It should be noted though that if the installation operates at a power lever lower than the nominal one (e.g., during a cloudy day at a PV-based DER installation), then the UF will be lower than the value that has been calculated by Equation (8). It should be noted that in Equation (8), we used the nominal power of inverters. In order to overcome this problem, we used a droop-controller for the magnitude of the harmonic injection, similar to the one used in reference [9]:

3.3. Description of the Proposed Modified Anti-Islanding Scheme for N Grid-Tied Inverters

In this work, we proposed to prolong the TCC interval of each inverter in order to maintain a minimum overlapped harmonic injection between the inverters that represent the N-subgroup. This strategy has the advantage of being effortlessly implemented in the control scheme of each inverter, without requiring communications. The equation that defines the minimum injection duration (TCC) of N-inverters such that at least l-inverters out of N perform an injection simultaneously, is:

It was noted that TStd should be the same among the N-inverters. Moreover, a beforehand synchronization agreement is required among the inverters (as in reference [9]), in order to avoid the harmonic cancellation effect. A synchronization agreement could entail that all inverters always inject harmonic current at the beginning of the positive/or negative grid voltage wave. This synchronization agreement can be made in advance and therefore it is not classified as a communication requirement.

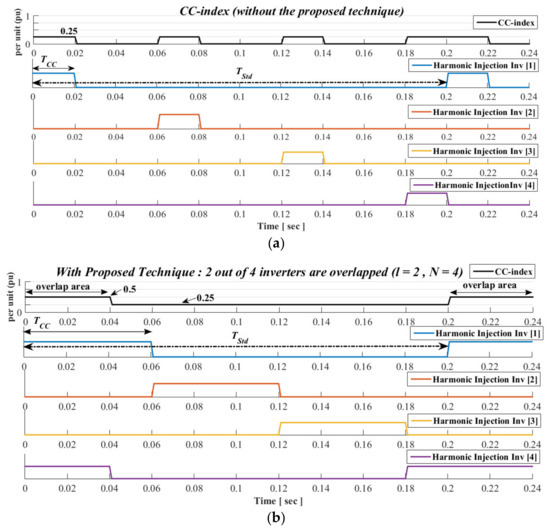

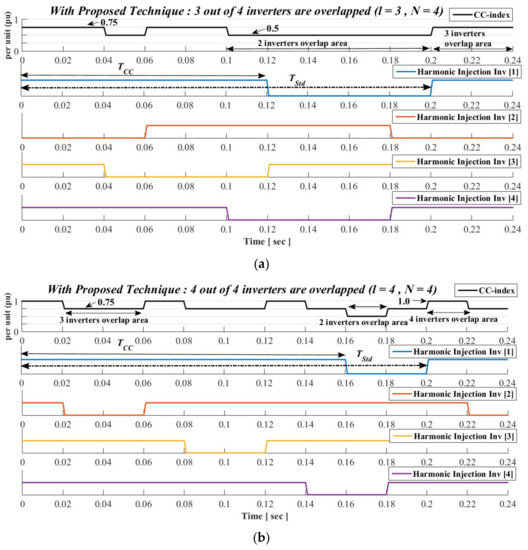

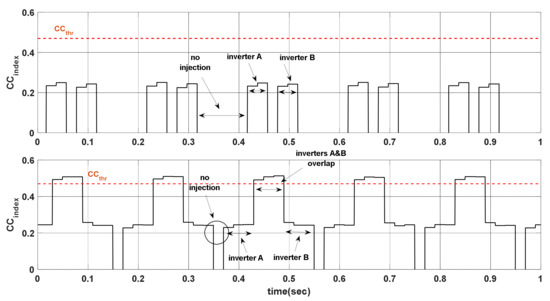

The proposed strategy is demonstrated in Figure 5 and Figure 6, where a set of N-subgroup inverters is considered. The CCindex is as well depicted in those figures, where 1 pu denotes the normalized CCindex that is generated by the overall of four inverters. Based on the presented results, the number, l, of inverters that overlap with each other, depends on the duration of their individual harmonic injection, denoted as TCC. It should be noted that TCC should be also the same among the inverters. For example, l = 3 implies that the harmonic injection of at least three inverters will overlap (see Figure 6a) with each other. It was noted that the proposed strategy indicates the minimum amount of overlapped inverters, even though there is a probability for more inverters to overlap as well.

Figure 5.

Injection pattern of the N-subgroup inverters and CCindex evolution in a time domain for, (a) N = 4 and l = 1, (b) N = 4 and l = 2 (implying that at least two inverters will be overlapped).

Figure 6.

Injection pattern of the N-subgroup inverters and CCindex evolution in a time domain for, (a) N = 4 and l = 3 (implying that at least three inverters will be overlapped), (b) N = 4 and l = 4 (implying that at least four inverters will be overlapped).

3.4. Discussion on the Limitations of the Proposed Modification

According to the power quality limitations [16], the mean magnitude of the 2nd–order current harmonic component captured in 10 cycles (i.e., 0.2 s for 50 Hz systems) under rated power conditions has to be less than 1%, implying that:

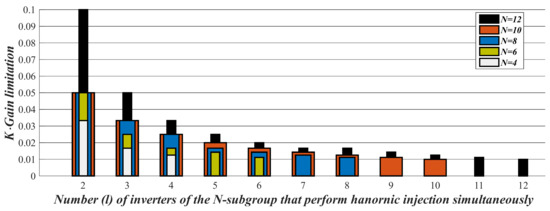

Combining Equations (9)–(11), the following equation was derived (assuming that 0.2 ≥ TStd):

According to Equation (12), higher l-values impose stricter limitations in the K·Gain product. This restriction is dictated by the power quality standards and it is associated with the upper limit of K. The K·Gain limitation is plotted in Figure 7, as a function of l, for five indicative N-values (i.e., N = 4, 6, 8, 10, 12). According to Figure 7, larger N-values enable the harmonic injection of the inverters to be overlapped with a lower limitation. For example, the limitation of K·Gain when two inverters are overlapped is 0.1 when the total number of inverters is 12, whereas it becomes 0.05 (much stricter) when less inverters are available. This happens because the same number of inverters can be overlapped with shorter injection durations when a larger total number of inverters is available. On the other hand, for the same l/N ratio, the K·Gain limitation gets stricter for higher N-values. Another notable factor that can be seen in Figure 7 is the round-down of the K·Gain values. The round-down is caused by the obligation of TCC being an integer multiple of Tb. Thus, various l, N combinations might lead to the same K·Gain limitation. For example, note that for l = 10 & N = 10, and for l = 12 & N = 12, the same limitation of 0.01 stands.

Figure 7.

K·Gain limitation as a function of l, for five indicative N-values (i.e., N = 4, 6, 8, 10, 12).

On the other hand, the restriction associated with the bottom limit of K-value is dictated by the inverter microcontroller. For example, in reference [3] a 16-bit DSPIC30F4011 achieves a 4-bit accuracy over the generation of the harmonic signal with K = 4% and Gain = 2, whereas for K = 0.5%, its accuracy is limited to 1 bit. Therefore, choosing the K-value involves a compromise between the desired accuracy of the produced signal, the maximization of UF parameter, and the microcontroller cost.

Finally, it should be noted that the obligations of Equation (12) only concern the operation of the inverter under its rated power. Therefore, we do not have to take into account the further limitation that comes from the higher values of K * [n], forced by the proposed droop-controller of Section 3.2 when the inverter operates with a lower power.

4. Simulation Results

Two main case studies are examined in this Section to demonstrate the effectiveness of the proposed anti-islanding technique. For this reason, a DER-installation that consists of five grid-tied inverters has been simulated in a Matlab/Simulink environment. Specifically, the DER-installation under study comprises four current-controlled VSIs that utilize the proposed anti-islanding scheme (N = 4) and one current-controlled VSI that utilizes a passive under/over voltage/frequency (U/O-V&F) anti-islanding scheme (M = 1). The inverters rating as well as rest of the system parameters are presented in Table 1, while all case-studies have been simulated considering the load-matching condition, in accordance with the IEEE 1547.1 and IEEE 929-2000 islanding requirements.

Table 1.

Electrical quantities/parameters of the system and parameters of the anti-islanding algorithm.

4.1. Case I, Grid-Tied CSI Inverter Operates at Nominal Power While l Varies

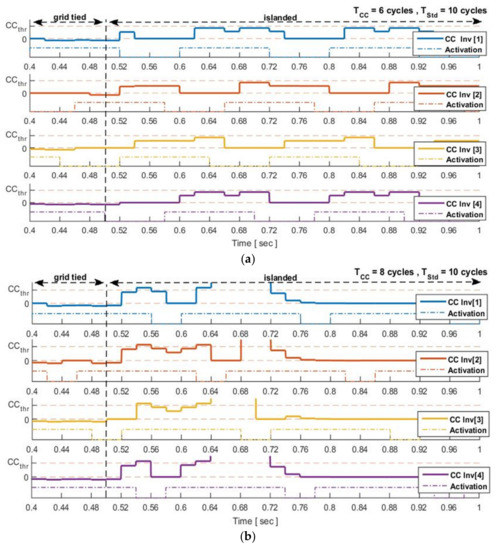

Two subcases have been simulated for this case, considering the nominal inverters’ power and maximum QL. Those cases consider three and four overlapping inverters, respectively (i.e., l = 3 and l = 4), implying that TCC = 6 cycles, and 8 cycles, according to Equation (11).

Based on the simulation results that are presented in Figure 8, we can see that the island was progressively detected for the case of l = 4 (Figure 8b), whereas for l = 3 (Figure 8a) none of the inverters managed to detect the islanded operation. On the other hand, the U/O-V&F protection scheme of the remaining VSI inverter, was activated only after the disconnection of the N-Subgroup inverters where the PCC voltage had dropped below the limits defined in Table 1.

Figure 8.

CCindex of inverters under nominal power operation, (a) l = 3 (TCC = six cycles), (b) l = 4 (TCC = eight cycles).

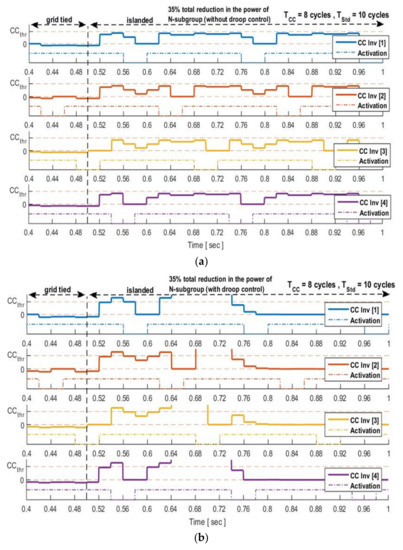

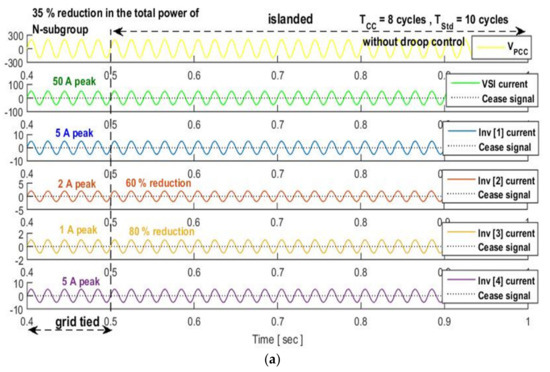

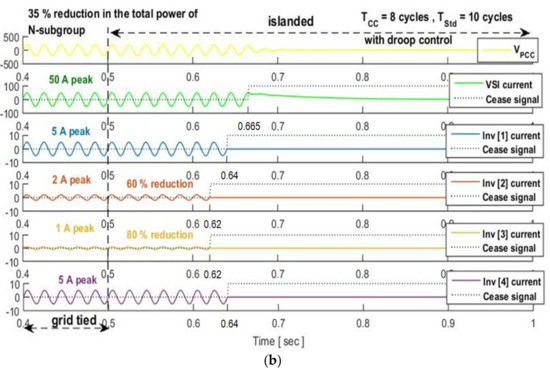

4.2. For Case II, l is Equal to 4, while the Power of CSI Is Reduced to 60%

In this subsection, the system undergoes a power reduction to investigate the impact of the inverter power and droop controller on the proposed technique. To do that, two subcases were simulated. In the first subcase the droop-controller was activated, whereas in the second one, the droop controller was inactive. According to the simulation results, the evolution of CCindex when the droop-controller is inactive (Figure 9a) was reduced by ~28% with respect to its initial value that is depicted in Figure 8, thereby failing to detect the islanded operation. On the other hand, the reduction of CCindex was effectively countered by the droop-controller (Figure 9b), leading to the successful detection of the islanded operation. Corresponding waveforms of inverters currents and PCC voltage are illustrated in Figure 10.

Figure 9.

CCindex of inverters under reduced power operation (60% and 80% reduction for the inverters 2 and 3, respectively) for l = 4 (TCC = 8 cycles), (a) without droop-controller, (b) with droop-controller.

Figure 10.

PCC voltage and inverter currents at reduced power levels (60% and 80% reduction for the inverters 2 and 3, respectively) and l = 4 (TCC = 8 cycles), (a) without a droop-controller; (b) with a droop-controller.

5. Experimental Results

In order to examine the effectiveness of the aforementioned anti-islanding technique, a test bench of two CSI interleaved flyback inverters, operating in DCM, was constructed. The foremost components used in the inverters’ circuitry, along with the system parameters and the parameters of the anti-islanding scheme, are recapped in Table 2. The inverters have been tested under a high quality factor (QL = 2.5) and load matching conditions. Moreover, two cases with different TCC have been studied, i.e., TCC = 0.02 s (1 cycle) and TCC = 0.12 s (6 cycles). Finally, corresponding results, supporting the effectiveness of the proposed modified scheme are presented in Figure 11 and Figure 12.

Table 2.

System parameters and anti-islanding algorithm parameters of the experimental setup.

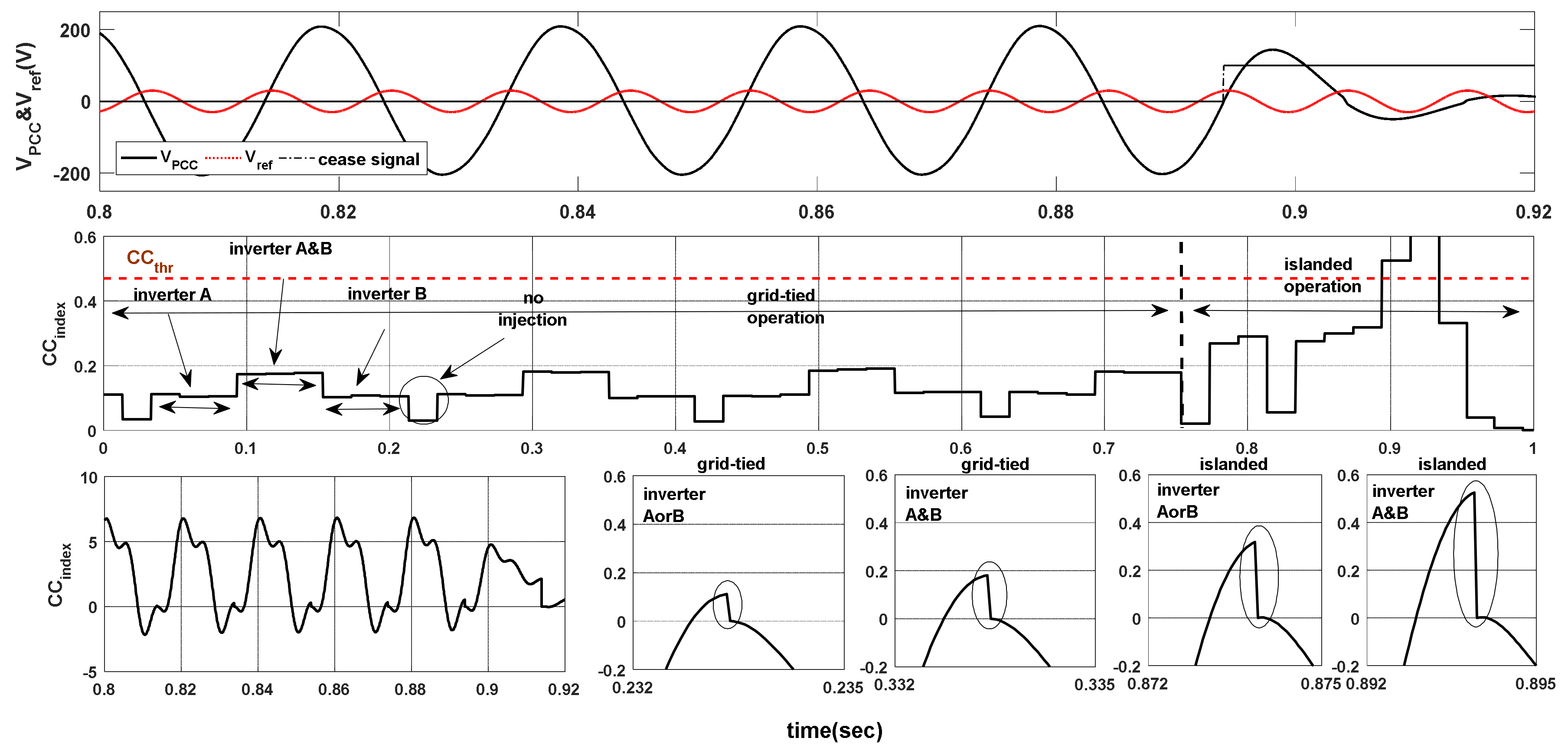

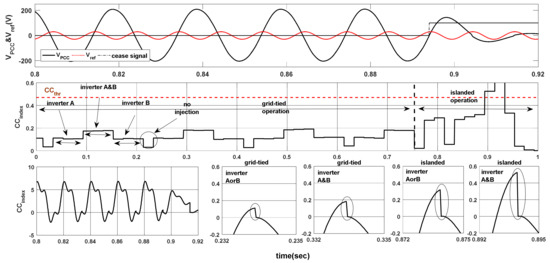

Figure 11.

Evolution of CCindex in an islanded operation for the two injection patterns, (top graph) 1/10 cycles, (bottom graph) 6/10 cycles.

Figure 12.

(top graph) VPCC along with Vref, (middle graph) evolution of CCindex in grid tied and islanded operation, (bottom graph) evolution of the CCindex calculation.

In Figure 11, the CCindex of both cases in an islanded-operation is illustrated. In the first case, the CCindex does not surpass the predefined CCthr as a result of the lack of power in the second harmonic, meaning the anti-islanded method fails. In second case, when inverters are overlapped, the CCindex surpasses CCthr and the method detects the islanded-operation.

Figure 12 illustrates the evolution of CCindex along with VPCC and Vref, in both islanded and grid-tied operation, and the evolution of the integration in the case of overlapping inverters. Finally, in accordance with the aforementioned standards, the island was detected in less than 10 fundamental cycles.

6. Conclusions

In this work, a strategy was proposed that enables the harmonic injection scheme that was presented in reference [2] to be implemented in multiple grid-tied inverters. Furthermore, a generalized mathematical model for the case of multiple grid-tied inverters was presented. Extensive simulation and experimental results were presented that verify the above outcomes. It was shown that the islanded operation can be detected, even when multiple grid-tied inverters are connected to the same node. The detection time has been recorded, within 10 fundamental cycles (from the activation of the algorithm), coping with all relevant anti-islanding as well as power quality standards. In conclusion, the proposed anti-islanding technique provides a very promising solution for the anti-islanding protection of grid-tied inverters that are connected to the same node, as well as a low computation cost solution with a reduced NDZ.

Author Contributions

Conceptualization, D.V., F.V., A.T. and N.P.; Methodology, D.V. and A.T.; software, D.V. and I.P.; Validation, D.V. and A.T.; Formal analysis, D.V. and A.T.; data curation, C.K.; writing—original draft preparation, D.V. and A.T.; writing—review and editing, D.V., A.T. and N.P.; supervision, N.P. All authors have read and agreed to the published version of the manuscript.

Funding

This research has been co-financed by the Operational Program “Human Resources Development, Education and Lifelong Learning” and is co-financed by the European Union (European Social Fund) and Greek national funds, in the context of the project “DGRES-PRO” (MIS 5006210).

Conflicts of Interest

The authors declare no conflict of interest.

Nomenclature

| PV | Photovoltaic generator |

| PCC | Point of Common Coupling |

| NDZ | Non- detection zone |

| FDZ | Fault-detection zone |

| THDi | Total harmonic distortion of the inverter output injected current |

| DPF | Displacement power factor |

| MPPT | Maximum power point tracking |

| PLL | Phase locked loop |

| CSI, VSI | Current and Voltage Source Inverter |

| DER-CSI | Distributed energy resource current source inverter |

| CC | Cross-correlation |

| N | Initial number of inverters that are using the proposed anti-islanding technique |

| M | Additional number of inverters that can be installed at PCC without compromising the effectiveness of the proposed anti-islanding technique |

| l | Minimum number of the inverters of the N-subgroup, which perform the harmonic injection, and are required to in order to achieve the desired overlap |

| m | Number of M-subgroup inverters that may (or may not) use the proposed anti-islanding technique |

| DCM | Discontinuous conduction mode |

| REP | Consecutive times that the anti-islanding threshold must be surpassed before the identification of islanded-operation |

| RL, CL, LL | Equivalent resistance, capacitance, and inductance of the islanded network |

| SSC | Short circuit power at PCC (VA) |

| ωb. fb, Tb | Utility base angular frequency, utility base frequency, and utility base period |

| Xg, Rg | Equivalent grid internal impedance (at base angular frequency ωb) and resistance at PCC |

| QL | Quality factor of islanded network |

| i | Islanded (i = isl) or grid-tied (i = grid) operation |

| Hi,h, ei,h | Index and evaluation function of the anti-islanding technique |

| VPCC, | Instantaneous and peak value of PCC voltage |

| Peak value of the h-order harmonic component of PCC voltage in islanded or grid-tied operation; it refers to the component that is induced by the islanding-scheme and not to the pre-existing harmonics of the grid-voltage | |

| Peak value of the fundamental component of PCC voltage | |

| Peak value of the harmonic current component which is injected by inverter (imposed by the anti-islanding technique), in grid-tied or islanded operation | |

| K | Rated ratio of the fundamental-harmonic current components of the inverter |

| K* | Actual value of K (activated during the droop control mode) |

| Gaini | Inverter gain in in grid-tied or islanded operation |

| TStd, TCC | Periodicity and duration of the harmonic injection |

| Zi,h | Impedance at the output stage of the inverter (at h-order), in grid-tied or islanded operation |

| ζi,h | = |Ζgrid/isl,h|/RL |

| Peak value of the reference that is used in the proposed scheme [2] | |

| S | Number of samples that is used to calculate the CCindex according to (3) |

| ΔφCC,i | Phase angle between and the reference signal |

| CCindex | Cross-correlation index |

| CCgrid, CCisl | Cross-correlation sequence index of the PCC voltage during the grid-tied operation or islanded operation |

| CCgridmax | Maximum value of CCgrid [2] |

| CCilsmin | Minimum value of CCisl, [2] |

| CCthr | Threshold-value that is used in the proposed method (CC>CCthr for islanded operation) |

| W% | Margin between the islanded and grid-operation (as a percentage) |

| PN[n] | Nominal power of each inverter of the N-subgroup |

| PN*[n] | Actual power of each N-subgroup inverter |

| PNtot | Total nominal power of N-subgroup |

| PM[m] | Nominal power of each inverter of the M-subgroup |

| PMtot | Total nominal power of M-subgroup |

| Ptot | Total nominal power of the installation (including both the N-subgroup and the M-subgroup inverters) |

| PL | = PNtot/SSC, penetration level of PV-units that are connected at the same node and utilize the proposed anti-islanding method |

| UF | = PMtot/PNtot, upgrade factor of the installation |

| U/O-V&F | Under/Over Voltage & Frequency, it is a widely used passive anti-islanding technique |

References

- Yang, Y.; Enjeti, P.; Wang, H.; Blaabjerg, F. Wide-scale adoption of photovoltaic energy: Grid code modifications are explored in the distribution grid. IEEE Ind. Appl. Mag. 2015, 21, 21–31. [Google Scholar] [CrossRef]

- Voglitsis, D.; Papanikolaou, N.; Kyritsis, A. Active cross-correlation anti-islanding scheme for PV module-integrated converters in the prospect of high penetration levels and weak grid conditions. IEEE Trans. Power Electron. 2018, 34, 2258–2274. [Google Scholar] [CrossRef]

- Voglitsis, D.; Papanikolaou, N.; Kyritsis, A. Incorporation of harmonic injection in an interleaved flyback inverter for the implementation of an active anti-islanding technique. IEEE Trans. Power Electron. 2016, 32, 8526–8543. [Google Scholar] [CrossRef]

- Asiminoaei, L.; Teodorescu, R.; Blaabjerg, F.; Borup, U. A digital controlled PV-inverter with grid impedance estimation for ENS detection’. IEEE Trans. Power Electron. 2005, 20, 1480–1490. [Google Scholar] [CrossRef]

- Byung-Gyu, Y.; Matsui, M.; Gwon-Jong, Y. A correlation-based islanding-detection method using current-magnitude disturbance for PV system. IEEE Trans. Ind. Electron. 2019, 58, 2935–2943. [Google Scholar]

- Bae, B.Y.; Jeong, J.K.; Lee, J.H.; Han, B.M. Islanding detection method for inverter-based distributed generation systems using a signal cross-correlation scheme. J. Power Electron. 2010, 10, 762–768. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, J.G.; Ji, Y.H.; Jung, Y.C.; Won, C.Y. An islanding detection method for a grid-tied system based on the Goertzel algorithm. IEEE Trans. Power Electron. 2010, 26, 1049–1055. [Google Scholar] [CrossRef]

- Voglitsis, D.; Valsamas, F.; Rigogiannis, N.; Papanikolaou, N.; Kyritsis, A. Comparative study of active anti-islanding schemes compatible to MICs in the prospect of high penetration levels and weak grid conditions. IET Gener. Transm. Distrib. 2018, 12, 4589–4596. [Google Scholar]

- Voglitsis, D.; Valsamas, F.; Rigogiannis, N.; Papanikolaou, N.P. On harmonic injection anti-islanding techniques under the operation of multiple DER-inverters. IEEE Trans. Energy Convers. 2018, 34, 455–467. [Google Scholar] [CrossRef]

- IEEE. IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces; IEEE Standard 1547; IEEE: Piscataway, NJ, USA, 2018. [Google Scholar]

- Tsimtsios, A.; Voglitsis, D.; Perpinias, I.; Korkas, C.; Papanikolaou, N. On the conflict between lvrt and line protection in LV distribution systems with PVs: A current-limitation-based solution. Energies 2019, 12, 2909. [Google Scholar] [CrossRef]

- Kyritsis, A.; Voglitsis, D.; Papanikolaou, N.P.; Tselepis, S.; Christodoulou, C.; Gonos, I.; Kalogirou, S.A. Evolution of PV systems in Greece and review of applicable solutions for higher penetration levels. Renew. Energy 2017, 109, 487–499. [Google Scholar] [CrossRef]

- Xue, Y.; Chang, L.; Kjær, S.B.; Bordonau, J.; Shimizu, T. Topologies of single-phase inverters for small distributed power generators: An overview. IEEE Trans. Power Electron. 2004, 19, 1305–1314. [Google Scholar] [CrossRef]

- Li, Q.; Wolfs, P. A review of the single phase photovoltaic module integrated converter topologies with three different DC link configurations. IEEE Trans. Power Electron. 2008, 23, 1320–1333. [Google Scholar]

- IEEE. IEEE Recommended Practice for Utility Interface of Photovoltaic (PV) Systems; IEEE Standard 929–2000; IEEE: Piscataway, NJ, USA, 2000. [Google Scholar]

- IEEE. IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems; IEEE Standard 1547.1–2005; IEEE: Piscataway, NJ, USA, 2005. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).