Micro- and Nano-Integration in the Production of GaAs and Ga2O3 Nanowire Arrays by Top-Down Design

Abstract

1. Introduction

2. Materials and Methods

3. Results and Discussion

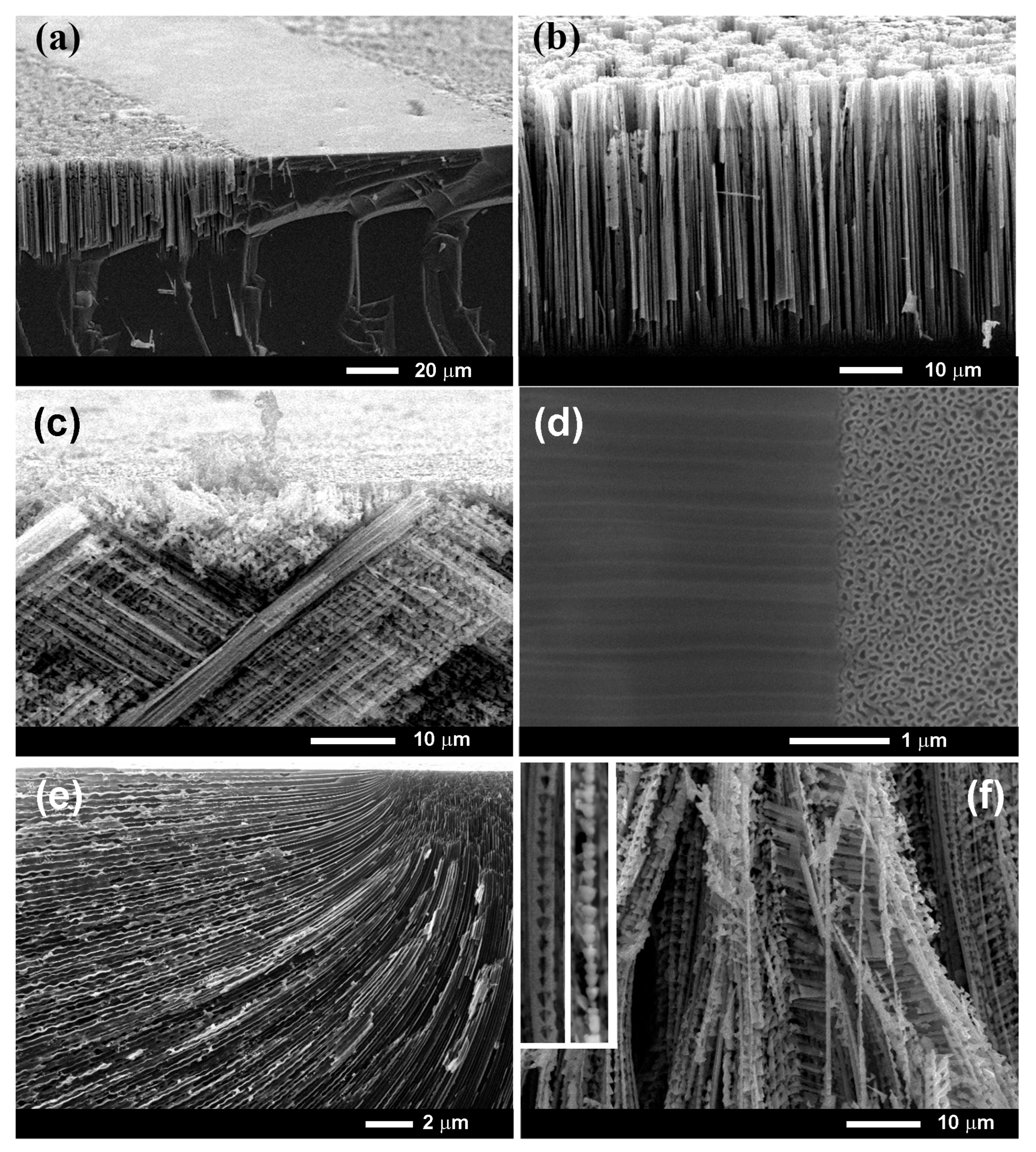

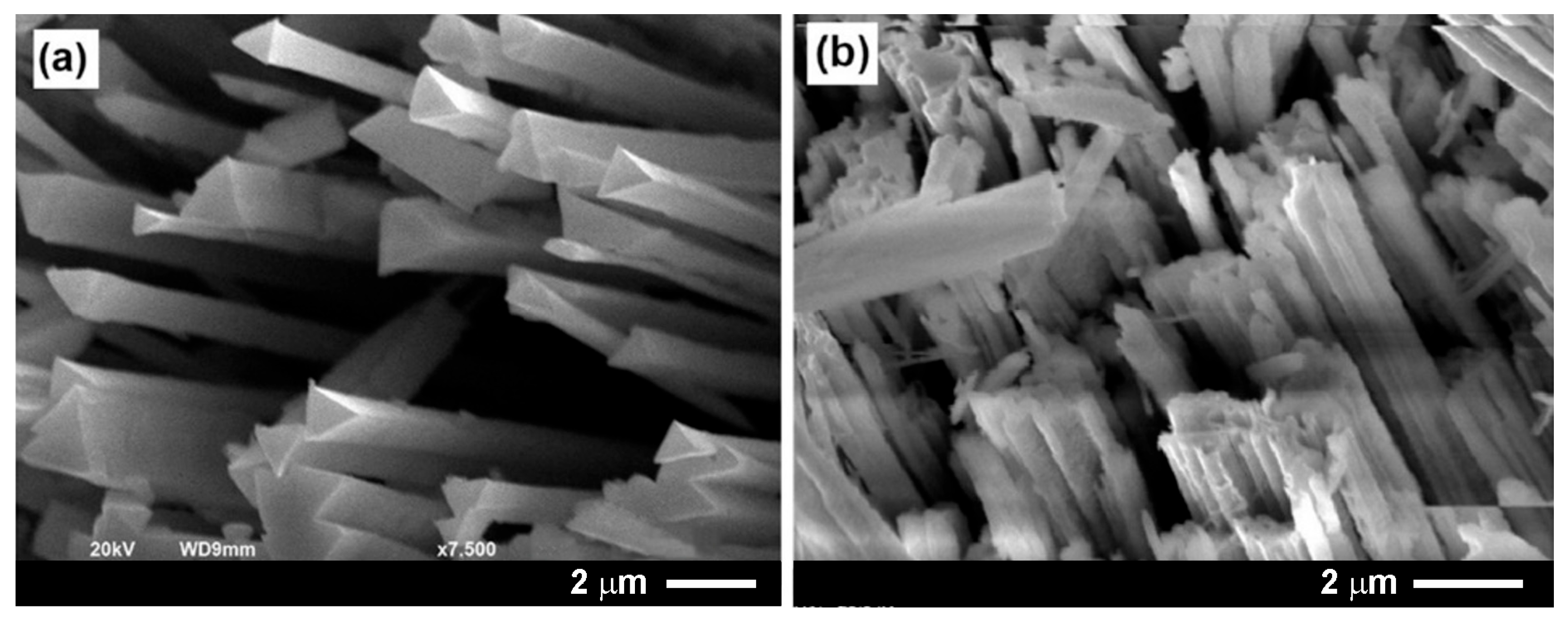

3.1. GaAs Substrate Patterning, Electrochemical Fabrication, and Morphology Control of GaAs Nanowire Arrays

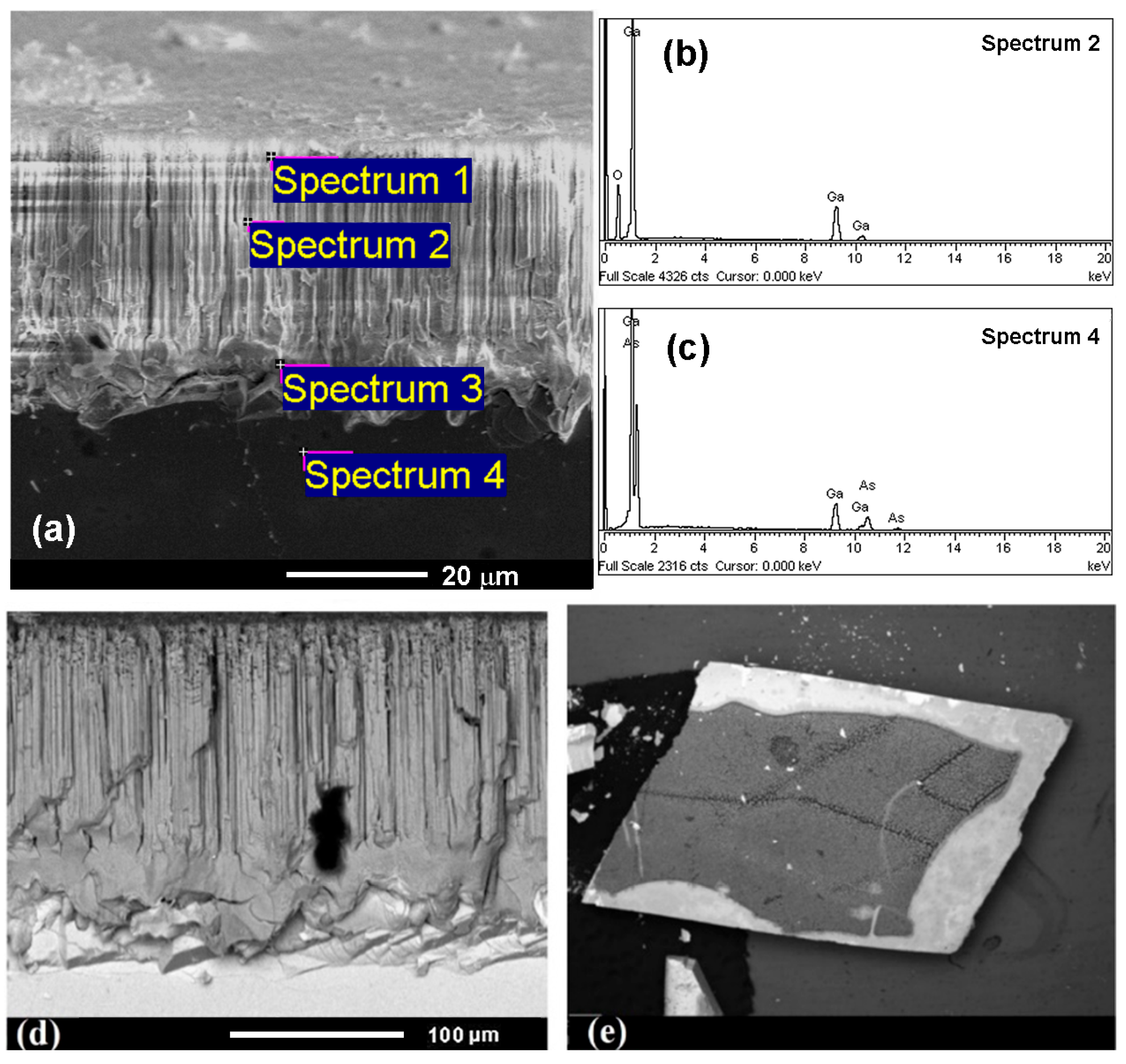

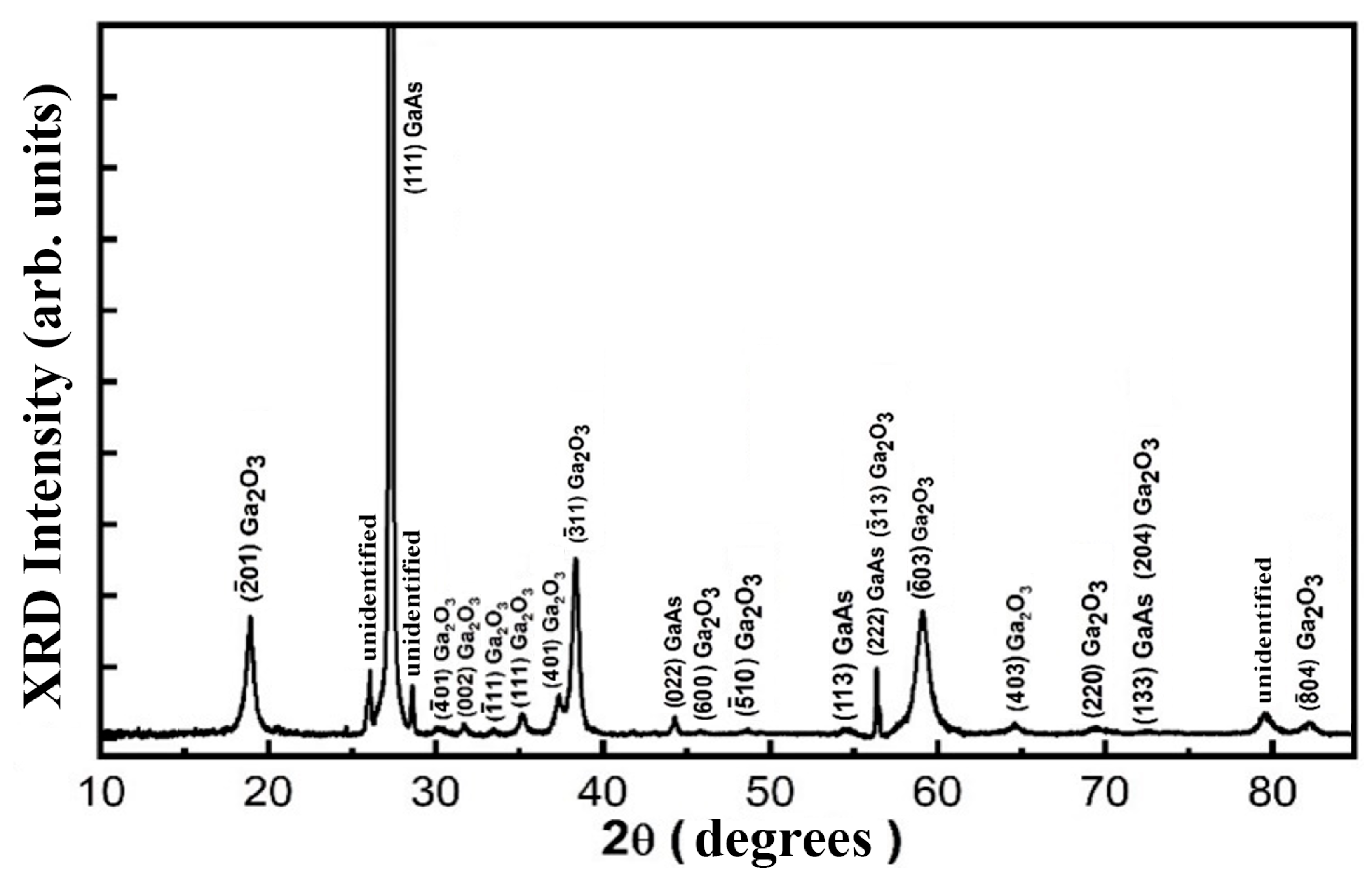

3.2. Selective Oxidation of GaAs Nanowires for Hybrid Semiconductor–Oxide Platforms

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Monaico, E.; Tiginyanu, I.; Ursaki, V. Porous Semiconductor Compounds. Semicond. Sci. Technol. 2020, 35, 103001. [Google Scholar] [CrossRef]

- Canham, L.T. Nanostructured Silicon as an Active Optoelectronic Material. In Frontiers of Nano-Optoelectronic Systems; Pavesi, L., Buzaneva, E., Eds.; Springer: Dordrecht, The Netherlands, 2000; pp. 85–97. [Google Scholar] [CrossRef]

- Boehringer, M.; Artmann, H.; Witt, K. Porous Silicon in a Semiconductor Manufacturing Environment. J. Microelectromechanical Syst. 2012, 21, 1375–1381. [Google Scholar] [CrossRef]

- Gautier, G.; Defforge, T.; Desplobain, S.; Billoué, J.; Capelle, M.; Povéda, P.; Vanga, K.; Lu, B.; Bardet, B.; Lascaud, J.; et al. Porous Silicon in Microelectronics: From Academic Studies to Industry. ECS Trans. 2015, 6i9, 123. [Google Scholar] [CrossRef]

- Karbassian, F. Porous Silicon. In Porosity—Process, Technologies and Applications; IntechOpen: London, UK, 2018; pp. 3–36. [Google Scholar] [CrossRef]

- Koshida, N.; Nakamura, T. Emerging Functions of Nanostructured Porous Silicon—With a Focus on the Emissive Properties of Photons, Electrons, and Ultrasound. Front. Chem. 2019, 7, 273. [Google Scholar] [CrossRef] [PubMed]

- Zhang, L.; Wang, S.; Shao, Y.; Wu, Y.; Sun, C.; Huo, Q.; Zhang, B.; Hu, H.; Hao, X. One-Step Fabrication of Porous GaN Crystal Membrane and Its Application in Energy Storage. Sci. Rep. 2017, 7, 44063. [Google Scholar] [CrossRef] [PubMed]

- Hou, F.; Zhang, M.-R.; Jiang, Q.-M.; Wang, Z.-G.; Yan, J.-H.; Pan, G.-B. Fabrication and Photoluminescence Performance of Porous Gallium Nitride Luminescent Materials Using Different 1-Ethyl-3-Methylimidazolium-Based Ionic Liquids. Mater. Lett. 2018, 223, 194–197. [Google Scholar] [CrossRef]

- Gryn, S.; Nychyporuk, T.; Bezverkhyy, I.; Korytko, D.; Iablokov, V.; Lysenko, V.; Alekseev, S. Mesoporous SiC with Potential Catalytic Application by Electrochemical Dissolution of Polycrystalline 3C-SiC. ACS Appl. Nano Mater. 2018, 1, 2609–2620. [Google Scholar] [CrossRef]

- Milovanov, Y.S.; Skryshevsky, V.A.; Gavrilchenko, I.V.; Kostiukevych, O.M.; Gryn, S.V.; Alekseev, S.A. Ethanol Gas Sensing Performance of Electrochemically Anodized Freestanding Porous SiC. Diam. Relat. Mater. 2019, 91, 84–89. [Google Scholar] [CrossRef]

- Milovanov, Y.; Skryshevsky, V.; Gavrilchenko, I.; Oksanich, A.; Pritchin, S.; Kogdas, M. Electrical Properties of Metal-Porous GaAs Structure at Water Adsorption. J. Electron. Mater. 2019, 48, 2587–2592. [Google Scholar] [CrossRef]

- Rad, Z.J.; Laaksonen, J.; Alitupa, V.; Miettinen, M.; Iltanen, K.; Lehtiö, J.-P.; Granroth, S.; Angervo, I.; Punkkinen, M.; Punkkinen, R.; et al. Below 1% Reflectance for Black GaAs Surface Prepared by Facile Two-Step Wet Chemical Treatment: Hydrogen Peroxide and Water. Adv. Photonics Res. 2025, 6, 2400200. [Google Scholar] [CrossRef]

- Suchikova, Y.; Nazarovets, S.; Popov, A.I. Electrochemical Etching vs. Electrochemical Deposition: A Comparative Bibliometric Analysis. Electrochem 2025, 6, 18. [Google Scholar] [CrossRef]

- Cao, D.; Wang, B.; Lu, D.; Zhou, X.; Ma, X. Preparation and Novel Photoluminescence Properties of the Self-Supporting Nanoporous InP Thin Films. Sci. Rep. 2020, 10, 20564. [Google Scholar] [CrossRef]

- Li, B.; Mi, C.; Kang, J.-H.; Li, H.; Elafandy, R.T.; Lai, W.-C.; Sheu, J.-K.; Han, J. Photonic Engineering of InP towards Homoepitaxial Short-Wavelength Infrared VCSELs. Optica 2024, 11, 113–119. [Google Scholar] [CrossRef]

- Acikgoz, S.; Yungevis, H.; Tor, N. Fabrication and Optical Characterization of V-Shaped Micro/Nano-Grooves on Indium Phosphide Surface through Double Cell Electrochemical Etching. Appl. Phys. A 2025, 131, 291. [Google Scholar] [CrossRef]

- Revenant, C.; Benwadih, M.; Proux, O. Local structure around Zn and Ga in solution-processed In-Ga-Zn-O and implications for electronic properties. Phys. Status Solidi (RRL) 2015, 9, 652–655. [Google Scholar] [CrossRef]

- Revenant, C.; Benwadih, M. Morphology of sol-gel porous In-Ga-Zn-O thin films as a function of annealing temperatures. Thin Solid Films 2016, 643–648. [Google Scholar] [CrossRef]

- Peng, K.; Parkinson, P.; Gao, Q.; Boland, J.L.; Li, Z.; Wang, F.; Mokkapati, S.; Fu, L.; Johnston, M.B.; Tan, H.H.; et al. Single N+-i-N+ InP Nanowires for Highly Sensitive Terahertz Detection. Nanotechnology 2017, 28, 125202. [Google Scholar] [CrossRef]

- Shafi, A.M.; Das, S.; Khayrudinov, V.; Ding, E.-X.; Uddin, M.G.; Ahmed, F.; Sun, Z.; Lipsanen, H. Direct Epitaxial Growth of InP Nanowires on MoS2 with Strong Nonlinear Optical Response. Chem. Mater. 2022, 34, 9055–9061. [Google Scholar] [CrossRef]

- Boulanger, J.P.; LaPierre, R.R. Patterned Gold-Assisted Growth of GaP Nanowires on Si. Semicond. Sci. Technol. 2012, 27, 035002. [Google Scholar] [CrossRef]

- Czaban, J.A.; Thompson, D.A.; LaPierre, R.R. GaAs Core−Shell Nanowires for Photovoltaic Applications. Nano Lett. 2009, 9, 148–154. [Google Scholar] [CrossRef]

- Maliakkal, C.B.; Jacobsson, D.; Tornberg, M.; Persson, A.R.; Johansson, J.; Wallenberg, R.; Dick, K.A. In Situ Analysis of Catalyst Composition during Gold Catalyzed GaAs Nanowire Growth. Nat. Commun. 2019, 10, 4577. [Google Scholar] [CrossRef]

- Maliakkal, C.B.; Tornberg, M.; Jacobsson, D.; Lehmann, S.; Dick, K.A. Vapor–Solid–Solid Growth Dynamics in GaAs Nanowires. Nanoscale Adv. 2021, 3, 5928–5940. [Google Scholar] [CrossRef]

- Jansen, M.M.; Perla, P.; Kaladzhian, M.; von den Driesch, N.; Janßen, J.; Luysberg, M.; Lepsa, M.I.; Grützmacher, D.; Pawlis, A. Phase-Pure Wurtzite GaAs Nanowires Grown by Self-Catalyzed Selective Area Molecular Beam Epitaxy for Advanced Laser Devices and Quantum Disks. ACS Appl. Nano Mater. 2020, 3, 11037–11047. [Google Scholar] [CrossRef]

- Tomioka, K.; Yoshimura, M.; Fukui, T. A III–V Nanowire Channel on Silicon for High-Performance Vertical Transistors. Nature 2012, 488, 189–192. [Google Scholar] [CrossRef] [PubMed]

- Kang, Y.; Hou, X.; Zhang, Z.; Tang, J.; Lin, F.; Li, K.; Hao, Q.; Wei, Z. Ultrahigh-performance and broadband photodetector from visible to shortwave infrared band based on GaAsSb nanowires. Chem. Eng. J. 2024, 501, 157392. [Google Scholar] [CrossRef]

- Kang, Y.; Hou, X.; Zhang, Z.; Meng, B.; Tang, J.; Hao, Q.; Wei, Z. Enhanced Visible-NIR Dual-Band Performance of GaAs Nanowire Photodetectors Through Phase Manipulation. Adv. Opt. Mater. 2025, 13, 2500289. [Google Scholar] [CrossRef]

- Abdullah, A.; Kulkarni, M.A.; Thaalbi, H.; Tariq, F.; Ryu, S.-W. Epitaxial Growth of 1D GaN-Based Heterostructures on Various Substrates for Photonic and Energy Applications. Nanoscale Adv. 2023, 5, 1023–1042. [Google Scholar] [CrossRef]

- Johar, M.A.; Song, H.-G.; Waseem, A.; Hassan, M.A.; Bagal, I.V.; Cho, Y.-H.; Ryu, S.-W. Universal and Scalable Route to Fabricate GaN Nanowire-Based LED on Amorphous Substrate by MOCVD. Appl. Mater. Today 2020, 19, 100541. [Google Scholar] [CrossRef]

- Shugurov, K.; Mozharov, A.; Sapunov, G.; Fedorov, V.; Tchernycheva, M.; Mukhin, I. Single GaN Nanowires for Extremely High Current Commutation. Phys. Status Solidi (RRL)–Rapid Res. Lett. 2021, 15, 2000590. [Google Scholar] [CrossRef]

- Kumar, S.; Fossard, F.; Amiri, G.; Chauveau, J.-M.; Sallet, V. MOCVD Growth and Structural Properties of ZnS Nanowires: A Case Study of Polytypism. Nanomaterials 2022, 12, 2323. [Google Scholar] [CrossRef]

- Kennedy, O.W.; White, E.R.; Shaffer, M.S.P.; Warburton, P.A. Vapour-Liquid-Solid Growth of ZnO-ZnMgO Core–Shell Nanowires by Gold-Catalysed Molecular Beam Epitaxy. Nanotechnology 2019, 30, 194001. [Google Scholar] [CrossRef]

- Galdámez-Martinez, A.; Santana, G.; Güell, F.; Martínez-Alanis, P.R.; Dutt, A. Photoluminescence of ZnO Nanowires: A Review. Nanomaterials 2020, 10, 857. [Google Scholar] [CrossRef]

- Mirzaei, A.; Lee, M.H.; Pawar, K.K.; Bharath, S.P.; Kim, T.-U.; Kim, J.-Y.; Kim, S.S.; Kim, H.W. Metal Oxide Nanowires Grown by a Vapor–Liquid–Solid Growth Mechanism for Resistive Gas-Sensing Applications: An Overview. Materials 2023, 16, 6233. [Google Scholar] [CrossRef]

- Güniat, L.; Caroff, P.; Fontcuberta i Morral, A. Vapor Phase Growth of Semiconductor Nanowires: Key Developments and Open Questions. Chem. Rev. 2019, 119, 8958–8971. [Google Scholar] [CrossRef]

- Dubrovskii, V.G.; Glas, F. Vapor–Liquid–Solid Growth of Semiconductor Nanowires. In Fundamental Properties of Semiconductor Nanowires; Fukata, N., Rurali, R., Eds.; Springer: Singapore, 2021; pp. 3–107. [Google Scholar] [CrossRef]

- Monaico, E.; Tiginyanu, I.; Volciuc, O.; Mehrtens, T.; Rosenauer, A.; Gutowski, J.; Nielsch, K. Formation of InP Nanomembranes and Nanowires under Fast Anodic Etching of Bulk Substrates. Electrochem. Commun. 2014, 47, 29–32. [Google Scholar] [CrossRef]

- Asoh, H.; Kotaka, S.; Ono, S. High-Aspect-Ratio GaAs Pores and Pillars with Triangular Cross Section. Electrochem. Commun. 2011, 13, 458–461. [Google Scholar] [CrossRef]

- Ono, S.; Kotaka, S.; Asoh, H. Fabrication and Structure Modulation of High-Aspect-Ratio Porous GaAs through Anisotropic Chemical Etching, Anodic Etching, and Anodic Oxidation. Electrochim. Acta 2013, 110, 393–401. [Google Scholar] [CrossRef]

- Li, X.; Guo, Z.; Xiao, Y.; Um, H.-D.; Lee, J.-H. Electrochemically Etched Pores and Wires on Smooth and Textured GaAs Surfaces. Electrochim. Acta 2011, 56, 5071–5079. [Google Scholar] [CrossRef]

- Asoh, H.; Kotaka, S.; Ono, S. High-Aspect-Ratio Vertically Aligned GaAs Nanowires Fabricated by Anodic Etching. Mater. Res. Express 2014, 1, 045002. [Google Scholar] [CrossRef]

- Monaico, E.I.; Monaico, E.V.; Ursaki, V.V.; Honnali, S.; Postolache, V.; Leistner, K.; Nielsch, K.; Tiginyanu, I.M. Electrochemical Nanostructuring of (111) Oriented GaAs Crystals: From Porous Structures to Nanowires. Beilstein J. Nanotechnol. 2020, 11, 966–975. [Google Scholar] [CrossRef]

- Monaico, E.V.; Morari, V.; Ursaki, V.V.; Nielsch, K.; Tiginyanu, I.M. Core–Shell GaAs-Fe Nanowire Arrays: Fabrication Using Electrochemical Etching and Deposition and Study of Their Magnetic Properties. Nanomaterials 2022, 12, 1506. [Google Scholar] [CrossRef]

- Monaico, E.V.; Monaico, E.I.; Ursaki, V.V.; Tiginyanu, I.M. Porous Semiconductor Compounds with Engineered Morphology as a Platform for Various Applications. Phys. Status Solidi (RRL)–Rapid Res. Lett. 2023, 17, 2300039. [Google Scholar] [CrossRef]

- Ursaki, V.V.; Lehmann, S.; Zalamai, V.V.; Morari, V.; Nielsch, K.; Tiginyanu, I.M.; Monaico, E.V. Core–Shell Structures Prepared by Atomic Layer Deposition on GaAs Nanowires. Crystals 2022, 12, 1145. [Google Scholar] [CrossRef]

- Monaico, E.I.; Monaico, E.V.; Ursaki, V.V.; Tiginyanu, I.M. Controlled Electroplating of Noble Metals on III-V Semiconductor Nanotemplates Fabricated by Anodic Etching of Bulk Substrates. Coatings 2022, 12, 1521. [Google Scholar] [CrossRef]

- Langa, S.; Carstensen, J.; Christophersen, M.; Steen, K.; Frey, S.; Tiginyanu, I.M.; Föll, H. Uniform and Nonuniform Nucleation of Pores during the Anodization of Si, Ge, and III-V Semiconductors. J. Electrochem. Soc. 2005, 152, C525. [Google Scholar] [CrossRef]

- Shi, F.; Qiao, H. Influence of Hydrothermal Reaction Time on Crystal Qualities and Photoluminescence Properties of β-Ga2O3 Nanorods. J. Mater. Sci. Mater. Electron. 2020, 31, 20223–20231. [Google Scholar] [CrossRef]

- Drygaś, M.; Jeleń, P.; Radecka, M.; Janik, J.F. Ammonolysis of Polycrystalline and Amorphized Gallium Arsenide GaAs to Polytype-Specific Nanopowders of Gallium Nitride GaN. RSC Adv. 2016, 6, 41074–41086. [Google Scholar] [CrossRef]

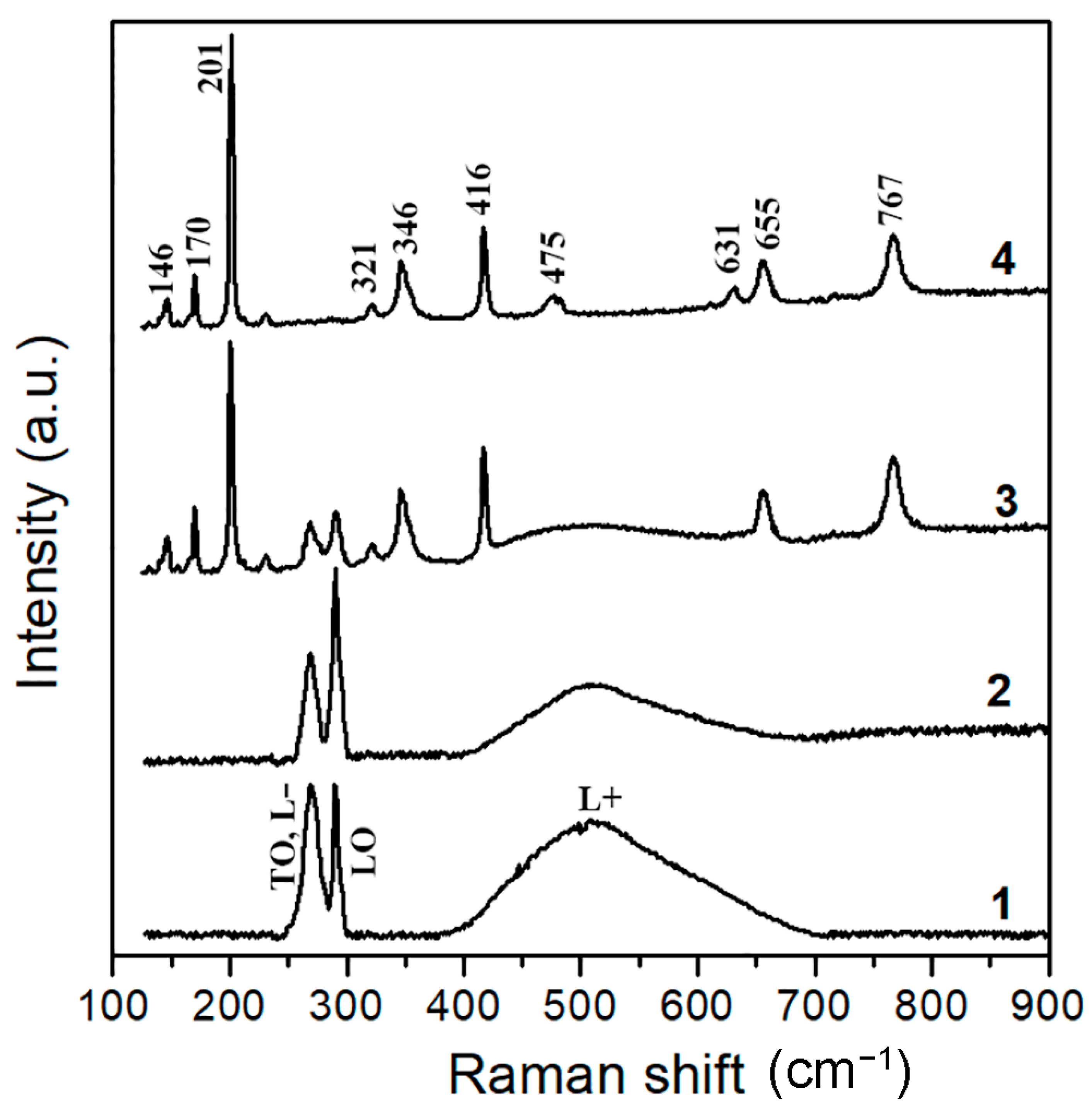

- Abstreiter, G.; Bauser, E.; Fischer, A.; Ploog, K. Raman Spectroscopy a Versatile Tool for Characterization of Thin Films and Heterostructures of GaAs and AlxGal-xAs. Appl. Phys. 1978, 16, 345–352. [Google Scholar] [CrossRef]

- Kranert, C.; Sturm, C.; Schmidt-Grund, R.; Grundmann, M. Raman tensor elements of-Ga2O3. Sci. Rep. 2016, 6, 35964. [Google Scholar] [CrossRef]

- Mao, H.; Alhalaili, B.; Kaya, A.; Dryden, D.M.; Woodall, J.M.; Islam, M.S. Oxidation of GaAs substrates to enable β-Ga2O3 films for sensors and optoelectronic devices. SPIE 10381, Wide Bandgap Power Devices and Applications II. In Proceedings of the SPIE Optical Engineering + Applications, San Diego, CA, USA, 6–10 August 2017; p. 103810B. [Google Scholar] [CrossRef]

- Bayam, Y.; Logeeswaran, V.J.; Katzenmeyer, A.M.; Sadeghian, R.B.; Chacon, R.J.; Wong, M.C.; Hunt, C.E.; Motomiya, K.; Jeyadevan, B.; Islam, M.S. Synthesis of Ga2O3 Nanorods with Ultra-Sharp Tips for High-Performance Field Emission Devices. Sci. Adv. Mater. 2015, 7, 211–218. [Google Scholar] [CrossRef][Green Version]

- Lowes, T.D.; Zinke-Allmang, M. Microscopic study of cluster formation in the Ga on GaAs(001) system. J. Appl. Phys. 1993, 73, 4937–4941. [Google Scholar] [CrossRef]

- Zhou, Z.Y.; Zheng, C.X.; Tang, W.X.; Jesson, D.E.; Tersoff, J. Congruent evaporation temperature of GaAs(001) controlled by As flux. Appl. Phys. Lett. 2010, 97, 121912–121914. [Google Scholar] [CrossRef]

- Chen, W.; Jiao, T.; Li, Z.; Diao, Z.; Li, Z.; Dong, X.; Zhang, Y.; Zhang, B. Preparation of β-Ga2O3 nanostructured films by thermal oxidation of GaAs substrate. Ceram. Int. 2022, 48, 5698–5703. [Google Scholar] [CrossRef]

- Kaya, A.; Dryden, D.M.; Woodall, J.M.; Islam, M.S. Spontaneous delamination via compressive buckling facilitates large-scale β-Ga2O3 thin film transfer from reusable GaAs substrates. Phys. Status Solidi (A) 2017, 214, 1700102. [Google Scholar] [CrossRef]

- Chen, W.; Jiao, T.; Chen, P.; Dang, X.; Yu Han, Y.; Yu, H.; Dong, X.; Zhang, Y.; Zhang, B. Preparation of high light-trapping β-Ga2O3 nanorod films via thermal oxidation of GaAs and metal-organic chemical vapor deposition. Mater. Sci. Semicond. Process. 2024, 169, 107912. [Google Scholar] [CrossRef]

- Amith, A. Electron and Phonon Scattering in GaAs at High Temperatures. Phys. Rev. 1965, 138, A1270–A1276. [Google Scholar] [CrossRef]

- Maycock, P.D. Thermal Conductivity of Silicon, Germanium, III–V Compounds and III–V Alloys. Solid-State Electron. 1967, 10, 161–168. [Google Scholar] [CrossRef]

- Guo, Z.; Verma, A.; Wu, X.; Sun, F.; Hickman, A.; Masui, T.; Kuramata, A.; Higashiwaki, M.; Jena, D.; Luo, T. Anisotropic Thermal Conductivity in Single Crystal β-Gallium Oxide. Appl. Phys. Lett. 2015, 106, 111909. [Google Scholar] [CrossRef]

- Bérardan, D.; Guilmeau, E.; Maignan, A.; Raveau, B. In2O3:Ge, a Promising n-Type Thermoelectric Oxide Composite. Solid State Commun. 2008, 146, 97–101. [Google Scholar] [CrossRef]

| Measured Region | Element | Weight % | Atomic % |

|---|---|---|---|

| Spectrum 1 | O K | 24.79 | 58.95 |

| Ga K | 75.21 | 41.05 | |

| Spectrum 2 | O K | 25.10 | 59.35 |

| Ga K | 74.90 | 40.65 | |

| Spectrum 3 | O K | 24.62 | 58.79 |

| Ga K | 73.02 | 40.00 | |

| Spectrum 4 | Ga K | 49.98 | 51.78 |

| As L | 50.02 | 48.22 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Monaico, E.I.; Monaico, E.V.; Ursaki, V.V.; Tiginyanu, I.M. Micro- and Nano-Integration in the Production of GaAs and Ga2O3 Nanowire Arrays by Top-Down Design. J. Manuf. Mater. Process. 2025, 9, 376. https://doi.org/10.3390/jmmp9110376

Monaico EI, Monaico EV, Ursaki VV, Tiginyanu IM. Micro- and Nano-Integration in the Production of GaAs and Ga2O3 Nanowire Arrays by Top-Down Design. Journal of Manufacturing and Materials Processing. 2025; 9(11):376. https://doi.org/10.3390/jmmp9110376

Chicago/Turabian StyleMonaico, Elena I., Eduard V. Monaico, Veaceslav V. Ursaki, and Ion M. Tiginyanu. 2025. "Micro- and Nano-Integration in the Production of GaAs and Ga2O3 Nanowire Arrays by Top-Down Design" Journal of Manufacturing and Materials Processing 9, no. 11: 376. https://doi.org/10.3390/jmmp9110376

APA StyleMonaico, E. I., Monaico, E. V., Ursaki, V. V., & Tiginyanu, I. M. (2025). Micro- and Nano-Integration in the Production of GaAs and Ga2O3 Nanowire Arrays by Top-Down Design. Journal of Manufacturing and Materials Processing, 9(11), 376. https://doi.org/10.3390/jmmp9110376