A CMOS-Based Thermopile Array Fabricated on a Single SiO2 Membrane †

Abstract

:1. Introduction

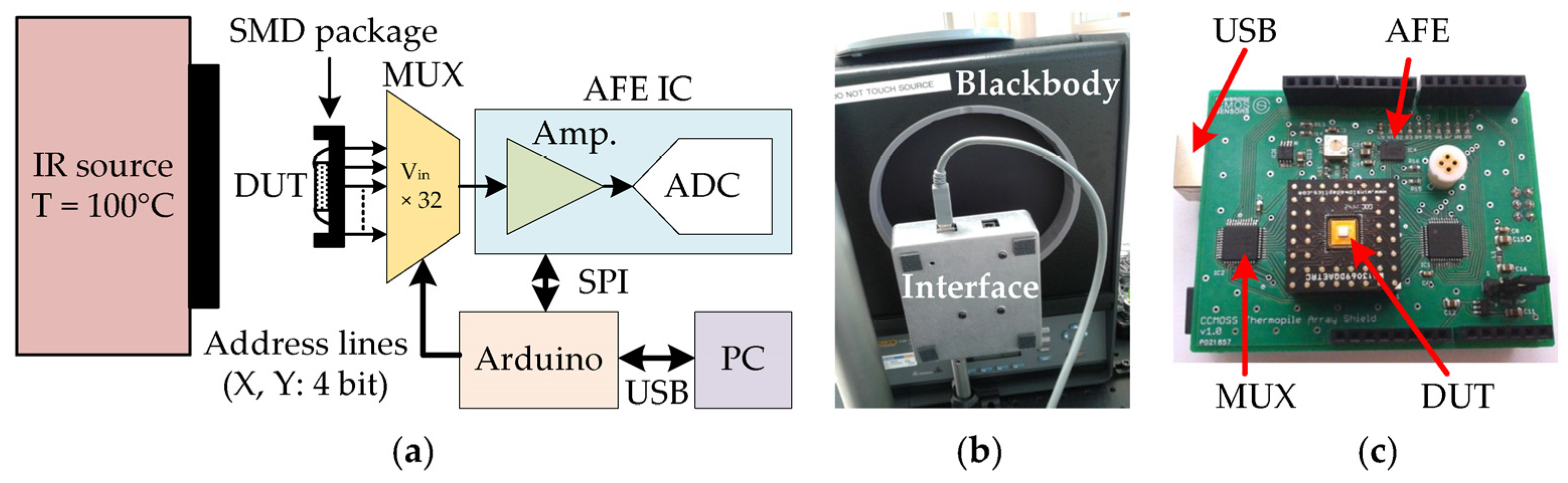

2. Device Fabrication

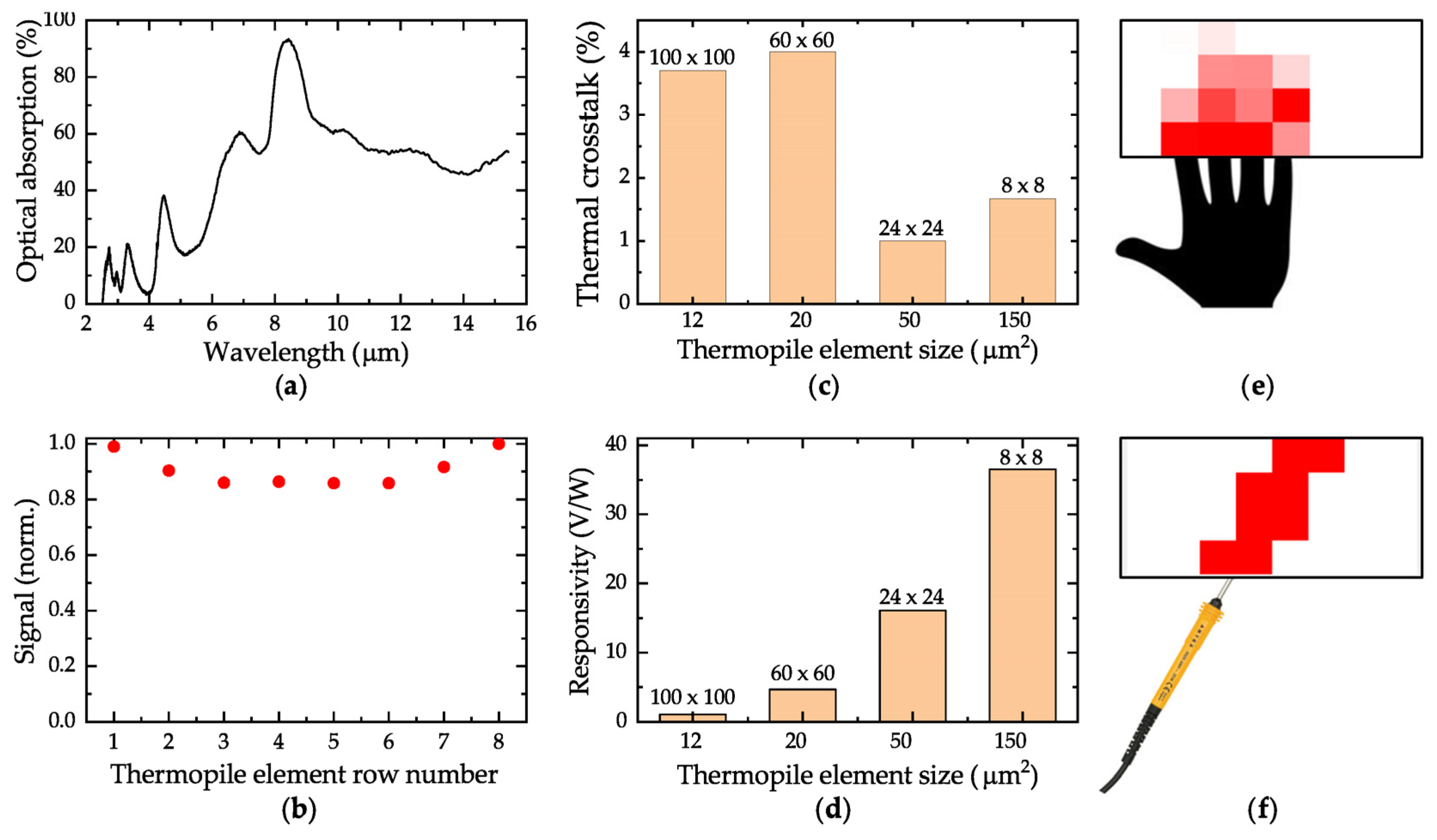

3. Results and Discussions

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kimata, M. Uncooled infrared focal plane arrays. IEEJ Trans. Electr. Electron. Eng. 2017, 13, 4–12. [Google Scholar] [CrossRef]

- Udrea, F.; Luca, A.D. CMOS technology platform for ubiquitous microsensors. In Proceedings of the 2017 International Semiconductor Conference (CAS), Sinaia, Romania, 11–14 October 2017; pp. 43–52. [Google Scholar]

- Baltes, H.; Brand, O. CMOS-based microsensors and packaging. Sens. Actuators A Phys. 2001, 92, 1–9. [Google Scholar] [CrossRef]

- Hopper, R.; Ali, S.; Chowdhury, M.; Boual, S.; De Luca, A.; Gardner, J.W.; Udrea, F. A CMOS-MEMS thermopile with an integrated temperature sensing diode for MID-IR thermometry. Procedia Eng. 2014, 87, 1127–1130. [Google Scholar] [CrossRef]

- Van Herwaarden, A.W.; Sarro, P.M. Thermal sensors based on the Seebeck effect. Sens. Actuator 1986, 10, 321–346. [Google Scholar] [CrossRef]

- Oliver, A.; Wise, K. A 1024-element bulk-micromachined thermopile infrared imaging array. Sens. Actuators A Phys. 1999, 73, 222–231. [Google Scholar] [CrossRef]

- Schaufelbuchl, A.; Munich, U.; Menolfi, C.; Brand, O.; Paul O. Huang, Q.; Baltes, H. 256-pixel CMOS-integrated thermoelectric infrared sensor array. In Proceedings of the 14th IEEE International Conference on Micro Electro Mechanical Systems Technical Digest (Cat. No.01CH37090) (MEMS 2001), Interlaken, Switzerland, 25–25 January 2001; Volume 48, pp. 47–54. [Google Scholar] [CrossRef]

- Zappi, P.; Farella, E.; Benini, L. Tracking Motion Direction and Distance with Pyroelectric IR Sensors. IEEE Sens. J. 2010, 10, 1486–1494. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Chip size | 1.76 mm × 1.76 mm |

| Sensor elements | 8 × 8 pixels |

| Thermopile material | n+/p+ Poly-Si |

| Membrane area | 1200 μm × 1200 μm |

| Pixel area | 150 × 150 μm |

| Membrane thickness | 5.17 μm |

| Detector resistance | 201 kΩ |

| ℜ (100 °C, 1 Hz) | 36.5 V/W |

| D* (100 °C, 1 Hz) | /W |

| NEP | |

| Sn | |

| Thermal crosstalk | <2% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hopper, R.; Ali, S.Z.; Boual, S.; Luca, A.D.; Dai, Y.; Popa, D.; Udrea, F. A CMOS-Based Thermopile Array Fabricated on a Single SiO2 Membrane. Proceedings 2018, 2, 878. https://doi.org/10.3390/proceedings2130878

Hopper R, Ali SZ, Boual S, Luca AD, Dai Y, Popa D, Udrea F. A CMOS-Based Thermopile Array Fabricated on a Single SiO2 Membrane. Proceedings. 2018; 2(13):878. https://doi.org/10.3390/proceedings2130878

Chicago/Turabian StyleHopper, Richard, Syed Zeeshan Ali, Sophie Boual, Andrea De Luca, Ying Dai, Daniel Popa, and Florin Udrea. 2018. "A CMOS-Based Thermopile Array Fabricated on a Single SiO2 Membrane" Proceedings 2, no. 13: 878. https://doi.org/10.3390/proceedings2130878

APA StyleHopper, R., Ali, S. Z., Boual, S., Luca, A. D., Dai, Y., Popa, D., & Udrea, F. (2018). A CMOS-Based Thermopile Array Fabricated on a Single SiO2 Membrane. Proceedings, 2(13), 878. https://doi.org/10.3390/proceedings2130878