Universal Integrated Photodetector Platform †

Abstract

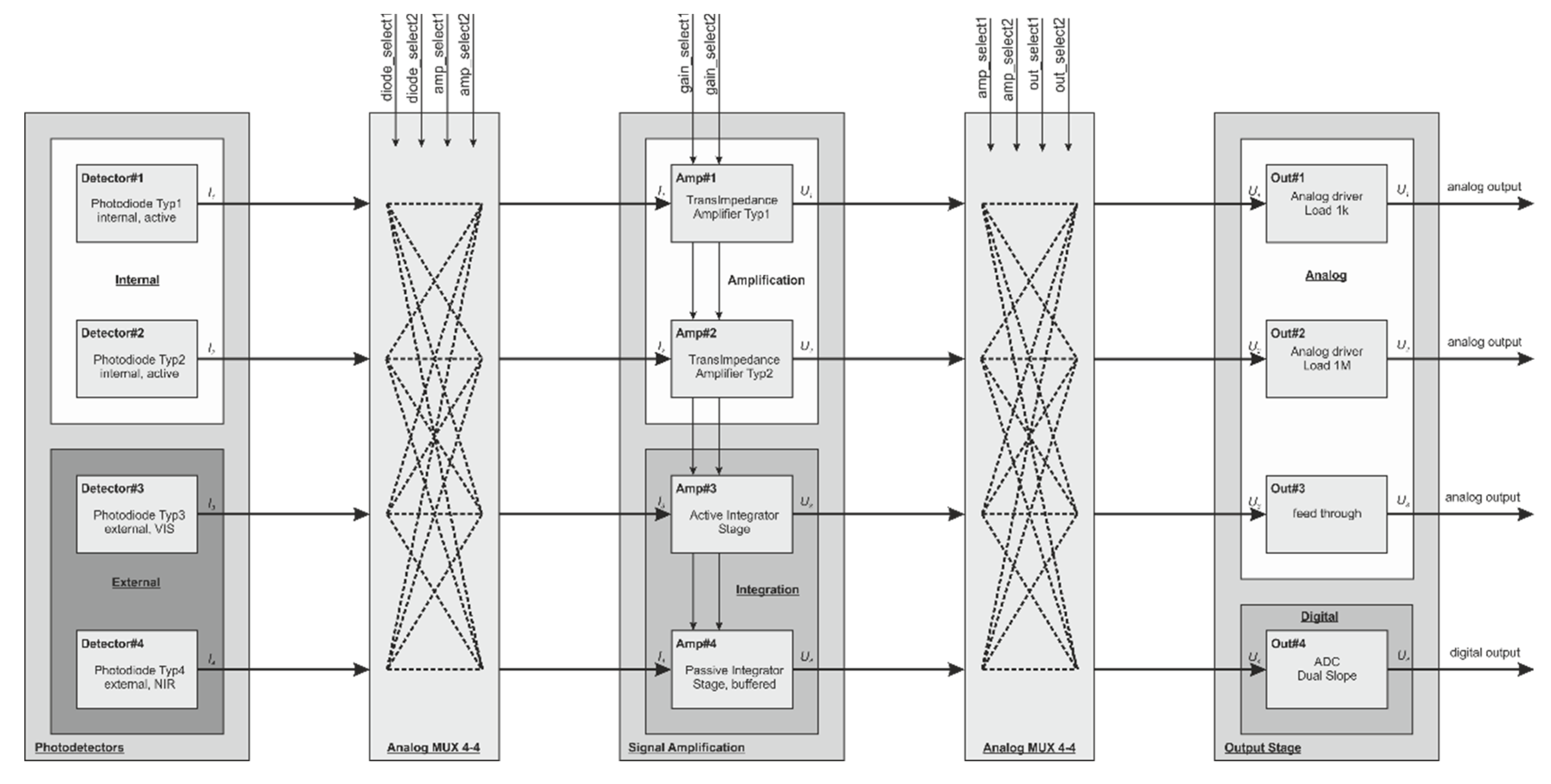

:1. Chip Concept

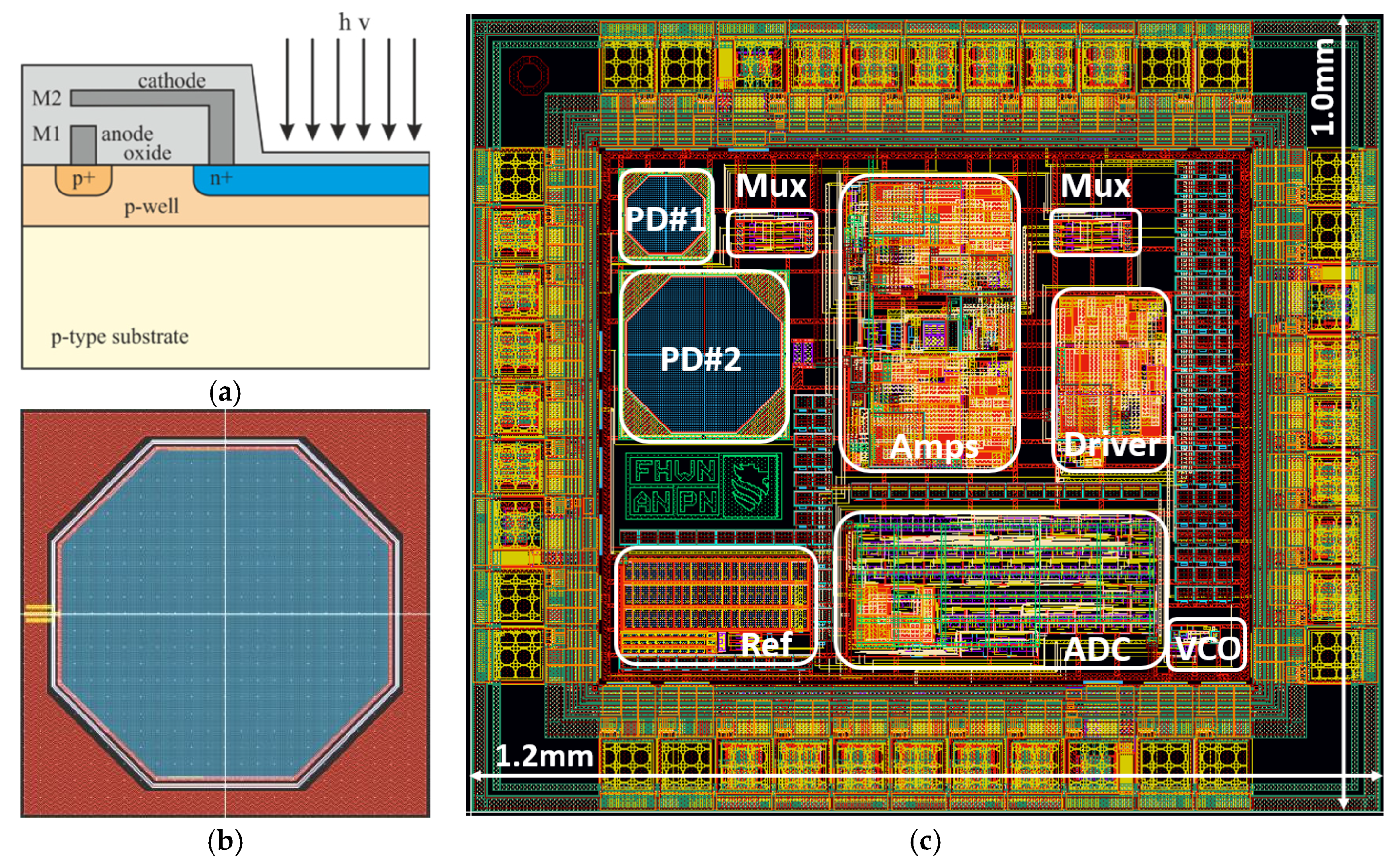

2. Optical Sensor Design

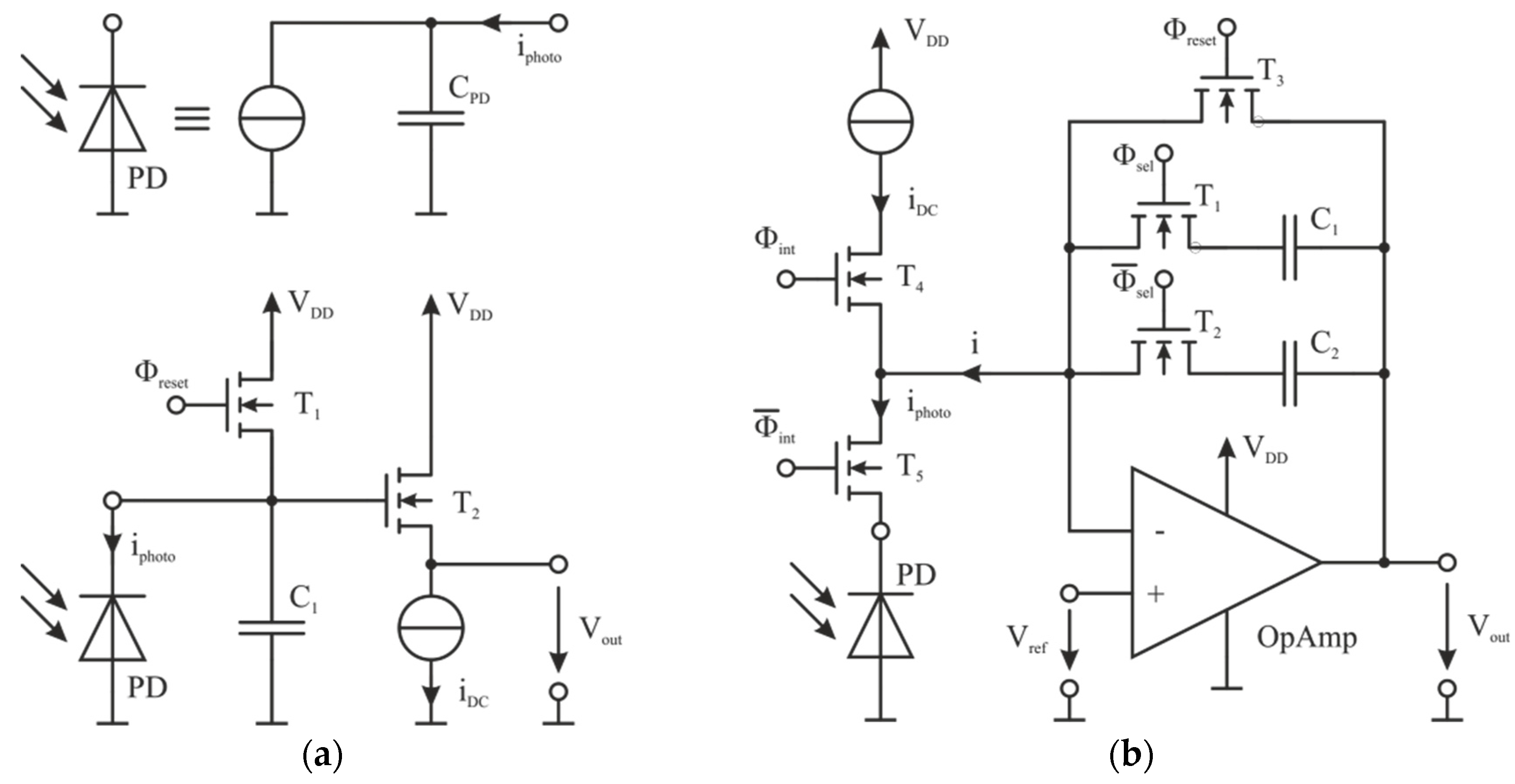

2.1. Photodetection

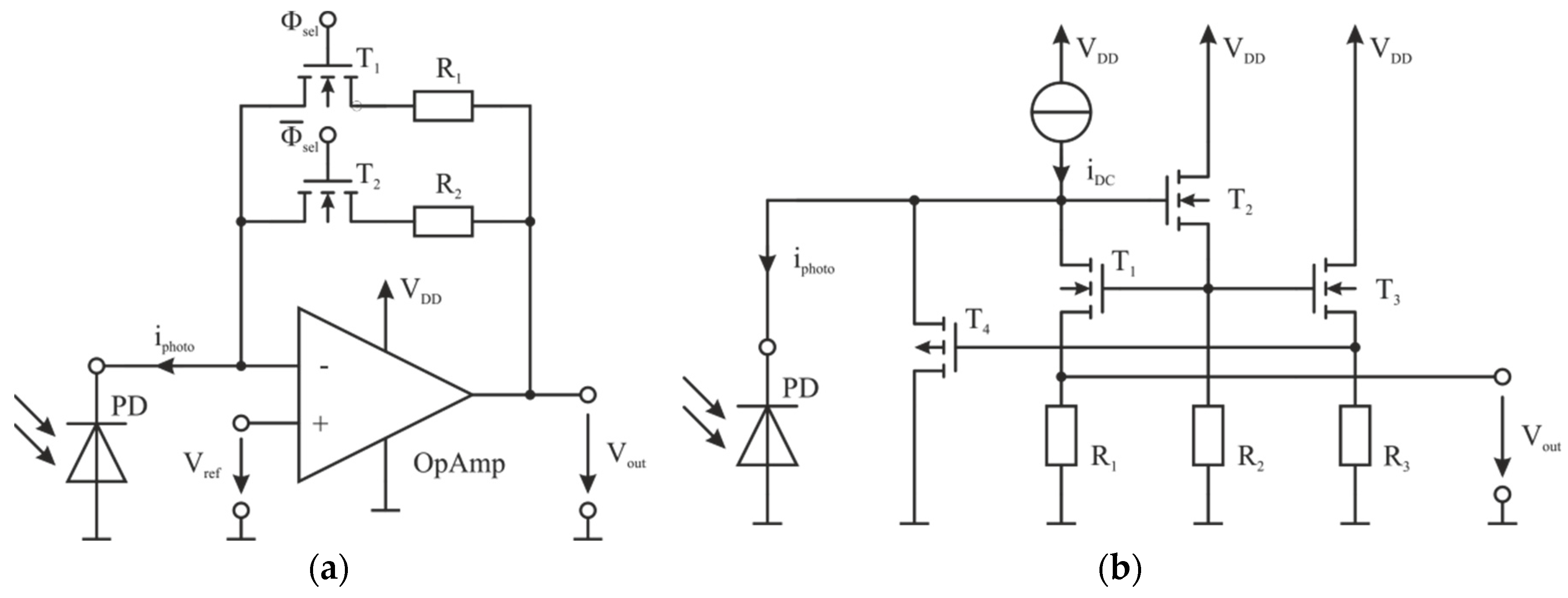

2.2. Amplification

2.3. Functional Blocks

3. Summary

Acknowledgments

References

- Neumann, P. Design eines multifunktionalen integrierten optischen Sensorchips für universelle Anwendungen in 0.18 µm CMOS-Technologie. Bachelor’s Thesis, Univ. Applied Sciences Wr. Neustadt, Wiener Neustadt, Austria, 2017. [Google Scholar]

- Kim, Y.; Lee, S. A 72 dBO 11.43 mA novel CMOS regulated cascode TIA for 3.125 Gb/s optical communications. In Proceedings of the IEEE 26th International SOC Conference, Erlangen, Germany, 4–6 September 2013. [Google Scholar]

- Gamauf, C.; Nemecek, A.; Leisenberger, F. Design and Characterization of an integrated 10 bit Analog to Digital Converter for 100 MSps in 0.18 µm CMOS. In Proceedings of the Austrochip Conference 2014, Graz, Austria, 9 October 2014. [Google Scholar]

| Key Data | |

|---|---|

| Photodiode | internal & external |

| internal PN-diodes | Ø = 100 µm/200 µm |

| Amplification | Integrator & TIA |

| Integrator active/passive | C = 1 pF/10 pF |

| Gain | R = 1 kΩ/5 kΩ/10 kΩ |

| TIA & RGC | f = 280 MHz/28 MHz |

| Output | analog & digital |

| Output driver | R = 1 kΩ/1 MΩ |

| Dual-slope ADC | 10 bit @ 250 kSps |

| Signal routing | 2 x 4:4 MUX |

| Supply | 5 V/<20 mA |

| Technology | 0.18 mm CMOS |

| # Pads | 40 |

| Chip area | A = 1.2 mm2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nemecek, A.; Neumann, P.; Koller, C. Universal Integrated Photodetector Platform. Proceedings 2018, 2, 756. https://doi.org/10.3390/proceedings2130756

Nemecek A, Neumann P, Koller C. Universal Integrated Photodetector Platform. Proceedings. 2018; 2(13):756. https://doi.org/10.3390/proceedings2130756

Chicago/Turabian StyleNemecek, Alexander, Philipp Neumann, and Christian Koller. 2018. "Universal Integrated Photodetector Platform" Proceedings 2, no. 13: 756. https://doi.org/10.3390/proceedings2130756

APA StyleNemecek, A., Neumann, P., & Koller, C. (2018). Universal Integrated Photodetector Platform. Proceedings, 2(13), 756. https://doi.org/10.3390/proceedings2130756