Low-Offset In-Plane Sensitive Hall Arrangement †

Abstract

:1. Introduction

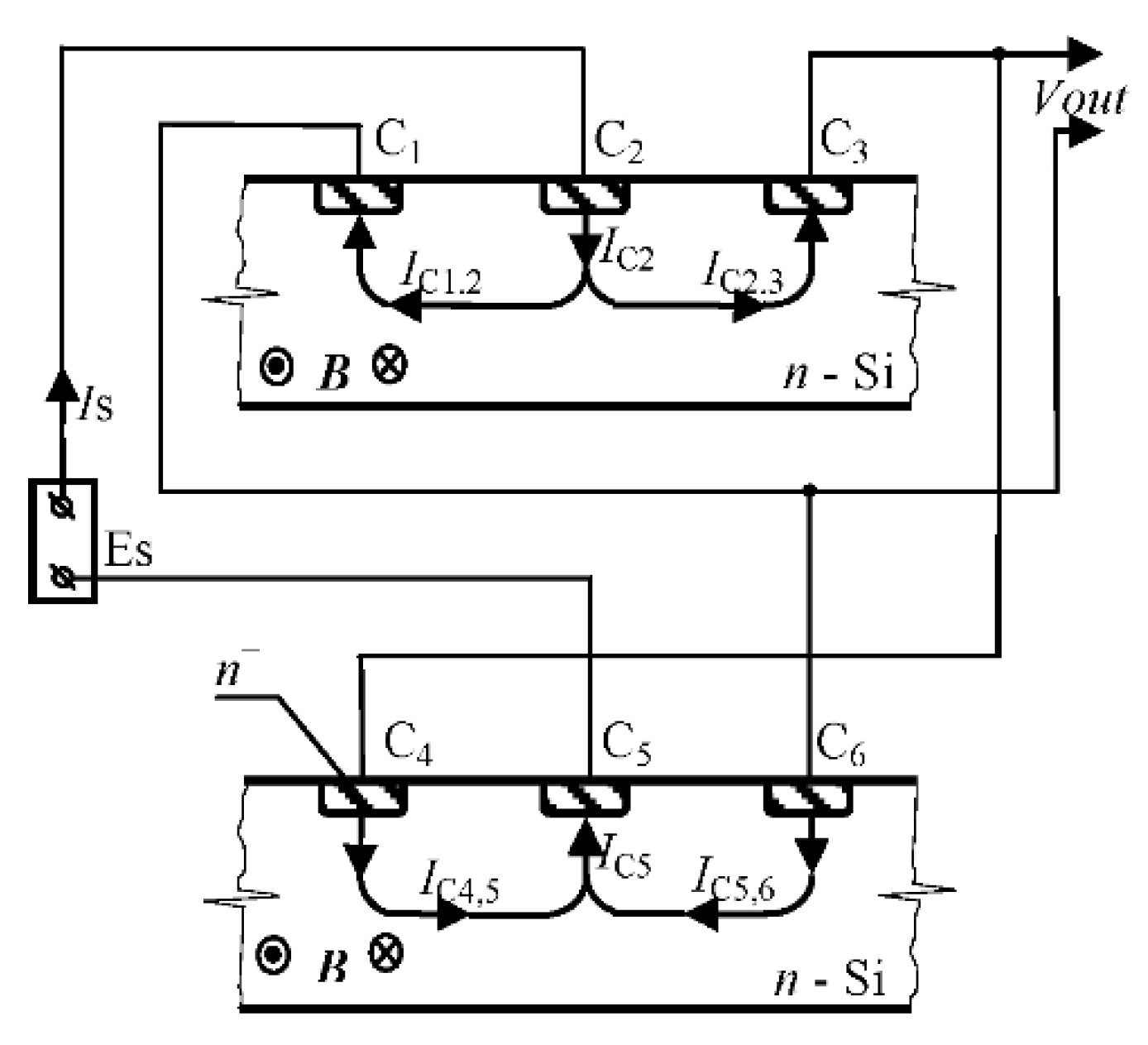

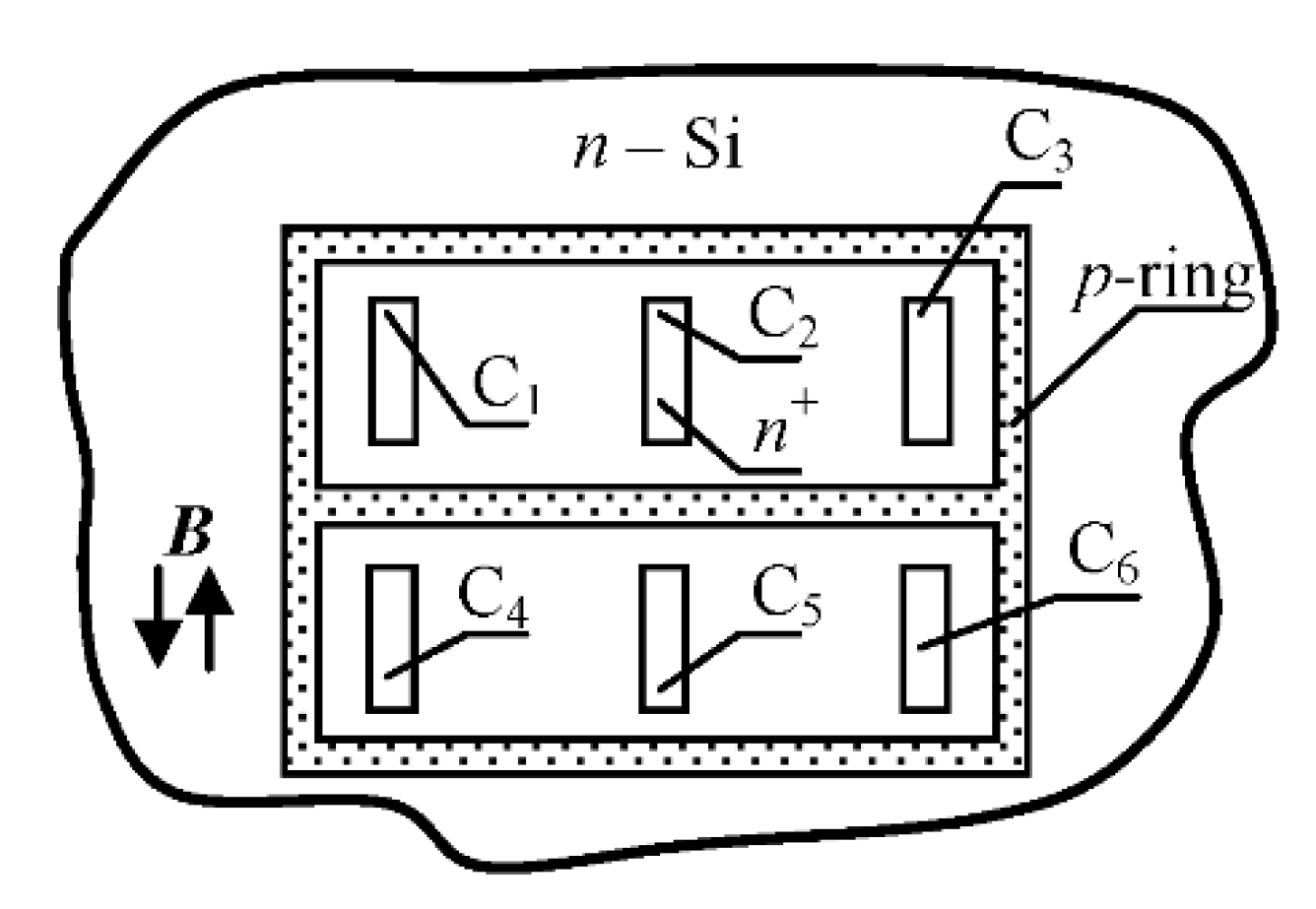

2. Sensor Layout and Operation Principle

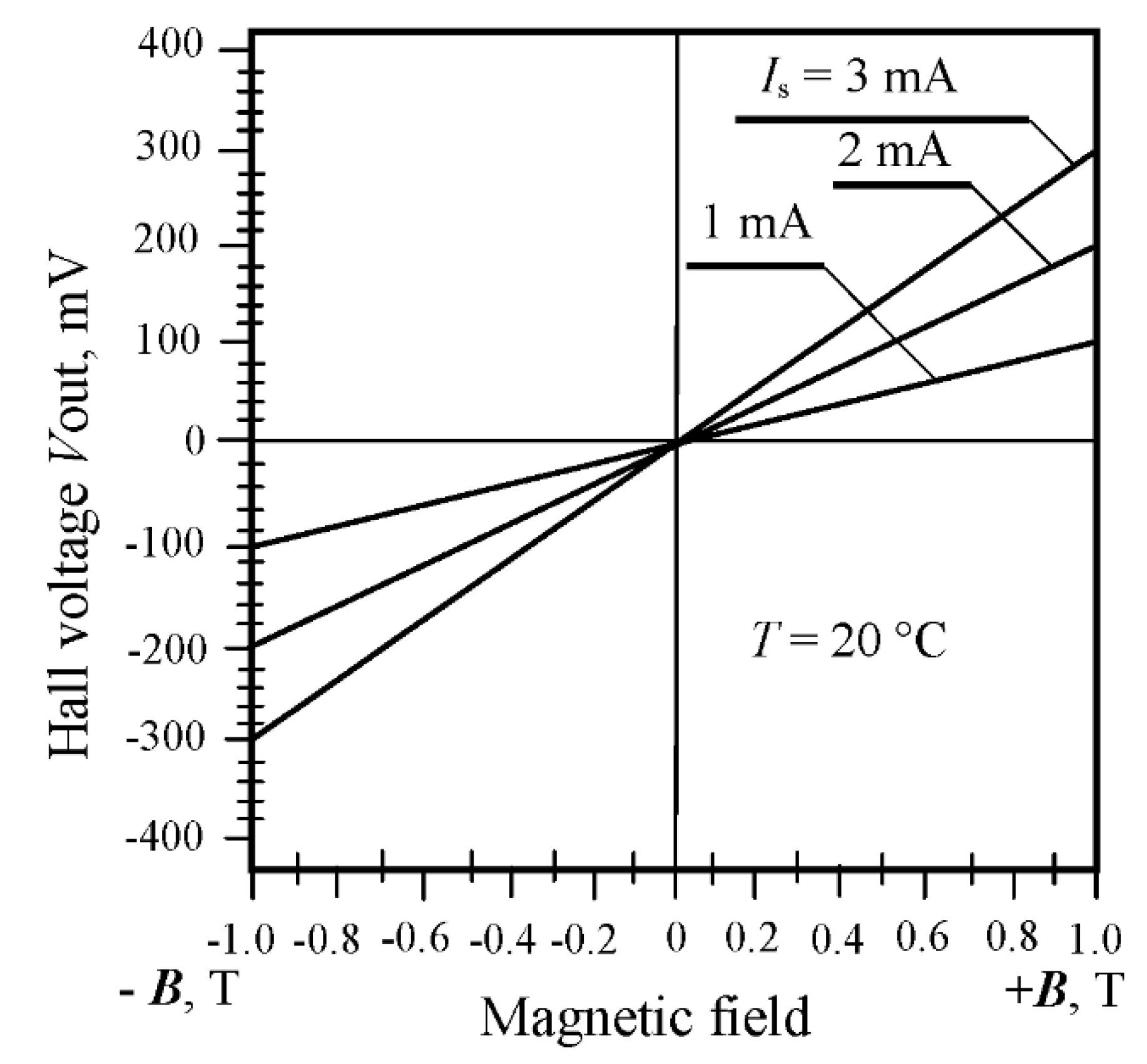

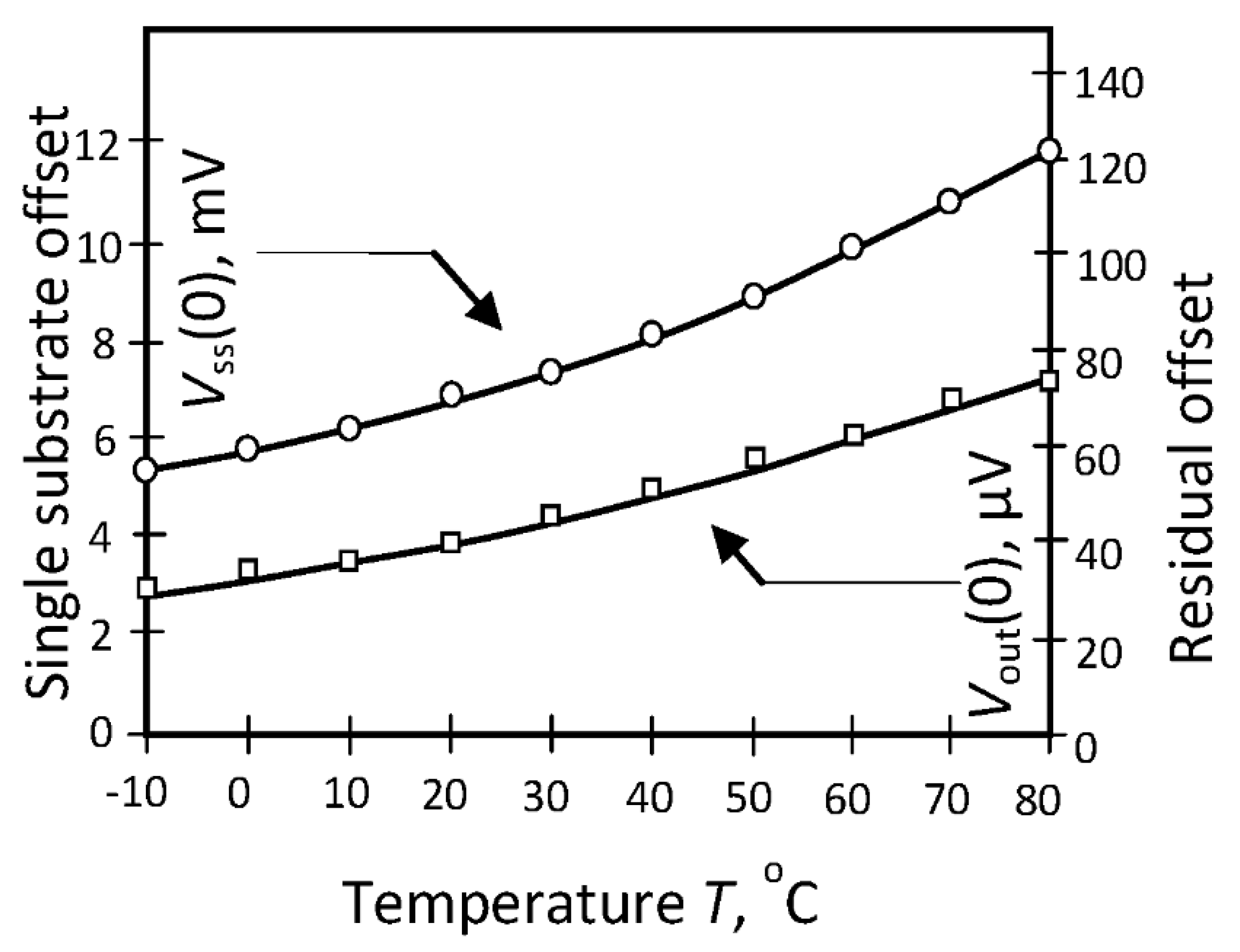

3. Results

4. Conclusions

Acknowledgments

References

- Roumenin, C. Solid State Magnetic Sensors; Elsevier: Amsterdam, The Netherlands, 1994. [Google Scholar]

- Kaufmann, T. On the Offset and Sensitivity of CMOS-Based Five-Contact Vertical Hall Devices; MEMS Technology and Engineering; Der Andere Verlag: Uelvesbull, Germany, 2013; Volume 21, p. 147. [Google Scholar]

- Lozanova, S.V.; Roumenin, C.S. Parallel-field silicon Hall effect microsensors with minimal design complexity. IEEE Sens. J. 2009, 9, 761–766. [Google Scholar] [CrossRef]

- Schurig, E.; Schott, C.; Besse, P.-A.; Popovic, R.S. CMOS integrated vertical Hall sensor with low offset. In Proceedings of the 16th European Conference on Solid-State Transducers, Prague, Czech Republic, 15–18 September 2002; pp. 868–871. [Google Scholar]

- Schurig, E.; Schott, C.; Besse, P.-A.; Demierre, M.; Popovic, R.S. 0.2 mT residual offset of CMOS integrated vertical Hall sensors. Sens. Actuators A 2004, 110, 98–104. [Google Scholar] [CrossRef]

- Schott, C.; Popovic, R. Integrated 3-D Hall magnetic field sensor. In Proceedings of the Transducers’99, Sendai, Japan, 7–10 June 1999; Volume 1, pp. 168–171. [Google Scholar]

- Lozanova, S.; Noykov, S.; Ivanov, A.; Roumenin, C. In-plane magnetosensitive double Hall device. In Proceedings of the 2017 XXVI International Scientific Conference Electronics (ET), Sozopol, Bulgaria, 13–15 September 2017; pp. 19–21. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lozanova, S.; Kolev, I.; Ivanov, A.; Roumenin, C. Low-Offset In-Plane Sensitive Hall Arrangement. Proceedings 2018, 2, 713. https://doi.org/10.3390/proceedings2130713

Lozanova S, Kolev I, Ivanov A, Roumenin C. Low-Offset In-Plane Sensitive Hall Arrangement. Proceedings. 2018; 2(13):713. https://doi.org/10.3390/proceedings2130713

Chicago/Turabian StyleLozanova, Siya, Ivan Kolev, Avgust Ivanov, and Chavdar Roumenin. 2018. "Low-Offset In-Plane Sensitive Hall Arrangement" Proceedings 2, no. 13: 713. https://doi.org/10.3390/proceedings2130713

APA StyleLozanova, S., Kolev, I., Ivanov, A., & Roumenin, C. (2018). Low-Offset In-Plane Sensitive Hall Arrangement. Proceedings, 2(13), 713. https://doi.org/10.3390/proceedings2130713