Microstrip Array Ring FETs with 2D p-Ga2O3 Channels Grown by MOCVD

Abstract

:1. Introduction

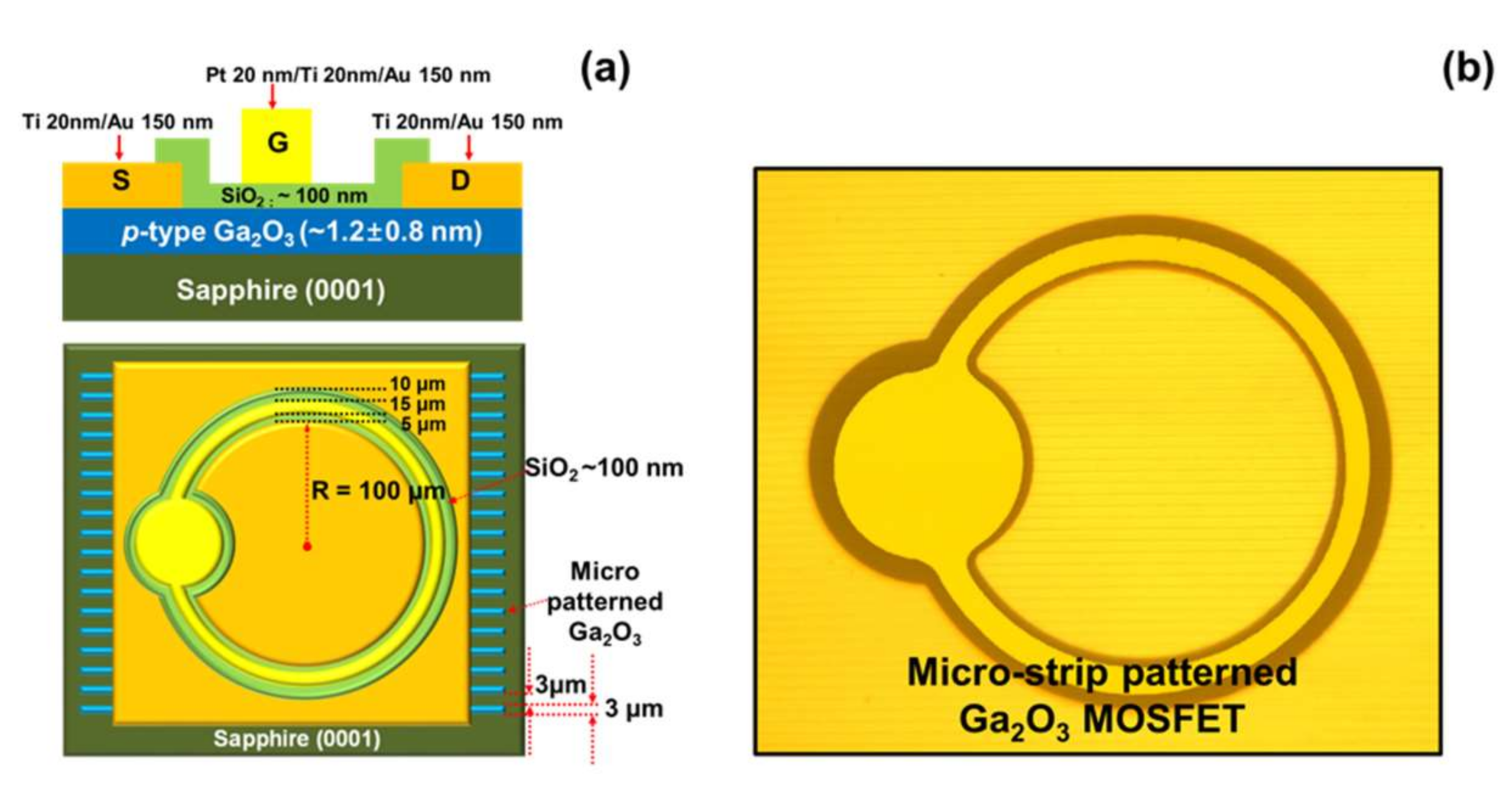

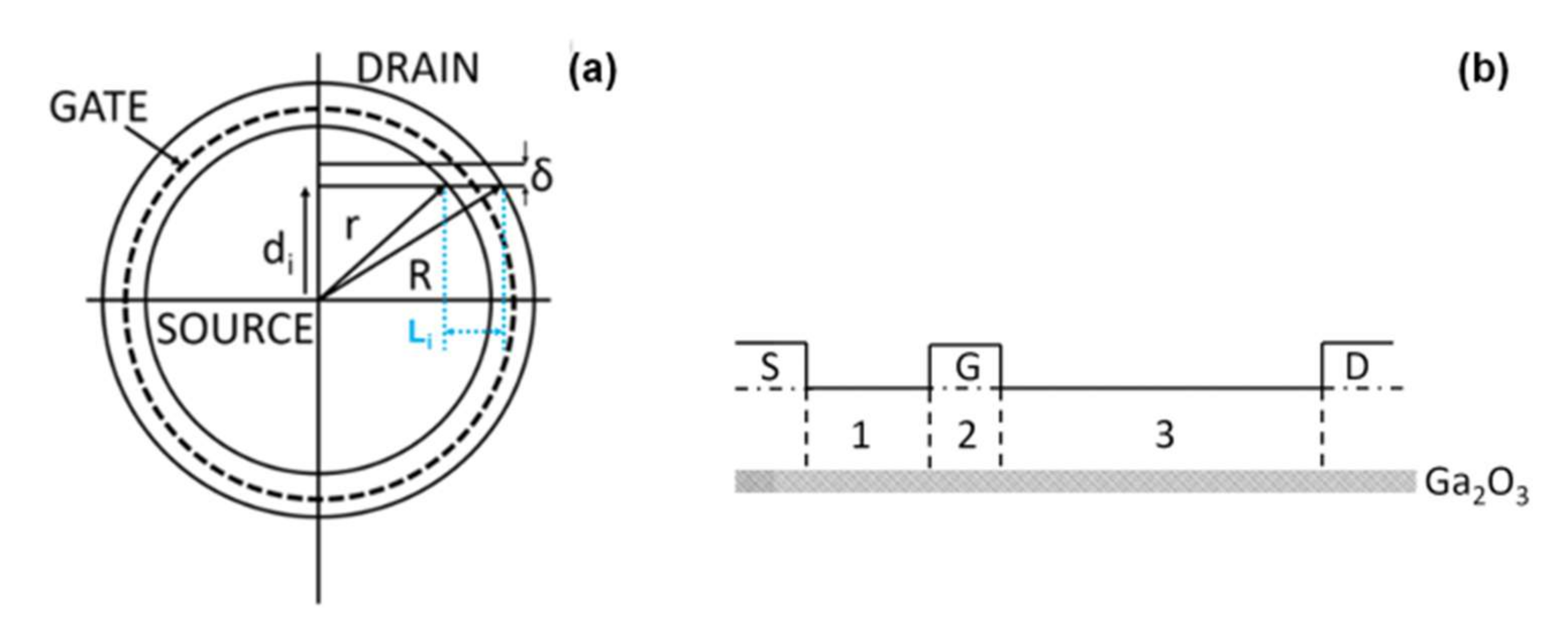

2. Materials and Methods

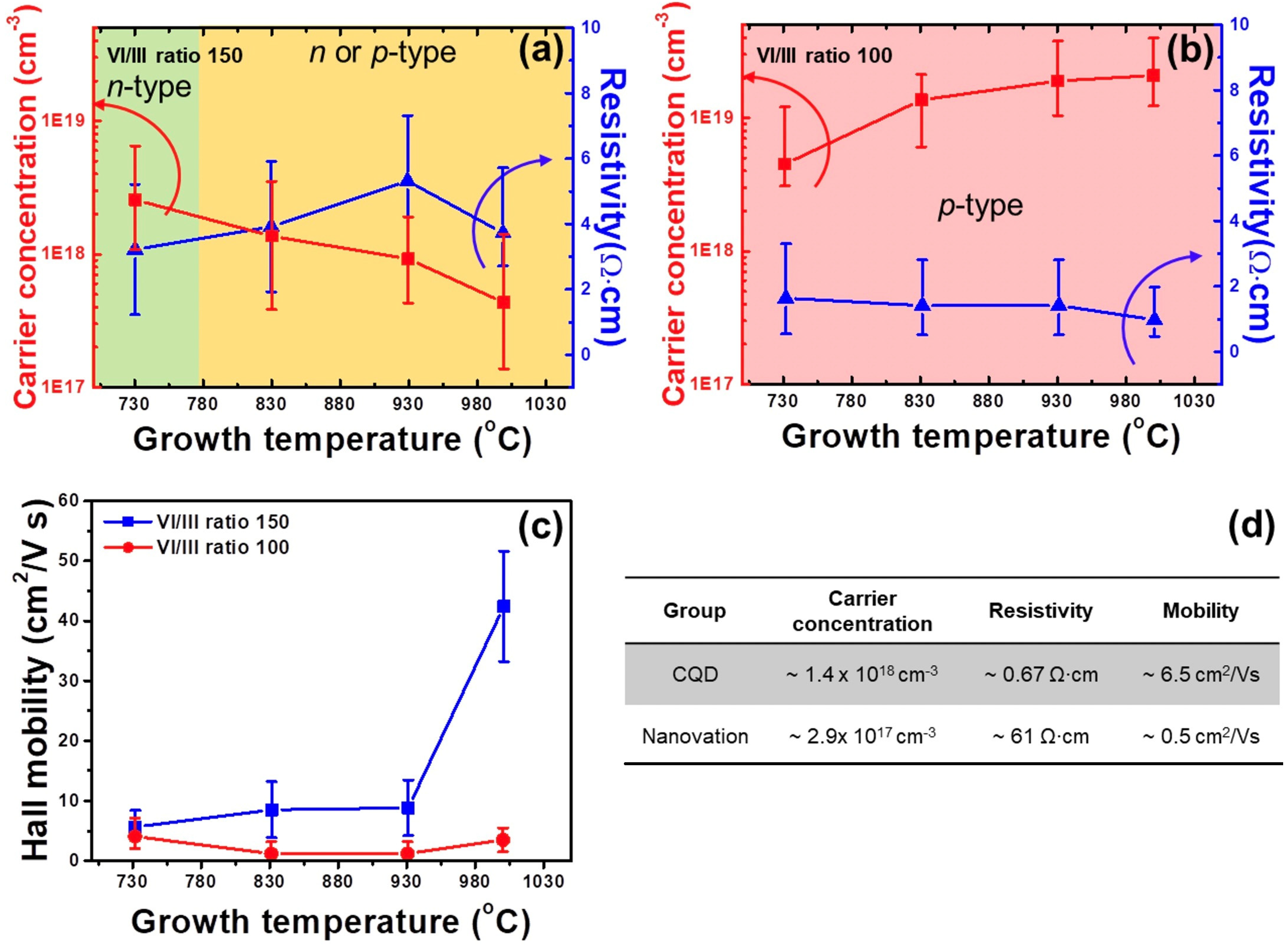

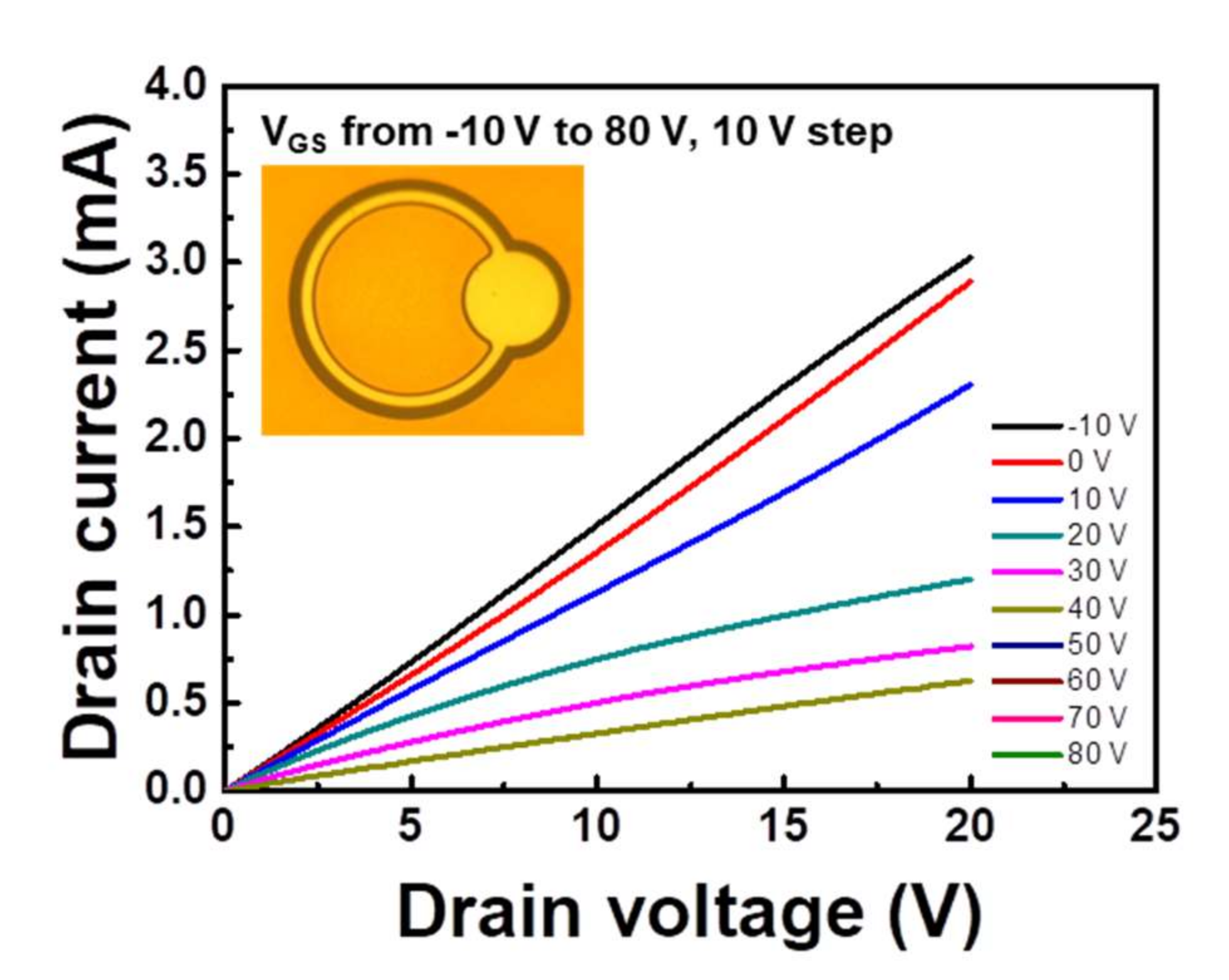

3. Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Higashiwaki, M.; Sasaki, K.; Kamimura, T.; Wong, M.H.; Krishnamurthy, D.; Kuramata, A.; Masui, T.; Yamakoshi, S. Depletion-mode Ga2O3 metal-oxide-semiconductor field-effect transistors on β-Ga2O3 (010) substrates and temperature dependence of their device characteristics. Appl. Phys. Lett. 2013, 103, 123511. [Google Scholar] [CrossRef] [Green Version]

- Sasaki, K.; Higashiwaki, M.; Kuramata, A.; Masui, T.; Yamakoshi, S.J. MBE grown Ga2O3 and its power device applications. Cryst. Growth 2013, 378, 591. [Google Scholar] [CrossRef]

- Sasaki, K.; Wakimoto, D.; Thieu, Q.T.; Koishikawa, Y.; Kuramata, A.; Higashiwaki, M.; Yamakoshi, S. First Demonstration of Ga2O3 Trench MOS-Type Schottky Barrier Diodes. IEEE Electron Device Lett. 2017, 38, 783. [Google Scholar] [CrossRef]

- Razeghi, M.; Park, J.-H.; McClintock, R.; Pavlidis, D.; Teherani, F.H.; Rogers, D.J.; Magill, B.A.; Khodaparast, G.A.; Xu, Y.; Wu, J.; et al. A review of the growth, doping, and applications of β-Ga2O3 thin films. In Proceedings of the SPIE, Oxide-Based Materials and Devices IX, San Francisco, CA, USA, 28 January–1 February 2018; Volume 10533, p. 105330R. [Google Scholar]

- Lee, J.; Kim, H.; Gautam, L.; He, K.; Hu, X.; Dravid, V.P.; Razeghi, M. Study of Phase Transition in MOCVD Grown Ga2O3 from κ to β Phase by Ex Situ and In Situ Annealing. Photonics 2021, 8, 17. [Google Scholar] [CrossRef]

- Lee, J.; Kim, H.; Gautam, L.; Razeghi, M. High Thermal Stability of κ-Ga2O3 Grown by MOCVD. Crystals 2021, 11, 446. [Google Scholar] [CrossRef]

- Lee, J.; Kim, H.; Gautam, L.; Razeghi, M. Highly Conductive Co-Doped Ga2O3:Si-In Grown by MOCVD. Coatings 2021, 11, 287. [Google Scholar] [CrossRef]

- Rogers, D.J.; Bove, P.; Arrateig, X.; Sandana, V.E.; Teherani, F.H.; Razeghi, M.; McClintock, R.; Frisch, E.; Harel, S. The new oxide paradigm for solid state ultraviolet photodetectors, Proceedings Volume 10533. In Proceedings of the SPIE 10533, Oxide-based Materials and Devices IX, 105331P, San Francisco, CA, USA, 30 April 2018. [Google Scholar]

- Park, J.-H.; McClintock, R.; Jaud, A.; Dehzangi, A.; Razeghi, M. MOCVD grown β-Ga2O3 metal-oxide-semiconductor field effect transistors on sapphire. Appl. Phys. Express 2019, 12, 095503. [Google Scholar] [CrossRef]

- Xu, Y.; Park, J.-H.; Yao, Z.; Wolverton, C.; Razeghi, M.; Wu, J.; Dravid, V.P. Strain-Induced Metastable Phase Stabilization in Ga2O3 Thin Films. ACS Appl. Mater. Interfaces 2019, 11, 5536–5543. [Google Scholar] [CrossRef] [PubMed]

- McClintock, R.; Jaud, A.; Gautam, L.; Razeghi, M. Solar-blind photodetectors based on Ga2O3 and III-nitrides. In Proceedings of the SPIE, Quantum Sensing and Nano Electronics and Photonics XVII, San Francisco, CA, USA, 24 March 2020; Volume 11288, p. 1128803. [Google Scholar]

- Park, J.-H.; McClintock, R.; Razeghi, M. Ga2O3 Metal-oxide-semiconductor Field Effect Transistors on Sapphire Substrate by MOCVD, Semicond. Sci. Technol. 2019, 34, 08LT01. [Google Scholar]

- Playford, H.Y.; Hannon, A.C.; Barney, E.R.; Walton, R.I. Structures of uncharacterised polymorphs of gallium oxide from total neutron diffraction. Chem. Eur. J. 2013, 19, 2803–2813. [Google Scholar] [CrossRef] [PubMed]

- Munoz-Yague, A.; Baceiredo, S.J. Ge Incorporation in GaAs Grown by Molecular Beam Epitaxy: A Thermodynamic Study. Electrochem. Soc. 1982, 129, 2108. [Google Scholar] [CrossRef]

- Teramoto, I.J. Calculation of distribution equilibrium of amphoteric silicon in gallium arsenide. Phys. Chem. Solids 1972, 33, 2089. [Google Scholar] [CrossRef]

- Meier, H.P.; Broom, R.F.; Epperlein, P.W.; van Giesen, E.; Harder, C.; Jäckel, H. Problems related to the formation of lateral p–n junctions on channeled substrate (100) GaAs for lasers. Vac. Sci. Technol. B 1988, 6, 692. [Google Scholar] [CrossRef]

- Agawa, K.; Hirakawa, K.; Sakamoto, N.; Hashimoto, Y.; Ikoma, T. Electrical properties of heavily Si-doped (311)A GaAs grown by molecular beam epitaxy. Appl. Phys. Lett. 1994, 65, 1171. [Google Scholar] [CrossRef]

- Quivy, A.A.; Sperandio, A.L.; Silva, E.C.F.; Leite, J.R. p-Type doping of GaAs (001) layers grown by MBE using silicon as a dopant. J. Cryst. Growth 1999, 206, 171. [Google Scholar] [CrossRef]

- Va, C.J.Z.I.; Kielara, S.M.; Jonesa, L.O.; Mosqueraa, M.A.; Schatz, G.C. Investigation of p-type doping in β-and κ-Ga2O3. J. Alloys Compd. 2021, 877, 160227. [Google Scholar]

- Lopez-Dominguez, V.; Shi, J.; Razeghi, M.; Amiri, P.K. “Magnetic Heterostructures using n- and p-doped Ga2O3 Films”, late news presentation. In Proceedings of the SPIE Quantum Sensing and Nano Electronics and Photonics XVI, San Francisco, CA, USA, 3–7 February 2019. [Google Scholar]

- Wang, C.; Park, J.-H.; Li, J.; McClintock, R.; Razeghi, M.; Grayson, M. “p-Type Ga2O3: P-type Hall, p-type Seebeck; mobility, anisotropy, and acceptor binding energy”, late news presentation. In Proceedings of the SPIE Quantum Sensing and Nano Electronics and Photonics XVI, San Francisco, CA, USA, 3–7 February 2019. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Razeghi, M.; Lee, J.; Gautam, L.; Leburton, J.-P.; Teherani, F.H.; Amiri, P.K.; Dravid, V.P.; Pavlidis, D. Microstrip Array Ring FETs with 2D p-Ga2O3 Channels Grown by MOCVD. Photonics 2021, 8, 578. https://doi.org/10.3390/photonics8120578

Razeghi M, Lee J, Gautam L, Leburton J-P, Teherani FH, Amiri PK, Dravid VP, Pavlidis D. Microstrip Array Ring FETs with 2D p-Ga2O3 Channels Grown by MOCVD. Photonics. 2021; 8(12):578. https://doi.org/10.3390/photonics8120578

Chicago/Turabian StyleRazeghi, Manijeh, Junhee Lee, Lakshay Gautam, Jean-Pierre Leburton, Ferechteh H. Teherani, Pedram Khalili Amiri, Vinayak P. Dravid, and Dimitris Pavlidis. 2021. "Microstrip Array Ring FETs with 2D p-Ga2O3 Channels Grown by MOCVD" Photonics 8, no. 12: 578. https://doi.org/10.3390/photonics8120578

APA StyleRazeghi, M., Lee, J., Gautam, L., Leburton, J.-P., Teherani, F. H., Amiri, P. K., Dravid, V. P., & Pavlidis, D. (2021). Microstrip Array Ring FETs with 2D p-Ga2O3 Channels Grown by MOCVD. Photonics, 8(12), 578. https://doi.org/10.3390/photonics8120578