1. Introduction

All-optical devices based on Surface Plasmon Polaritons (SPP) are the topic of comprehensive research in recent years. All-optical SPP devices motivate extensively new research to overcome the major performance constraints of semiconductor electronic devices which suffer from inherent delay and high heat generation, as well as to overcome the problem of photonics devices, that is, the diffraction limit. Therefore, the utilization of the aforementioned devices enables the manipulation of light on a subwavelength scale [

1]. However, the main idea is to control the constructive/destructive interference of two or more light signals in two or more plasmonic waveguides [

2,

3]. The constructive/destructive interferences are considered as a switch operation and the devices that perform this operation called all-optical switching devices [

4]. Plasmonic logic gates such as OR, AND, NOR, NAND, XOR, XNOR and NOT logical operations can make the basic units of future subwavelength processors [

2]. Recently, many all-optical plasmonic structures have provided nanoscale logic gates [

5,

6,

7,

8,

9].

On the other hand, many all-optical structures provided combinational logic functions [

10,

11,

12,

13,

14,

15,

16,

17,

18,

19]. Some of these works [

10,

11,

12,

13,

14,

15] investigate a surface plasmon polariton (SPP) to achieve a desired function(s) from the combinational logic functions, each combinational logic circuit has their own way to realize the function of the combinational logic circuit, such as a different number of combinational logic functions, different types of combinational logic functions, etc. For examples, a nanoscale plasmonic half-adder architecture as a simple plasmonic processor has been introduced and verified based on interference of SPP modes in Reference [

10], an optical half-adder has been realized with a footprint of only 10 μm × 28 μm in Reference [

11], a plasmonic adder-subtractor module based on a Metal-Insulator-Metal (MIM) ring resonator is proposed in Reference [

12], a compact design of a one-bit magnitude comparator using a nonlinear plasmonic Mach–Zehnder Interferometer (MZI) has been designed in Reference [

13], and a low-power ultra-compact chip-integrated all-optical logic half-adder and full-adder in X-shaped plasmonic microstructures covered with a nonlinear nanocomposite layer, and etched in plasmonic integrated circuits directly experimentally realized in Reference [

14]. According to our knowledge, so far, there is no theoretical or experimental demonstration of a combinational logic functions structure that satisfies the requirements of ultra-small feature size, and four plasmonic combinational logic functions in one structure.

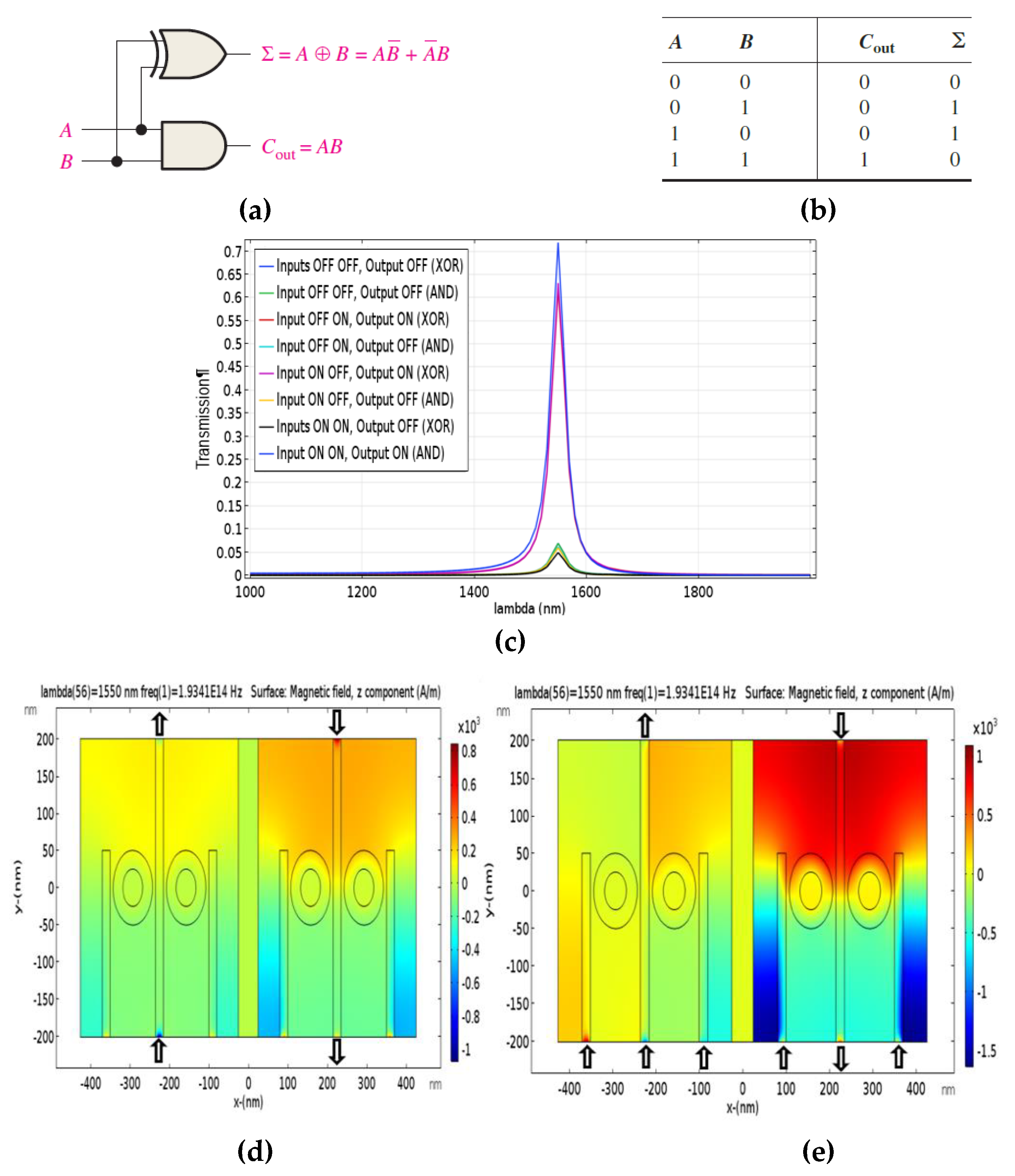

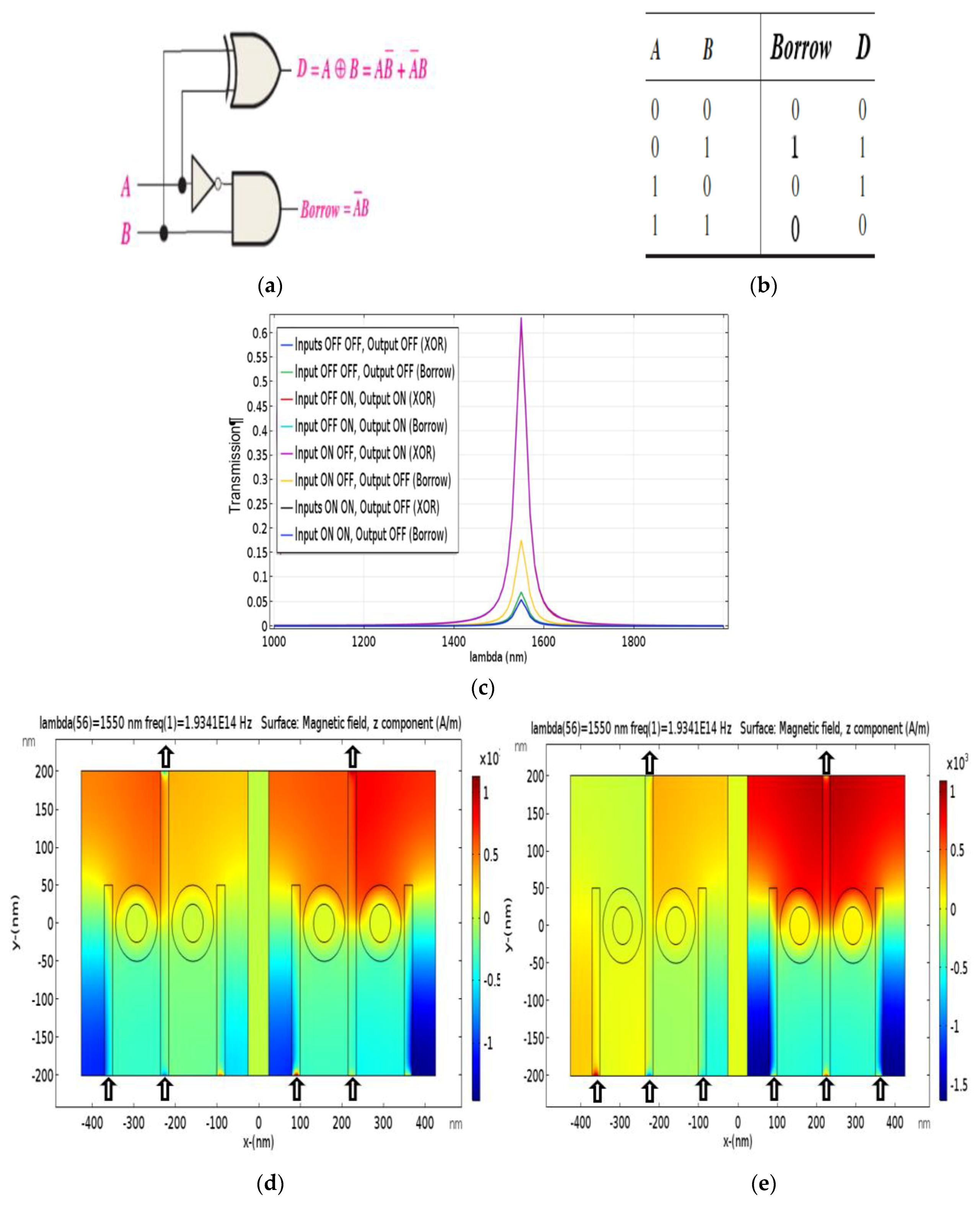

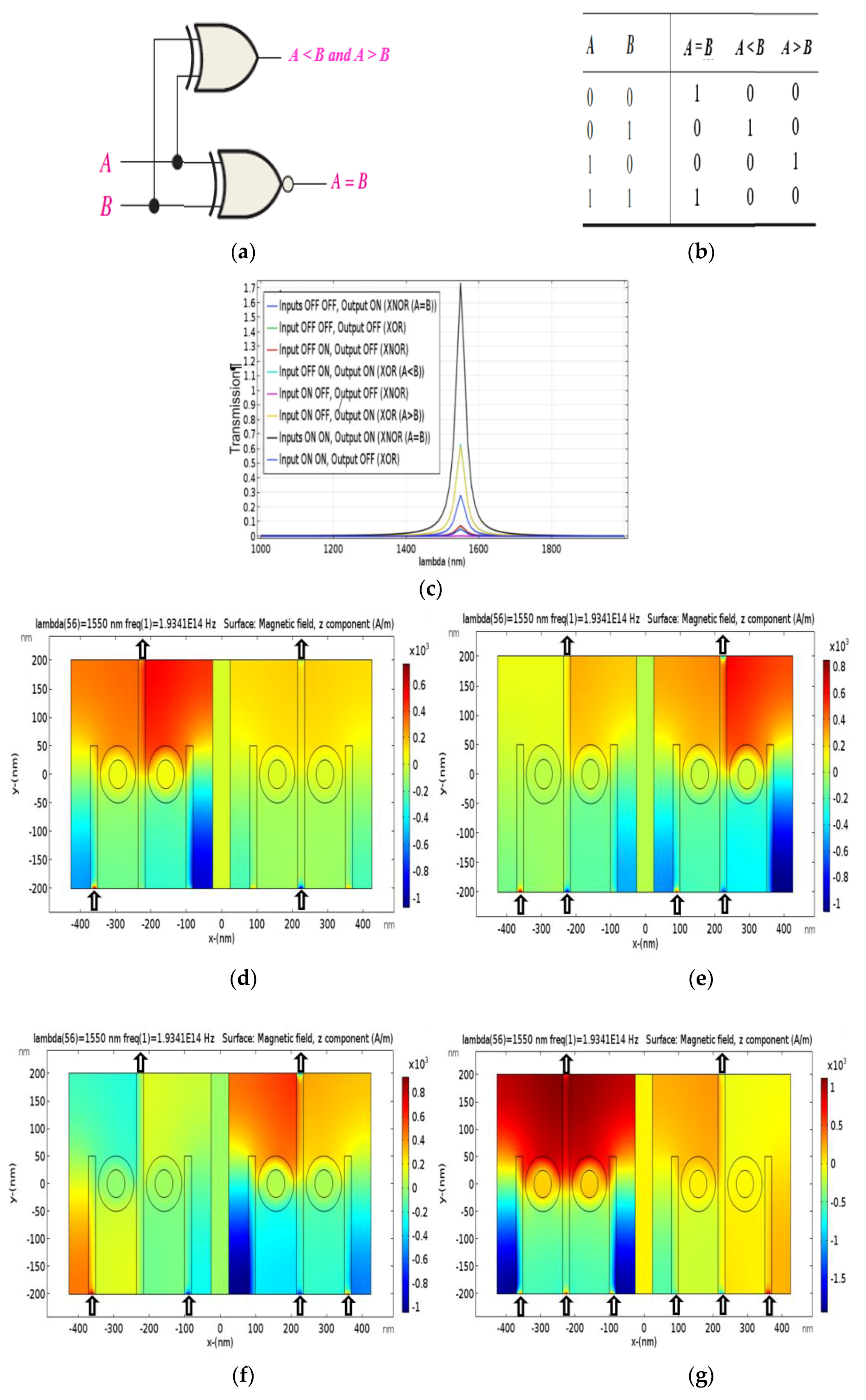

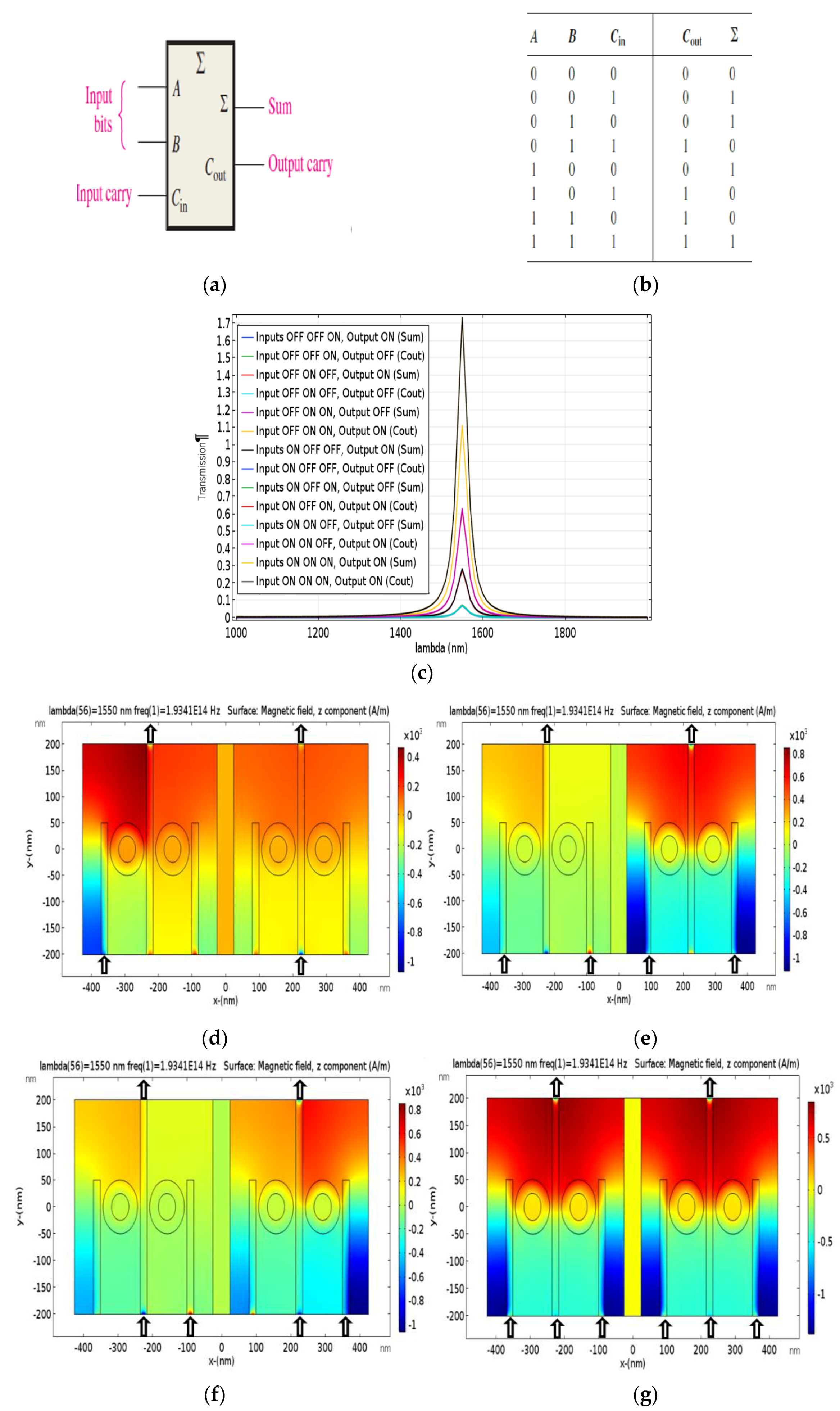

In this article, we offer the sub-micron size structure, enhancing the transmission (exceeding 100%), and the largest number (four plasmonic combinational logic functions) of plasmonic combinational logic function in the same structure with the same of resonance frequency and the same transmission threshold in structure with Nano-rings resonator and plasmonic Nano-waveguides. The plasmonic combinational logic functions that are proposed, designed and simulated are half-adder, full-adder, half-subtractor, and comparator one-bit. The simulation results are obtained by FEM. In the future, these devices will be the gateway to the Nano-photonic integrated circuits applications.

The organization of this article is as follows:

Section 2 contains the proposed structure layout and theoretical operation concept. In

Section 3, the simulation results and performance of the proposed all-optical plasmonic combinational logic function are presented, demonstrated and discussed. In

Section 4, a comparison between the proposed plasmonic combinational logic functions and previous researches is introduced. Finally, we conclude the suggested work in

Section 5.

2. Structure Layout and Theoretical Concept

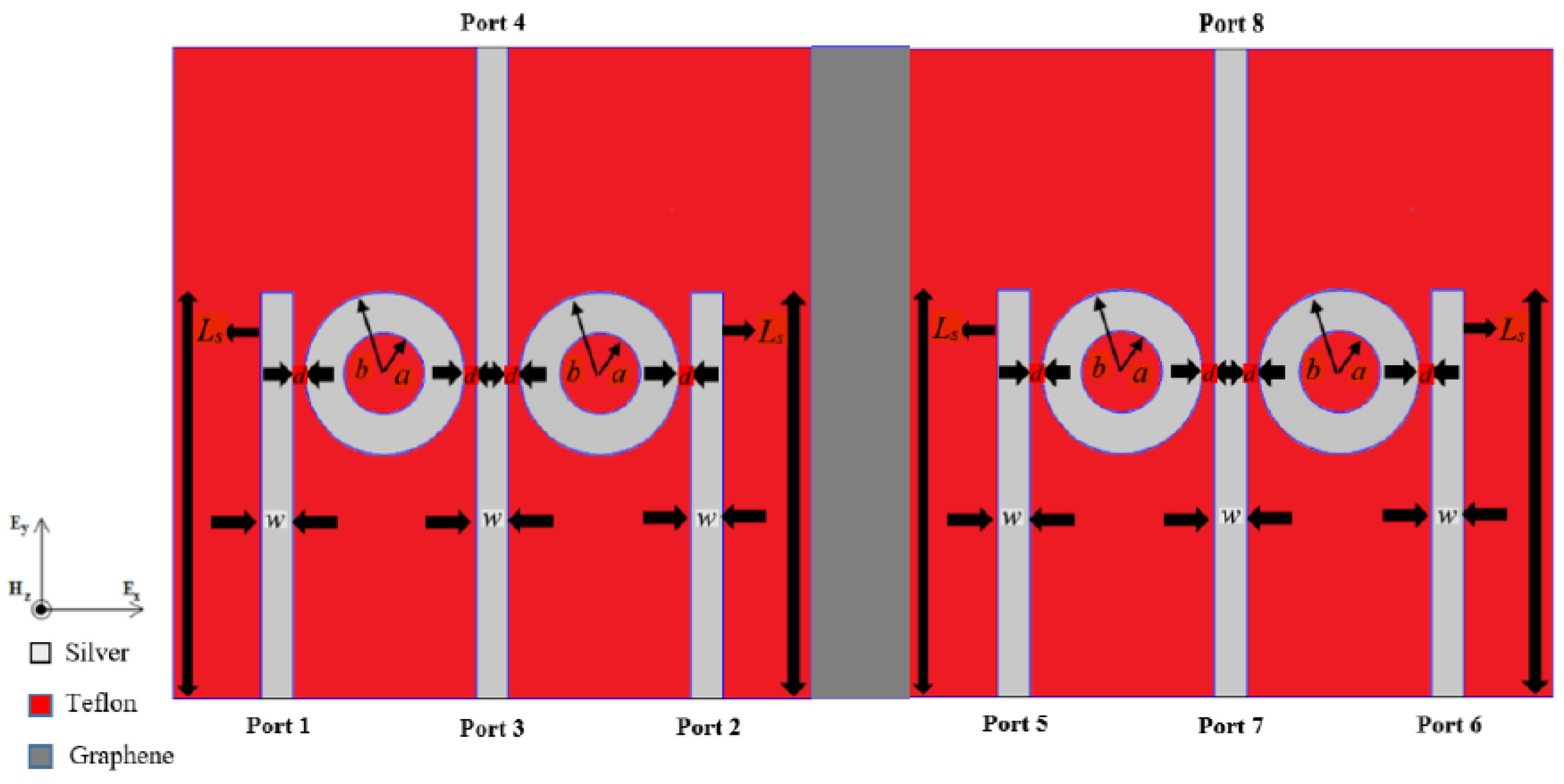

The proposed structure to simulate all-optical plasmonic combinational logic functions (four combinational logic functions) is shown in

Figure 1.

The structure that construct four combinational logic functions consists of two sub-structures of dimensions 400 nm × 400 nm separated by 50 nm width of perfect mirror to do the isolation process between the two sub-structures. The perfect mirror can be realized by using graphene material [

20,

21]. Each sub-structure has three straight stripes and two Nano-rings resonators to give one of the outputs of the proposed plasmonic combinational logic functions based on the IMI plasmonic waveguides. The length of the middle and side stripes (

Ls) in each sub-structure are 400 nm and 250 nm, respectively. The width (

w) of these stripes is 20 nm, the radii of the Nano-ring resonator (

a) and (

b) in each sub-structure are 25 nm and 50 nm, respectively, and the coupling distance (

d) between the Nano-rings resonator and stripes in each sub-structure is 7.5 nm.

The materials of the proposed structure are silver and Teflon. In our structure, stripes and two Nano-rings in each sub-structure are represented as silver material, while the remaining part of the structure is a Teflon material as shown in

Figure 1.

All four proposed plasmonic combinational logic functions have the same dimensions, parameters, and materials in their structures.

In our simulations, Johnson and Christy data is used to describe the silver permittivity [

22], while the refractive index of Teflon material is 1.375 [

23]. The resonance wavelength of the Nano-rings can be determined by [

24,

25]:

where n

eff is the effective refractive index and D is the bigger diameter of the Nano-ring. According to Equation (1), the structure parameters and the type of materials play a role in choosing the resonance wavelength. We focus on the resonance wavelength of 1550 nm since this wavelength is the best choice in optical communications applications.

The performance of the proposed plasmonic combinational logic functions is measured by the transmission as a function of wavelengths sweep. The transmission is a ratio between the output optical power to the single input optical power (Input Port or control Port). The transmission is described Equation (2) [

26]:

where

T is the transmission, P

out is the output optical power of the output Port in ON state and OFF state, and P

in is the input optical power for single Input Port or single control Port.

5. Conclusions

In this paper, four plasmonic combinational logic functions have been proposed, designed and simulated using 2-D FEM. These combinational logic functions are half-adder, half-subtractor, comparator one-bit, and full-adder. The combinational logic functions are constructed by Nano-rings IMI plasmonic structure. By employing the coupling property between straight stripes and ring resonator waveguides, we can achieve a plasmonic combinational logic function. By changing the state of the Input Port(s), the position of the Input Port(s) and a Control Port(s), and the Phase of incident light in these ports, we can make the transmission in the Output Port minimized or maximized according to the required plasmonic combinational logic function. To give a decision that the proposed plasmonic combinational logic function is investigating the truth table of one of the combinational logic functions, we have established a threshold value of transmission to distinguish between Logic 1 and Logic 0 states. The proposed value of transmission threshold is 0.25 or 25%; choosing this value achieves four plasmonic combinational logic functions in one structure. Finally, the proposed plasmonic combinational logic functions are considered fundamental building blocks in photonic integrated circuits and all-optical signal processing systems, and pave a way to achieve ultra-high-speed optical chip circuits.