All-Monolithically Integrated Self-Scanning Addressable VCSEL Array for 3D Sensing

Abstract

1. Introduction

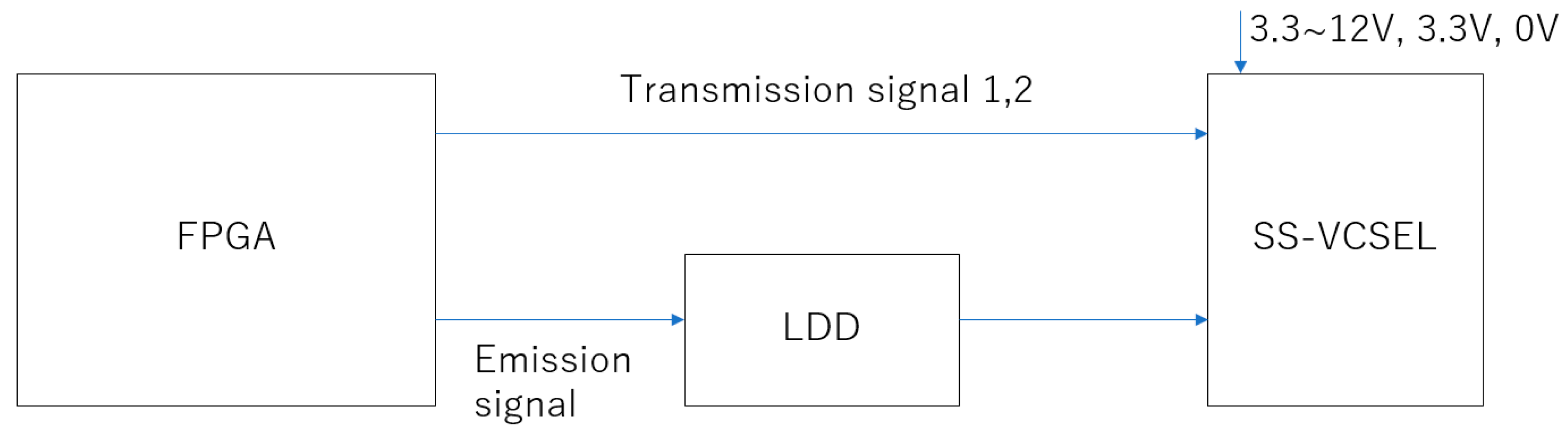

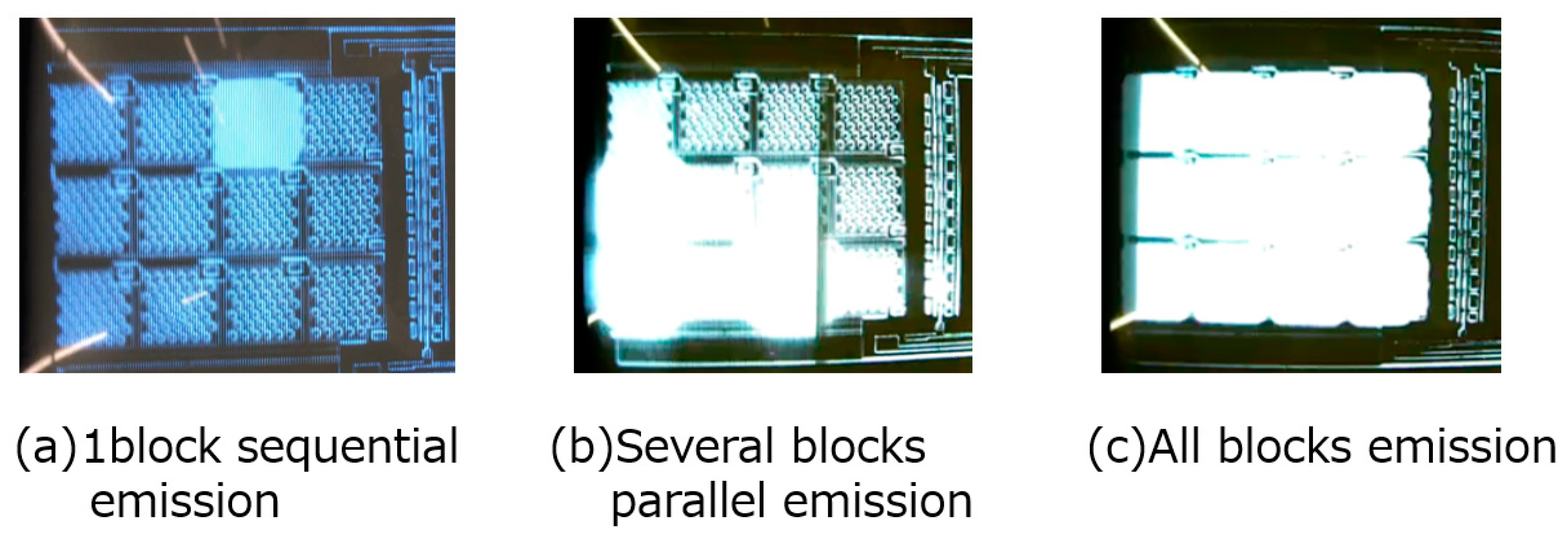

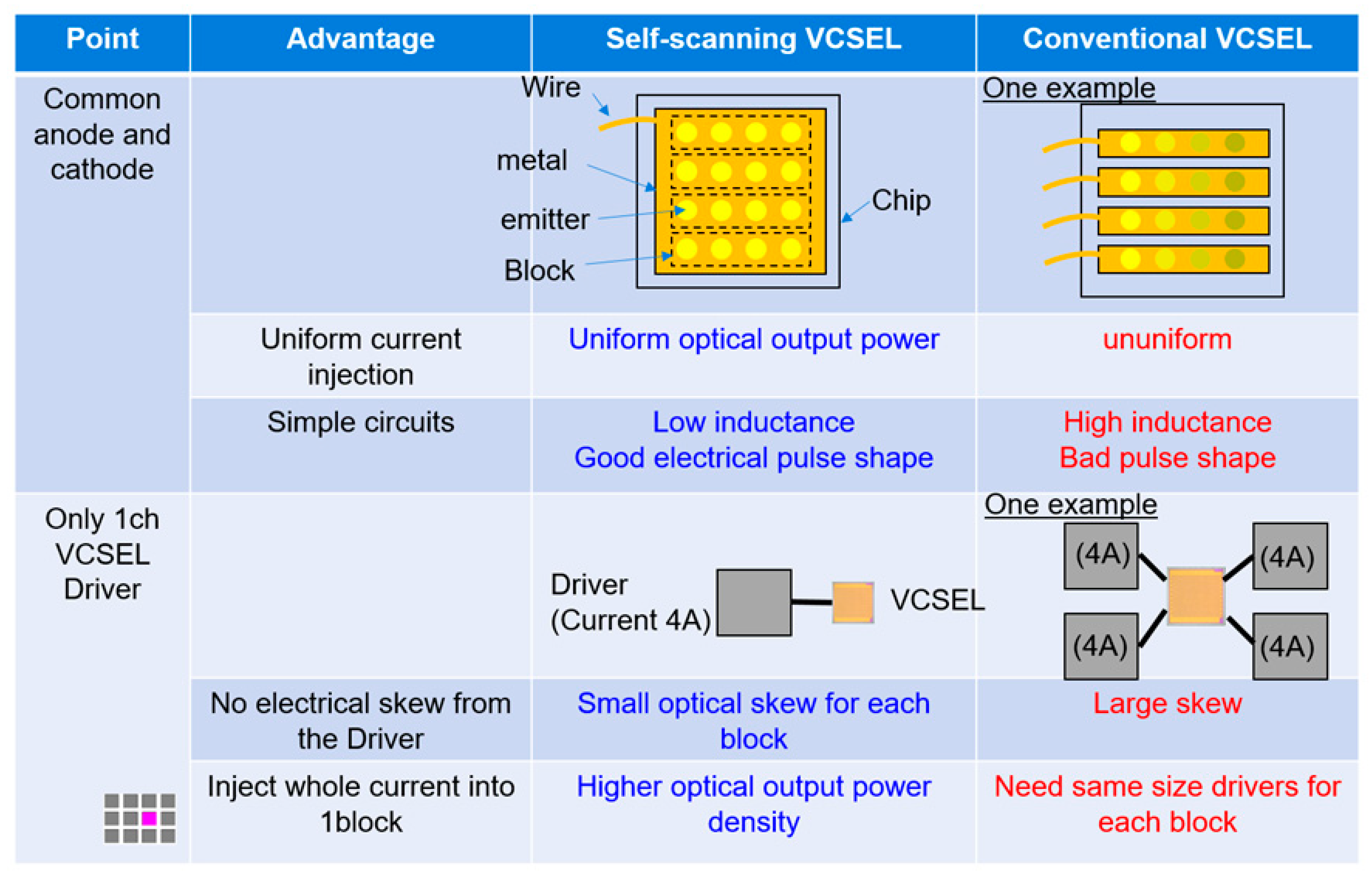

2. Materials and Methods

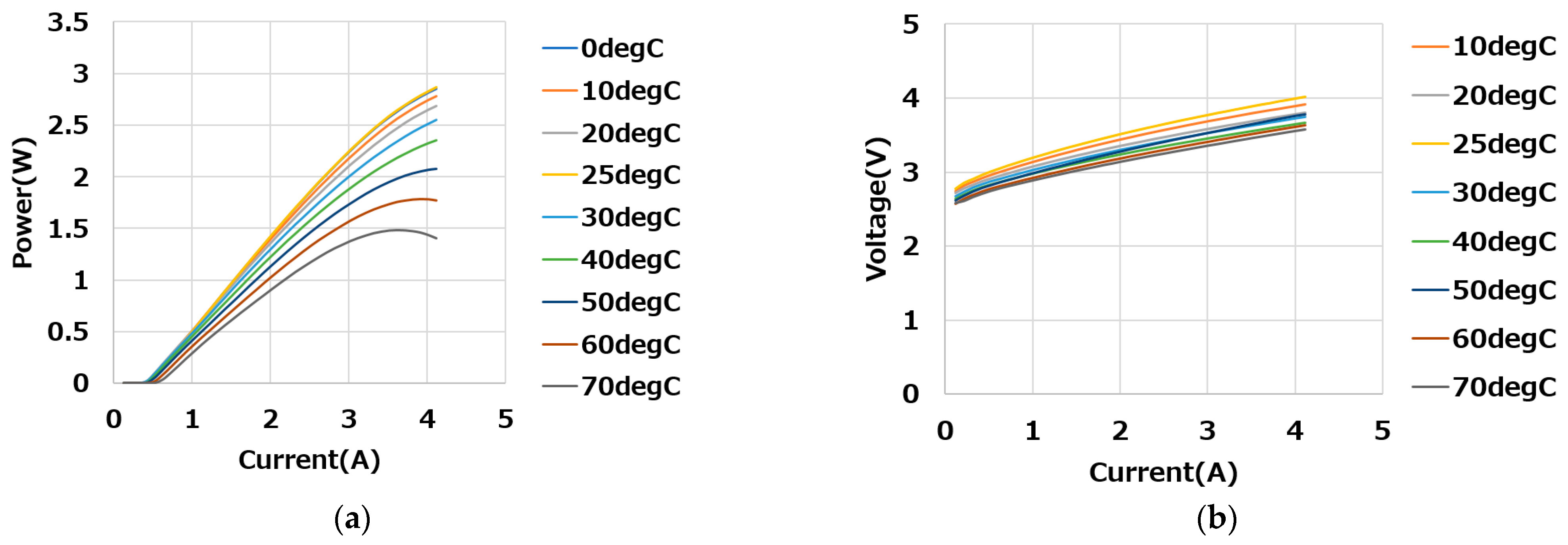

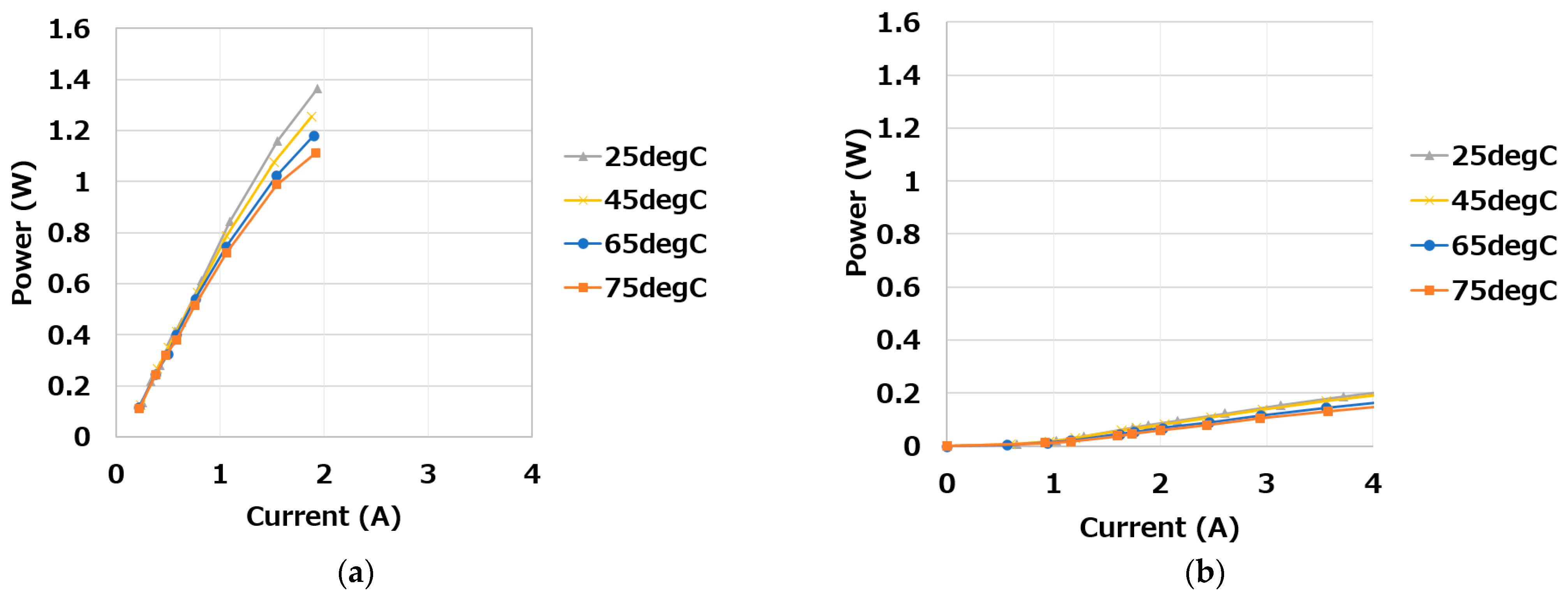

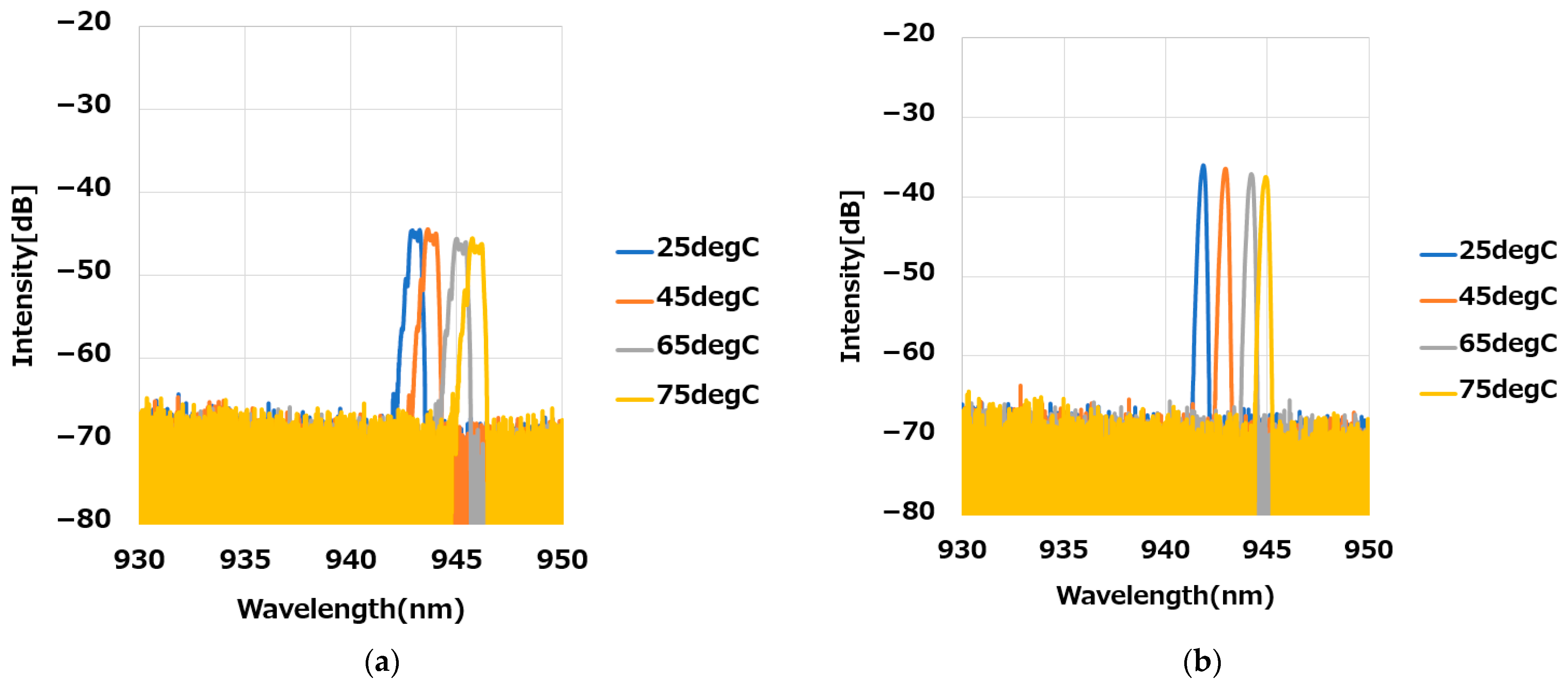

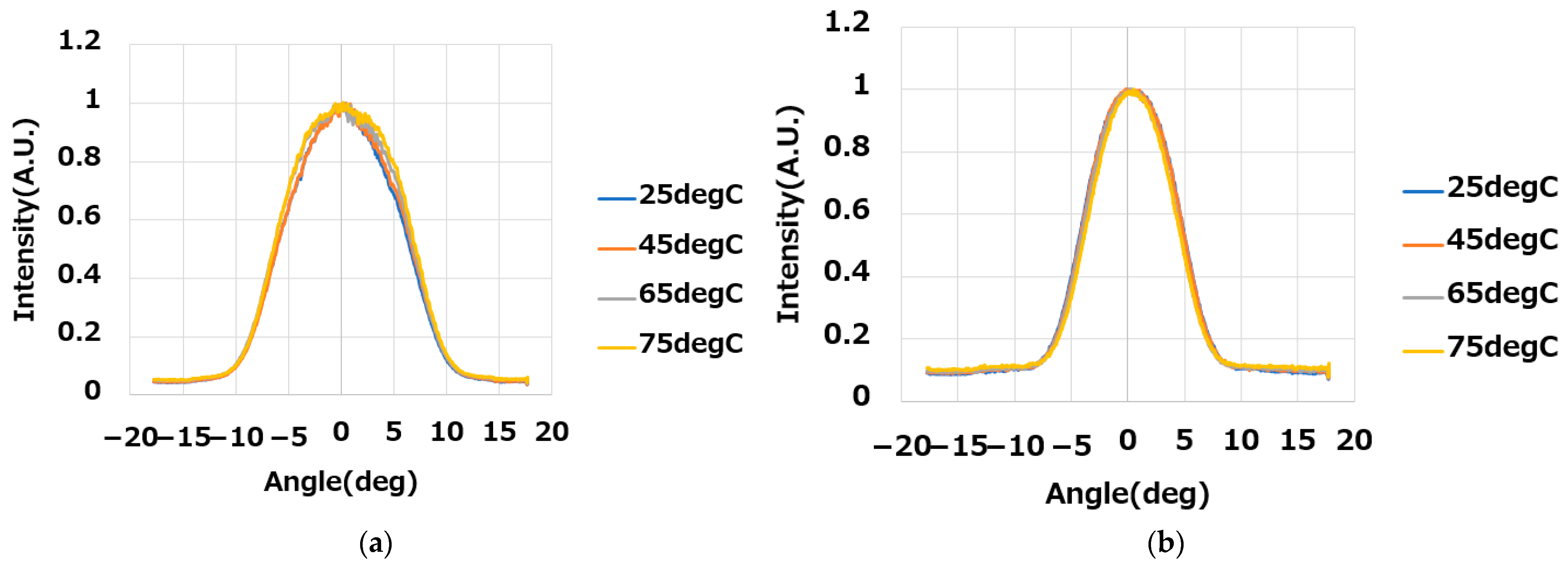

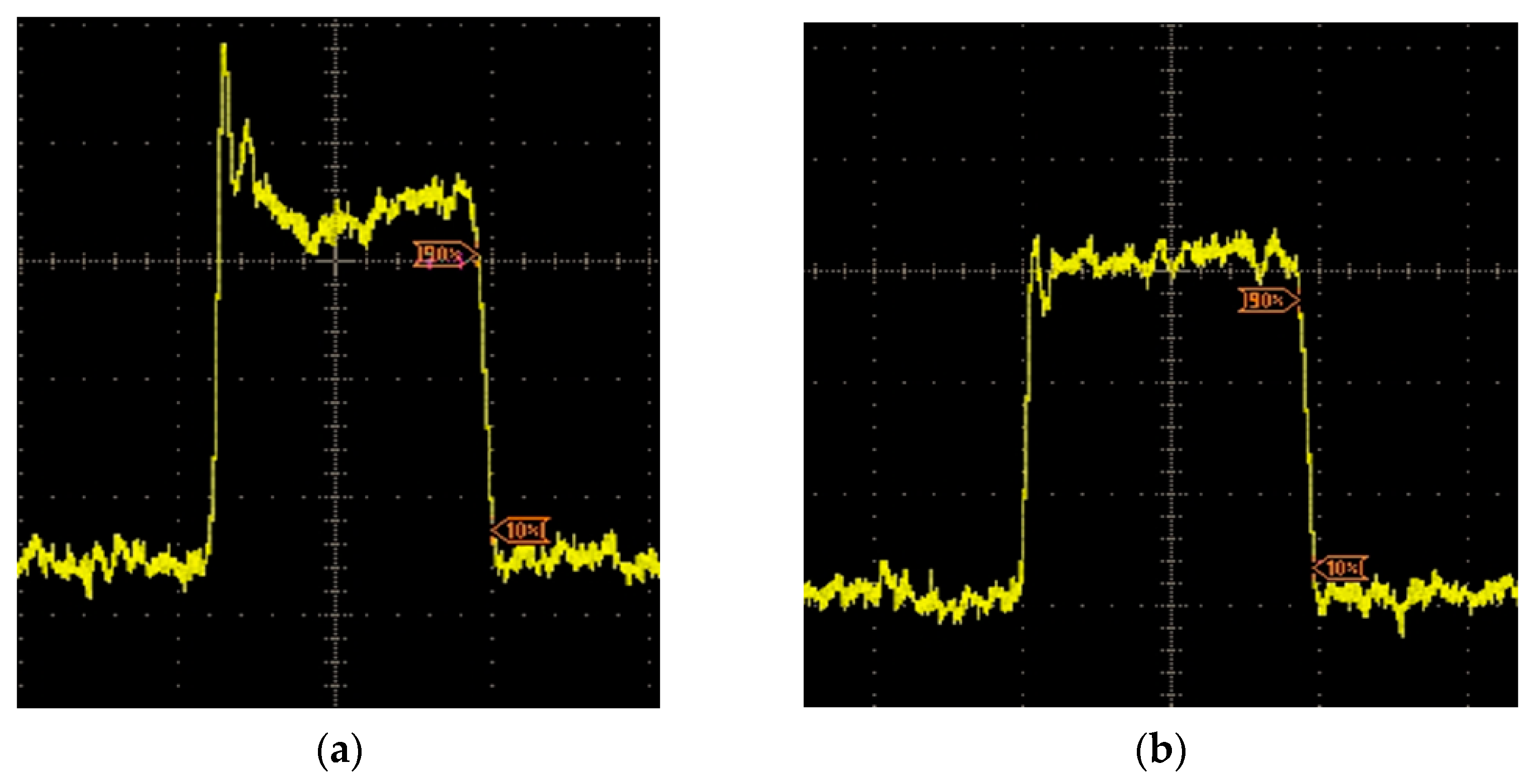

3. Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Dalir, H.; Koyama, F. Bandwidth enhancement of single-mode VCSEL with lateral optical feedback of slow light. IEICE Electron. Exp. 2011, 8, 1075–1081. [Google Scholar] [CrossRef]

- Kondo, T.; Takeda, K.; Otoma, H.; Murakami, A.; Sakurai, J.; Nakayama, H.; Gu, X.; Koyama, F. Developments of VCSELs for printers and optical communications at Fuji Xerox. In Vertical-Cavity Surface-Emitting Lasers XX; SPIE: Bellingham, WA, USA, 2016; Volume 9766, pp. 51–59. [Google Scholar]

- Seurin, J.F.; Ghosh, C.L.; Khalfin, V.; Miglo, A.; Xu, G.; Wynn, J.D.; Pradhan, P.; D’Asaro, L.A. High-power high efficiency 2D VCSEL arrays. In Vertical-Cavity Surface-Emitting Lasers XII; SPIE: Bellingham, WA, USA, 2008; Volume 6908, pp. 45–58. [Google Scholar]

- Seurin, J.F.; Zhou, D.; Xu, G.; Miglo, A.; Li, D.; Chen, T.; Guo, B.; Ghosh, C. High-efficiency VCSEL arrays for illumination and sensing in consumer applications. In Vertical-Cavity Surface-Emitting Lasers XX; SPIE: Bellingham, WA, USA, 2016; Volume 9766, pp. 60–68. [Google Scholar]

- Grabherr, M. New applications boost VCSEL quantities: Recent developments at Philips. In Vertical-Cavity Surface-Emitting Lasers XIX; SPIE: Bellingham, WA, USA, 2015; Volume 9381, p. 938102. [Google Scholar]

- Moench, H.; Carpaij, M.; Gerlach, P.; Groneborn, S.; Gudde, R.; Hellmig, J.; Kolb, J.; van der Lee, A. VCSEL-based sensors for distance and velocity. In Vertical-Cavity Surface-Emitting Lasers XX; SPIE: Bellingham, WA, USA, 2016; Volume 9766, pp. 40–50. [Google Scholar]

- Warren, M.E.; Podva, D.; Dacha, P.; Block, M.K.; Helms, C.J.; Maynard, J. Low-divergence high-power VCSEL arrays for lidar application. In Vertical-Cavity Surface-Emitting Lasers XXII; SPIE: Bellingham, WA, USA, 2018; Volume 10552, pp. 72–81. [Google Scholar]

- Bamji, C.S.; Mehta, S.; Thompson, B.; Elkhatib, T.; Wurster, S.; Akkaya, O.; Payne, A.; Godbaz, J.; Fenton, M.; Rajasekaran, V.; et al. 1Mpixel 65 nm BSI 320 MHz demodulated TOF image sensor with 3.5 μm global shutter pixels and analog binning. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 94–96. [Google Scholar]

- Kato, Y.; Sano, T.; Moriyama, Y.; Maeda, S.; Yamazaki, T.; Nose, A.; Shiina, K.; Yasu, Y.; Van der Tempel, W.; Ercana, A.; et al. 320 × 240 back-illuminated 10-μm CAPD pixels for high-speed modulation time-of-flight CMOS image sensor. IEEE J. Solid-State. Circuits 2018, 53, 1071–1078. [Google Scholar] [CrossRef]

- Shirakawa, Y.; Yasutomi, K.; Kagawa, K.; Aoyama, S.; Kawahito, S. An 8-Tap CMOS lock-in pixel image sensor for short-pulse time-of-flight measurements. Sensors 2020, 20, 1040. [Google Scholar] [CrossRef] [PubMed]

- Tontini, A.; Gasparini, L.; Perenzoni, M. Numerical model of SPAD-based direct time-of-flight flash lidar CMOS image sensors. Sensors 2020, 20, 5203. [Google Scholar] [CrossRef] [PubMed]

- Foix, S.; Alenya, G.; Torras, C. Lock-in time-of-flight (ToF) cameras: A survey. IEEE Sens. J. 2011, 11, 1917–1926. [Google Scholar] [CrossRef]

- Naik, N.; Kadambi, A.; Rhemann, C.; Izadi, S.; Raskar, R.; Kang, S.B. A light transport model for mitigating multipath interference in time-of-flight sensors. In Proceedings of the 2015 IEEE Conference on Computer Vision and Pattern Recognition (CVPR), Boston, MA, USA, 7–12 June 2015; pp. 73–81. [Google Scholar]

- Mure-Dubois, J.; Hügli, H. Real-time scattering compensation for time-of-flight camera. In Proceedings of the Proceedings of the ICVS Workshop on Camera Calibration Methods for Computer Vision Systems, Bielefeld, Germany, 21–24 March 2007. [Google Scholar]

- Lange, R.; Seitz, P. Solid-state time-of-flight range camera. IEEE J. Quantum Electron. 2001, 37, 390–397. [Google Scholar] [CrossRef]

- Kondo, T. All monolithically integrated self-scanning vertical-cavity surface-emitting array. In Proceedings of the 2018 IEEE International Semiconductor Laser Conference (ISLC), Santa Fe, NM, USA, 16–19 September 2018; pp. 1–2. [Google Scholar]

- Kondo, T.; Kitsunai, M.; Komagata, S.; Ohno, S.; Usami, H. Temperature characteristics of all-monolithically integrated self-scanning VCSEL array. In Vertical-Cavity Surface-Emitting Lasers XXIII; SPIE: Bellingham, WA, USA, 2019; Volume 10938, pp. 34–43. [Google Scholar]

- Kuijk, M.; Heremans, P.L.; Borghs, G.; Vounckx, R. Depleted double-heterojunction optical thyristor. Appl. Phys. Lett. 1994, 64, 2073–2075. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kondo, T.; Hayakawa, J.; Iguchi, D.; Sakita, T.; Higuchi, T.; Takeyama, K.; Ohno, S.; Murata, M.; Usami, H. All-Monolithically Integrated Self-Scanning Addressable VCSEL Array for 3D Sensing. Photonics 2023, 10, 304. https://doi.org/10.3390/photonics10030304

Kondo T, Hayakawa J, Iguchi D, Sakita T, Higuchi T, Takeyama K, Ohno S, Murata M, Usami H. All-Monolithically Integrated Self-Scanning Addressable VCSEL Array for 3D Sensing. Photonics. 2023; 10(3):304. https://doi.org/10.3390/photonics10030304

Chicago/Turabian StyleKondo, Takashi, Junichiro Hayakawa, Daisuke Iguchi, Tomoaki Sakita, Takafumi Higuchi, Kei Takeyama, Seiji Ohno, Michiaki Murata, and Hiroyuki Usami. 2023. "All-Monolithically Integrated Self-Scanning Addressable VCSEL Array for 3D Sensing" Photonics 10, no. 3: 304. https://doi.org/10.3390/photonics10030304

APA StyleKondo, T., Hayakawa, J., Iguchi, D., Sakita, T., Higuchi, T., Takeyama, K., Ohno, S., Murata, M., & Usami, H. (2023). All-Monolithically Integrated Self-Scanning Addressable VCSEL Array for 3D Sensing. Photonics, 10(3), 304. https://doi.org/10.3390/photonics10030304