An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC Converter with Output LC Filter

Abstract

1. Introduction

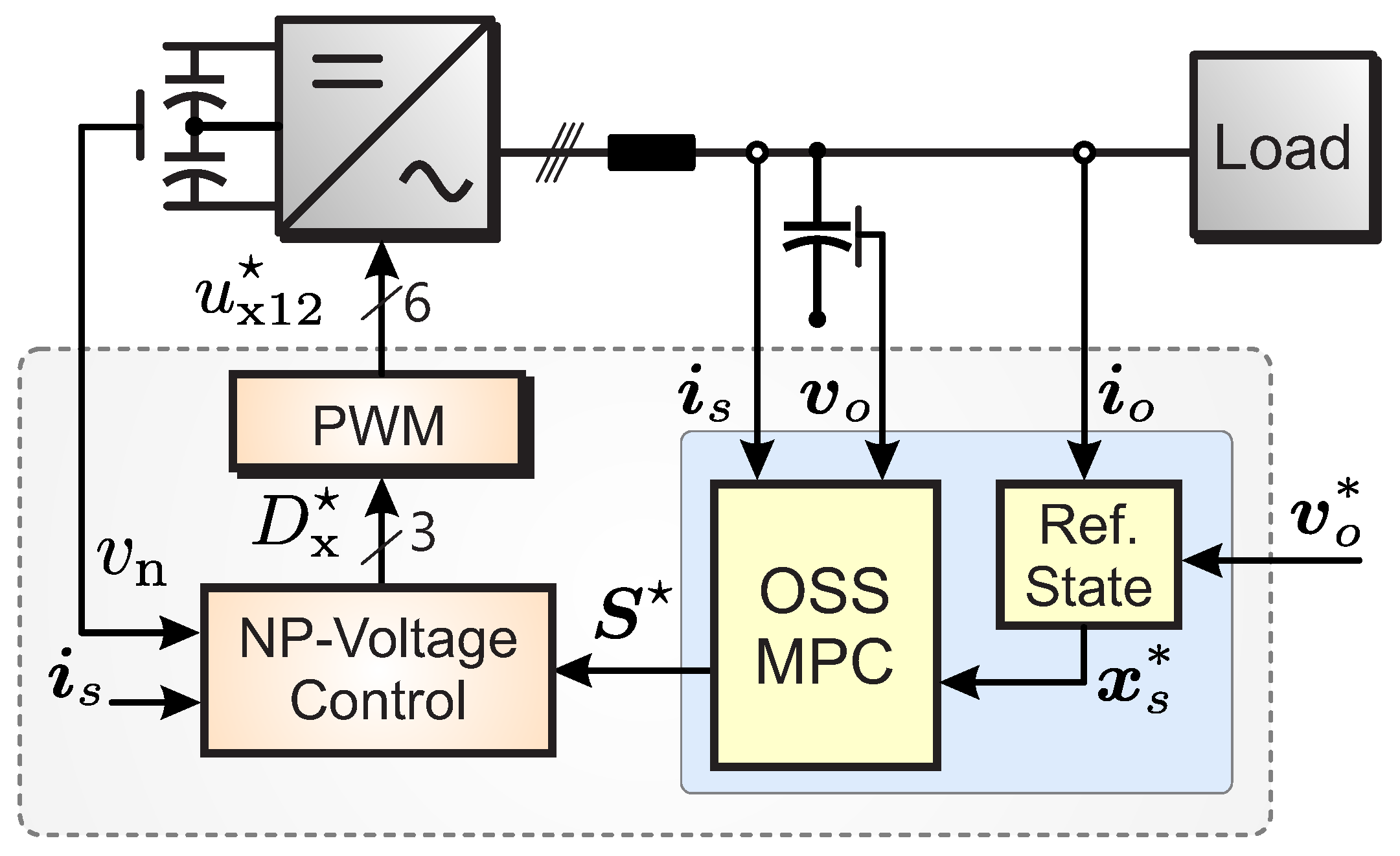

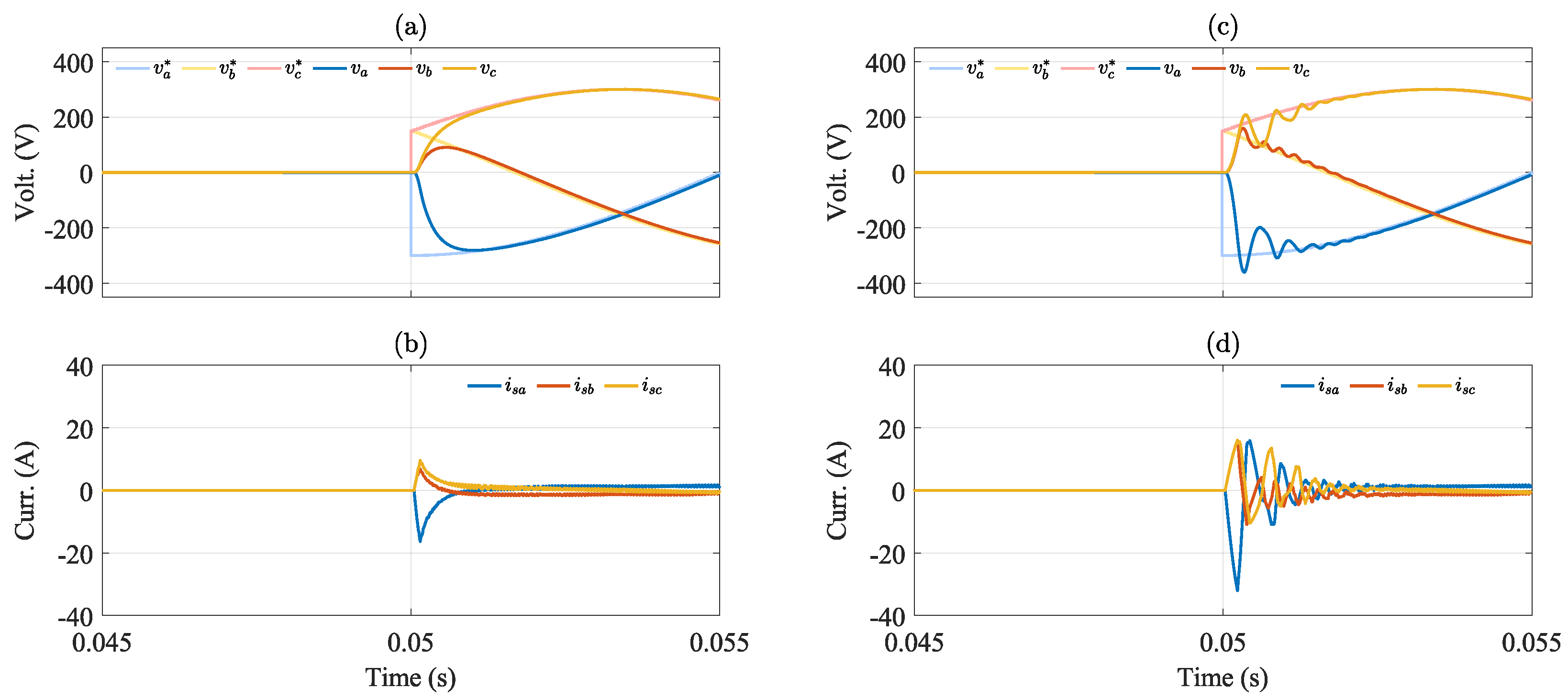

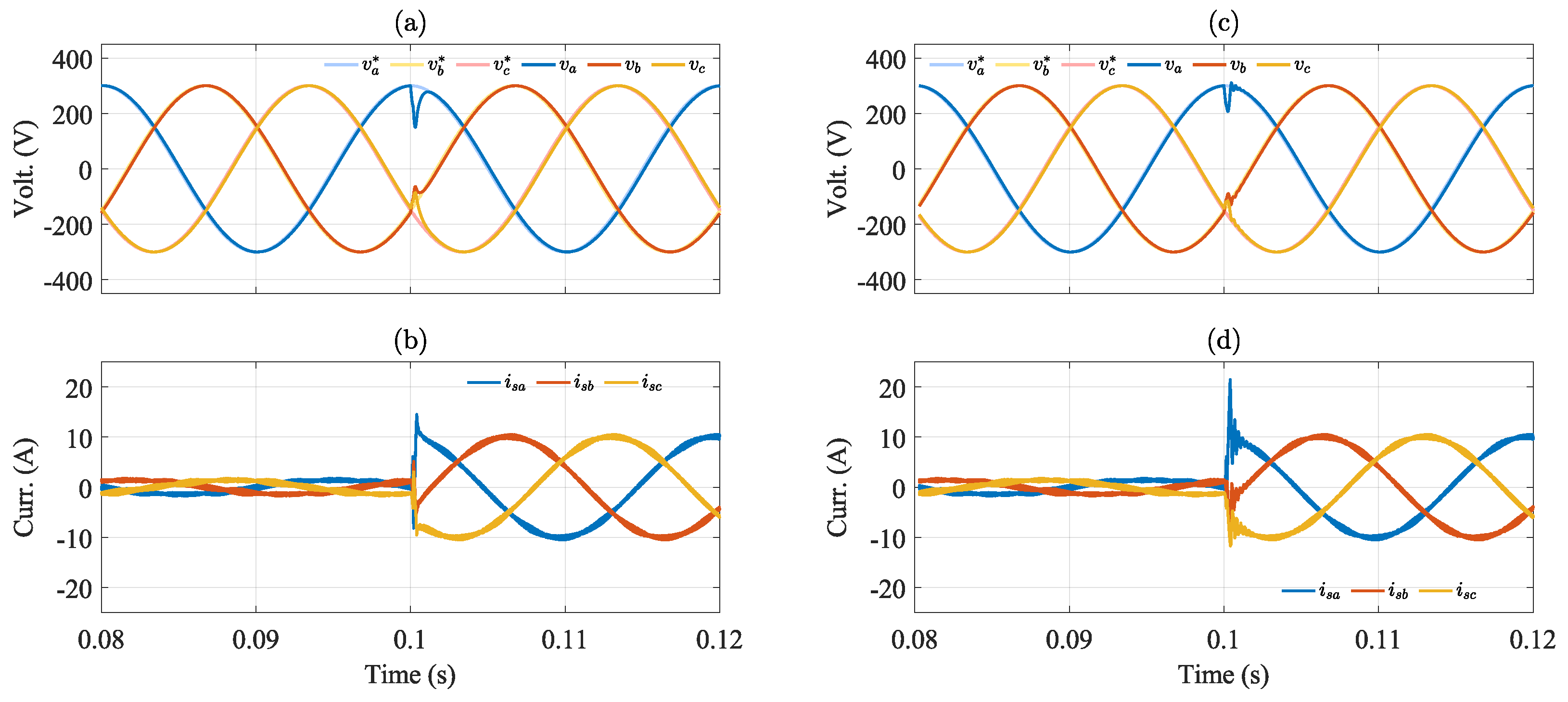

- A new OSS–MPC algorithm is proposed for the control of a 3L-NPC converter feeding an -filtered stand-alone load. It is shown that the system is more complex to regulate than the grid-connected applications discussed in [24,26], where typically only two state variables, the current components, are regulated. Conversely, for an -filtered stand-alone load, there are two more state variables, the components of the inductance currents and load voltages, and the system is not reachable using a one-step horizon OSS–MPC (for a discussion of reachability, see [28]). Moreover, as discussed in Section 3.2.1, the forward-Euler discretisation algorithm may produce some performance issues when implementing current and voltage control for an -filtered stand-alone load.

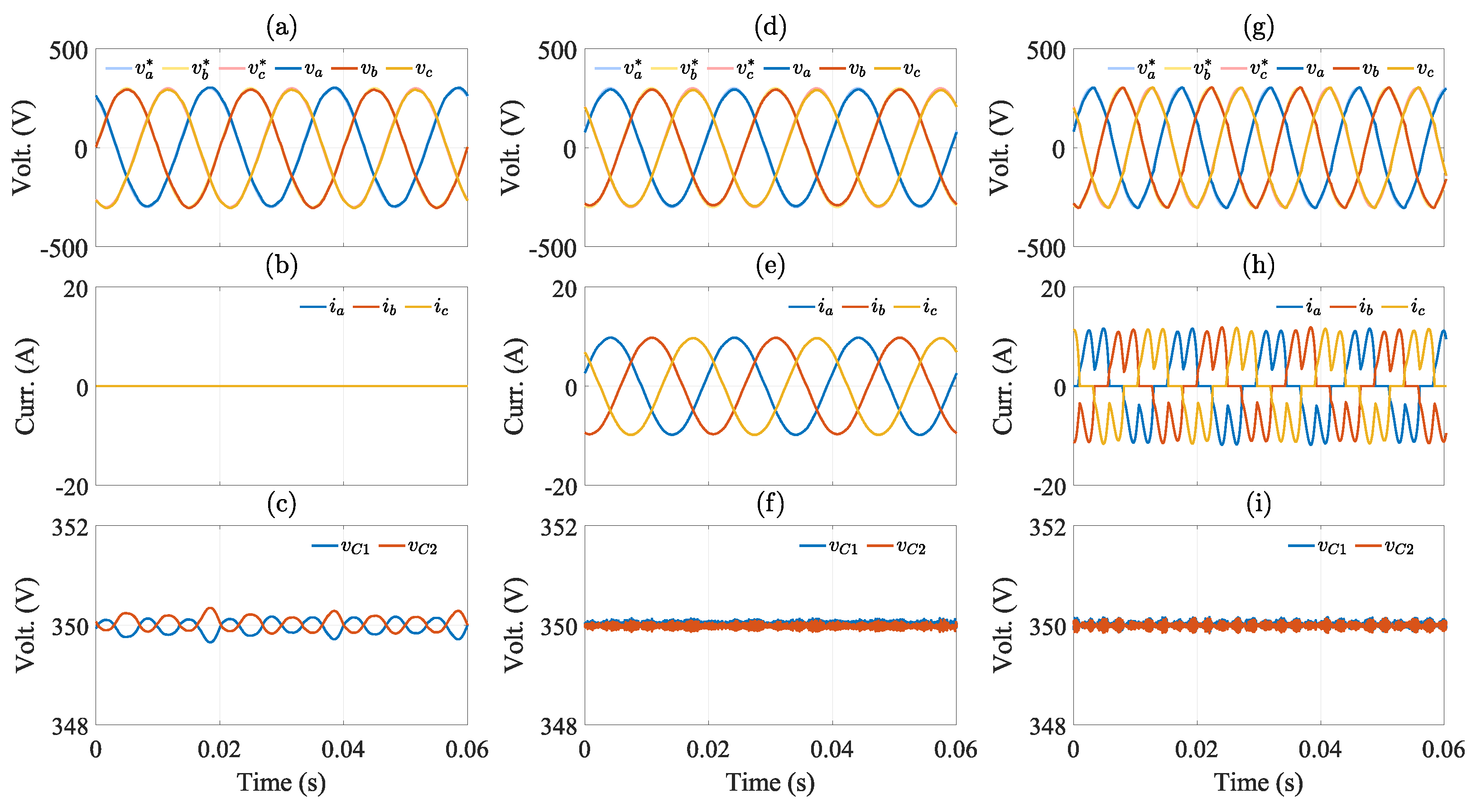

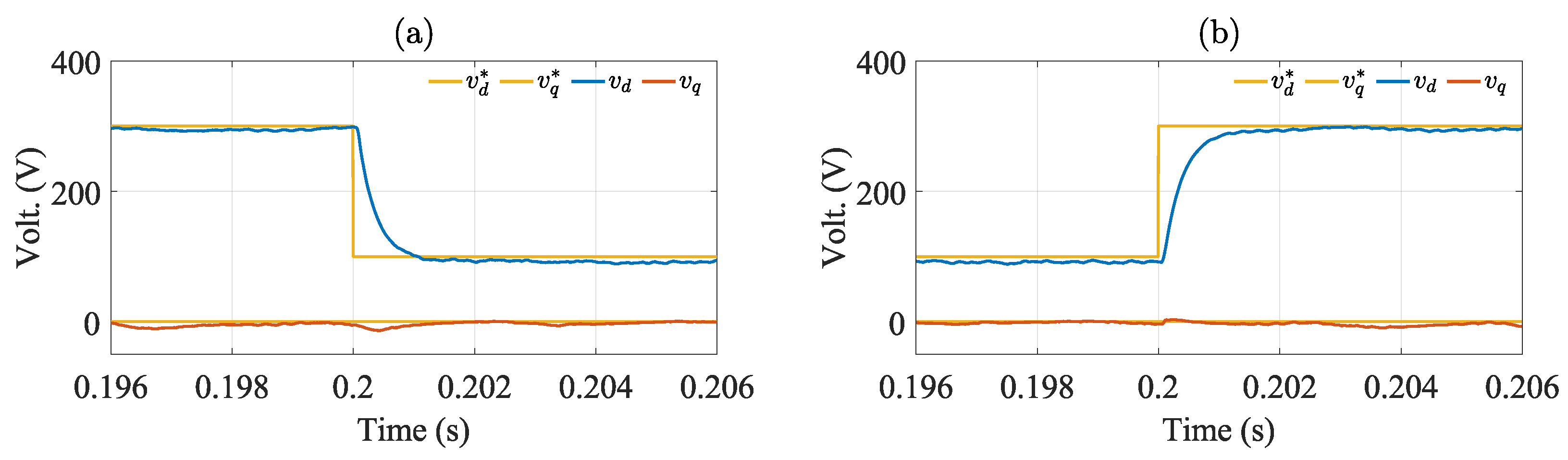

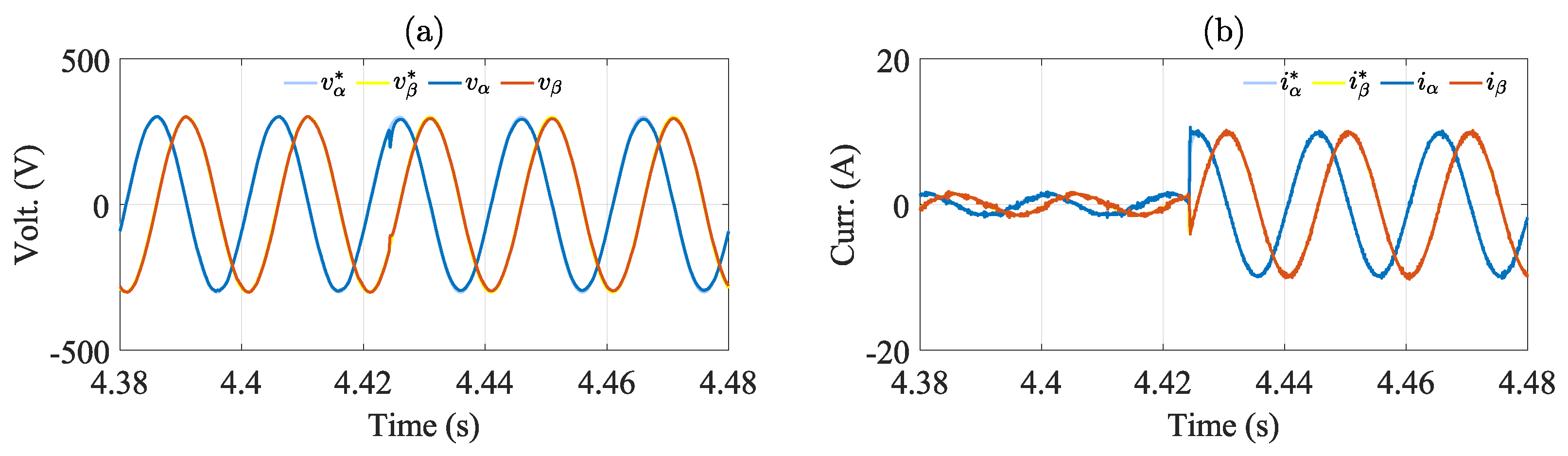

- It is shown in this work that the proposed OSS–MPC, based on the improved-Euler discretisation method, can simultaneously control the 3L-NPC converter output current and load voltage with good tracking of the references (see the final paragraphs of Section 3.2.1). This is not considered in previously reported OSS–MPCs [27], where good output-current regulation is neglected, focusing mainly on load-voltage control. Moreover, in [27] the solution to the optimal problem is obtained using an extensive search of all the space vectors available in the 3L-NPC converter. Conversely, in this work a simpler methodology with a much lesser computational burden is applied to obtain the optimal solution (see Section 5.2).

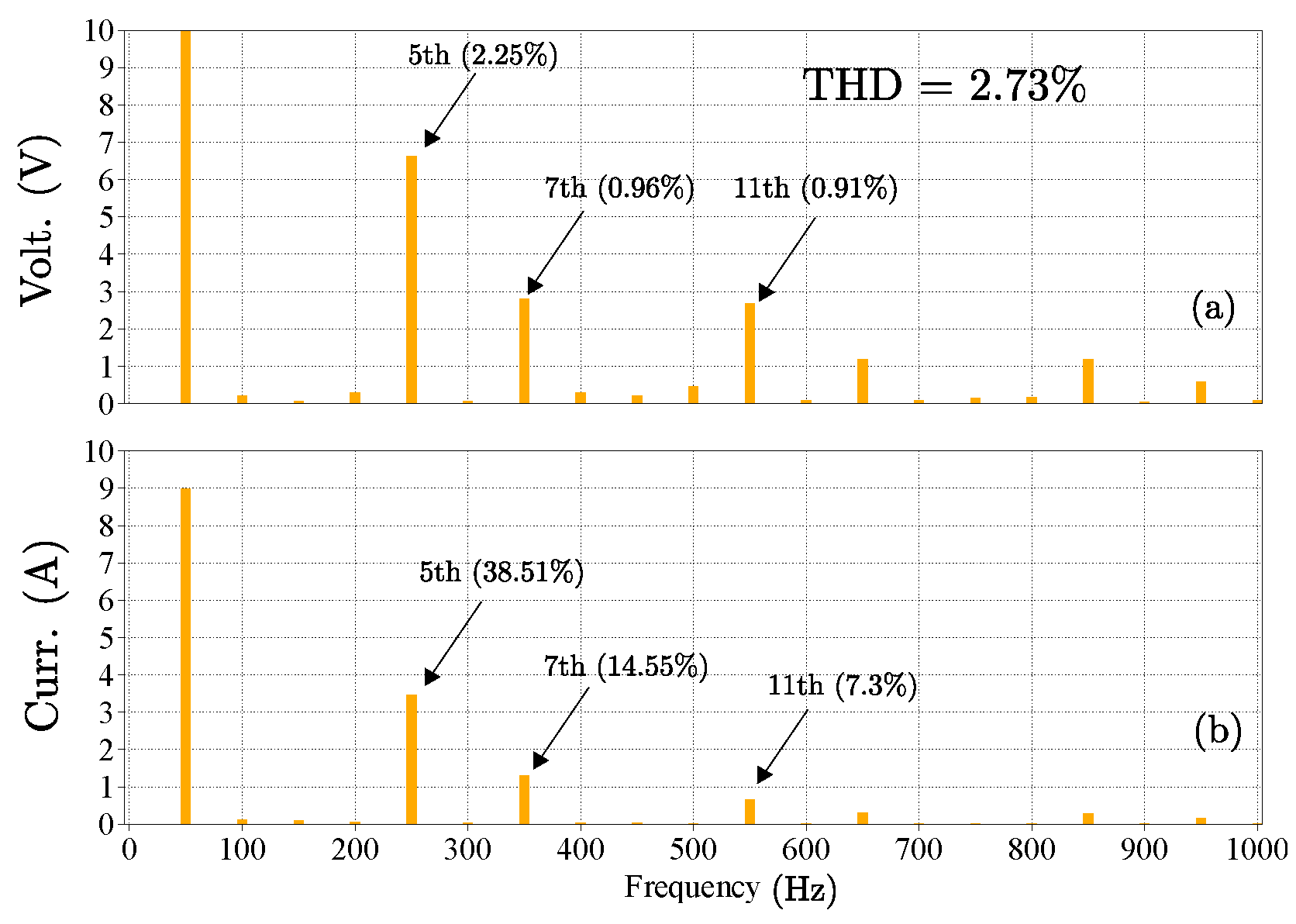

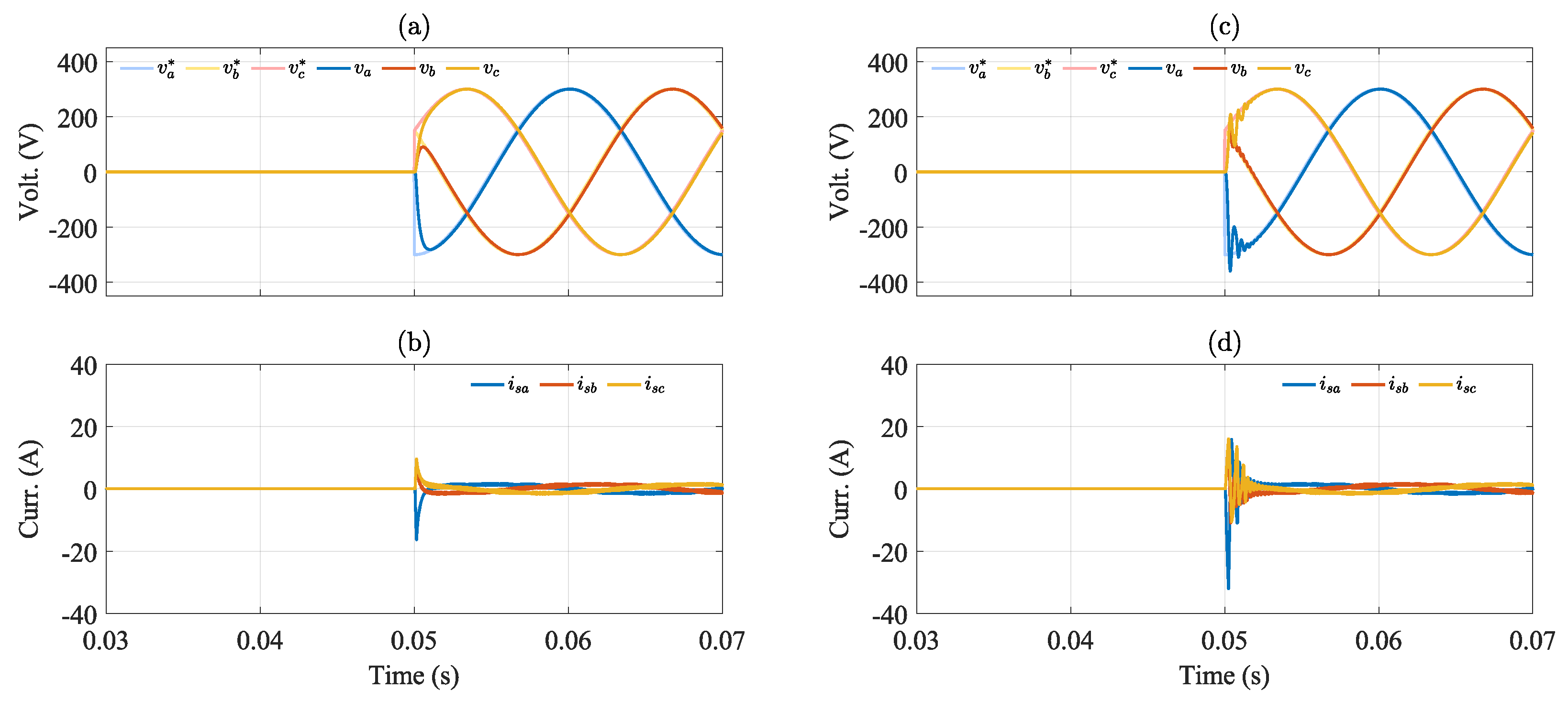

- It is shown in this work that the proposed methodology can achieve good performance for linear and nonlinear loads. This is extensively demonstrated using HIL results. Moreover, in Section 8 it is shown that the OSS–MPC proposed in this work outperforms the OSS–MPC strategy reported in [27] for several tests, including applications involving nonlinear loads.

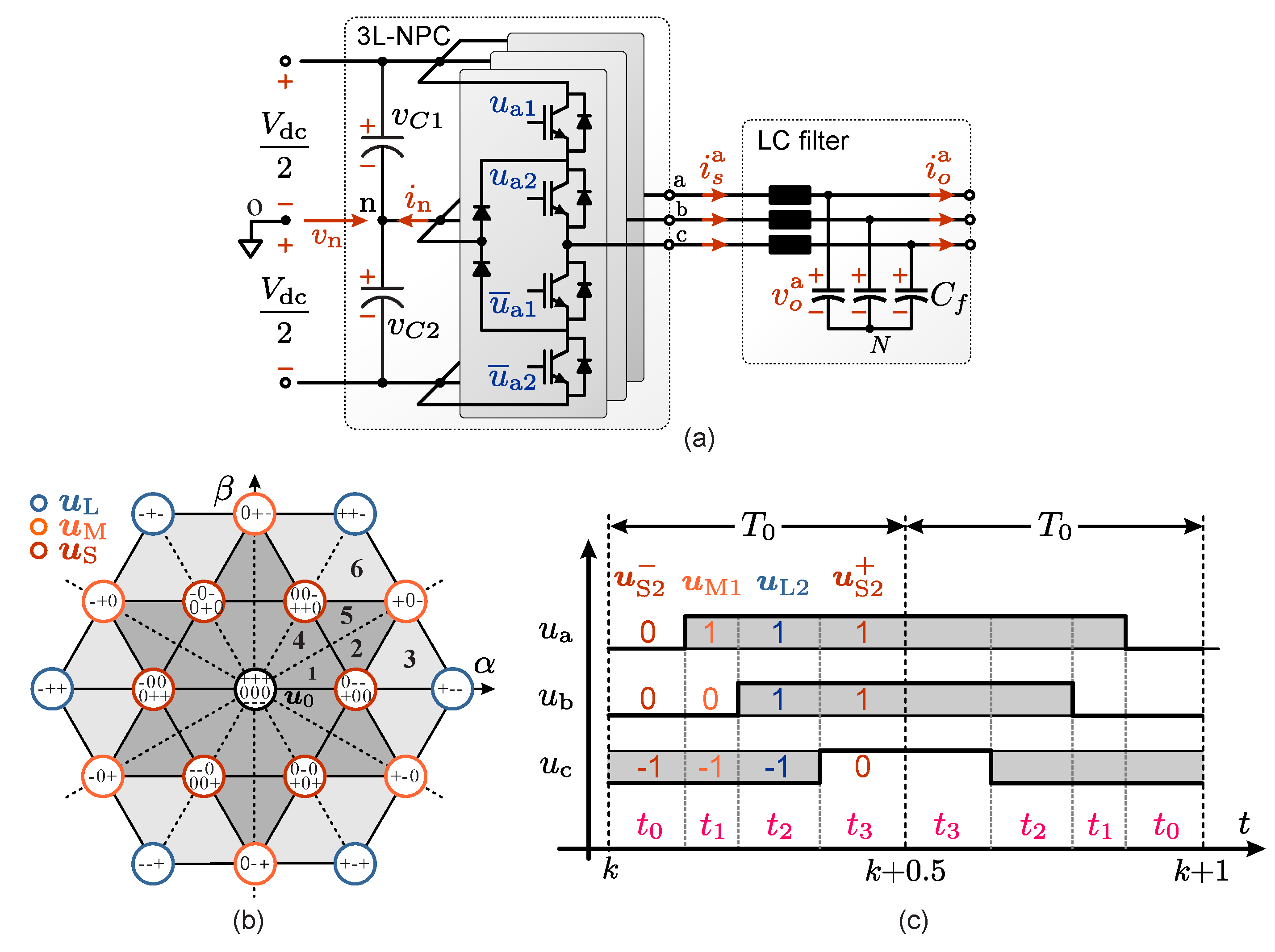

2. The 3L-NPC Inverter

3. OSS-MPC Strategy for Voltage and Current Control

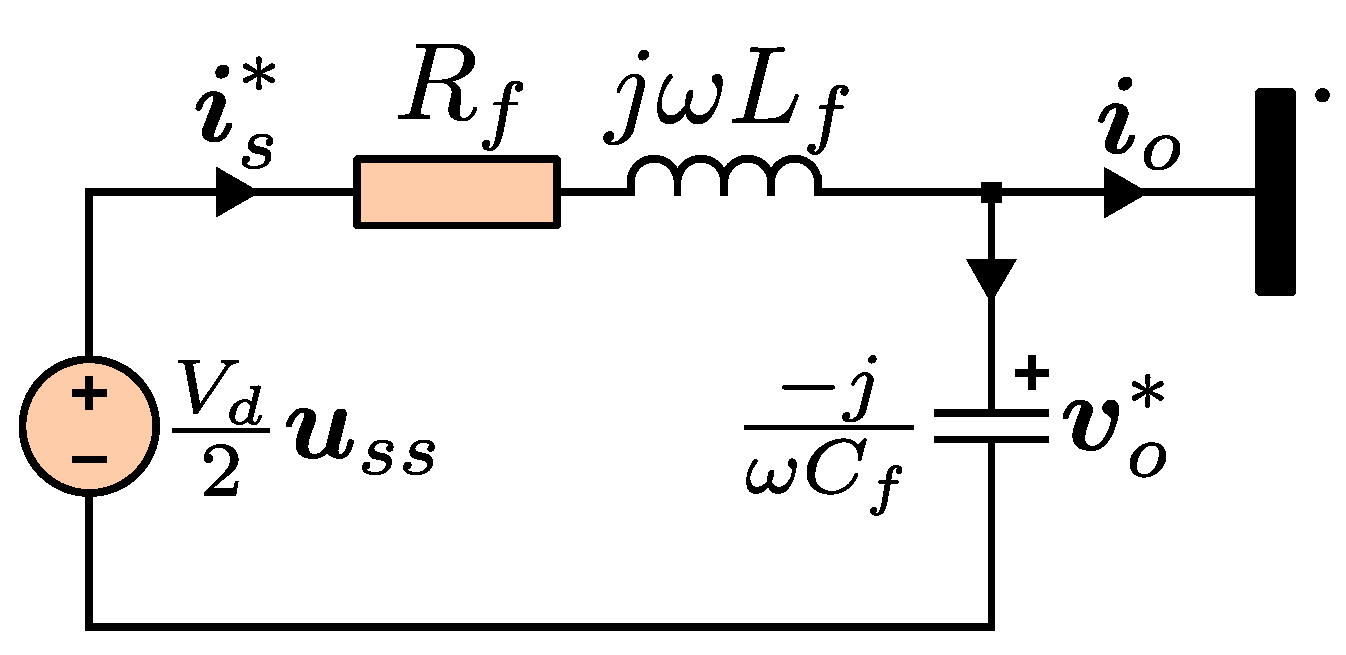

3.1. Continuous-Time Model

3.2. Discrete-Time Model

3.2.1. Forward-Euler-Based Discrete Time Model

- For these sort of applications, usually two cascaded MPC algorithm are implemented [36] to regulate the voltages and currents. An outer MPC regulates the voltages and an inner MPC regulates the converter’s output currents; in this case, the standard forward-Euler algorithm performs well. Nevertheless, when nested cascaded MPC loops are implemented, two cost functions are required and a global optimum is not necessarily reached. This is further discussed in [37].

- To obtain a global optimum, a single cost function is recommended, which has to consider the tracking errors of the currents and load voltages. However, an -filtered load is a plant which is not reachable in a single-step horizon, i.e., the output currents and load voltages cannot reach their reference values in one step because the matrix of (11) is not squared (see [28]). To solve this issue when the forward-Euler discretisation method is used, an MPC algorithm with a two-step horizon has been proposed in [37]; nevertheless, this larger prediction horizon may produce a relatively large computer burden, which can be justifiable for a large and costly modular multilevel converter but is hardly convenient for a smaller stand-alone application.

- Moreover, one of the main disadvantages of forward-Euler-based MPC algorithms for single-stage implementation (i.e., the application presented in this work) is the unconstrained solution obtained from the cost solution of (30). The matrices and obtained using the forward-Euler discretisation method (see (12)) are prone to producing an unconstrained solution for which is very weakly related to the load-voltage tracking error. Therefore, when forward-Euler is applied to the system of Figure 1b, poor performance or even a complete lack of control could be obtained for the regulation of the load voltage. Conversely, when the improved-Euler method is used to discretise (6a) and (6b), more exact matrices are obtained for and (see (17)) and the unconstrained solution for can be tuned (by adjusting the cost weights) to be dependent on both the tracking error of the load voltage as well as on the tracking error of the 3L-NPC converter output current.

3.2.2. Improved-Euler-Based Discrete Time Model

4. OSS-MPC Formulation for Voltage and Current Control

4.1. Cost Function

4.2. Optimisation Problem

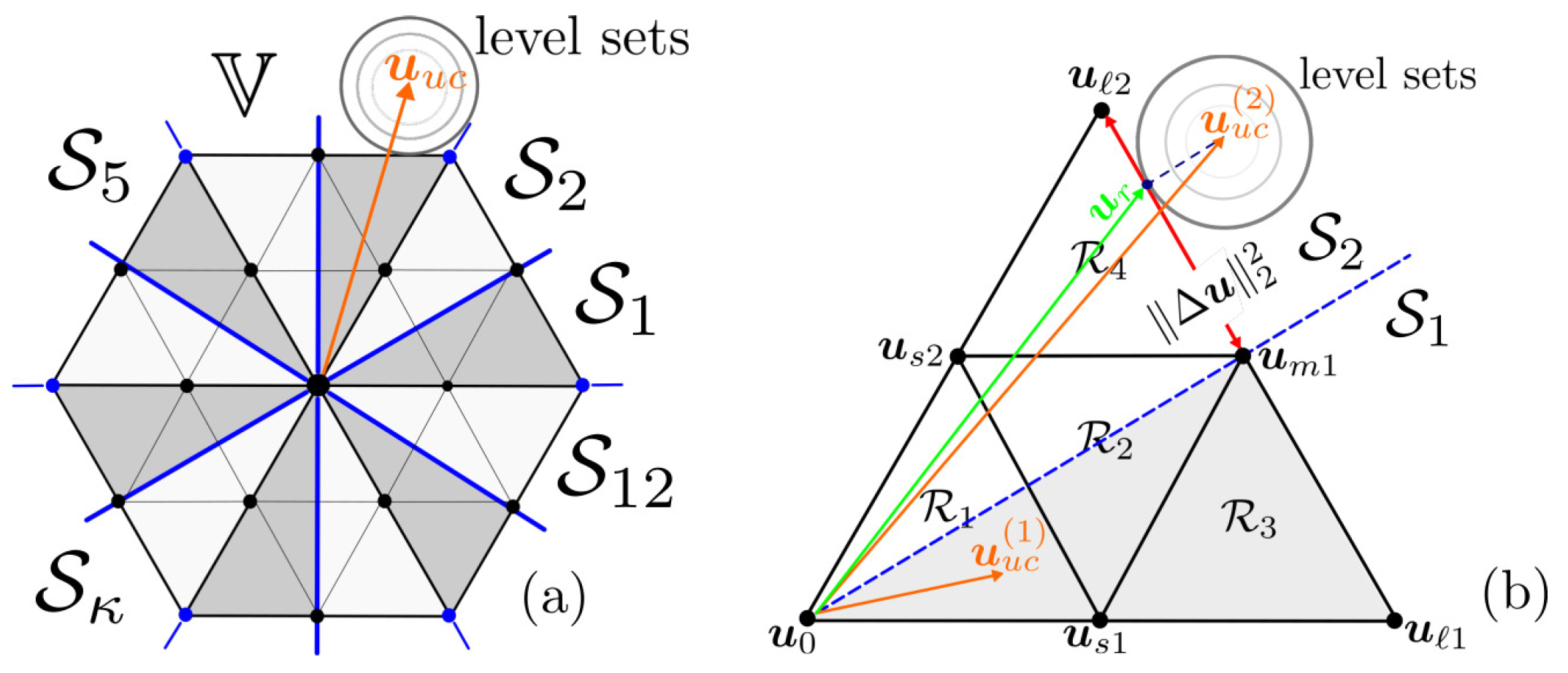

5. Optimal Solution

5.1. Non-Negative Duty Cycles: The Linear Modulation Stage

5.2. Handling the Negative Duty Cycles: The Overmodulation Stage

5.2.1. Relaxed Optimisation Problem

5.2.2. Solution of the Relaxed Optimisation Problem

6. NP-Voltage Control and PWM Modulator

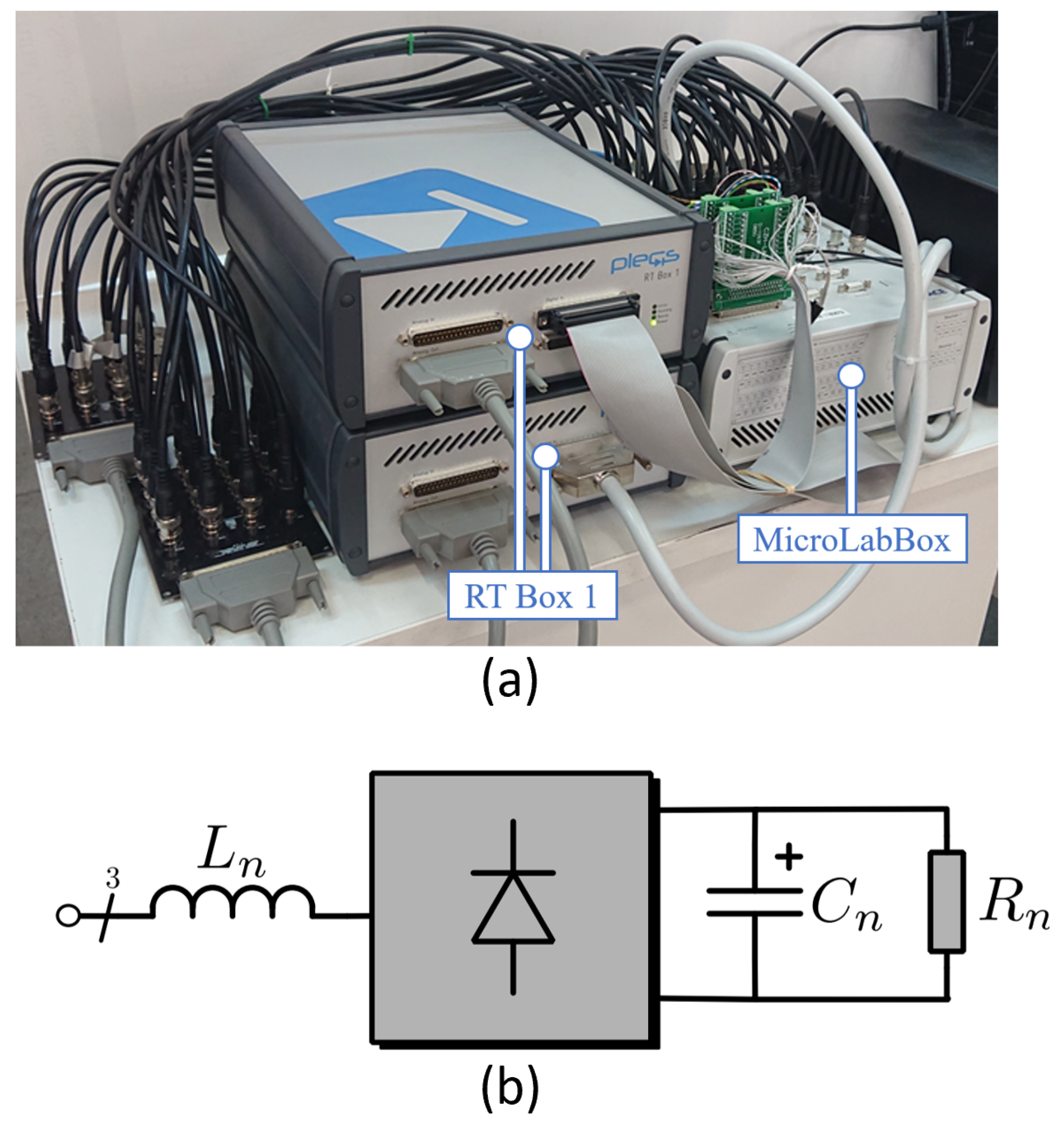

7. Hardware-in-the-Loop (HIL) Results

8. Comparison with a Previously Reported OSS-MPC Algorithm

9. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| 7S-SS | Seven Segments Switching Sequence |

| DC | Direct Current |

| AC | Alternate Current |

| FPGA | Field Programmable Gate Array |

| FCS-MPC | Finite Control Set Model Predictive Control |

| Modulated Model Predictive Control | |

| HIL | Hardware-in-the-Loop |

| LC-filter | Inductance Capacitor Filter |

| MIMO | Multiple-Input–Multiple-Output |

| MPC | Model Predictive Control |

| NPC | Neutral Point Clamped |

| OSS | Optimal Switching Sequence |

| OSV | Optimal Switching Vector |

| PWM | Pulse Width Modulation |

| RT | Real Time |

| SISO | Single-Input–Single-Output |

| THD | Total Harmonic Distortion |

| UPS | Uninterruptible Power Supply |

| VFD | Variable Frequency Drives |

References

- Loh, P.C.; Newman, M.; Zmood, D.; Holmes, D. A comparative analysis of multiloop voltage regulation strategies for single and three-phase UPS systems. IEEE Trans. Power Electron. 2003, 18, 1176–1185. [Google Scholar] [CrossRef]

- Hua, B.; Zhengming, Z.; Liqiang, Y.; Bing, L. A High Voltage and High Power Adjustable Speed Drive System Using the Integrated LC and Step-Up Transforming Filter. IEEE Trans. Power Electron. 2006, 21, 1336–1346. [Google Scholar] [CrossRef]

- Alhosaini, W.; Zhao, Y. A Model Predictive Voltage Control using Virtual Space Vectors for Grid-Forming Energy Storage Converters. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 1466–1471. [Google Scholar] [CrossRef]

- Xue, C.; Zhou, D.; Li, Y. Finite-Control-Set Model Predictive Control for Three-Level NPC Inverter-Fed PMSM Drives with LC Filter. IEEE Trans. Ind. Electron. 2021, 68, 11980–11991. [Google Scholar] [CrossRef]

- Wu, L.; Qi, X.; Shi, X.; Su, T.; Deng, Y.; Xu, D. Sensorless Predictive Control Methods for Induction Motor-An Overview. In Proceedings of the 2021 IEEE International Conference on Predictive Control of Electrical Drives and Power Electronics (PRECEDE), Jinan, China, 20–22 November 2021; pp. 536–541. [Google Scholar] [CrossRef]

- Dragičević, T. Model Predictive Control of Power Converters for Robust and Fast Operation of AC Microgrids. IEEE Trans. Power Electron. 2018, 33, 6304–6317. [Google Scholar] [CrossRef]

- Mohamed, I.S.; Rovetta, S.; Do, T.D.; Dragicević, T.; Diab, A.A.Z. A Neural-Network-Based Model Predictive Control of Three-Phase Inverter with an Output LC Filter. IEEE Access 2019, 7, 124737–124749. [Google Scholar] [CrossRef]

- Babayomi, O.; Li, Y.; Zhang, Z.; Kennel, R.; Kang, J. Overview of Model Predictive Control of Converters for Islanded AC Microgrids. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 1023–1028. [Google Scholar] [CrossRef]

- Lio, W.H.; Rossiter, J.; Jones, B.L. A review on applications of model predictive control to wind turbines. In Proceedings of the 2014 UKACC International Conference on Control (CONTROL), Loughborough, UK, 9–11 July 2014; pp. 673–678. [Google Scholar] [CrossRef]

- Soto-Sanchez, D.E.; Pena, R.; Cardenas, R.; Clare, J.; Wheeler, P. A Cascade Multilevel Frequency Changing Converter for High-Power Applications. IEEE Trans. Ind. Electron. 2013, 60, 2118–2130. [Google Scholar] [CrossRef]

- Kazmierkowski, M.P. Model Predictive Control of High Power Converters and Industrial Drives [Book News]. IEEE Ind. Electron. Mag. 2018, 12, 55–56. [Google Scholar] [CrossRef]

- Mesbah, A. Stochastic Model Predictive Control: An Overview and Perspectives for Future Research. IEEE Control. Syst. Mag. 2016, 36, 30–44. [Google Scholar] [CrossRef]

- Elmorshedy, M.F.; Xu, W.; El-Sousy, F.F.M.; Islam, M.R.; Ahmed, A.A. Recent Achievements in Model Predictive Control Techniques for Industrial Motor: A Comprehensive State-of-the-Art. IEEE Access 2021, 9, 58170–58191. [Google Scholar] [CrossRef]

- Mirzaeva, G.; Mo, Y. Model Predictive Control for Industrial Drive Applications. IEEE Trans. Ind. Appl. 2023, 59, 7897–7907. [Google Scholar] [CrossRef]

- Karamanakos, P.; Geyer, T.; Oikonomou, N.; Kieferndorf, F.D.; Manias, S. Direct Model Predictive Control: A Review of Strategies That Achieve Long Prediction Intervals for Power Electronics. IEEE Ind. Electron. Mag. 2014, 8, 32–43. [Google Scholar] [CrossRef]

- Renjith, K.K.; Sankar, D.; Hima, T. A Comprehensive Review on Finite Control Set Model Predictive Control: Trends and Prospects. In Proceedings of the 2022 Third International Conference on Intelligent Computing Instrumentation and Control Technologies (ICICICT), Kannur, India, 11–12 August 2022; pp. 206–210. [Google Scholar] [CrossRef]

- Karamanakos, P.; Liegmann, E.; Geyer, T.; Kennel, R. Model Predictive Control of Power Electronic Systems: Methods, Results, and Challenges. IEEE Open J. Ind. Appl. 2020, 1, 95–114. [Google Scholar] [CrossRef]

- Rodriguez, J.; Pontt, J.; Silva, C.A.; Correa, P.; Lezana, P.; Cortes, P.; Ammann, U. Predictive Current Control of a Voltage Source Inverter. IEEE Trans. Ind. Electron. 2007, 54, 495–503. [Google Scholar] [CrossRef]

- Karamanakos, P.; Geyer, T. Guidelines for the Design of Finite Control Set Model Predictive Controllers. IEEE Trans. Power Electron. 2020, 35, 7434–7450. [Google Scholar] [CrossRef]

- Tarisciotti, L.; Zanchetta, P.; Watson, A.; Clare, J.; Degano, M.; Bifaretti, S. Modulated model predictive control (M2PC) for a 3-phase active front-end. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 1062–1069. [Google Scholar] [CrossRef]

- Vazquez, S.; Marquez, A.; Aguilera, R.; Quevedo, D.; Leon, J.I.; Franquelo, L.G. Predictive Optimal Switching Sequence Direct Power Control for Grid-Connected Power Converters. IEEE Trans. Ind. Electron. 2015, 62, 2010–2020. [Google Scholar] [CrossRef]

- Karamanakos, P.; Nahalparvari, M.; Geyer, T. Fixed Switching Frequency Direct Model Predictive Control with Continuous and Discontinuous Modulation for Grid-Tied Converters with LCL Filters. IEEE Trans. Control. Syst. Technol. 2020, 29, 1503–1518. [Google Scholar] [CrossRef]

- Xu, B.; Liu, K.; Ran, X. Computationally Efficient Optimal Switching Sequence Model Predictive Control for Three-Phase Vienna Rectifier Under Balanced and Unbalanced DC Links. IEEE Trans. Power Electron. 2021, 36, 12268–12280. [Google Scholar] [CrossRef]

- Mora, A.; Cárdenas-Dobson, R.; Aguilera, R.P.; Angulo, A.; Donoso, F.; Rodriguez, J. Computationally Efficient Cascaded Optimal Switching Sequence MPC for Grid-Connected Three-Level NPC Converters. IEEE Trans. Power Electron. 2019, 34, 12464–12475. [Google Scholar] [CrossRef]

- Vazquez, S.; Acuna, P.; Aguilera, R.P.; Pou, J.; Leon, J.I.; Franquelo, L.G. DC-Link Voltage-Balancing Strategy Based on Optimal Switching Sequence Model Predictive Control for Single-Phase H-NPC Converters. IEEE Trans. Ind. Electron. 2020, 67, 7410–7420. [Google Scholar] [CrossRef]

- Mora, A.; Cardenas, R.; Aguilera, R.P.; Angulo, A.; Lezana, P.; Lu, D.D.C. Predictive Optimal Switching Sequence Direct Power Control for Grid-Tied 3L-NPC Converters. IEEE Trans. Ind. Electron. 2021, 68, 8561–8571. [Google Scholar] [CrossRef]

- Zheng, C.; Dragičević, T.; Zhang, Z.; Rodriguez, J.; Blaabjerg, F. Model Predictive Control of LC-Filtered Voltage Source Inverters with Optimal Switching Sequence. IEEE Trans. Power Electron. 2021, 36, 3422–3436. [Google Scholar] [CrossRef]

- Quevedo, D.E.; Aguilera, R.P.; Geyer, T. Predictive Control in Power Electronics and Drives: Basic Concepts, Theory, and Methods. In Advanced and Intelligent Control in Power Electronics and Drives; Orłowska-Kowalska, T., Blaabjerg, F., Rodríguez, J., Eds.; Studies in Computational Intelligence; Springer International Publishing: Cham, Switzerland, 2014; pp. 181–226. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Zakzewski, D.; Resalayyan, R.; Khaligh, A. Hybrid Neutral Point Clamped Converter: Review and Comparison to Traditional Topologies. IEEE Trans. Transp. Electrif. 2023, 1. [Google Scholar] [CrossRef]

- Rocha, A.V.; de Paula, H.; dos Santos, M.E.; Filho, B.J.C. Increasing long belt-conveyors availability by using fault-resilient medium voltage AC drives: Part II—Reliability and maintenance assessment. In Proceedings of the 2012 IEEE Industry Applications Society Annual Meeting, Las Vegas, NV, USA, 7–11 October 2012; pp. 1–8, ISSN 0197-2618. [Google Scholar]

- Akagi, H.; Watanabe, E.H.; Aredes, M. Instantaneous Power Theory and Applications to Power Conditioning; Wiley: Hoboken, NJ, USA, 2007; p. 379. [Google Scholar]

- Wu, B. High-Power Converters and AC Drives; Wiley-IEEE Press: Hoboken, NJ, USA, 2006. [Google Scholar]

- Jayakumar, V.; Chokkalingam, B.; Munda, J.L. A Comprehensive Review on Space Vector Modulation Techniques for Neutral Point Clamped Multi-Level Inverters. IEEE Access 2021, 9, 112104–112144. [Google Scholar] [CrossRef]

- Arias-Esquivel, Y.; Cárdenas, R.; Urrutia, M.; Diaz, M.; Tarisciotti, L.; Clare, J.C. Continuous Control Set Model Predictive Control of a Modular Multilevel Converter for Drive Applications. IEEE Trans. Ind. Electron. 2023, 70, 8723–8733. [Google Scholar] [CrossRef]

- Arias-Esquivel, Y.; Cárdenas, R.; Tarisciotti, L.; Díaz, M.; Mora, A. A Two-Step Continuous-Control-Set MPC for Modular Multilevel Converters Operating with Variable Output Voltage and Frequency. IEEE Trans. Power Electron. 2023, 38, 12091–12103. [Google Scholar] [CrossRef]

- Süli, E.; Mayers, D. An Introduction to Numerical Analysis; Cambridge University Press: Cambridge, UK, 2003. [Google Scholar]

- Zheng, C.; Yang, J.; Gong, Z. Efficient Finite-Set Model Predictive Voltage Control of Islanded-Mode Grid-Forming Inverters with Current Constraints. IEEE Access 2022, 10, 95919–95927. [Google Scholar] [CrossRef]

- Mattavelli, P. An improved deadbeat control for UPS using disturbance observers. IEEE Trans. Ind. Electron. 2005, 52, 206–212. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B. Fundamentals of Model Predictive Control. In Model Predictive Control of Wind Energy Conversion Systems; Wiley: Hoboken, NJ, USA, 2017; pp. 117–148. [Google Scholar] [CrossRef]

- Hackl, C. MPC with analytical solution and integral error feedback for LTI MIMO systems and its application to current control of grid-connected power converters with LCL-filter. In Proceedings of the 2015 IEEE International Symposium on Predictive Control of Electrical Drives and Power Electronics (PRECEDE), Valparaiso, Chile, 5–6 October 2015; pp. 61–66. [Google Scholar] [CrossRef]

- Oravec, J.; Bakosova, M.; Hanulova, L. Experimental Investigation of Robust MPC Design with Integral Action for a Continuous Stirred Tank Reactor. In Proceedings of the 2018 IEEE Conference on Decision and Control (CDC), Miami, FL, USA, 17–19 December 2018; pp. 2611–2616. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Switching and sampling frequency | = 20 kHz |

| DC-link voltage | = 700 V |

| LC filter | = 1 m = 2.4 mH = 15 F |

| Load resistance | = 30 |

| Nonlinear load | = 1.8 mH = 2.2 mF = 60 |

| Filter current weight factor | = 0.25 |

| Load-voltage weight factor |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Herrera, F.; Mora, A.; Cárdenas, R.; Díaz, M.; Rodríguez, J.; Rivera, M. An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC Converter with Output LC Filter. Processes 2024, 12, 348. https://doi.org/10.3390/pr12020348

Herrera F, Mora A, Cárdenas R, Díaz M, Rodríguez J, Rivera M. An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC Converter with Output LC Filter. Processes. 2024; 12(2):348. https://doi.org/10.3390/pr12020348

Chicago/Turabian StyleHerrera, Felipe, Andrés Mora, Roberto Cárdenas, Matías Díaz, José Rodríguez, and Marco Rivera. 2024. "An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC Converter with Output LC Filter" Processes 12, no. 2: 348. https://doi.org/10.3390/pr12020348

APA StyleHerrera, F., Mora, A., Cárdenas, R., Díaz, M., Rodríguez, J., & Rivera, M. (2024). An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC Converter with Output LC Filter. Processes, 12(2), 348. https://doi.org/10.3390/pr12020348