Research on Modeling Method of Testability Design Based on Static Automatic Fault Tree

Abstract

1. Introduction

- Customized modeling for diverse application objects is of utmost importance. For instance, studies on the liquid rocket engine system [7], radar system [8], power filter combined system [9], and USB–GPIB controller interface circuit [10], among others, focus on refining the MSFM or hybrid diagnosis model to fit different objects. However, as objects change, these methods may become inapplicable.

- Tackling the challenge of identifying analog signals is essential. Chakrabarty et al. employed Monte Carlo simulation and threshold determination to evaluate the effectiveness of analog signals [11]. Similarly, Chen et al. enhanced Chakrabarty’s model and proposed adaptive threshold judgment theory, broadening the range of recognizable analog signals [12].

- Resolving the issue of insufficient information in existing models is crucial due to its versatility. The MSFM faces this challenge more prominently. For example, Yang et al. introduced two additional attributes to propose a new testability prediction method based on the MSFM [13]. Likewise, Sun et al. improved the single-feature dependency matrix through feature extraction and multi-value coding, presenting a testability model based on multiple features [14].

- This work establishes a novel and versatile model for testability design, capable of evaluating both system reliability and safety in one process.

- This study presents safety sensitivity indicators that can effectively assess the impact of faults on system safety and offers two new safety-related testing metrics as practical and reliable evaluation criteria for system safety.

2. Safety-Related Fault Model (SRFM)

2.1. Motivation

2.2. The Whole Picture of SRFM

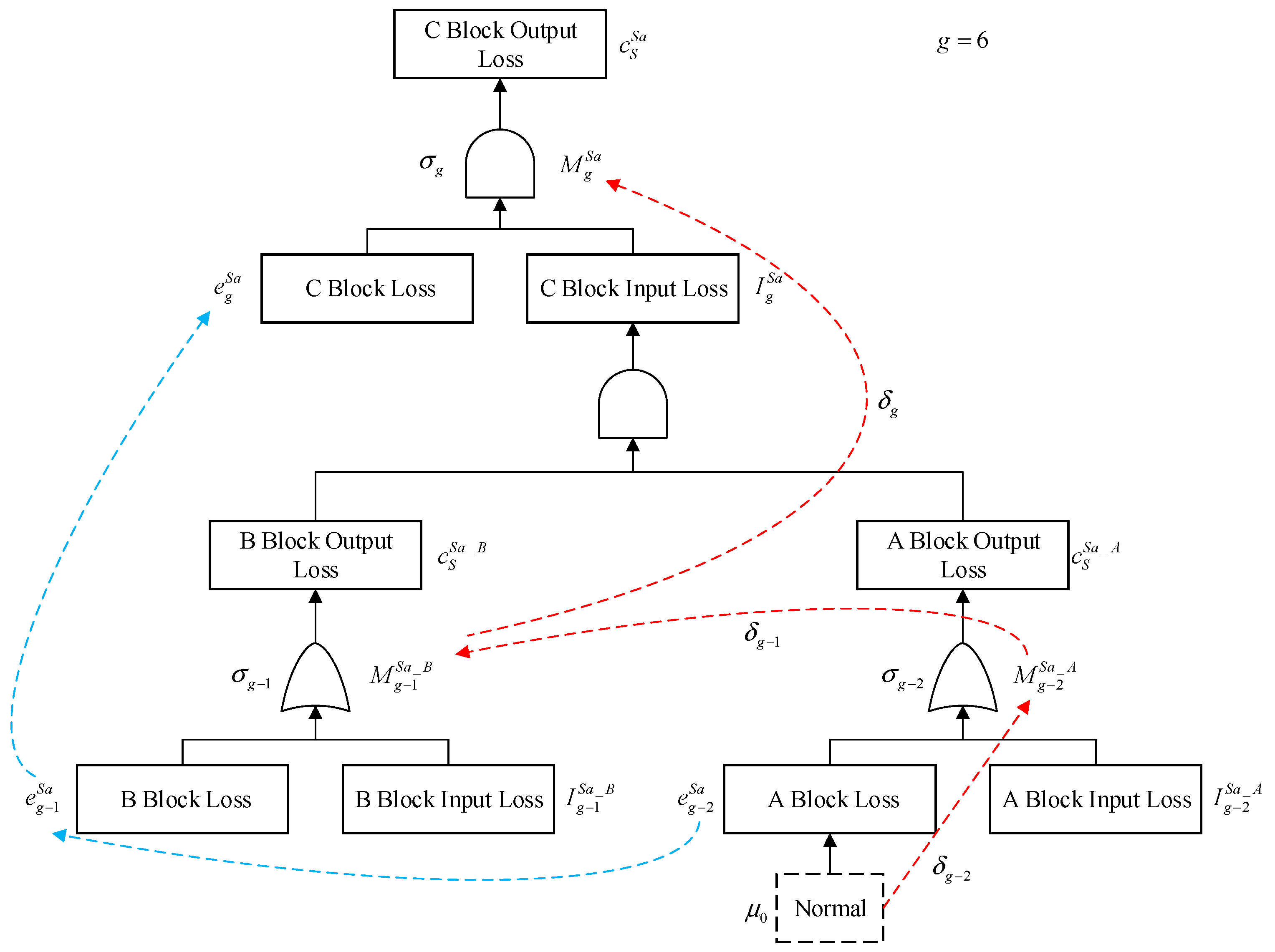

2.3. Static Automatic Fault Tree

2.3.1. Fundamental Concepts of Nine Tuples

2.3.2. The Theoretical Analysis Process

- (a)

- The variable of is ;

- (b)

- The minimum cut set of corresponds to the event set one by one, so there is a modal sequence , and

2.3.3. Modal Change Analysis of MSFM Based on Nine Tuples

2.3.4. A General Static Automatic Fault Tree Modeling Method

2.4. Safety-Related Faults and Safety-Related Signal Features

2.4.1. Safety Sensitivity

2.4.2. Calculation of SRF and SRSF

2.5. Safety-Related Dependency Matrix (S-D Matrix)

2.6. New Metrics

3. Experimental Section

3.1. Experiment Setup

- Testability Modeling Process

- 2.

- Fault Diagnosis Process

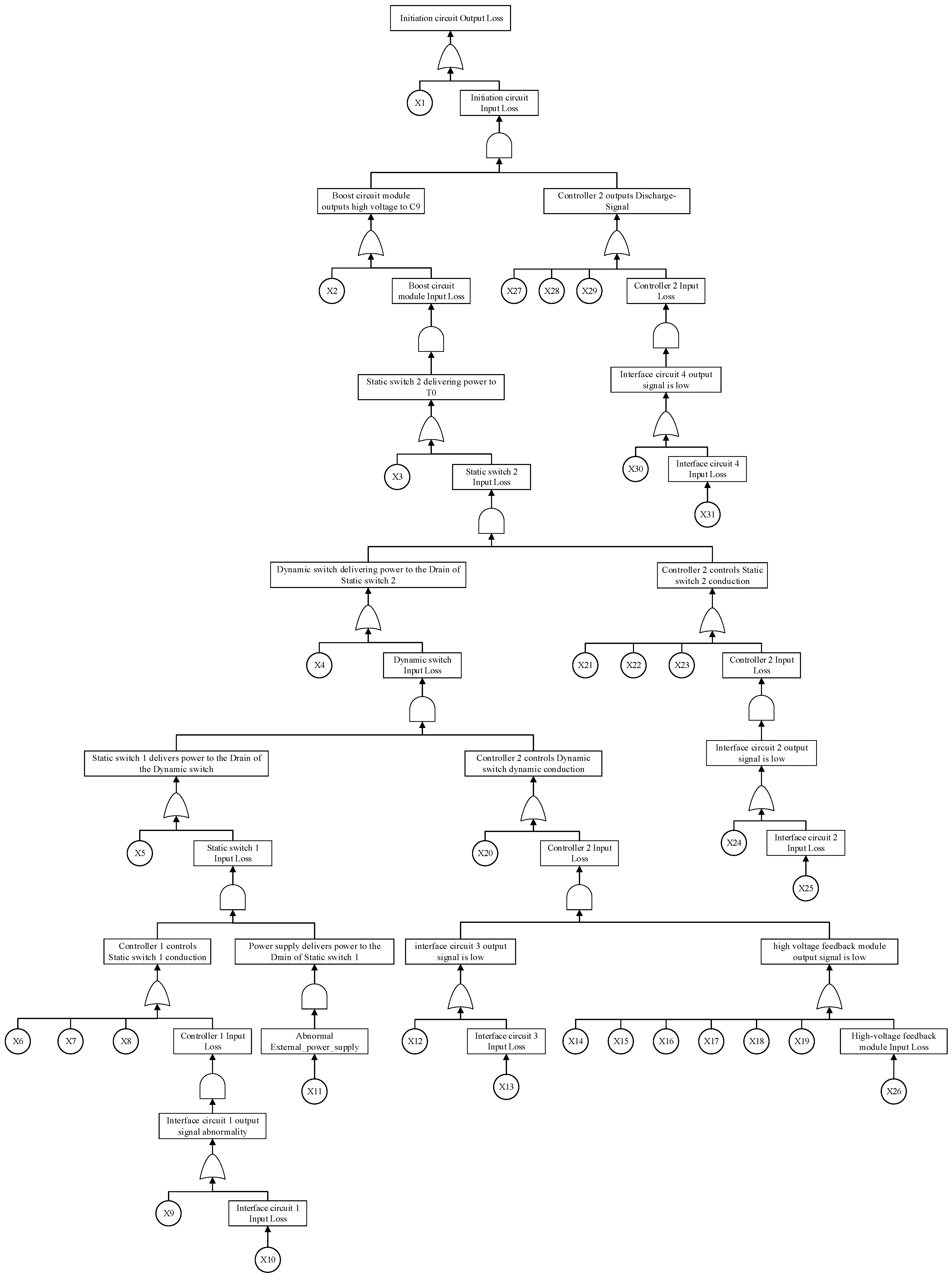

3.2. Electronic Safety and Arming

- Power supply function: S1 logic power supply signal, S2 power supply signal.

- Logic control functions: S3 static switch 1 status signal, S4 static switch 2 status signal, S5 dynamic switch status signal, and S9 energy circuit conduction signal.

- Circuit boost function: S6 high-voltage capacitor voltage steady-state value and S7 high-voltage capacitor voltage boost speed.

- Trigger function: S8 ignition signal.

- Establishing the Static Automatic Fault Tree (SAFT)

- 2.

- Calculating the result of Safety-Related Faults (SRF) and Safety-Related Signal Features (SRSF)

- The probability of lightning striking the equipment using the ESA is generally one in hundreds of thousands. It is nearly impossible for lightning to penetrate the external shell of the equipment and affect the internal capacitance.

- If the feedback signal of the initiation circuit is abnormal, it is necessary to ensure that the high-voltage capacitor in the initiation circuit is charged.

- 3.

- Establishment of safety-related dependency matrix (S-D matrix)

3.3. Results and Analysis

- Improvement in TASAP: By comparing the S-D matrix and D matrix established for the ESA, when WFD is used as the processing algorithm, the TASAP of the former increases by 82%, and when IG is used, it increases by 303%. This indicates that the test sequence generated by the S-D matrix significantly enhances the system safety evaluation.

- Enhancement in TASAN: The S-D matrix and D matrix established for the ESA show an improvement in TASAN. With WFD, the former increases by 59%, and with IG, it increases by 52%. This reinforces the idea that the test sequence derived from the S-D matrix improves system safety evaluation.

- IG’s ETC remains largely unchanged: When IG is used as the processing algorithm, the ETC of the S-D matrix is reduced by only 0.0148 compared to the D matrix. This suggests that the ETC generated by the S-D matrix’s test sequence is comparable to or insignificantly different from that generated by the D matrix as measured by the ETC standard.

- Both WFD and IG achieve a 100% FDR: Using the ESA as the subject, it is clear that employing the S-D matrix for diagnostic fault testing (DFT) does not lead to a decline in FDR.

- Prioritization of safety-related tests: For instance, in the IG-processed S-D matrix result, T9 is initially selected as the test object. In contrast, T8 is the preferred test in the IG-processed D matrix result. In the case of the ESA, the accidental charging of the high-voltage capacitor (boost circuit) is a typical safety-related fault (SRF), significantly impacting safety. Testing T9 first directly assesses the status of the boost circuit, promptly detecting potential safety hazards. If T8 were tested first and a fault in the booster circuit was present, a safety risk might go unnoticed.

- Increased selection of safety-related tests: The test sequence based on the S-D matrix additionally selects T4, which tests the control signal of the dynamic switch for the ESA. This test is crucial for ensuring energy accumulation through dynamic switch closure, which is vital for ESA safety. However, the test sequence generated based on the D matrix lacks such targeted detection.

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Cui, Y.; Shi, J.; Wang, Z. Intermittent fault process and false alarm interaction modelling of threshold-based monitoring built-in tests (BITs). Int. J. Prod. Res. 2016, 54, 1610–1626. [Google Scholar] [CrossRef]

- Yang, C. Parallel-series multiobjective genetic algorithm for optimal tests selection with multiple constraints. IEEE Trans. Instrum. Meas. 2018, 67, 1859–1876. [Google Scholar] [CrossRef]

- Sheppard, J.W.; Simpson, W.R. A mathematical model for integrated diagnostics. IEEE Des. Test Comput. 1992, 8, 25–38. [Google Scholar] [CrossRef]

- Shakeri, M. Advances in System Fault Modeling and Diagnosis. University of Connecticut. 1996. Available online: https://opencommons.uconn.edu/dissertations/AAI9707210 (accessed on 22 March 2024).

- Somnath, D.; Pattipati, K.R. Multi-signal flow graphs: A novel approach for system testability analysis and fault diagnosis. IEEE Aerosp. Electron. Syst. Mag. 1995, 10, 14–25. [Google Scholar] [CrossRef]

- Gould, E. Modeling it both ways: Hybrid diagnostic modeling and its application to hierarchical system designs. In Proceedings of the Autotestcon, San Antonio, TX, USA, 20–23 September 2004. [Google Scholar]

- Wu, Y.; Yu, J.; Tang, D.; Tian, L.; Gao, Z.; Dai, J. A hierarchical testability analysis method for reusable liquid rocket engines based on multi-signal flow model. In Proceedings of the 2020 15th IEEE Conference on Industrial Electronics and Applications (ICIEA), Kristiansand, Norway, 9–13 November 2020; pp. 1768–1772. [Google Scholar] [CrossRef]

- Du, X.; Hu, B.; Qin, J. Testability Analysis Method of Radar Equipment Based on Dependency Model. J. Phys. Conf. Ser. 2021, 2093, 012031. [Google Scholar] [CrossRef]

- Neser, H.; van Schoor, G.; Uren, K.R. Energy-based fault detection and isolation of a Brayton cycle-based HTGR power conversion unit—A comparative study. Ann. Nucl. Energy 2021, 164, 108616. [Google Scholar] [CrossRef]

- Bing, L.; Tian, S.; Wang, H. Modified Diagnosis Algorithms Based on Multisignal Model and Application in Circuit Boards. In Proceedings of the International Conference on Communications, Kokura, Japan, 11–13 July 2007; IEEE: New York, NY, USA, 2007; pp. 1168–1171. [Google Scholar] [CrossRef]

- Chakrabarty, S.; Rajan, V.; Ying, J.; Mansjur, M.; Pattipati, K.; Deb, S. A virtual test-bench for analog circuit testability analysis and fault diagnosis. In Proceedings of the 1998 IEEE AUTOTESTCON Proceedings. IEEE Systems Readiness Technology Conference. Test Technology for the 21st Century (Cat. No.98CH36179), Salt Lake City, UT, USA, 25–27 August 1998; pp. 337–352. [Google Scholar] [CrossRef]

- Xiaomei, X.C.; Xiaofeng, X.F.; Guohua, G.H. A Modified Simulation-Based Multi-Signal Modeling for Electronic System. J Electron Test 2012, 28, 155–165. [Google Scholar] [CrossRef]

- Zhiyong, Y.; Xu, A.; Niu, S.; Wang, Z. A new method of testability prediction on model and probability analysis. In Proceedings of the 2007 8th International Conference on Electronic Measurement and Instruments, Xi’an, China, 16–18 August 2007; pp. 3-991–3-994. [Google Scholar] [CrossRef]

- Sun, M.; Jing, B.; Yifeng, H.; Xiaoxuan, J.; Guangyue, X. Establishment and analysis of D matrix model based on multi-feature quantity. J. Electron. Meas. Instrum. 2016, 31, 1731–1736. [Google Scholar] [CrossRef]

- Hu, Y.; Parhizkar, T.; Mosleh, A. Guided simulation for dynamic probabilistic risk assessment of complex systems: Concept, method, and application. Reliab. Eng. Syst. Saf. 2022, 217, 108047. [Google Scholar] [CrossRef]

- Sharvia, S.; Papadopoulos, Y. Non-coherent modelling in compositional fault tree analysis. IFAC Proc. Vol. 2008, 41, 4138–4143. [Google Scholar] [CrossRef]

- Huo, L.; Wang, Y. Fuze ballistic burst estimation by fault tree analysis. J. Detect. Control 2020, 42, 13–20. [Google Scholar]

- Xu, R.; Che, J.; Yang, Z.; Zuo, X. The Fault Tree Analysis and Its Application in the system Reliability Analysis. Command. Control Simul. 2010, 32, 112–115. [Google Scholar]

- Garrick, B.J. Lessons Learned from 21 Nuclear Plant Probabilistic Risk Assessments. Nucl. Technol. 1989, 84, 319–330. [Google Scholar] [CrossRef]

- U.S. Nuclear Regulatory Commission. Nuclear Regulatory Commission. NUREG/CR-1150: Severe Accident Risks: An Assessment for Five U.S. Nuclear Power Plants Final Summary Report; U.S. Nuclear Regulatory Commission. Nuclear Regulatory Commission: Rockville, MD, USA, 2005. [Google Scholar]

- U.S. Nuclear Regulatory Commission. Nuclear Regulatory Commission. NUREG/CR-7110: State-of-the-Art Reactor Consequence Analyses Project; Volume 1, Peach Bottom Integrated Analysis; U.S. Nuclear Regulatory Commission: Rockville, MD, USA, 2012. [Google Scholar]

- U.S. Nuclear Regulatory Commission. Nuclear Regulatory Commission. NUREG/CR-7110: State-of-the-Art Reactor Consequence Analyses Project; Volume 2, Surry Integrated Analysis; U.S. Nuclear Regulatory Commission: Rockville, MD, USA, 2012. [Google Scholar]

- Huang, W.; Liu, Z.; Zhang, Y.; Yu, Y.; Xu, Y.; Xu, M.; Zhang, R.; De Dieu, G.J.; Dezhi, D.Y.; Liu, Z. Historical data-driven risk assessment of railway dangerous goods transportation system: Comparisons between entropy weight method and scatter degree method. Reliab. Eng. Syst. Saf. 2021, 205, 107236. [Google Scholar] [CrossRef]

- Hogenboom, S.; Parhizkar, T.; Vinnem, J.E. Temporal decision-making factors in risk analyses of dynamic positioning operations. Reliab. Eng. Syst. Saf. 2021, 207, 107347. [Google Scholar] [CrossRef]

- Lee, J.C.; McCormick, N.J. Risk and Safety Analysis of Nuclear Systems; Wiley-Blackwell: Hoboken, NJ, USA, 2011. [Google Scholar] [CrossRef]

- Madden, M.G.; Nolan, P.J. Generation of Fault Trees from Simulated Incipient Fault Case Data; WIT Press: Southampton, UK, 2001. [Google Scholar]

- Bieber, P.; Castel, C.; Seguin, C. Combination of fault tree analysis and model checking for safety assessment of complex system. In B13 Ninth International Conference on Artificial Intelligence in Engineering. In Proceedings of the 1994 Fourth European Dependable Computing Conference, Toulouse, France, 23–25 October 2002; Springer: Berlin/Heidelberg, Germany, 2002; pp. 19–31. [Google Scholar] [CrossRef]

- Kaiser, B.; Liggesmeyer, P.; Mäckel, O. A new component concept for fault trees. In Proceedings of the 33 8th Australian Workshop on Safety Critical Systems and Software, Canberra, Australia, 9–10 October 2003; pp. 37–46. [Google Scholar]

- Bozzano, M.; Villafiorita, A. Improving system reliability via model checking: The FSAP/NuSMV-SA safety analysis platform. In Proceedings of the 22nd International Conference, SAFECOMP 2003, Edinburgh, UK, 23–26 September 2003; Lecture Notes in Computer Science. 2003; Volume 2788, pp. 49–62. [Google Scholar] [CrossRef]

- Rae, A.; Lindsay, P. A behaviour-based method for fault tree generation. In Proceedings of the 22nd International System Safety Conference, Providence, RI, USA, 2–6 August 2004. [Google Scholar]

- Ortmeier, F.; Schellhorn, G. Formal fault tree analysis–Practical experiences. Electron. Notes Theor. Comput. 2007, 185, 139–151. [Google Scholar] [CrossRef]

- Tajarrod, F.; Latif-Shabgahi, G. A novel methodology for synthesis of fault trees from MATLAB-Simulink model. World Acad. Sci. Eng. Technol. 2008, 17, 1256–1262. [Google Scholar] [CrossRef]

- Prosvirnova, T.; Rauzy, A. Guarded Transition Systems: Pivot Modelling Formalism for Safety Analysis; Actes du Congrès Lambda-Mu: Saclay, France, 2012; Volume 18. [Google Scholar]

- Rauzy, A. Guarded transition systems: A new states/events formalism for reliability studies. J. Risk Reliab. 2008, 222, 295–505. [Google Scholar] [CrossRef]

- Nejad, H.S.; Parhizkar, T.; Mosleh, A. Automatic generation of event sequence diagrams for guiding simulation based dynamic probabilistic risk assessment (SIMPRA) of complex systems. Reliab. Eng. Syst. Saf. 2022, 222, 108416. [Google Scholar] [CrossRef]

- Friedenthal, S.; Moore, A.; Steiner, R. A Practical Guide to SysML: The Systems Modeling Language; Morgan Kaufmann: Cambridge, MA, USA, 2008. [Google Scholar]

- Hecht, M.; Dimpfl, E.; Pinchak, J. Automated Generation of Failure Modes and Effects Analysis from SysML Models. In Proceedings of the 2014 IEEE International Symposium on Software Reliability Engineering Workshops, Naples, Italy, 3–6 November 2014; pp. 62–65. [Google Scholar] [CrossRef]

- Rauzy, A. Mode Automata and Their Compilation into Fault Trees. Reliab. Eng. Syst. Saf. 2002, 78, 1–12. [Google Scholar] [CrossRef]

- Munk, P.; Nordmann, A. Model-based safety assessment with SysML and component fault trees: Application and lessons learned. Softw. Syst. Model. 2020, 19, 889–910. [Google Scholar] [CrossRef]

- MBSE Wiki. Standards Development Organization. Available online: https://www.omgwiki.org/MBSE/doku.php (accessed on 31 January 2022).

- Mbenni, F.; Nguyen, N.; Choley, J.Y. Automatic fault tree generation from SysML system models. In Proceedings of the 2014 IEEE/ASME International Conference on Advanced Intelligent Mechatronics, Besacon, France, 8–11 July 2014; pp. 715–720. [Google Scholar] [CrossRef]

- Mandelli, D.; Alfonsi, A.; Aldemir, T. Automatic generation of event trees and fault trees: A model-based approach. Nucl. Technol. 2023, 209, 1653–1665. [Google Scholar] [CrossRef]

- Kaiser, B.; Soden, M.; Heuermann, N. A UAV Case Study on an MBSE Workflow with Integrated Modular Safety and Reliability Analysis. In Proceedings of the 2024 Annual Reliability and Maintainability Symposium (RAMS), Albuquerque, NM, USA, 22–25 January 2024; IEEE: New York, NY, USA, 2024; pp. 1–7. [Google Scholar] [CrossRef]

- Lanzani, I.; Scattolini, R.; Zio, E.; Cimatti, A.; Bozzano, M.; Tonetta, S. Two formal methodologies of Model-Based Safety Assessment for Fault Tree Analysis. In Proceedings of the 2023 7th International Conference on System Reliability and Safety (ICSRS), Bologna, Italy, 22–24 November 2023; pp. 376–383. [Google Scholar] [CrossRef]

- SAE International. ARP 4754A: Guidelines for Development of Civil Aircraft and Systems; SAE International: Warrendale, PA, USA, 2010. [Google Scholar]

- SAE International. ARP 4761: Guidelines and Methods for Conducting the Safety Assessment Process on Civil Airborne Systems and Equipment; SAE International: Warrendale, PA, USA, 1996. [Google Scholar]

- Kumar, R.; Stoelinga, M. Quantitative Security and Safety Analysis with Attack-Fault Trees. In Proceedings of the 2017 IEEE 18th International Symposium on High Assurance Systems Engineering (HASE), Singapore, 12–14 January 2017; IEEE: New York, NY, USA, 2017; pp. 25–32. [Google Scholar] [CrossRef]

- ISO 26262; Road Vehicles—Functional Safety. International Organization for Standardization (ISO): Geneva, Switzerland, 2018.

- Roth, M.; Wolf, M.; Lindemann, U. Integrated matrix-based fault tree generation and evaluation. Procedia Comput. Sci. 2015, 44, 299–608. [Google Scholar] [CrossRef]

- Prosvirnova, T.; Batteux, M.; Brameret, P.A.; Cherfi, A.; Friedlhuber, T.; Roussel, J.M.; Rauzy, A. The AltaRica 3.0 project for model-based safety assessment. Proc. IEEE Int. Conf. Indust. Inform. IFAC Proc. Vol. 2013, 46, 127–132. [Google Scholar] [CrossRef]

- Boiteau, M.; Dutuit, Y.; Rauzy, A.; Signoret, J.-P. The AltaRica data-flow language in use: Assessment of production availability of a multistate system. Reliab. Eng. Syst. Saf. 2006, 91, 747–755. [Google Scholar] [CrossRef]

- Xu, W.H.; Zhang, Y.P. A fault tree auto-modeling method based on avionics system architecture model. Comput. Eng. Sci. 2017, 39, 2269–2277. [Google Scholar]

- Zhenzhou, Z.; Luyi, L.; Shufang, S. Importance Analysis Theory and Solution Methods for Uncertainty Structural Systems; Science Press: Beijing, China, 2015. [Google Scholar]

- Pattipati, K.R.; Alexandridis, M.G. Application of heuristic search and information theory to sequential fault diagnosis. In IEEE Transactions on Systems, Man, and Cybernetics; IEEE: New York, NY, USA, 1990; Volume 20, pp. 872–887. [Google Scholar] [CrossRef]

- Guo, J.; Sun, J.T.; Liu, Y.T. The Application of ESA to Airborne Missile. Aero Weapon 2005, 4, 23–26. [Google Scholar]

- Zhang, J.; Chen, D.; Gao, P. A divide-and-conquer information entropy algorithm for dependency matrix processing. IEEE Access 2023, 11, 121306–121313. [Google Scholar] [CrossRef]

- Shi, J.Y. Testability Design Analysis and Verification; National Defense Industry Press: Washington, DC, USA, 2011. [Google Scholar]

- GJB/Z299C-2006; Reliability Prediction Handbook Electronic Equipment. Standardization Administration of China: Beijing, China, 2006.

| Code | Description | ||

|---|---|---|---|

| X1 | Unexpected function of EFI due to lightning stroke | 0.0001 | −2.632 × 10−7 |

| X2 | D3 accidentally outputs high voltage due to lightning stroke | 0.0001 | 0 |

| X3 | Static switch 2 fault causes constant continuity between source and drain | 7.35 | −9.678 × 10−10 |

| X4 | Dynamic switch fault causes constant continuity between source and drain | 7.35 | −9.678 × 10−10 |

| X5 | Static switch 1 fault causes constant continuity between source and drain | 7.35 | 0 |

| X6 | Photocoupler 6 in controller 1 is damaged, resulting in constant continuity of emitter and collector | 0.801 | 0 |

| X7 | Chip fault in controller 1 causes IO_8_E7 constant output low | 0.801 | 0 |

| X8 | Chip program error in controller 1 causes IO_8_E7 constant output low | 0.801 | 0 |

| X9 | High output due to photocoupler 2 fault in interface circuit 1 | 1.77 | 0 |

| X10 | Abnormal Order_1 signal | 0.058 | 0 |

| X11 | Abnormal External_power_supply | 0.058 | 0 |

| X12 | High output due to photocoupler 4 fault in interface circuit 3 | 1.77 | 0 |

| X13 | Abnormal Order_3 signal | 0.058 | 0 |

| X14 | Constant high output caused by operational amplifier 1 fault | 1.593 | 0 |

| X15 | Constant low output caused by operational amplifier 2 fault | 1.593 | 0 |

| X16 | R31 short circuit | 0.058 | 0 |

| X17 | R32 open circuit | 0.058 | 0 |

| X18 | R29 short circuit | 0.058 | 0 |

| X19 | R30 open circuit | 0.058 | 0 |

| X20 | High and low of port IO_8_B9 output dynamic change caused by chip program error in controller 2 | 0.801 | 0 |

| X21 | Driver chip 2 fault in controller 2 causes out port to output differential signal | 0.801 | −1.709 × 10−10 |

| X22 | Chip fault in controller 2 causes IO_8_B6 constant output low | 0.801 | −1.709 × 10−10 |

| X23 | Chip program error in controller 2 causes IO_8_B6 constant output low | 0.801 | −1.709 × 10−10 |

| X24 | High output due to photocoupler 3 fault in interface circuit 2 | 1.77 | −2.710 × 10−10 |

| X25 | Abnormal Order_2 signal | 0.058 | 0 |

| X26 | Abnormal feedback signal of the initiation circuit | 0.0001 | 0 |

| X27 | Driver chip 2 fault in controller 2 causes out port to output differential signal | 0.801 | −1.709 × 10−10 |

| X28 | Chip fault in controller 2 causes IO_8_B6 constant output low | 0.801 | −1.709 × 10−10 |

| X29 | Chip program error in controller 2 causes IO_8_B6 constant output low | 0.801 | −1.709 × 10−10 |

| X30 | High output due to photocoupler 5 fault in interface circuit 4 | 1.77 | −2.710 × 10−10 |

| X31 | Abnormal Order_4 signal | 0.058 | 0 |

| Module Code | Safety-Related Faults | Safety-Related Signal Features |

|---|---|---|

| M7 | Unexpected function of EFI due to lightning stroke | S6 |

| M8 | High output due to photocoupler 3 fault in interface circuit 2 | S5 |

| M10 | High output due to photocoupler 5 fault in interface circuit 4 | S8 |

| M11 | Driver chip 2 fault in controller 2 causes out port to output differential signal | S8 |

| Chip fault in controller 2 causes IO_8_B6 constant output low | S8 | |

| Chip program error in controller 2 causes IO_8_B6 constant output low | S8 | |

| M12 | Dynamic switch fault causes constant continuity between source and drain | S5,S7 |

| M13 | Static switch 2 fault causes constant continuity between source and drain | S4,S7 |

| T1 | T2 | T3 | T4 | T5 | T6 | T7 | T8 | T9 | T10 | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S1 | S2 | S1 | S3 | S1 | S5 | S1 | S4 | S1 | S2 | S6 | S1 | S8 | S1 | S5 | S6 | S7 | S9 | |||

| F1GN | M1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0.74 |

| F2GN | M2 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0.38 |

| F3GN | M3 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.62 |

| F4GN | M4 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.40 |

| F5GN | M5 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.95 |

| F5FN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0.82 | |

| F6GN | M6 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.18 |

| F6FN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0.56 | |

| F7GN | M7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.12 |

| F7GS | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.0001 | |

| F7FN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0.79 | |

| F8GN | M8 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.23 |

| F8GS | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1.8 | |

| F9GN | M9 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.52 |

| F10GN | M10 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0.96 |

| F10 GS | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1.8 | |

| F11GN | M11 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0.45 |

| F11 GS1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0.80 | |

| F11 GS2 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0.80 | |

| F11 GS3 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0.80 | |

| F11FN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0.81 | |

| F12GN | M12 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.16 |

| F12GS | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 7.3 | |

| F12FN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0.59 | |

| F13GN | M13 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.12 |

| F13GS | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 7.3 | |

| F13FN | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0.33 | |

| F14GN | M14 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0.38 |

| T1 | T2 | T3 | T4 | T5 | T6 | T7 | T8 | T9 | T10 | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S1 | S2 | S1 | S3 | S1 | S5 | S1 | S4 | S1 | S2 | S6 | S1 | S8 | S1 | S5 | S6 | S7 | S9 | ||

| F1G | M1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| F2G | M2 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| F3G | M3 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F4G | M4 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F5G | M5 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F5F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| F6G | M6 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F6F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |

| F7G | M7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F7F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |

| F8G | M8 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F9G | M9 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F10G | M10 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| F11G | M11 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| F11F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | |

| F12G | M12 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F12F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| F13G | M13 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| F13F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| F14G | M14 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| Test | Description (A Means the Analogue Quantity, D Means the Digital Quantity) | Corresponding Signal Feature Number |

|---|---|---|

| T1 | Test the logic power supply signal level (A) | 1 |

| T2 | Test the power supply signal level (A) | 2 |

| T3 | Test the control signal level output from controller 1 to static switch 2 (D) | 1,3 |

| T4 | Test the control signal level output from controller 2 to dynamic switch (D) | 1,5 |

| T5 | Test the control signal level output from controller 2 to static switch 2 (D) | 1,4 |

| T6 | Test the output voltage value of the boost circuit module (A) | 1,2,6 |

| T7 | Test the control signal level output from controller 2 to the initiation circuit (D) | 1,8 |

| T8 | Test the feedback voltage signal of high-voltage feedback module (D) | 1,5,6 |

| T9 | Test the dynamic switch output signal (voltage or current can be used) (A) | 7 |

| T10 | Test the output signal (voltage or current) of static switch 2 (A) | 9 |

| Object | Processing Method | Test Sequence | FDR | ETC | TASAP | TASAN |

|---|---|---|---|---|---|---|

| S-D | WFD | T8→T7→T9→T10→T4 | 100% | 2.6376 | 0.2386 | 0.7143 |

| IG | T9→T7→T6→T4→T10 | 100% | 1.8395 | 0.5584 | 0.6071 | |

| D | WFD | T8→T9→T10→T7 | 100% | 1.9199 | 0.1306 | 0.45 |

| IG | T8→T9→T7→T10 | 100% | 1.8427 | 0.1385 | 0.40 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, J.; Chen, D.; Gao, P.; Wang, Z.; Zhang, J. Research on Modeling Method of Testability Design Based on Static Automatic Fault Tree. Processes 2024, 12, 2826. https://doi.org/10.3390/pr12122826

Zhang J, Chen D, Gao P, Wang Z, Zhang J. Research on Modeling Method of Testability Design Based on Static Automatic Fault Tree. Processes. 2024; 12(12):2826. https://doi.org/10.3390/pr12122826

Chicago/Turabian StyleZhang, Jiashuo, Derong Chen, Peng Gao, Zepeng Wang, and Jingang Zhang. 2024. "Research on Modeling Method of Testability Design Based on Static Automatic Fault Tree" Processes 12, no. 12: 2826. https://doi.org/10.3390/pr12122826

APA StyleZhang, J., Chen, D., Gao, P., Wang, Z., & Zhang, J. (2024). Research on Modeling Method of Testability Design Based on Static Automatic Fault Tree. Processes, 12(12), 2826. https://doi.org/10.3390/pr12122826