On Model Order Reduction of Interconnect Circuit Network: A Fast and Accurate Method

Abstract

1. Introduction

- (1)

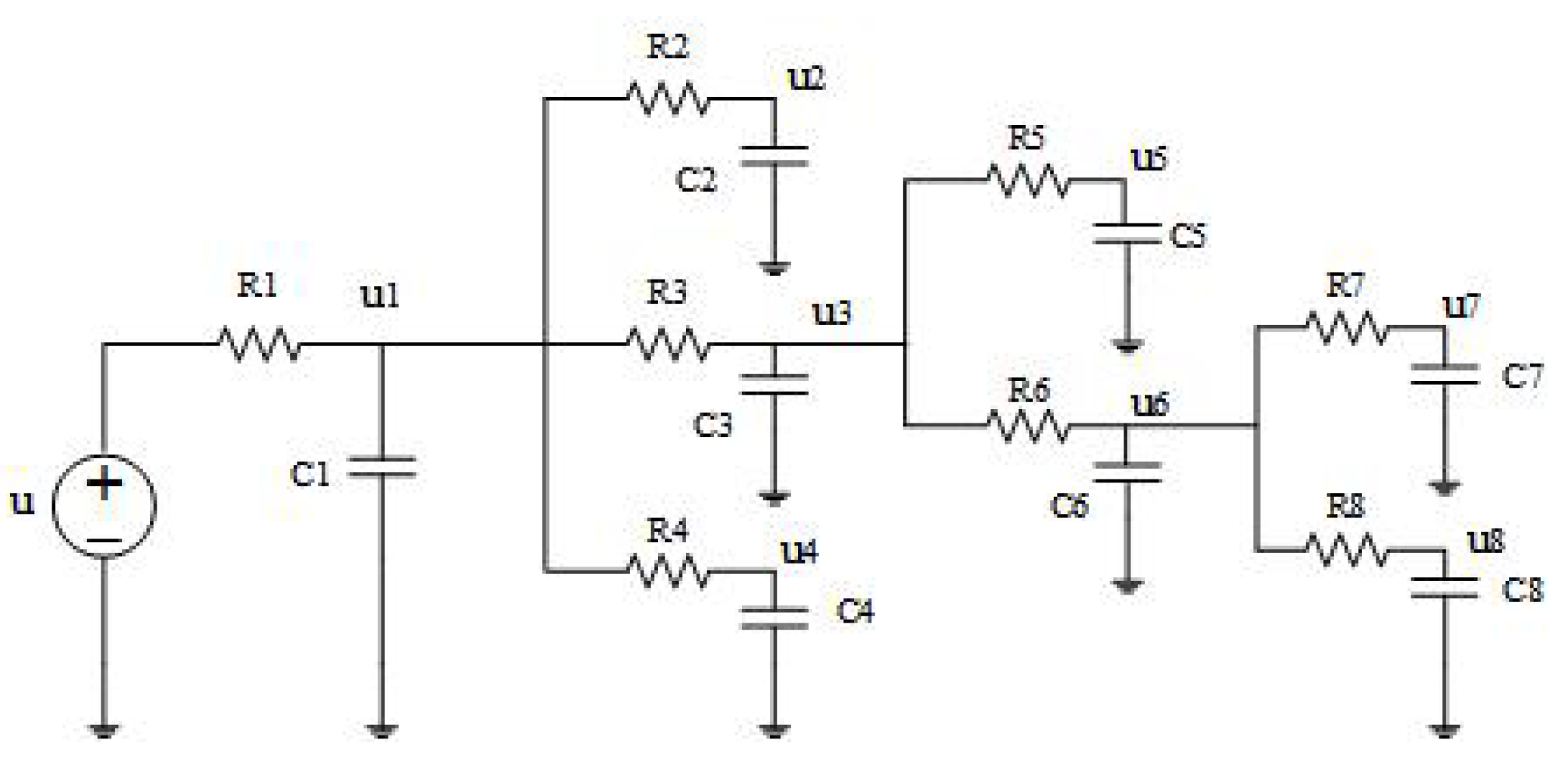

- We extract the interconnected parts of the circuit into a network system composed of some different linear elements such as resistors and capacitors.

- (2)

- We establish the first-order ordinary differential equations of the network system by using state variable analysis.

- (3)

- By using Taylor series theory, we expand the state variables in the system of differential equations as the sum of the low-order power functions of time t and make the error between the original state variables and the approximately expanded state variables converge.

- (4)

- We use the norm theory to square the error of each state variable and then integrate it. By limiting the error convergence to the integral interval, the model has a certain error margin. Finally, we take the partial derivative of each of the coefficients and let each of the partial derivatives be equal to zero to minimize the squared error. Both theoretical derivation and simulation results prove that the reduced order model proposed in this paper converges to a certain error limit and can transform the process of solving large ordinary differential equations into the process of solving linear equations. In the time-domain model order reduction, the proposed method is fairly effective in establishing a balance between time-saving and reduced order accuracy.

2. Interconnect Circuit Model

3. Order Reduction Method of Approximation Model

3.1. One-Dimensional Convergence Derivation

3.2. Two-Dimensional Convergence Derivation

3.3. N-Dimensional Convergent Derivation

4. Simulation Results and Analysis

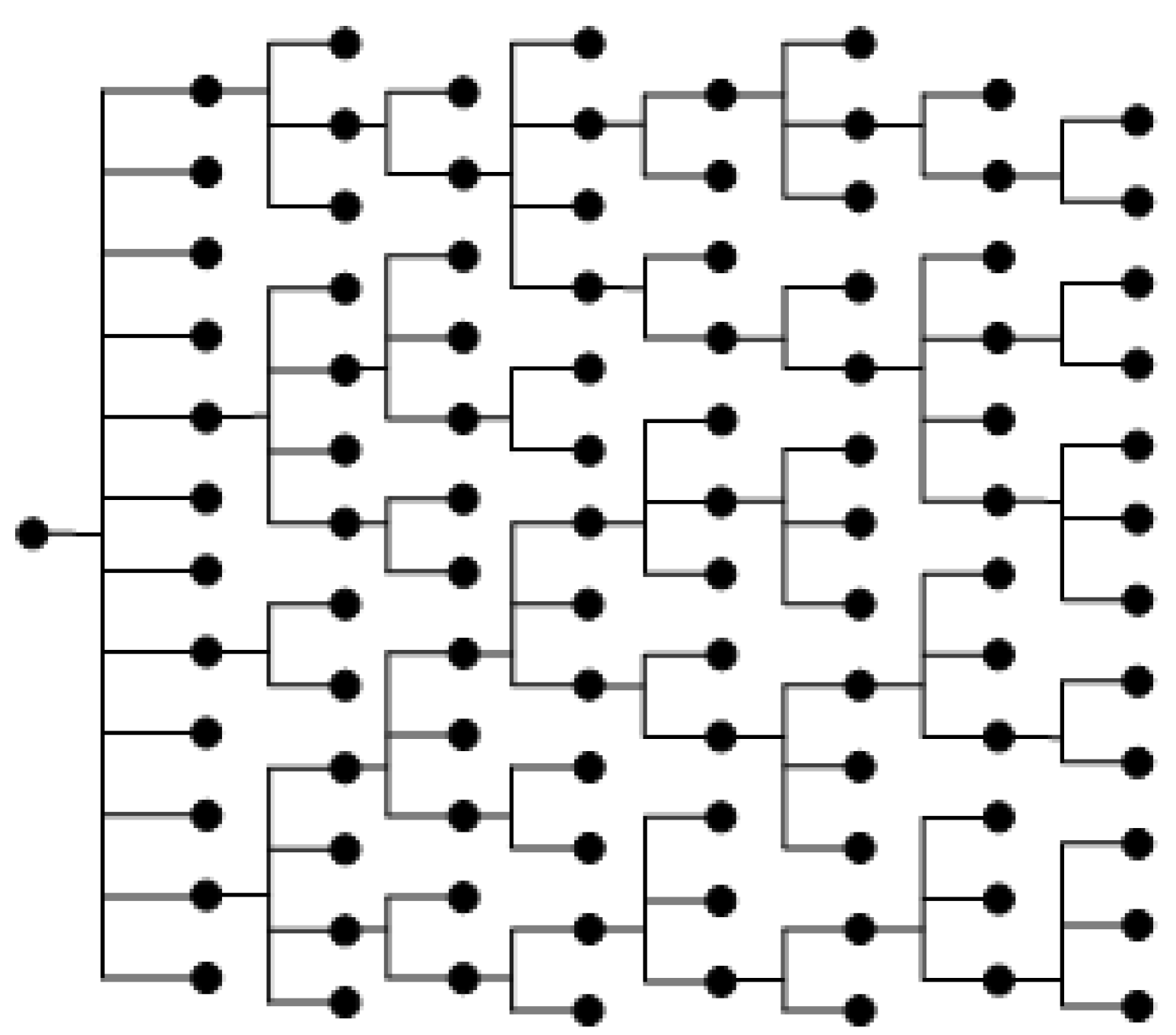

4.1. Simple Model Implementation

- (1)

- The objective function to be optimized can be understood as the adaptability of a biological population to the environment.

- (2)

- The optimization variable corresponds to the individual of the biological population.

- (3)

- Analogize the problem that needs to be optimized with the evolution of a population.

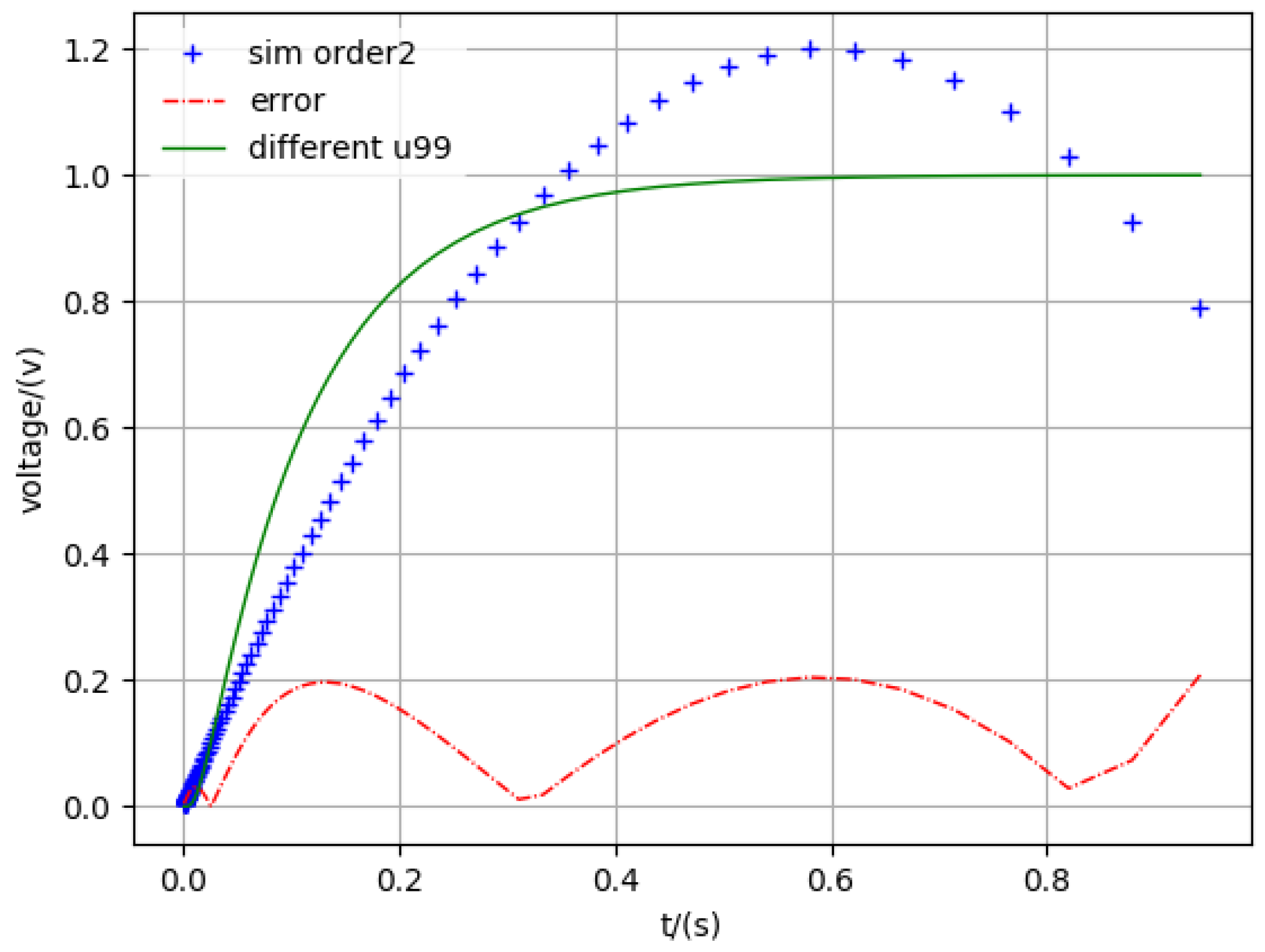

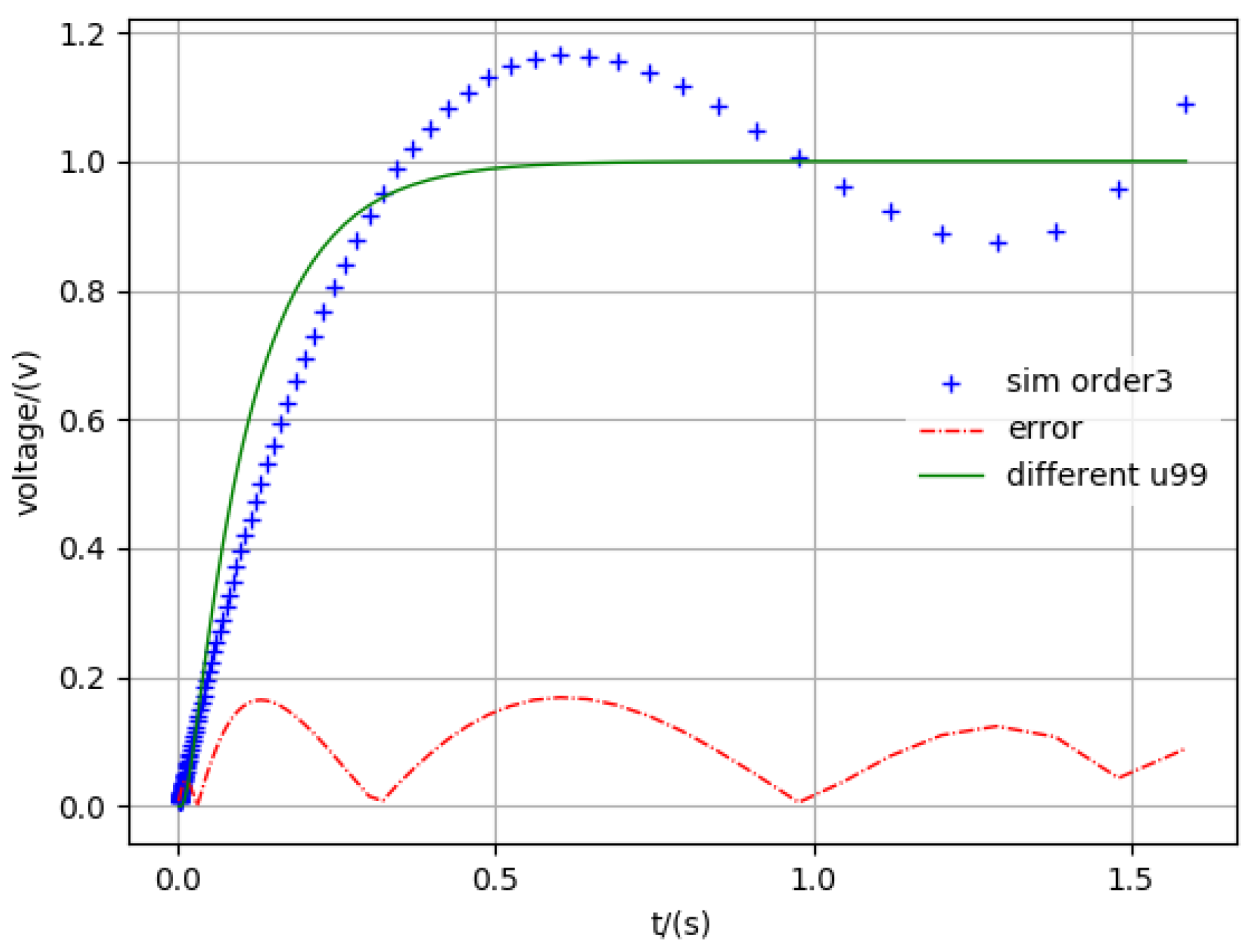

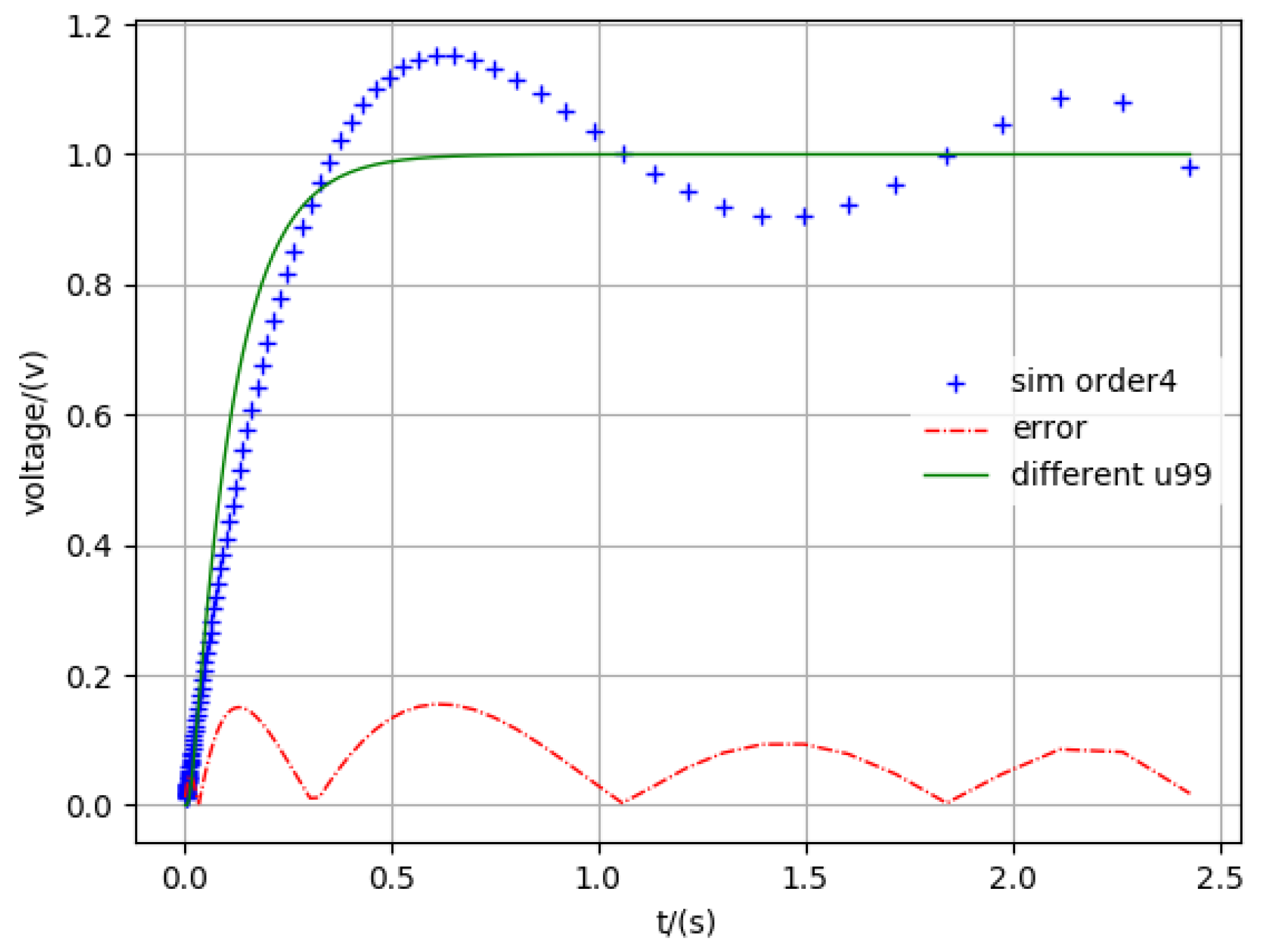

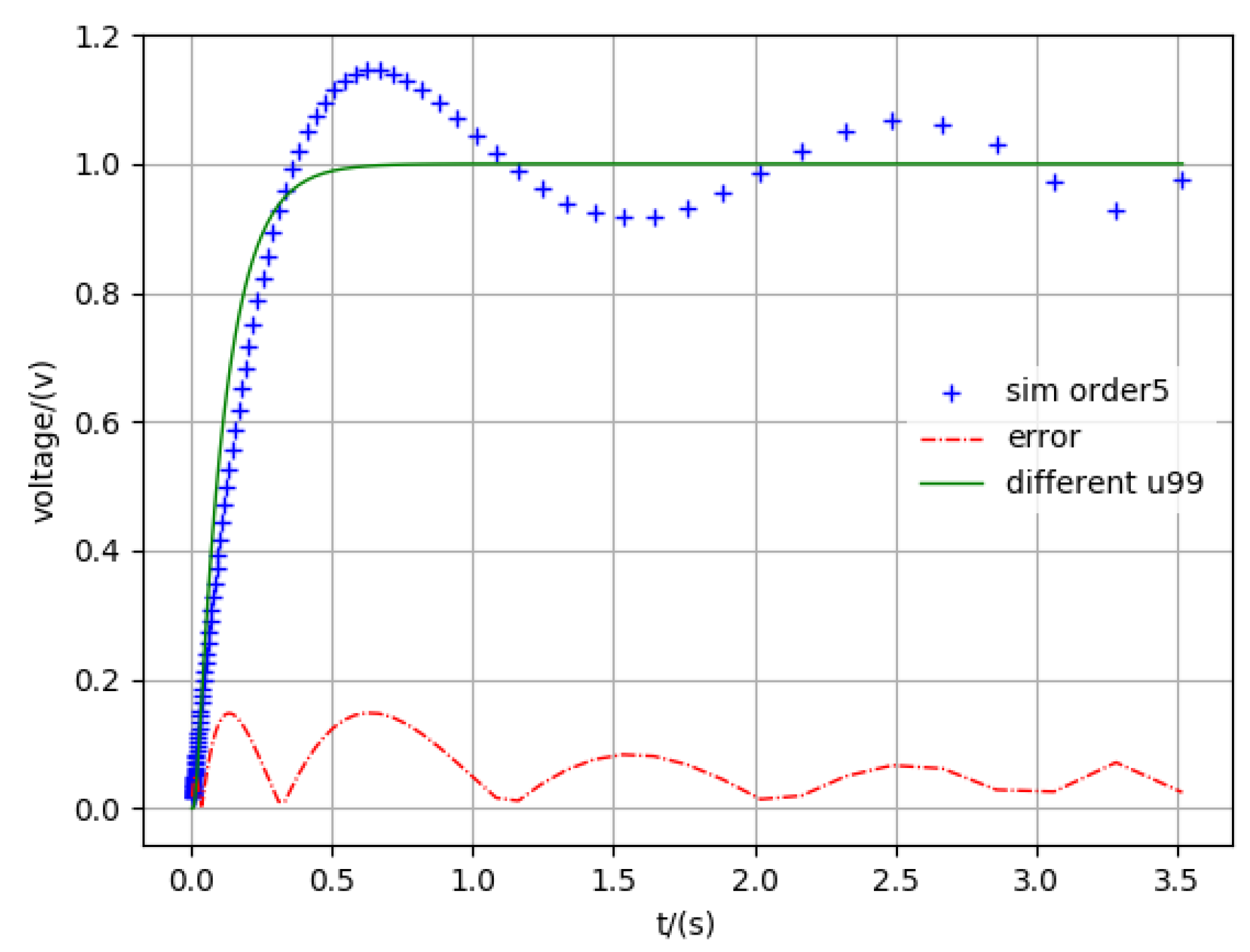

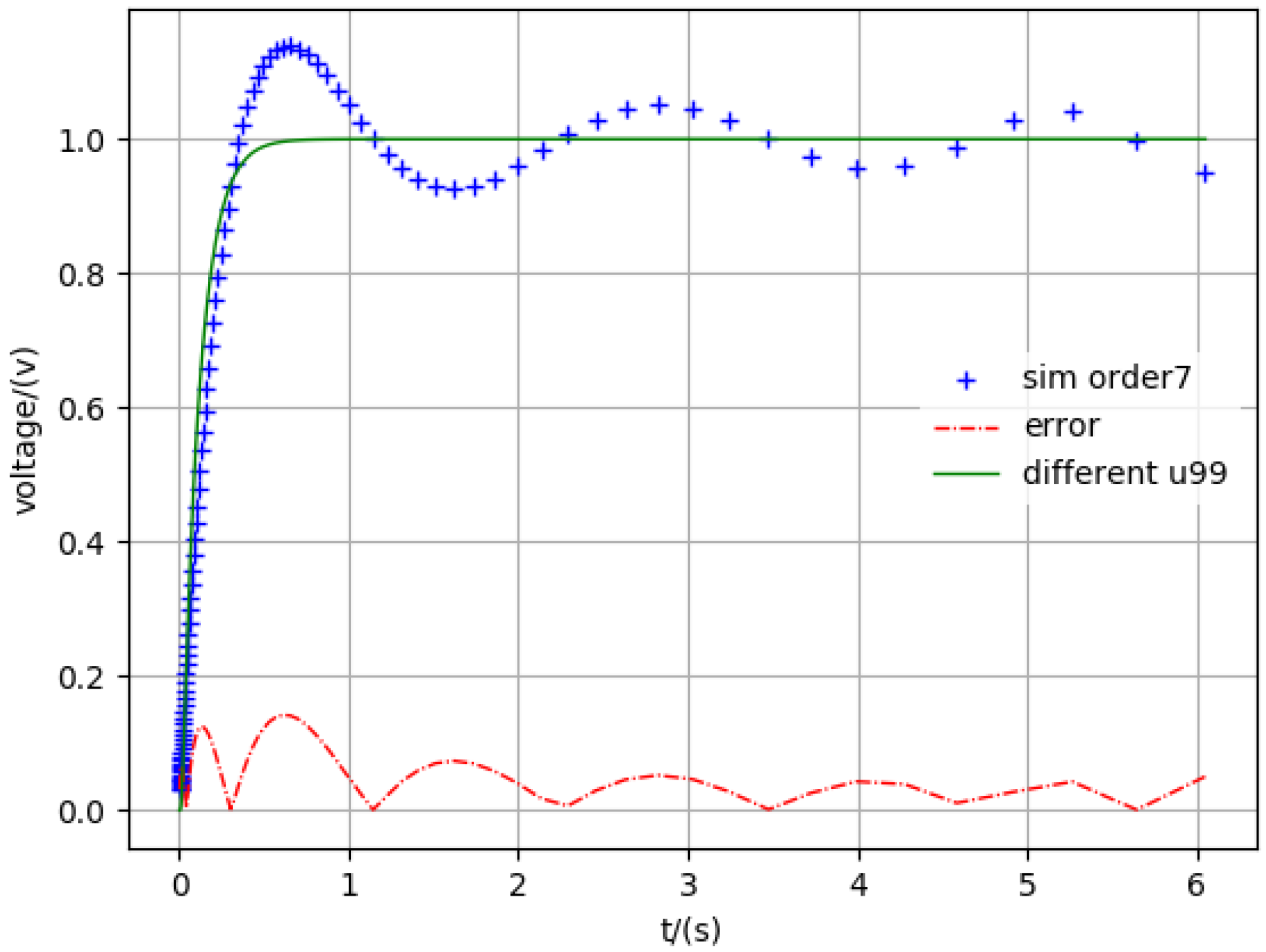

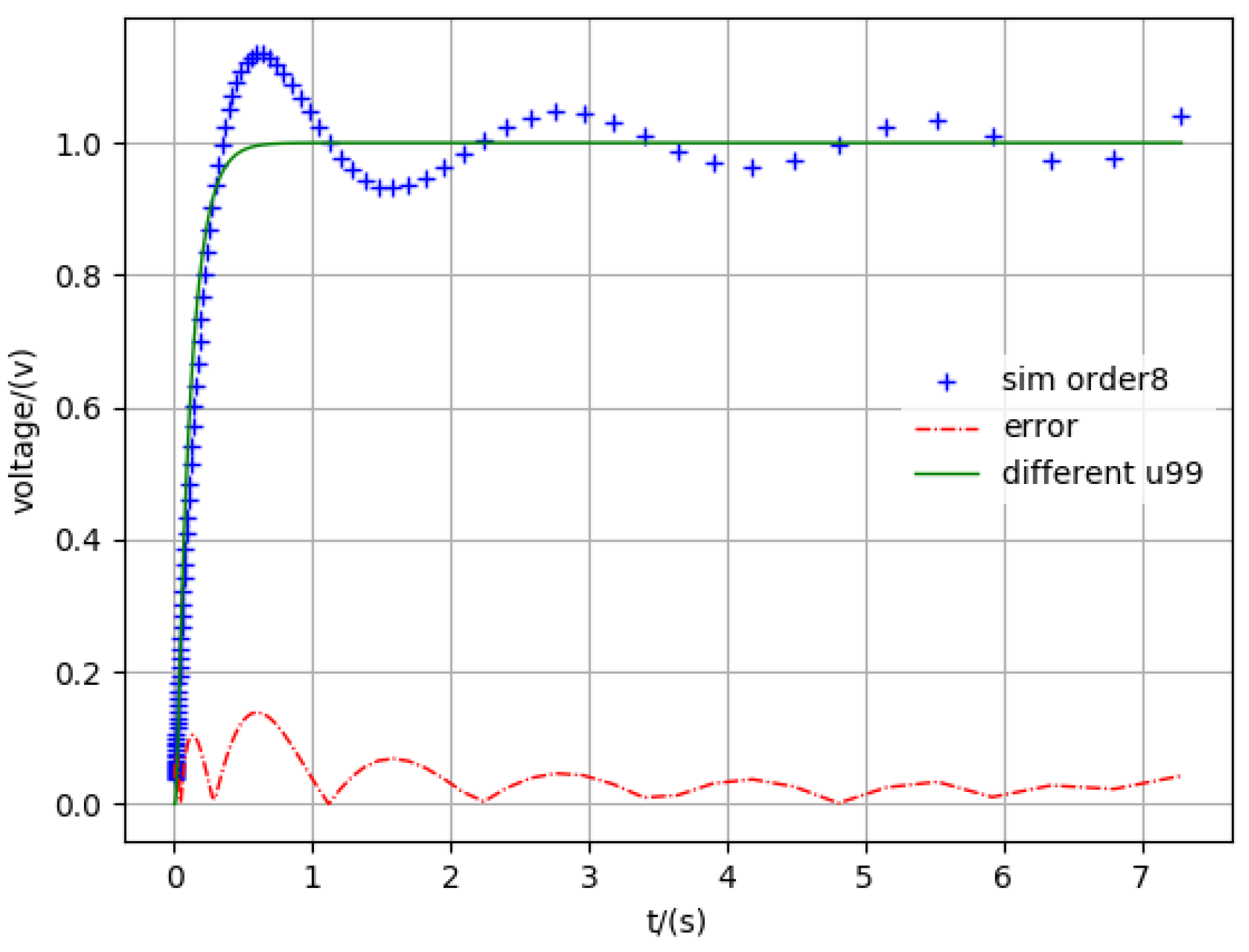

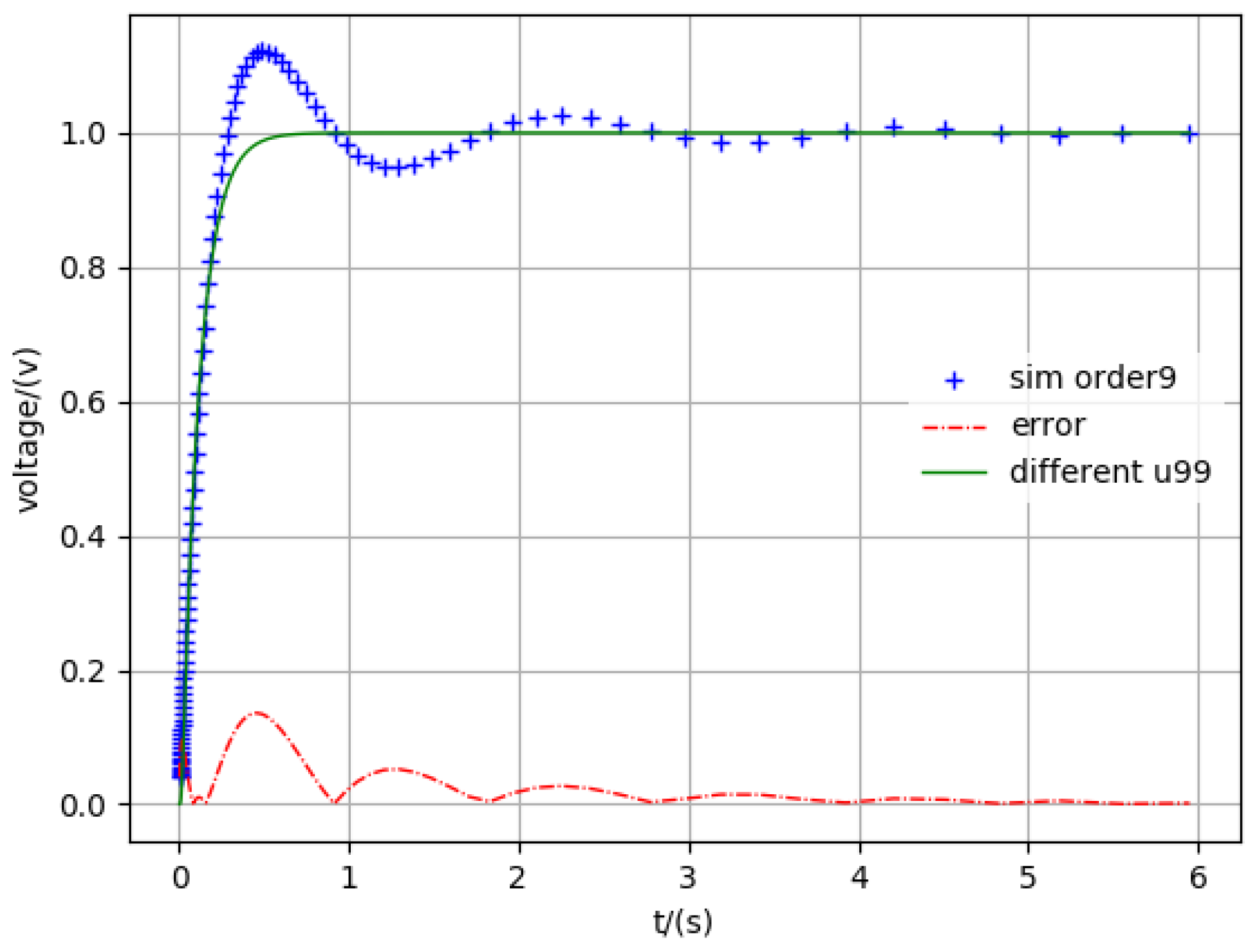

4.2. Model Example and Simulation Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lithotechsolutions. Current Status of the Integrated Circuit Industry in China. J. Microelectron. Manuf. 2018, 1, 1–8. [Google Scholar]

- Telescu, M.; Tanguy, N.; Bréhonnet, P.; Vilbé, P.; Calvez, L.C.; Huret, F. Model-order reduction of VLSI circuit interconnects via a Laguerre representation. In Proceedings of the 9th IEEE Workshop on Signal Propagation on Interconnects, Garmisch-Partenkirchen, Germany, 10–13 May 2005; pp. 107–110. [Google Scholar]

- Achar, R.; Nakhla, M.S. Simulation of high-speed interconnects. Proc. IEEE 2001, 89, 693–728. [Google Scholar] [CrossRef]

- Li, P.; Shi, W. Model order reduction of linear networks with massive ports via frequency-dependent port packing. In Proceedings of the 43rd Annual Design Automation Conference, San Francisco, CA, USA, 24–28 July 2006; pp. 267–272. [Google Scholar]

- Scarciotti, G. Steady-State Matching and Model Reduction for Systems of Differential–Algebraic Equations. IEEE Trans. Autom. Control. 2017, 62, 5372–5379. [Google Scholar] [CrossRef]

- Fujimoto, K. On subspace balanced realization and model order reduction for nonlinear interconnected systems. In Proceedings of the 2012 IEEE 51st IEEE Conference on Decision and Control (CDC), Maui, HI, USA, 10–13 December 2012; pp. 4314–4319. [Google Scholar]

- Yan, B.; Zhou, L.; Tan, S.X.D.; Chen, J.; McGaughy, B. DeMOR: Decentralized model order reduction of linear networks with massive ports. In Proceedings of the 45th annual Design Automation Conference, Anaheim, CA, USA, 9–13 June 2008; pp. 409–414. [Google Scholar]

- Tan, S.X.D.; Yan, B.; Wang, H. Recent Advance in Non-Krylov Subspace Model Order Reduction of Interconnect Circuits. Tsinghua Sci. Technol. 2010, 15, 151–168. [Google Scholar] [CrossRef]

- Cairone, F.; Gagliano, S.; Carbone, D.C.; Recca, G.; Bucolo, M. Micro-optofluidic switch realized by 3D printing technology. Microfluid. Nanofluidics 2016, 20, 61. [Google Scholar] [CrossRef]

- Anandan, P.; Gagliano, S.; Bucolo, M. Computational models in microfluidic bubble logic. Microfluid. Nanofluidics 2015, 18, 305–321. [Google Scholar] [CrossRef]

- Gunupudi, P.; Khazaka, R.; Dounavis, A.; Nakhla, M.; Achar, R. Global multi-level reduction technique for nonlinear simulation of high-speed interconnect circuits. In Proceedings of the IEEE 10th Topical Meeting on Electrical Performance of Electronic Packaging (Cat. No. 01TH8565), Cambridge, MA, USA, 22–31 October 2001; pp. 259–262. [Google Scholar]

- Papachristodoulou, A.; Chang, Y.C.; August, E.; Anderson, J. Structured model reduction for dynamical networked systems. In Proceedings of the 49th IEEE Conference on Decision and Control (CDC), Atlanta, GA, USA, 15–17 December 2010; pp. 2670–2675. [Google Scholar]

- Choroszucha, R.B.; Sun, J. Empirical Riccati covariance matrices for closed-loop model order reduction of nonlinear systems by balanced truncation. In Proceedings of the 2017 American Control Conference (ACC), Seattle, WA, USA, 24–26 May 2017; pp. 3476–3482. [Google Scholar]

- Xu, Q.; Li, Z.F.; Mazumder, P.; Mao, J.F. Time-domain modeling of high-speed interconnects by modified method of characteristics. IEEE Trans. Microw. Theory Tech. 2000, 48, 323–327. [Google Scholar]

- Ding, W.; Liu, F.; Liu, S.; Wang, G. Localization of critical frequency for simulation of high-speed interconnects. In Proceedings of the 2014 15th International Conference on Electronic Packaging Technology, Chengdu, China, 12–15 August 2014; pp. 1512–1515. [Google Scholar]

- Sun, Y.; Dong, J.; Pu, T.; Yu, T. Reduction of power system dynamic model using Krylov subspace method. In Proceedings of the 2014 International Conference on Power System Technology, Chengdu, China, 20–22 October 2014; pp. 343–348. [Google Scholar]

- Zhu, Z.; Geng, G.; Jiang, Q. Power System Dynamic Model Reduction Based on Extended Krylov Subspace Method. IEEE Trans. Power Syst. 2016, 31, 4483–4494. [Google Scholar] [CrossRef]

- Chaniotis, D.; Pai, M. Model reduction in power systems using Krylov subspace methods. IEEE Trans. Power Syst. 2005, 20, 888–894. [Google Scholar] [CrossRef]

- Frangos, M.; Jaimoukha, I. Adaptive rational Krylov algorithms for model reduction. In Proceedings of the 2007 European Control Conference (ECC), Kos, Greece, 2–5 July 2007; pp. 4179–4186. [Google Scholar]

- Chen, Y.; Balakrishnan, V.; Koh, C.K.; Roy, K. Model Reduction in the Time-Domain Using Laguerre Polynomials and Krylov Methods. In Proceedings of the 2002 Design, Automation and Test in Europe Conference and Exhibition, Paris, France, 4–8 March 2002; pp. 931–935. [Google Scholar]

- Jiang, G.; Liu, H.; Yang, K.; Gao, X. A fast reduced-order model for radial integral boundary element method based on proper orthogonal decomposition in nonlinear transient heat conduction problems. Comput. Methods Appl. Mech. Eng. 2020, 368, 113190. [Google Scholar] [CrossRef]

- Panjapornpon, C.; Kajornrungsilp, I.; Rochpuang, C. Input/output linearizing controller with Taylor series expansion for a nonminimum phase process by hardware-in-the-loop approach. Asia-Pac. J. Chem. Eng. 2020, 15, e2440. [Google Scholar] [CrossRef]

- Hsinchu. Synopsys and UMC Collaborate to Accelerate Development of a 14nm Finfet Process. Electron. World 2013, 119, 50. [Google Scholar]

- Geng, X.; Xiao, Z.; Ji, L.; Zhao, Y.; Wang, F. A Gaussian elimination based fast endmember extraction algorithm for hyperspectral imagery. ISPRS J. Photogramm. Remote Sens. 2013, 79, 211–218. [Google Scholar] [CrossRef]

| Reduced Order | Time (s) | Average Error Margin |

|---|---|---|

| 2 | 0.038567 s | 0.208194 |

| 3 | 0.090528 s | 0.168275 |

| 4 | 0.172582 s | 0.154782 |

| 5 | 0.252482 s | 0.148063 |

| 6 | 0.358407 s | 0.144806 |

| 7 | 0.463968 s | 0.142452 |

| 8 | 0.637438 s | 0.141266 |

| 9 | 0.739400 s | 0.140600 |

| exact solution | 12.165914 s | 0 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, X.; Fan, S.; Dai, M.-Z.; Zhang, C. On Model Order Reduction of Interconnect Circuit Network: A Fast and Accurate Method. Mathematics 2021, 9, 1248. https://doi.org/10.3390/math9111248

Wang X, Fan S, Dai M-Z, Zhang C. On Model Order Reduction of Interconnect Circuit Network: A Fast and Accurate Method. Mathematics. 2021; 9(11):1248. https://doi.org/10.3390/math9111248

Chicago/Turabian StyleWang, Xinsheng, Shimin Fan, Ming-Zhe Dai, and Chengxi Zhang. 2021. "On Model Order Reduction of Interconnect Circuit Network: A Fast and Accurate Method" Mathematics 9, no. 11: 1248. https://doi.org/10.3390/math9111248

APA StyleWang, X., Fan, S., Dai, M.-Z., & Zhang, C. (2021). On Model Order Reduction of Interconnect Circuit Network: A Fast and Accurate Method. Mathematics, 9(11), 1248. https://doi.org/10.3390/math9111248