A Review of High-Performance Computing Methods for Power Flow Analysis

Abstract

1. Introduction

2. Background

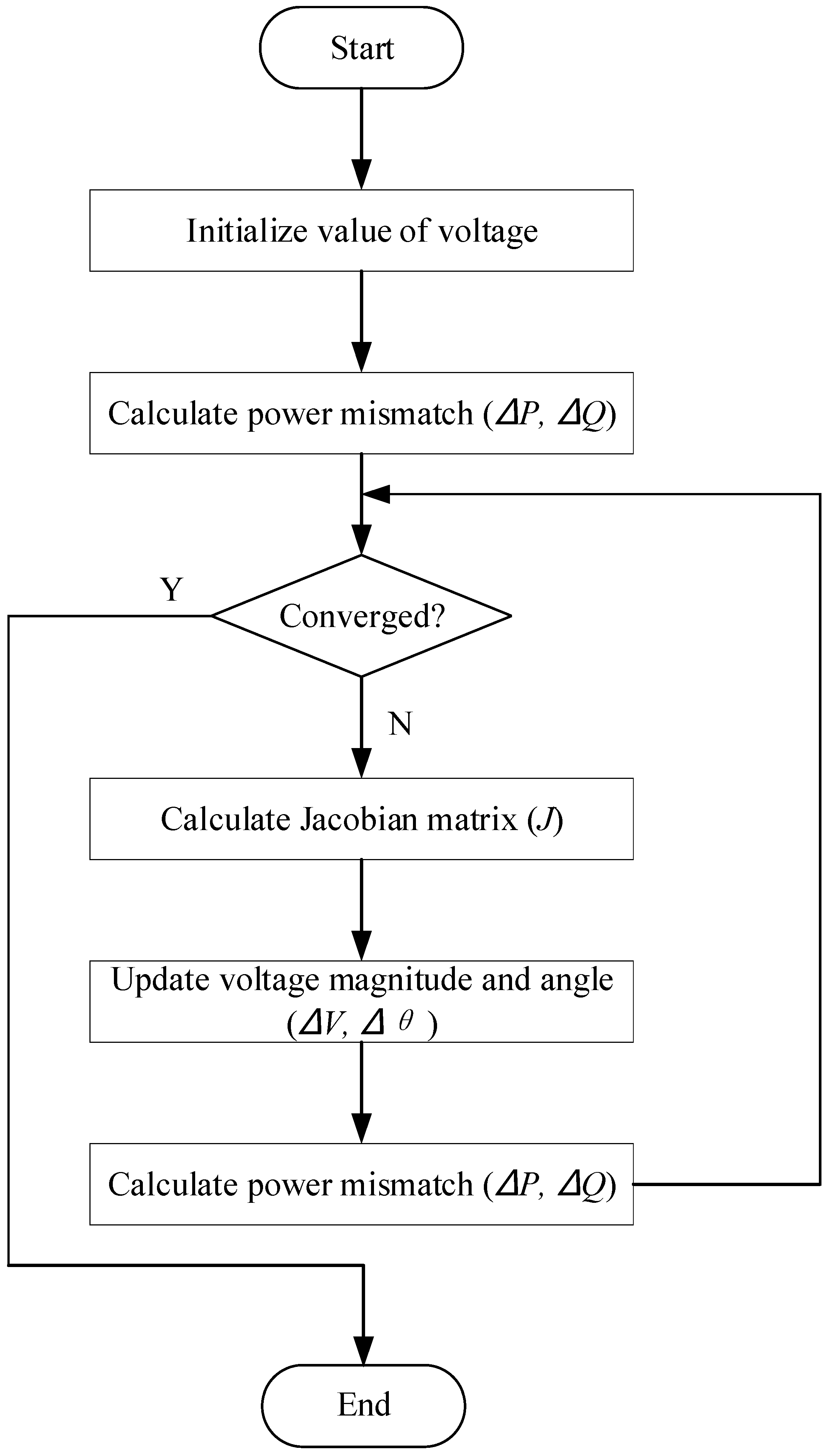

2.1. PF Model and Analysis

2.2. PF Methods

2.3. Linear System Solver

2.3.1. LU Factorization

- Elimination: Factorize matrix A into lower and upper triangular matrices L and U and obtain permutation matrix P, which can be expressed as follows:

- 2.

- Forward: Generate the intermediate vector y depending on P and L in Equation (17), and they can be written as:

- 3.

- Backward: solving a triangular system, based on the vector y of Equation (18), as follows:

2.3.2. QR Factorization

2.3.3. Iterative Method

3. Parallel Method and Performance

3.1. The Multi-Core CPU Architecture

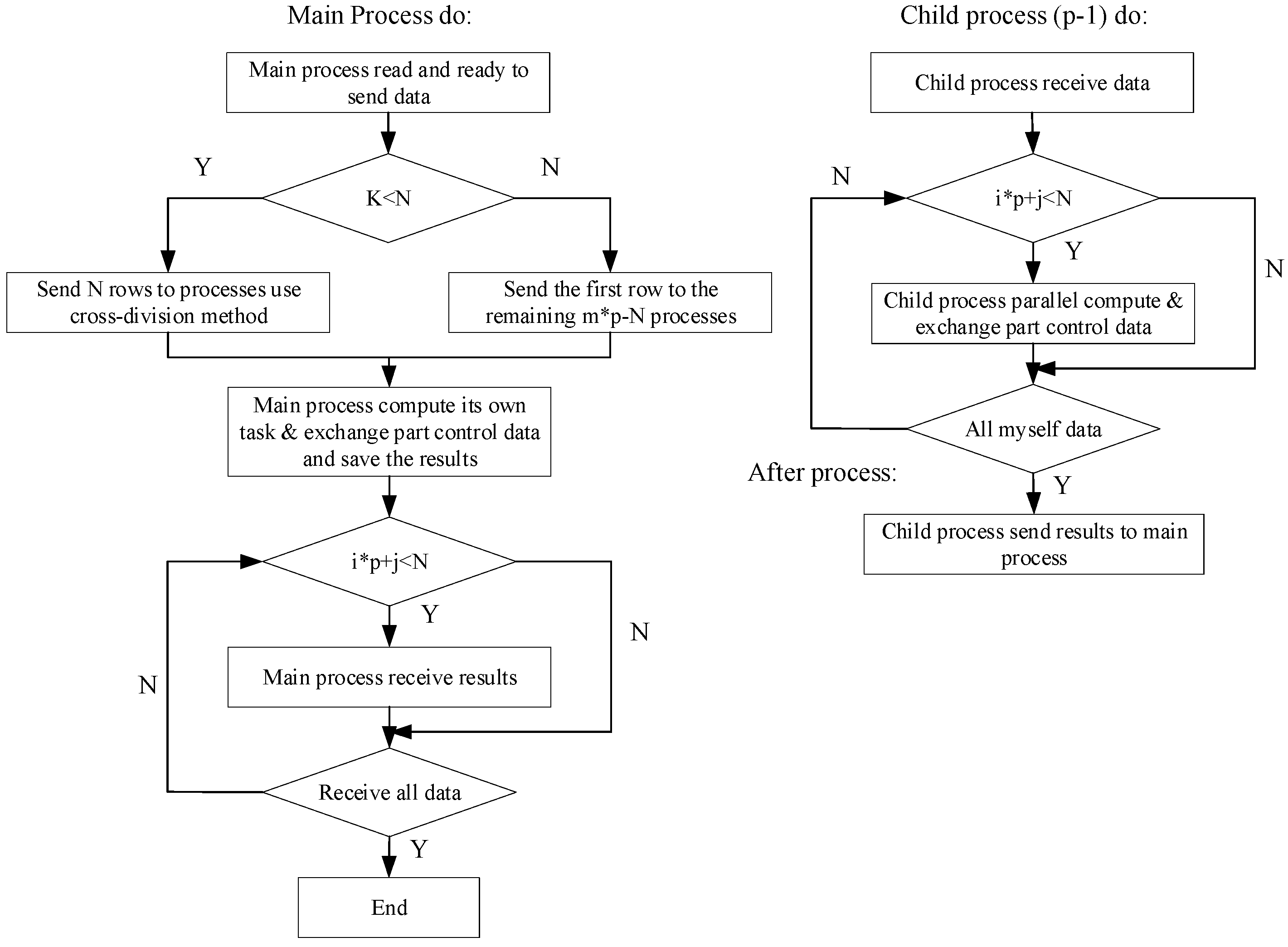

3.2. The Multi-Core Parallel in PF Studies

| Algorithm 1 Solving dx = J\F [65] |

| 1 #pragma omp parallel for schedule (guided, chunk_size) … |

| 2 for k = 0, 1, …, n{ |

| 3 for j = k + 1, k + 2, …, n { |

| 4 x = Jik/Jkk; |

| 5 for I = k, k + 1, …, n |

| 6 Jji = Jji − x × Jki; |

| 7 Jik = x; |

| 8 } |

| 9 } |

| 10 #paragma omp parallel for schedule (guided, chunk_size) |

| 11 for m = 0, 1, …, n { |

| 12 d[m] = 1.0; |

| 13 if(m! = 0) d[m − 1] = 0; |

| 14 for i = 0, 1, …, n { |

| 15 sum = 0.0; |

| 16 for j = 0, 1, …, i − 1 sum = sum + Jij × yj; |

| 17 yi = di − sum; |

| 18 } |

| 19 for i = n, n − 1, …, 0 { |

| 20 sum = 0.0; |

| 21 for j = i + 1, i + 2, …, n sum = sum + Jij × dxjm; |

| 22 dxjm = (yi − sum)/Jii; |

| 23 } |

| 24 } |

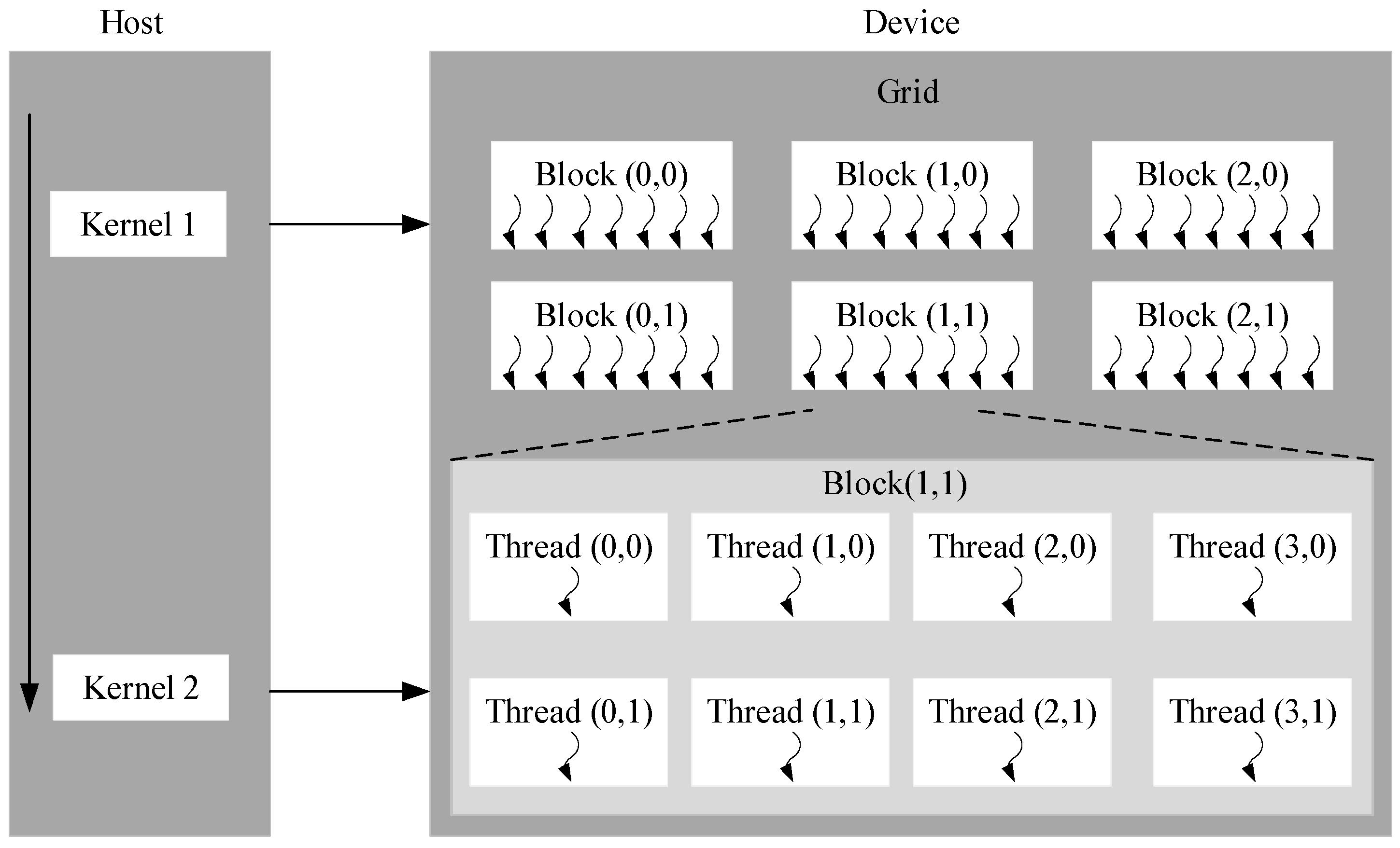

3.3. The GPU Architecture

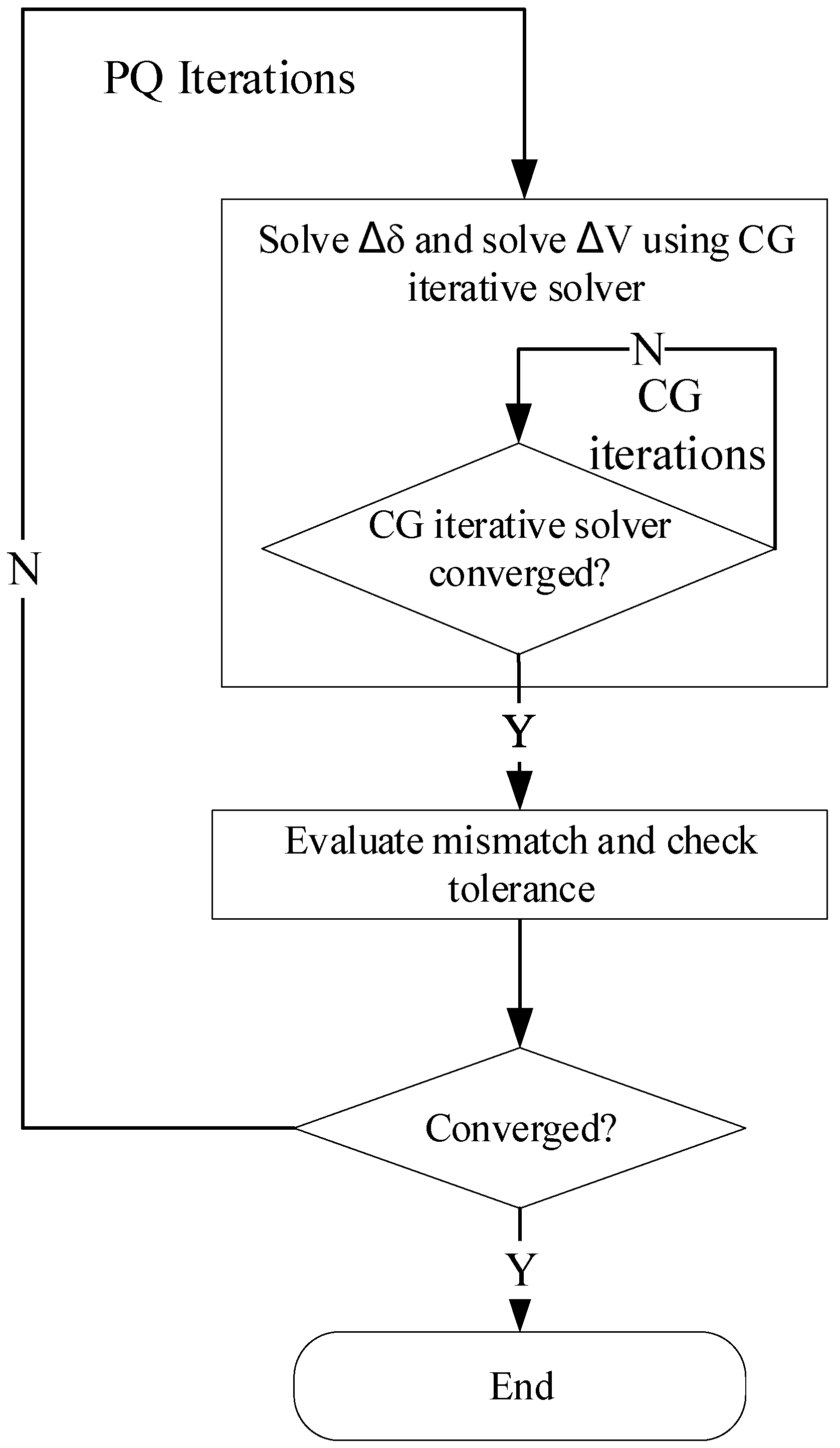

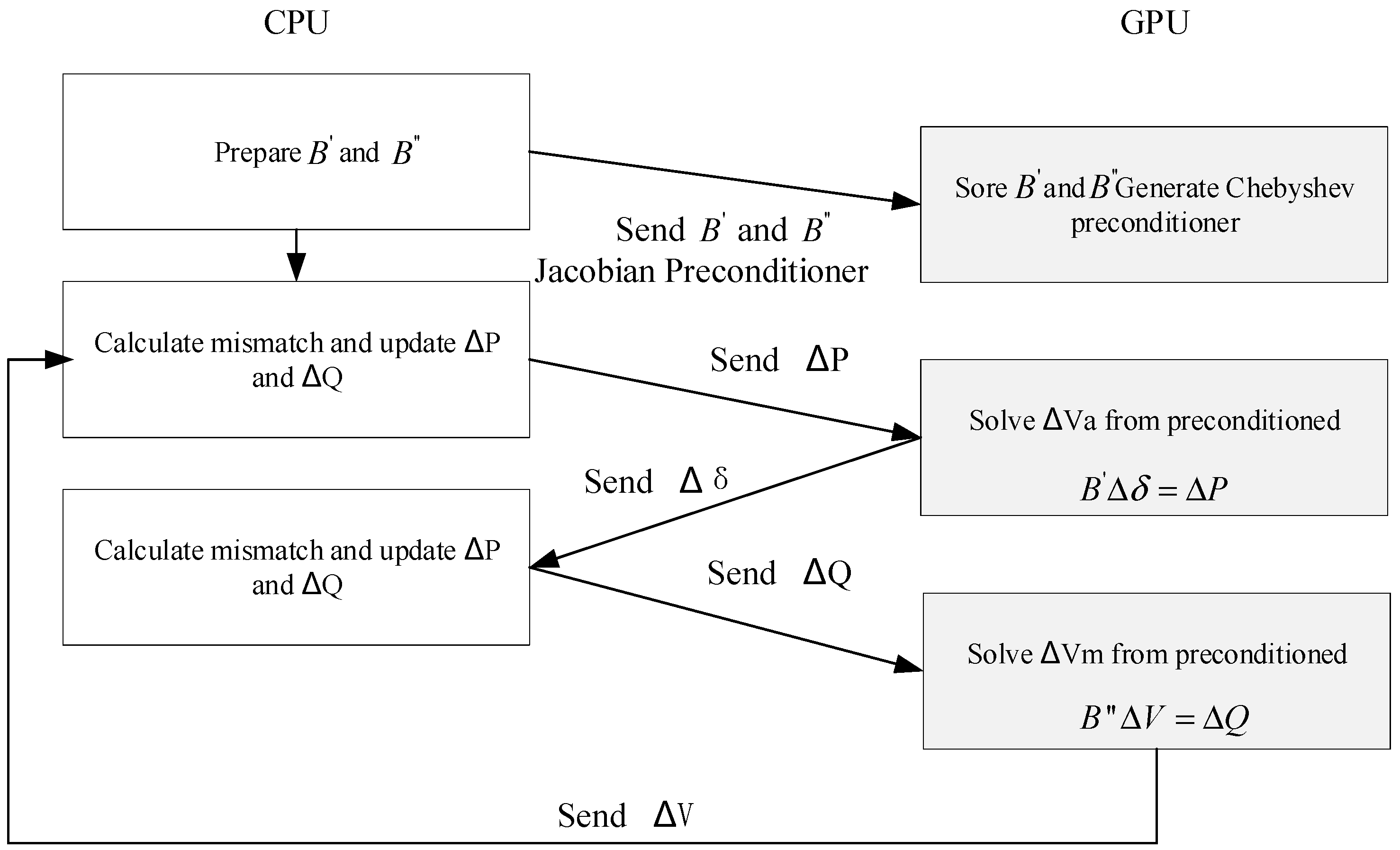

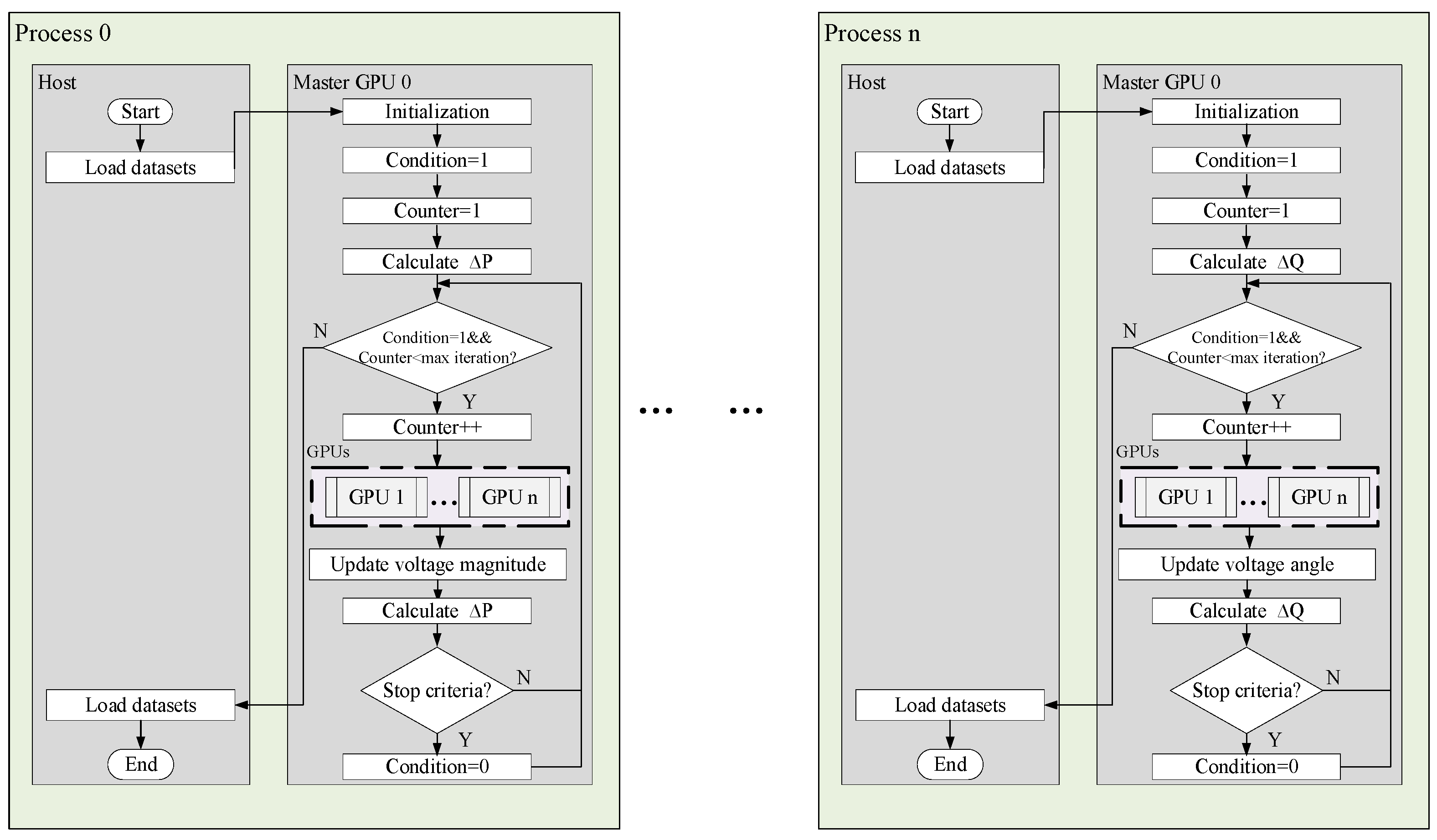

3.4. The Hybrid CPU-GPU Parallel in PF Studies

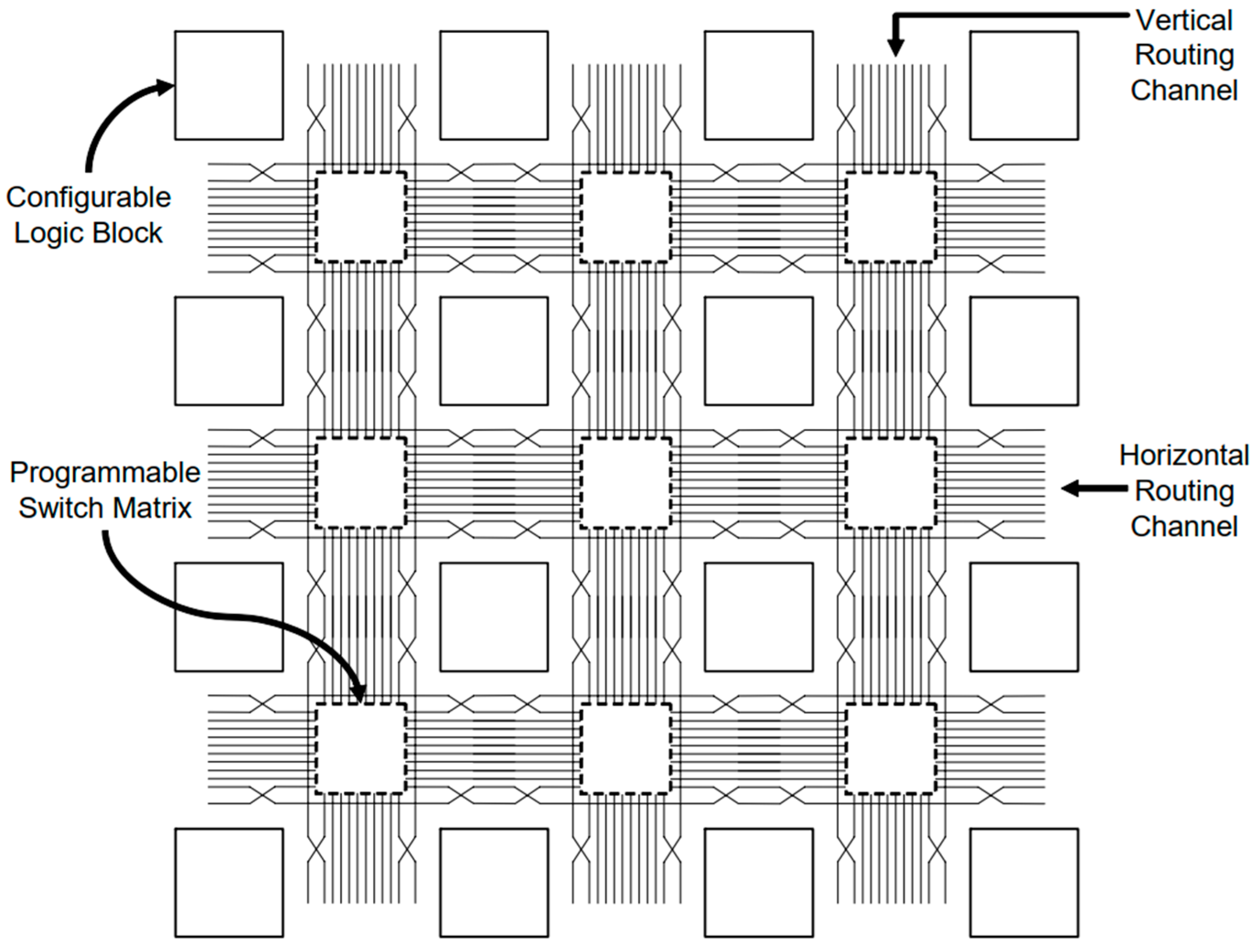

3.5. The FPGA Architecture

3.6. The FPGA Parallel in PF Studies

4. Results and Comparison

- The direct method is usually more robust than the iterative method.

- The direct method of sparse format is suited for small-memory platforms, such as PCs, laptops, and workstations.

- The iterative method performs better on almost all kinds of platforms, but it needs a preconditioner for enhanced stability in PF calculation.

- The direct method of dense format can provide an overall performance improvement for large-scale power systems on large-memory parallel platforms.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yoon, D.-H.; Han, Y. Parallel Power Flow Computation Trends and Applications: A Review Focusing on GPU. Energies 2020, 13, 2147. [Google Scholar] [CrossRef]

- Grainger, J.; Stevenson, W. Power System Analysis; McGraw-Hill: New York, NY, USA, 1999; pp. 329–368. [Google Scholar]

- Wang, M.; Xia, Y.; Chen, Y.; Huang, S. GPU-based power flow analysis with continuous Newton’s method. In Proceedings of the 2017 IEEE Conference on Energy Internet and Energy System Integration (EI2), Beijing, China, 26–28 November 2017; pp. 1–5. [Google Scholar]

- Wang, X.; Song, Y.; Irving, M. Modern Power Systems Analysis; Springer: New York, NY, USA, 2008. [Google Scholar]

- Khairy, M.; Wassal, A.G.; Zahran, M. A survey of architectural approaches for improving GPGPU performance, programmability, and heterogeneity. J. Parallel Distrib. Comput. 2019, 127, 65–88. [Google Scholar] [CrossRef]

- Falcão, D.M. High performance computing in power system applications. In Proceedings of the International Conference on Vector and Parallel Processing, Porto, Portugal, 25–27 September 1996; Springer: Berlin, Germany, 1996; pp. 1–23. [Google Scholar]

- Ramesh, V. On distributed computing for on-line power system applications. Int. J. Electr. Power Energy Syst. 1996, 18, 527–533. [Google Scholar] [CrossRef]

- Baldick, R.; Kim, B.H.; Chase, C.; Luo, Y. A fast distributed implementation of optimal power flow. IEEE Trans. Power Syst. 1999, 14, 858–864. [Google Scholar] [CrossRef]

- Li, F.; Broadwater, R.P. Distributed algorithms with theoretical scalability analysis of radial and looped load flows for power distribution system. Electr. Power Syst. Res. 2003, 65, 169–177. [Google Scholar] [CrossRef]

- Green, R.C.; Wang, L.; Alam, M. High performance for electric power systems: Applications and trends. In Proceedings of the 2011 IEEE Power and Energy Society General Meeting, Detroit, MI, USA, 24–28 July 2011; pp. 1–8. [Google Scholar]

- Saad, Y. Iterative Methods for Sparse Linear Systems, 2nd ed.; PWS: Boston, MA, USA, 2004. [Google Scholar]

- Dag, H.; Semlyen, A. A new preconditioned conjugate gradient power flow. IEEE Trans. Power Syst. 2003, 4, 1248–1255. [Google Scholar] [CrossRef]

- Chen, Y.; Shen, C. A Jacobian-free Newton-GMRES(m) method with adaptive preconditioner and its application for power flow calculations. IEEE Trans. Power Syst. 2006, 21, 1096–1103. [Google Scholar] [CrossRef]

- Flueck, A.J.; Chiang, H.-D. Solving the nonlinear power flow equations with a Newton process and GMRES. IEEE Trans. Power Syst. 1998, 13, 267–273. [Google Scholar] [CrossRef]

- Davis, T.A. Direct Methods for Sparse Linear Systems; SIAM: Philadelphia, PA, USA, 2006. [Google Scholar]

- Singh, J.; Aruni, I. Accelerating Power Flow Studies on Graphics Processing Unit. In Proceedings of the 2010 Annual IEEE India Conference (INDICON), Kolkata, India, 17–19 December 2010; pp. 1–5. [Google Scholar]

- Guo, C.; Jiang, B.; Yuan, H.; Yang, Z.; Wang, L.; Ren, S. Performance Comparison of Parallel Power Flow Solvers on GPU System. In Proceedings of the 2012 IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, Seoul, Republic of Korea, 19–22 August 2012; pp. 232–239. [Google Scholar]

- Li, X.; Li, F.-X.; Clark, J.M. Exploration of multifrontal method with GPU in power flow computation. In Proceedings of the 2013 IEEE Power & Energy Society General Meeting, Vancouver, BC, Canada, 21–25 July 2013; pp. 1–5. [Google Scholar]

- Gopal, A.; Niebur, D.; Venkatasubramanian, S. DC Power Flow Based Contingency Analysis Using Graphics Processing Units. In Proceedings of the 2007 IEEE Lausanne Power Tech, Lausanne, Switzerland, 1–5 July 2007; pp. 731–736. [Google Scholar]

- Su, X.; He, C.; Liu, T.; Wu, L. Full Parallel Power Flow Solution: A GPU-CPU-Based Vectorization Parallelization and Sparse Techniques for Newton-Raphson Implementation. IEEE Trans. Smart Grid 2020, 11, 1833–1844. [Google Scholar] [CrossRef]

- Huang, S.; Dinavahi, V. Performance analysis of GPU-accelerated fast decoupled Power Flow using direct linear solver. In Proceedings of the 2017 IEEE Electrical Power and Energy Conference (EPEC), Saskatoon, SK, Canada, 22–25 October 2017; pp. 1–6. [Google Scholar]

- Schäfer, F.; Braun, M. An efficient open-source implementation to compute the jacobian matrix for the Newton-Raphson Power flow algorithm. In Proceedings of the 2018 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe), Sarajevo, Bosnia and Herzegovina, 21–25 October 2018; pp. 1–6. [Google Scholar]

- Gnanavignesh, R.; Shenoy, U.J. Parallel Sparse LU Factorization of Power Flow Jacobian using GPU. In Proceedings of the TENCON 2019–2019 IEEE Region 10 Conference (TENCON), Kochi, India, 17–20 October 2019; pp. 1857–1862. [Google Scholar]

- Wang, Z.-Q.; Wende, S.; Berg, V.; Braun, M. Fast Parallel Newton-Raphson Power flow Solver for Large Number of System Calculations with CPU and GPU. CoRR 2021, 27, 100483. [Google Scholar] [CrossRef]

- Chen, X.; Wu, W.; Wang, Y.; Yu, H.; Yang, H. An escheduler-Based Data Dependence Analysis and Task Scheduling for Parallel Circuit Simulation. IEEE Trans. Circuits Syst. Ⅱ Express Briefs 2011, 58, 702–706. [Google Scholar] [CrossRef]

- Li, X.; Li, F.; Yuan, H.; Cui, H.; Hu, Q. GPU-Based Fast Decoupled Power Flow with Preconditioned Iterative Solver and Inexact Newton Method. IEEE Trans. Power Syst. 2017, 31, 2695–2703. [Google Scholar] [CrossRef]

- Li, X.; Li, F. GPU-based power flow analysis with Chebyshev Preconditioner and Conjugate gradient method. Elect. Power Syst. Res. 2014, 116, 87–93. [Google Scholar] [CrossRef]

- Li, X.; Li, F. GPU-based two-step preconditioning for conjugate gradient method in power flow. In Proceedings of the 2015 IEEE Power & Energy Society General Meeting, Denver, CO, USA, 26–30 July 2015; pp. 1–5. [Google Scholar]

- Zhou, Y.; He, F.; Hou, N.; Qiu, Y. Parallel ant colony optimization on multi-core SIMD CPUs. Future Gener. Comput. Syst. 2018, 79, 473–487. [Google Scholar] [CrossRef]

- Zhou, Y.; He, F.; Qiu, Y. Dynamic strategy based parallel ant colony optimization on GPUs for TSPs. Sci. China Inf. Sci. 2017, 60, 068102. [Google Scholar] [CrossRef]

- Sooknanan, D.J.; Joshi, A. GPU Computing Using CUDA in the Deployment of Smart Grids. In Proceedings of the 2016 SAI Computing Conference, London, UK, 13–15 July 2016; pp. 1260–1266. [Google Scholar]

- Demmel, J.W.; Eisenstat, S.C.; Gilbert, J.R.; Li, X.S.; Liu, J.W. A supernodal approach to sparse partial pivoting. SIAM J. Matrix Anal. Appl. 1999, 20, 720–755. [Google Scholar] [CrossRef]

- Schenk, O.; Gärtner, K. Solving unsymemetric sparse systems of linear equations with PARDISO. Future Gener. Comput. Syst. 2004, 20, 475–487. [Google Scholar] [CrossRef]

- Christen, M.; Schenk, O.; Burkhart, H. General-purpose Sparse Matrix Building Blocks Using the NVIDIA CUDA Technology Platform. In Proceedings of the First Workshop on General Purpose Processing on Graphics Processing Units, Boston, MA, USA, 4 October 2007; p. 32. [Google Scholar]

- Zeng, L.; Alawneh, S.G.; Arefifar, S.A. GPU-based Sparse Power Flow Studies with Modified Newton’s Method. IEEE Access 2021, 9, 153226–153239. [Google Scholar] [CrossRef]

- Zhou, G.; Feng, Y.-J.; Bo, R.; Zhang, T. GPU-accelerated sparse matrices parallel inversion algorithm for large-scale power systems. Int. J. Electr. Power Energy Syst. 2019, 111, 34–43. [Google Scholar] [CrossRef]

- Wu, J.Q.; Bose, A. Parallel solution of large sparse matrix equations and parallel power flow. IEEE Trans. Power Syst. 1995, 10, 1343–1349. [Google Scholar]

- He, K.; Sheldon, X.-D.T.; Wang, H.; Shi, G. GPU-Accelerated Parallel Sparse LU Factorization Method for Fast Circuit Analysis. IEEE Trans. Very Large-Scale Integr. VLSI Syst. 2016, 24, 1140–1150. [Google Scholar] [CrossRef]

- Peng, S.; Sheldon, X.-D.T. GLU3.0: Fast GPU-based Parallel Sparse LU Factorization for Circuit Simulation. IEEE Des. Test 2020, 37, 78–90. [Google Scholar] [CrossRef]

- Chen, X.; Ren, L.; Wang, Y.; Yang, H. GPU-Accelerated Sparse LU Factorization for Circuit Simulation with Performance Modeling. IEEE Trans. Parallel Distrib. Syst. 2015, 26, 786–795. [Google Scholar] [CrossRef]

- Lee, W.-K.; Achar, R.; Nakhla, M.S. Dynamic GPU Parallel Sparse LU Factorization for Fast Circuit Simulation. IEEE Trans. Very Large-Scale Integr. VLSI Syst. 2018, 26, 2518–2529. [Google Scholar] [CrossRef]

- Gao, J.-Q.; Chen, Q.; He, G.-X. A thread-adaptive sparse approximate inverse preconditioning algorithm on multi-GPUs. Parallel Comput. 2021, 101, 102724. [Google Scholar] [CrossRef]

- Xie, C.-H.; Chen, J.-Y.; Firoz, J.; Li, J.-J.; Song, S.-W.L.; Barker, K.; Raugas, M.; Li, A. Fast and Scalable Sparse Triangular Solver for Multi-GPU Based HPC. In Proceedings of the 50th International Conference on Parallel Processing, Lemont, IL, USA, 9–12 August 2021. [Google Scholar]

- Ma, W.; Hu, Y.; Yuan, W.; Liu, X. Developing a multi-GPU-enabled preconditioned GMRES with inexact triangular solves for block sparse matrices. Math. Probl. Eng. 2021, 2021, 6804723. [Google Scholar] [CrossRef]

- Lin, S.; Xie, Z. A Jacobi_PCG solver for sparse linear systems on multi-GPU cluster. J. Supercomput. 2017, 73, 433–454. [Google Scholar] [CrossRef]

- Ding, N.; Liu, Y.; Williams, S.; Li, X.-Y.S. A Message-Driven, Multi-GPU Parallel Sparse Triangular Solver. In Proceedings of the 2021 SIAM Conference on Applied and Computational Discrete Algorithms (ACDA21), Virtual, 19–21 July 2021; pp. 147–159. [Google Scholar]

- Zeng, L.; Alawneh, S.G.; Arefifar, S.A. Parallel Multi-GPU Implementation of Fast Decoupled Power Flow Solver with Hybrid Architecture. Comput. Clust. 2022. under review. [Google Scholar]

- Glover, J.-D.; Overbye, T.-J.; Sarma, M.-S. Power System Analysis & Design, 6th ed.; Cengage Learning: Boston, MA, USA, 2015; pp. 349–353. [Google Scholar]

- Kundur, P.; Balu, N.J.; Lauby, M.G. Power System Stability and Control; McGraw-hill: New York, NY, USA, 1994; Volume 7. [Google Scholar]

- Stoot, B.; Alsac, O. Fast decoupled load flow. IEEE Trans. Power Appar. Syst. 1974, PAS-93, 859–869. [Google Scholar] [CrossRef]

- Chapra, S.-C. Applied Numerical Methods with MATLAB® for Engineers and Scientists, 3rd ed.; McGraw-Hill: New York, NY, USA, 2012; pp. 260–261. [Google Scholar]

- Zhou, G.; Zhang, X.; Lang, Y.; Bo, R.; Jia, Y.; Lin, J.; Feng, Y. A novel GPU-based strategy for contingency screening of static security analysis. Int. J. Electr. Power Energy Syst. 2016, 83, 33–39. [Google Scholar] [CrossRef]

- Lau, K.; Tylavsky, D.J.; Bose, A. Coarse grain scheduling in parallel triangular factorization and solution of power system matrices. IEEE Trans. Power Syst. 1991, 6, 708–714. [Google Scholar] [CrossRef]

- Amano, M.; Zecevic, A.; Siljak, D. An improved block-parallel Newton method via epsilon decompositions for load-flow calculations. IEEE Trans. Power Syst. 1996, 11, 1519–1527. [Google Scholar] [CrossRef]

- El-Keib, A.; Ding, H.; Maratukulam, D. A parallel load flow algorithm. Electr. Power Syst. Res. 1994, 30, 203–208. [Google Scholar] [CrossRef]

- Fukuyama, Y.; Nakanishi, Y.; Chiang, H.D. Parallel power flow calculation in electric distribution networks. In Proceedings of the 1996 IEEE International Symposium on Circuits and Systems, Circuits and Systems Connecting the World (ISCAS 96), Atlanta, GA, USA, 15 May 1996; Volume 1, pp. 669–672. [Google Scholar]

- Luo, C.; Zhang, K.; Salinas, S.; Li, P. SecFact: Secure Large-scale QR and LU Factorizations. IEEE Trans. Big Data 2021, 7, 796–807. [Google Scholar] [CrossRef]

- Golub, G.H.; Van Loan, C.F. Matrix Computation, 4th ed.; John Hopkins University Press: Baltimore, MD, USA, 2013; pp. 233–255. [Google Scholar]

- Buttari, A.; Langou, J.; Kurzak, J.; Dongarra, J. A class of parallel tiled linear algebra algorithms for multicore architectures. Parallel Comput. 2009, 35, 38–53. [Google Scholar] [CrossRef]

- Gregorio, Q.-O.; Enrique, S.Q.-O.; Robert, A.; Van, D.G.; Field, G.V.-Z.; Ernie, C. Programming matrix algorithms-by-blocks for thread-level parallelism. ACM Trans. Math. Softw. 2009, 36, 1–26. [Google Scholar]

- Zhou, G.; Feng, Y.; Bo, R.; Chien, L.; Zhang, X.; Lang, Y.; Jia, Y.; Chen, Z. GPU-accelerated batch-ACPF solution for N-1 static security analysis. IEEE Trans. Smart Grid. 2017, 8, 1406–1416. [Google Scholar] [CrossRef]

- Garcia, N. Parallel power flow solutions using a biconjugate gradient algorithm and a Newton method: A GPU-based approach. In Proceedings of the Power and Energy Society General Meeting, Providence, RI, USA, 25–29 July 2010; pp. 1–4. [Google Scholar]

- Geer, D. Chip Makers Turn to Multicore Processor. Computer 2005, 38, 11–13. [Google Scholar] [CrossRef]

- David, B.K.; Hwu, W.-M.W. Programming Massively Parallel Processors: A Hands-on Approach, 3rd ed.; Elsevier: Cambridge, MA, USA, 2010; pp. 3–6. [Google Scholar]

- Ahmadi, A.; Jin, S.; Smith, M.C.; Collins, E.R.; Goudarzi, A. Parallel Power Flow based on OpenMP. In Proceedings of the 2018 North American Power Symposium (NAPS), Fargo, ND, USA, 9–11 September 2018; pp. 1–6. [Google Scholar]

- Zimmerman, R.D.; Murillo- Sánchez, C.E.; Thomas, R.J. MATPOWER: Steady-State Operations, Planning and Analysis Tools for Power Systems Research and Education. IEEE Trans. Power Syst. 2011, 26, 12–19. [Google Scholar] [CrossRef]

- Ao, L.; Cheng, B.; Li, F. Research of Power Flow Parallel Computing Based on MPI and P-Q Decomposition Method. In Proceedings of the 2010 International Conference on Electrical and Control Engineering, Tuxtla Gutierrez, Mexico, 25–27 June 2010; pp. 2925–2928. [Google Scholar]

- Zhang, Y.; Owens, J.D. A quantitative performance analysis model for GPU architectures. In Proceedings of the 2011 IEEE 17th International Symposium on High Performance Computer Architecture, San Antonio, TX, USA, 12–16 February 2011; pp. 382–393. [Google Scholar]

- Cook, S. CUDA Programming: A Developer’s Guide to Parallel Computing with GPUs; Morgan Kaufmann: Burlington, MA, USA, 2012; pp. 84–89. [Google Scholar]

- Alvarado, F.L. Computional complexity in power systems. IEEE Trans. Power Appar. Syst. 1976, 95, 1028–1037. [Google Scholar] [CrossRef]

- Zhang, B.; Chen, S. Advanced Power System Network Analysis; Tsinghua University Press: Beijing, China, 1996. [Google Scholar]

- Dagum, L.; Menon, R. Openmp: An industry standard api for shared-memory programmming. IEEE Comput. Sci. Eng. 1998, 5, 46–55. [Google Scholar] [CrossRef]

- Kuon, I.; Tessier, R.; Rose, J. FPGA Architecture: Survey for DC power flow solution using LabVIEW language. AADV Electr. Eng. 2012, 10, 68–74. [Google Scholar]

- Yaseen, A.Y.; Abbood, A.A. Study of Power System Load Flow Using FPGA and LabView. Eng. Technol. J. 2020, 38, 690–697. [Google Scholar] [CrossRef]

- Murach, M.; Nagvajara, P.; Johnson, J.; Nwankpa, C. Optimal power flow utilizing FPGA technology. In Proceedings of the 37th Annual North American Power Symposium, Ames, IA, USA, 23–25 October 2005; pp. 97–101. [Google Scholar]

- Wills, A.; Mills, A.; Ninness, B. FPGA implementation of an interior-point solution for linear model predictive control. IFAC Proc. Vol. 2011, 44, 14527–14532. [Google Scholar] [CrossRef]

- Jerez, J.L.; Constantinides, G.A.; Kerrigan, E.C.; Ling, K.-V. Parallel Mpc for real-time FPGA-based implementation. IFAC Proc. Vol. 2014, 59, 3238–3251. [Google Scholar] [CrossRef]

- Ling, K.V.; Wu, B.F.; Maciejowski, J.M. Embeded model predictive control (MPC) using a FPGA. IFAC Proc. Vol. 2008, 41, 15250–15255. [Google Scholar] [CrossRef]

- Abughalieh, K.M.; Alawneh, S.G. A survey of parallel implementations for model predictive control. IEEE Access. 2019, 7, 34348–34360. [Google Scholar] [CrossRef]

- Mehrotra, S. On the Implemetation of a Primal-Dual Interior Point Method. SIAM J. Optim. 1992, 2, 575–601. [Google Scholar] [CrossRef]

- Wang, X.F.; Ziavras, S.G.; Nwankpa, C.; Johnson, J. Nagvajara Prawat. Parallel Solution of Newton’s Power Flow Equations on Configurable Chips. Electr. Power Energy Syst. 2007, 29, 422–431. [Google Scholar] [CrossRef]

- Wang, X.; Ziavras, S.G. Parallel LU. Factorization of sparse matrices on FPGA-based configurable computing engines. Concurr. Comput. Pract. Exp. 2004, 16, 319–343. [Google Scholar] [CrossRef]

- Wang, X.; Ziavras, S.G. Parallel direct solution of linear equations on FPGA-based machines. In Proceedings of the Seventieth IEEE International Parallel and Distributed Processing Symposium IPDPS2003 (Eleventh IEEE International Workshop on Parallel and Distributed Real-Time Systems), Nice, France, 22–26 April 2003. [Google Scholar]

| References | Method | Speedup | Matrix Format | Hardware Platform |

|---|---|---|---|---|

| [65] | Direct method | 2.0× (MATPOWER counterpart) | Dense | CPU: Intel Core i5-2400 RAM: 12GB |

| [67] | Direct method | 3.0× (CPU counterpart) | Dense | HPC cluster self-built RAM: not available |

| [26] | Iterative method | 2.86× (MATPOWER counterpart) | Sparse | CPU: Intel Xeon E5607 GPU: NVIDIA Tesla M2070 RAM: 24GB |

| [27] | Iterative method | 4× (MATPOWER counterpart) | Sparse | CPU: Intel Xeon E5607 GPU: NVIDIA Tesla M2070 RAM: 24GB |

| [28] | Iterative method | 8× (MATPOWER counterpart) | Sparse | CPU: Intel Xeon E5607 GPU: NVIDIA Tesla M2070 RAM: 24GB |

| [16] | Direct method | 10×–40× (CPU counterpart) | Dense | CPU: Intel i7-4500U GPU: NVIDIA GeForce GT745 RAM: not available |

| [31] | Direct method | 7× (CPU counterpart) | Dense | CPU: Intel Xeon Quad GPU: NVIDIA TESLA C1006 RAM: 8GB |

| [21] | Direct method | 4.16× (MATPOWER counterpart) | Sparse | CPU: Intel Xeon E5-2620 GPU: NVIDIA Ge-Force Titan RAM: 32GB |

| [35] | Direct method | 2.68× (CPU counterpart) | Sparse | CPU: Intel i9 GPU: NVIDIA RTX400 RAM: 16GB |

| [24] | Direct method | 100× (PandaPower counter) | Sparse | CPU: Intel i7-8700k GPU: NVIDIA GTX 1080 GPU: NVIDIA GTX 1080 RAM: 32GB |

| [47] | Direct method | 9×–33× (Single GPU counterpart) | Dense | CPU: Intel Xeon GPU: NVIDIA Tesla V100 (4 nodes) RAM: 32GB |

| [75] | Direct method | 3× (CPU counterpart) | Sparse | FPGA RAM: not available |

| [81] | Direct method | 7× (EP20KE1500 counterpart) | Sparse | ES2S180 RAM: 9,383,040 bits |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alawneh, S.G.; Zeng, L.; Arefifar, S.A. A Review of High-Performance Computing Methods for Power Flow Analysis. Mathematics 2023, 11, 2461. https://doi.org/10.3390/math11112461

Alawneh SG, Zeng L, Arefifar SA. A Review of High-Performance Computing Methods for Power Flow Analysis. Mathematics. 2023; 11(11):2461. https://doi.org/10.3390/math11112461

Chicago/Turabian StyleAlawneh, Shadi G., Lei Zeng, and Seyed Ali Arefifar. 2023. "A Review of High-Performance Computing Methods for Power Flow Analysis" Mathematics 11, no. 11: 2461. https://doi.org/10.3390/math11112461

APA StyleAlawneh, S. G., Zeng, L., & Arefifar, S. A. (2023). A Review of High-Performance Computing Methods for Power Flow Analysis. Mathematics, 11(11), 2461. https://doi.org/10.3390/math11112461