A Bidirectional, Full-Duplex, Implantable Wireless CMOS System for Prosthetic Control

Abstract

1. Introduction

2. Materials and Methods

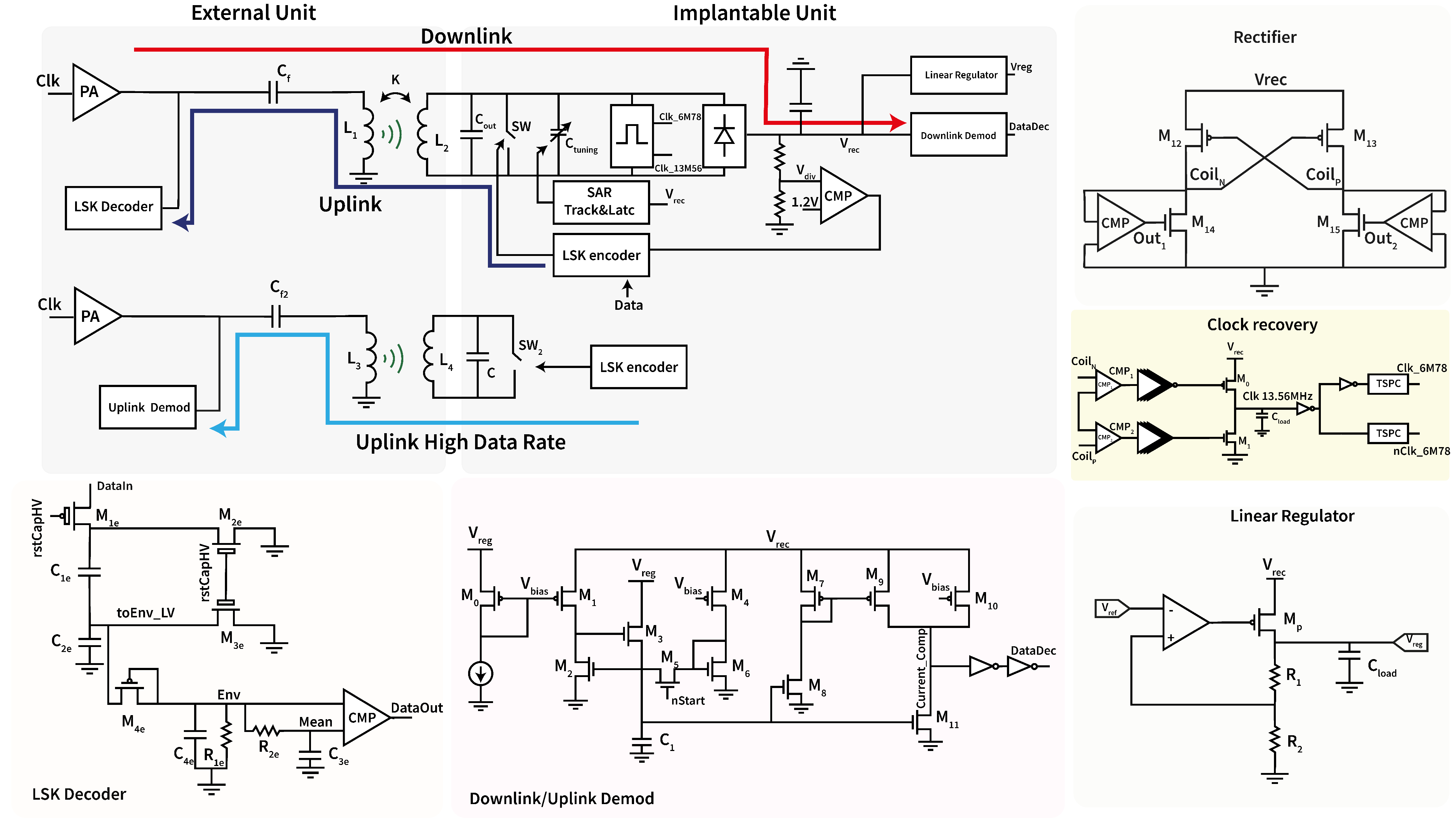

2.1. Implantable Unit

2.1.1. Power Line and Tuning

2.1.2. Wireless Data Transfer

2.2. External Unit

3. Results

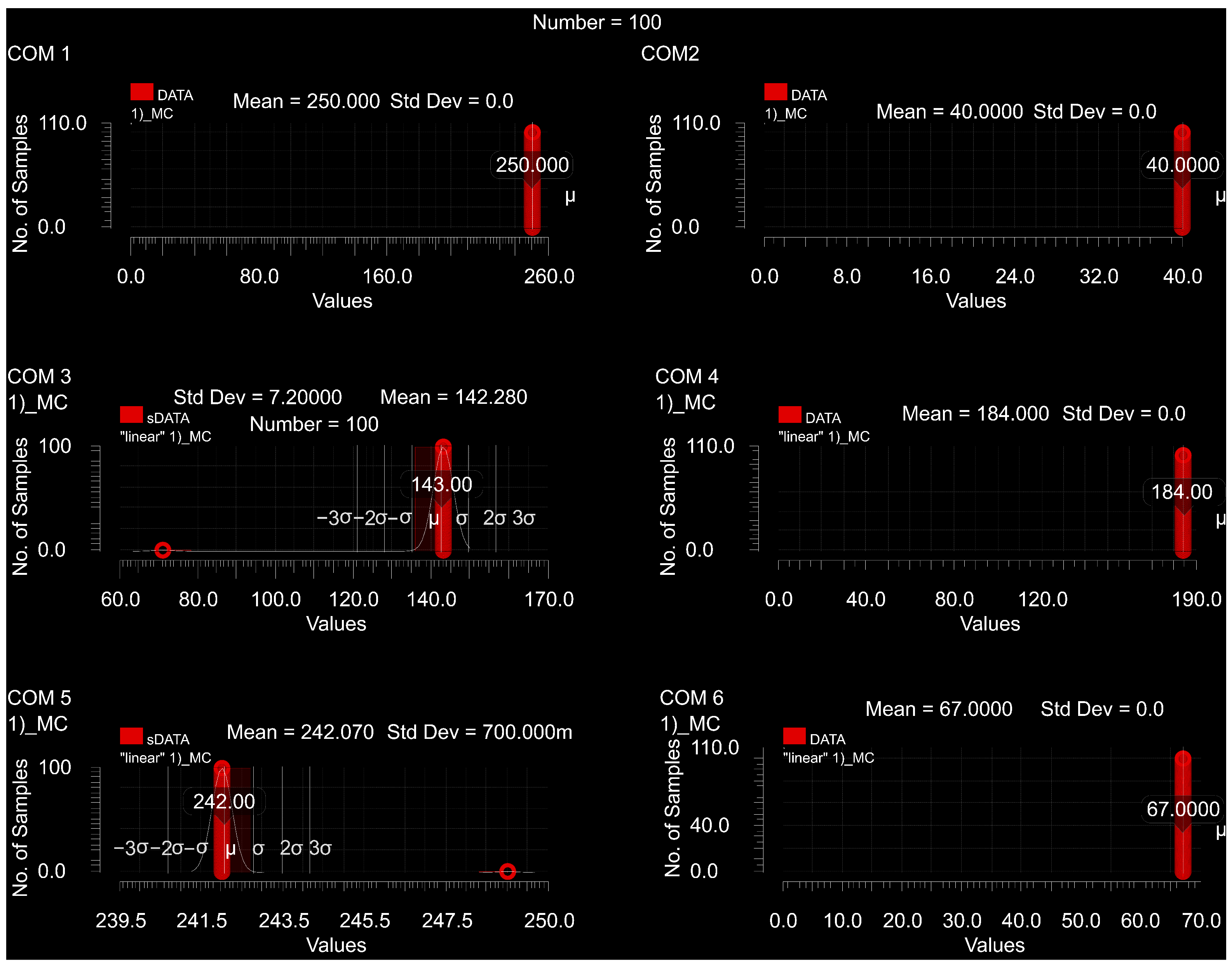

3.1. Active Rectifier

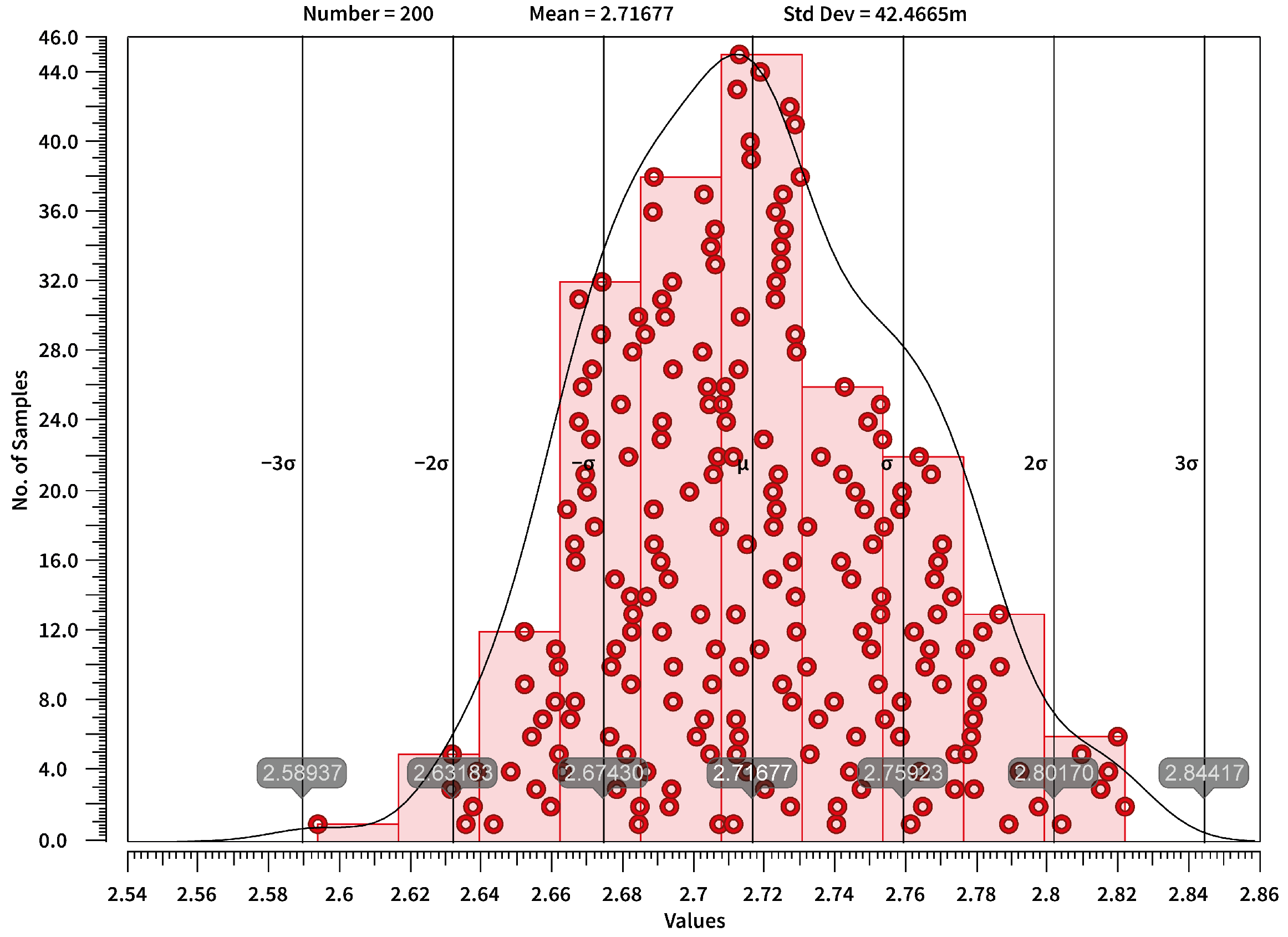

3.2. Linear Regulator

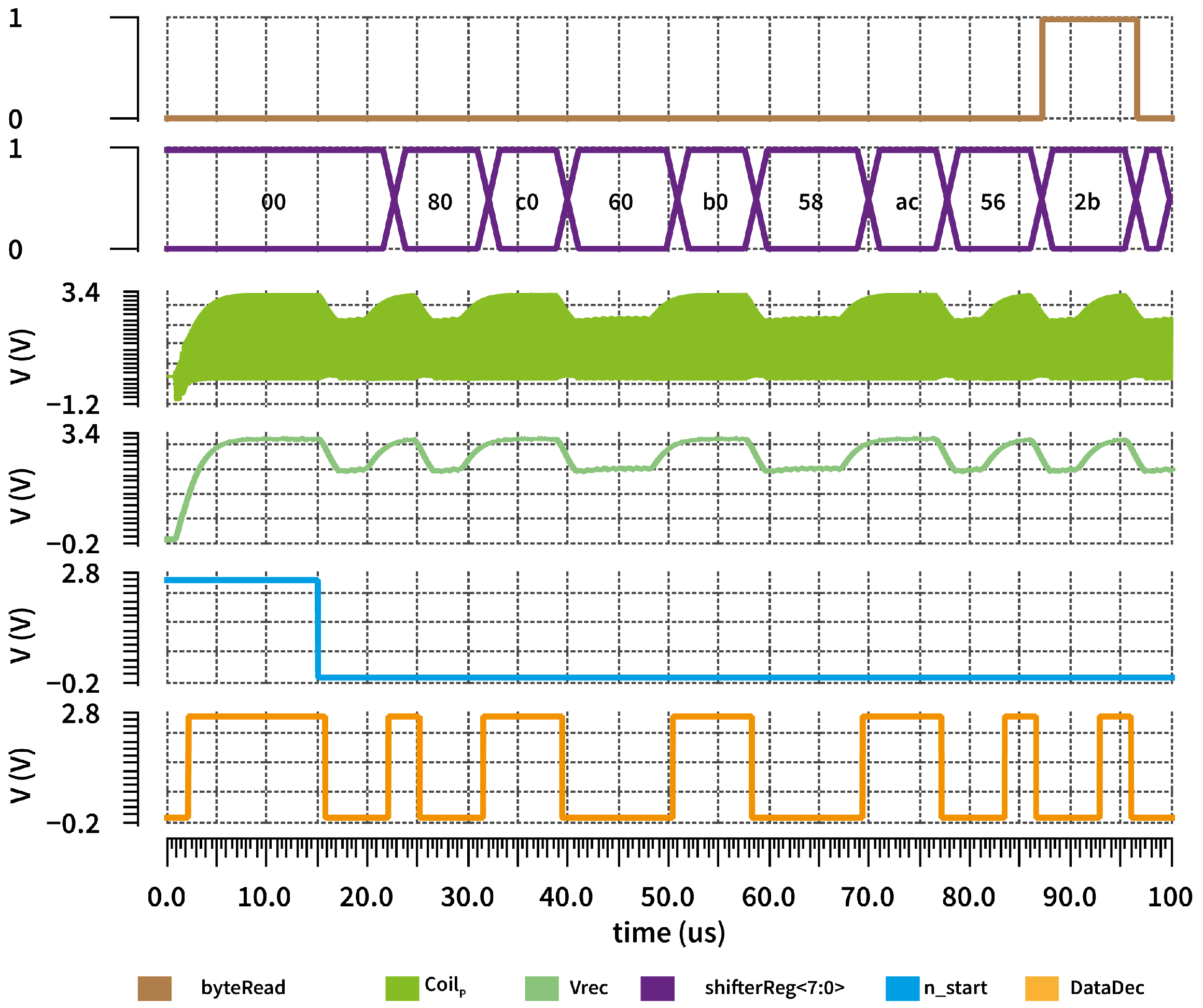

3.3. Half-Duplex Link

3.4. Uplink Low-Data-Rate Demodulation

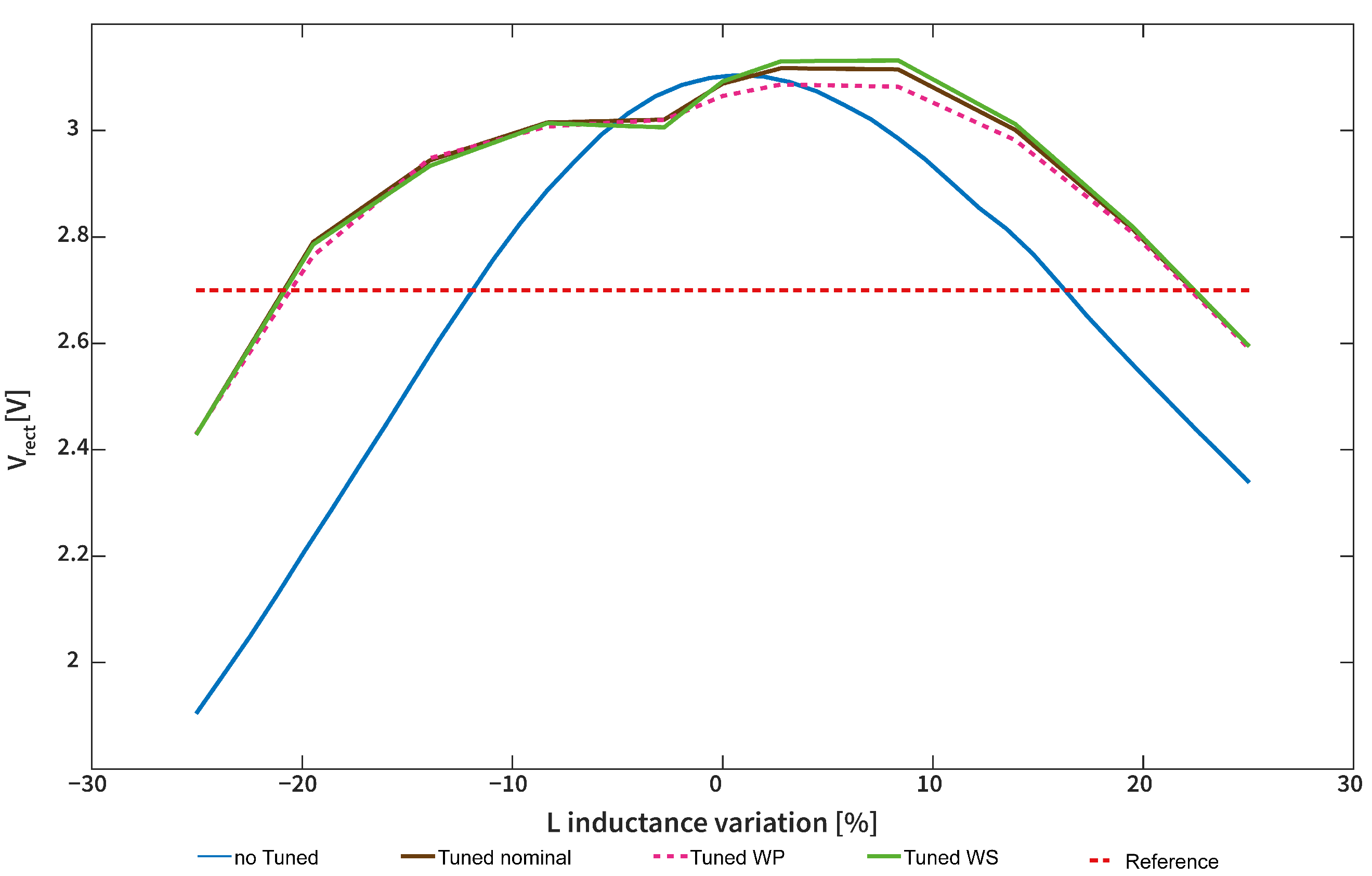

3.5. Tuning Circuit

3.6. Uplink High-Data-Rate Demodulation

3.7. Layout Design

4. Conclusions

Author Contributions

Funding

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Joung, Y.H. Development of implantable medical devices: From an engineering perspective. Int. Neurourol. J. 2013, 17, 98–106. [Google Scholar] [CrossRef]

- Sobot, R. Implantable Technology: History, Controversies, and Social Implications [Commentary]. IEEE Technol. Soc. Mag. 2018, 37, 35–45. [Google Scholar] [CrossRef]

- Xu, S.; Liu, Y.; Lee, H.; Li, W. Neural interfaces: Bridging the brain to the world beyond healthcare. Exploration 2024, 4, 20230146. [Google Scholar] [CrossRef] [PubMed]

- Yoo, S.; Lee, J.; Joo, H.; Sunwoo, S.H.; Kim, S.; Kim, D.H. Wireless Power Transfer and Telemetry for Implantable Bioelectronics. Adv. Healthc. Mater. 2021, 10, 2100614. [Google Scholar] [CrossRef] [PubMed]

- Ortiz-Catalan, M. Ultrasound-powered tiny neural stimulators. Nat. Biomed. Eng. 2020, 4, 144–145. [Google Scholar] [CrossRef]

- Ortiz-Catalan, M.; Mastinu, E.; Sassu, P.; Aszmann, O.; Brånemark, R. Self-Contained Neuromusculoskeletal Arm Prostheses. N. Engl. J. Med. 2020, 382, 1732–1738. [Google Scholar] [CrossRef]

- Zhou, Y.; Liu, C.; Huang, Y. Wireless power transfer for implanted medical application: A review. Energies 2020, 13, 2837. [Google Scholar] [CrossRef]

- Lorach, H.; Galvez, A.; Spagnolo, V.; Martel, F.; Karakas, S.; Intering, N.; Vat, M.; Faivre, O.; Harte, C.; Komi, S.; et al. Walking naturally after spinal cord injury using a brain–spine interface. Nature 2023, 618, 126–133. [Google Scholar] [CrossRef]

- Kindermann, M.; Schwaab, B.; Berg, M.; Fröhlig, G. Longevity of dual chamber pacemakers: Device and patient related determinants. Pacing Clin. Electrophysiol. 2001, 24, 810–815. [Google Scholar] [CrossRef]

- Zhang, J.; Das, R.; Zhao, J.; Mirzai, N.; Mercer, J.; Heidari, H. Battery-Free and Wireless Technologies for Cardiovascular Implantable Medical Devices. Adv. Mater. Technol. 2022, 7, 2101086. [Google Scholar] [CrossRef]

- McGlynn, E.; Nabaei, V.; Ren, E.; Galeote-Checa, G.; Das, R.; Curia, G.; Heidari, H. The Future of Neuroscience: Flexible and Wireless Implantable Neural Electronics. Adv. Sci. 2021, 8, 2002693. [Google Scholar] [CrossRef]

- Singer, A.; Robinson, J.T. Wireless Power Delivery Techniques for Miniature Implantable Bioelectronics. Adv. Healthc. Mater. 2021, 10, 2100664. [Google Scholar] [CrossRef] [PubMed]

- Khan, S.R.; Pavuluri, S.K.; Cummins, G.; Desmulliez, M.P.Y. Wireless power transfer techniques for implantable medical devices: A review. Sensors 2020, 20, 3487. [Google Scholar] [CrossRef] [PubMed]

- Agarwal, K.; Jegadeesan, R.; Guo, Y.X.; Thakor, N.V. Wireless Power Transfer Strategies for Implantable Bioelectronics. IEEE Rev. Biomed. Eng. 2017, 10, 136–161. [Google Scholar] [CrossRef] [PubMed]

- Won, S.M.; Cai, L.; Gutruf, P.; Rogers, J.A. Wireless and battery-free technologies for neuroengineering. Nat. Biomed. Eng. 2023, 7, 405–423. [Google Scholar] [CrossRef]

- Kim, A.; Ochoa, M.; Rahimi, R.; Ziaie, B. New and Emerging Energy Sources for Implantable Wireless Microdevices. IEEE Access 2015, 3, 89–98. [Google Scholar] [CrossRef]

- Wirdatmadja, S.A.; Balasubramaniam, S.; Koucheryavy, Y.; Jornet, J.M. Wireless optogenetic neural dust for deep brain stimulation. In Proceedings of the 2016 IEEE 18th International Conference on e-Health Networking, Applications and Services (Healthcom 2016), Munich, Germany, 14–17 September 2016. [Google Scholar] [CrossRef]

- Neely, R.M.; Piech, D.K.; Santacruz, S.R.; Maharbiz, M.M.; Carmena, J.M. Recent advances in neural dust: Towards a neural interface platform. Curr. Opin. Neurobiol. 2018, 50, 64–71. [Google Scholar] [CrossRef]

- Seo, D.; Carmena, J.M.; Rabaey, J.M.; Alon, E.; Maharbiz, M.M. Neural Dust: An Ultrasonic, Low Power Solution for Chronic Brain-Machine Interfaces. arXiv 2013, arXiv:1307.2196. [Google Scholar] [CrossRef]

- Tyler, D.J. Neural interfaces for somatosensory feedback: Bringing life to a prosthesis. Curr. Opin. Neurol. 2015, 28, 574–581. [Google Scholar] [CrossRef]

- Johnson, B.C.; Shen, K.; Piech, D.; Ghanbari, M.M.; Li, K.Y.; Neely, R.; Carmena, J.M.; Maharbiz, M.M.; Muller, R. StimDust: A 6.5mm3, Wireless Ultrasonic Peripheral Nerve Stimulator with 82% Peak Chip Efficiency. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Piech, D.; Johnson, B.C.; Shen, K.; Ghanbari, M.M.; Li, K.Y.; Neely, R.M.; Muller, R. A wireless millimetre-scale implantable neural stimulator with ultrasonically powered bidirectional communication. Nat. Biomed. Eng. 2020, 4, 207–222. [Google Scholar] [CrossRef]

- Montgomery, K.L.; Yeh, A.J.; Ho, J.S.; Tsao, V.; Mohan Iyer, S.; Grosenick, L.; Ferenczi, E.A.; Tanabe, Y.; Deisseroth, K.; Poon, A.S.Y.; et al. Wirelessly powered, fully internal optogenetics for brain, spinal and peripheral circuits in mice. Nat. Methods 2015, 12, 969–974. [Google Scholar] [CrossRef]

- Park, S.I.; Shin, G.; Banks, A.; McCall, J.G.; Siuda, E.R.; Schmidt, M.J.; Chung, H.U.; Noh, K.N.; Mun, J.G.; Rhodes, J.; et al. Ultraminiaturized photovoltaic and radio frequency powered optoelectronic systems for wireless optogenetics. J. Neural. Eng. 2015, 12, 056002. [Google Scholar] [CrossRef]

- Marincic, A.S.; Grade, B.; Avi, Y. Nikola tesla and the wireless transmission of energy. IEEE Trans. Power Appar. Syst. 1982, 101, 4064–4068. [Google Scholar] [CrossRef]

- Patrick, J.F.; Busby, P.A.; Gibson, P.J. The Development of the Nucleus®FreedomTM Cochlear Implant System. Trends Amplif. 2006, 10, 175–200. [Google Scholar] [CrossRef]

- Zeng, F.G.; Rebscher, S.; Harrison, W.; Sun, X.; Feng, H. Cochlear Implants: System Design, Integration, and Evaluation. IEEE Rev. Biomed. Eng. 2008, 1, 115–142. [Google Scholar] [CrossRef] [PubMed]

- Habibagahi, I.; Omidbeigi, M.; Hadaya, J.; Lyu, H.; Jang, J.; Ardell, J.L.; Bari, A.A.; Babakhani, A. Vagus nerve stimulation using a miniaturized wirelessly powered stimulator in pigs. Sci. Rep. 2022, 12, 8184. [Google Scholar] [CrossRef] [PubMed]

- Lyu, H.; John, M.; Burkland, D.; Greet, B.; Post, A.; Babakhani, A.; Razavi, M. Synchronized Biventricular Heart Pacing in a Closed-chest Porcine Model based on Wirelessly Powered Leadless Pacemakers. Sci. Rep. 2020, 10, 2067. [Google Scholar] [CrossRef]

- Salis, C.; Collu, R.; Barbaro, M. Demodulation Circuit for Power and Bidirectional Data Transmission in Implantable Distributed Wired System. In Proceedings of the 2024 19th Conference On Ph.D Research In Microelectronics And Electronics (PRIME), Larnaca, Cyprus, 9–12 June 2024; pp. 1–4. [Google Scholar]

- Collu, R.; Salis, C.; Barbaro, M. An Automatic Tuning System to Improve Near-Field Powering in Implanted Electronics. In Proceedings of the PRIME 2022—17th International Conference on Ph.D Research in Microelectronics and Electronics, Villasimius, Italy, 12–15 June 2022. [Google Scholar] [CrossRef]

- Gosselin, P.; Puddu, R.; Carreira, A.; Ghanad, M.; Barbaro, M.; Dehollain, C. A CMOS automatic tuning system to maximize remote powering efficiency. In Proceedings of the IEEE 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Tang, Z.; Smith, B.; Schild, J.H.; Peckham, P.H. Data Transmission from an Implantable Biotelemeter by Load-Shift Keying Using Circuit Configuration Modulator. IEEE Trans. Biomed. Eng. 1995, 42, 524–528. [Google Scholar] [CrossRef]

- Baxandall, P.J. Transistor Sine-Wave LC oscillators. Some General Considerations and New Developments. Proc. IEE Part B Electron. Commun. Eng. 1960, 106, 748–758. [Google Scholar] [CrossRef]

- Berkhout, M. An integrated 200-W class-D audio amplifier. IEEE J. Solid-State Circuits 2003, 38, 1198–1206. [Google Scholar] [CrossRef]

- Mei, S.; Hu, Y.; Xu, H.; Wen, H. The Class D Audio Power Amplifier: A Review. Electronics 2022, 11, 3244. [Google Scholar] [CrossRef]

- Shi, L.; Rodriguez, J.C.; Carrizosa, M.J.; Alou, P. ZVS tank optimization for class-D amplifiers in high frequency WPT applications. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; pp. 1593–1598. [Google Scholar] [CrossRef]

- Park, W.; Namgoong, G.; Choi, E.; Bien, F. An On-/Off-Time Sensing-Based Load-Adaptive Mode Control of Triple Mode Buck Converter for Implantable Medical Devices. IEEE Trans. Biomed. Circuits Syst. 2023, 17, 585–597. [Google Scholar] [CrossRef]

- Lee, B.; Kiani, M.; Ghovanloo, M. A Triple-Loop Inductive Power Transmission System for Biomedical Applications. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 138–148. [Google Scholar] [CrossRef]

- Karimi, M.J.; Jin, M.; Zhou, Y.; Dehollain, C.; Schmid, A. Wirelessly Powered and Bi-directional Data Communication System with Adaptive Conversion Chain for Multisite Biomedical Implants Over Single Inductive Link. IEEE Trans. Biomed. Circuits Syst. 2024, 18, 636–647. [Google Scholar] [CrossRef]

- Wang, S.H.; Huang, Y.K.; Chen, C.Y.; Tang, L.Y.; Tu, Y.F.; Chang, P.C.; Lee, C.F.; Yang, C.H.; Hung, C.C.; Liu, C.H.; et al. Design of a Bone-Guided Cochlear Implant Microsystem With Monopolar Biphasic Multiple Stimulations and Evoked Compound Action Potential Acquisition and Its In Vivo Verification. IEEE J. Solid-State Circuits 2021, 56, 3062–3076. [Google Scholar] [CrossRef]

| Work | WPT Carrier (MHz) | Downlink Data Rate | Uplink Data Rate | AC/DC Conv. Eff. | Coil Config (No. Coil) | Tech. |

|---|---|---|---|---|---|---|

| [39] | 13.56 | 50 kbps | 160 bps | 76.2 % | 3 | 0.35 m |

| [40] | 13.56–6.78 | 100 kbps | 678 kbps | 80.1 % | 2 | 0.18 m |

| [41] | 13.56 | 339 kbps | 340 kbps | 90.1 % | 2 | 0.18 m |

| 30 kbps (@13.56 MHz) | ||||||

| This work | 13.56 | 106 kbps | 95.1 % | 4 | 0.18 m | |

| 2.25 Mbps (@27 MHz) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Collu, R.; Salis, C.; Ferrazzano, E.; Barbaro, M. A Bidirectional, Full-Duplex, Implantable Wireless CMOS System for Prosthetic Control. J. Sens. Actuator Netw. 2025, 14, 92. https://doi.org/10.3390/jsan14050092

Collu R, Salis C, Ferrazzano E, Barbaro M. A Bidirectional, Full-Duplex, Implantable Wireless CMOS System for Prosthetic Control. Journal of Sensor and Actuator Networks. 2025; 14(5):92. https://doi.org/10.3390/jsan14050092

Chicago/Turabian StyleCollu, Riccardo, Cinzia Salis, Elena Ferrazzano, and Massimo Barbaro. 2025. "A Bidirectional, Full-Duplex, Implantable Wireless CMOS System for Prosthetic Control" Journal of Sensor and Actuator Networks 14, no. 5: 92. https://doi.org/10.3390/jsan14050092

APA StyleCollu, R., Salis, C., Ferrazzano, E., & Barbaro, M. (2025). A Bidirectional, Full-Duplex, Implantable Wireless CMOS System for Prosthetic Control. Journal of Sensor and Actuator Networks, 14(5), 92. https://doi.org/10.3390/jsan14050092